Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                               |

| Number of I/O              | 24                                                                        |

| Program Memory Size        | 28KB (16K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 2K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 11x12b; D/A 1x8b, 3x5b                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1788-e-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| A0/AN0/C1IN <u>0-/C</u> 2IN0-/<br>3IN0-/C4IN0-/SS <sup>(1)</sup> | RA0<br>AN0<br>C1IN0-<br>C2IN0- | TTL/ST<br>AN | CMOS | General purpose I/O.                            |

|------------------------------------------------------------------|--------------------------------|--------------|------|-------------------------------------------------|

| 3IN0-/C4IN0-/SS <sup>(1)</sup>                                   | C1IN0-                         | AN           |      |                                                 |

|                                                                  |                                |              | —    | ADC Channel 0 input.                            |

|                                                                  | C2IN0-                         | AN           | —    | Comparator C1 negative input.                   |

|                                                                  | 021110                         | AN           | —    | Comparator C2 negative input.                   |

|                                                                  | C3IN0-                         | AN           | —    | Comparator C3 negative input.                   |

|                                                                  | C4IN0-                         | AN           | —    | Comparator C4 negative input.                   |

|                                                                  | SS                             | ST           | —    | Slave Select input.                             |

| A1/AN1/C1IN1-/C2IN1-/                                            | RA1                            | TTL/ST       | CMOS | General purpose I/O.                            |

| 3IN1-/C4IN1-/OPA1OUT                                             | AN1                            | AN           | _    | ADC Channel 1 input.                            |

|                                                                  | C1IN1-                         | AN           | _    | Comparator C1 negative input.                   |

|                                                                  | C2IN1-                         | AN           |      | Comparator C2 negative input.                   |

|                                                                  | C3IN1-                         | AN           |      | Comparator C3 negative input.                   |

|                                                                  | C4IN1-                         | AN           |      | Comparator C4 negative input.                   |

|                                                                  | OPA1OUT                        |              | AN   | Operational Amplifier 1 output.                 |

| A2/AN2/C1IN0+/C2IN0+/                                            | RA2                            | TTL/ST       | CMOS | General purpose I/O.                            |

| 3IN0+/C4IN0+/DAC1OUT1/                                           | AN2                            | AN           | _    | ADC Channel 2 input.                            |

| REF-/DAC1VREF-                                                   | C1IN0+                         | AN           | _    | Comparator C1 positive input.                   |

|                                                                  | C2IN0+                         | AN           | —    | Comparator C2 positive input.                   |

|                                                                  | C3IN0+                         | AN           | _    | Comparator C3 positive input.                   |

|                                                                  | C4IN0+                         | AN           |      | Comparator C4 positive input.                   |

|                                                                  | DAC1OUT1                       | _            | AN   | Digital-to-Analog Converter output.             |

|                                                                  | VREF-                          | AN           |      | ADC Negative Voltage Reference input.           |

|                                                                  | DAC1VREF-                      | AN           |      | Digital-to-Analog Converter negative reference. |

| A3/AN3/VREF+/C1IN1+/                                             | RA3                            | TTL/ST       | CMOS | General purpose I/O.                            |

| AC1VREF+/DAC2VREF+/                                              | AN3                            | AN           |      | ADC Channel 3 input.                            |

| AC3VREF+/DAC4VREF+                                               | VREF+                          | AN           |      | ADC Voltage Reference input.                    |

|                                                                  | C1IN1+                         | AN           | _    | Comparator C1 positive input.                   |

|                                                                  | DAC1VREF+                      | AN           |      | Digital-to-Analog Converter positive reference. |

|                                                                  | DAC2VREF+                      | AN           |      | Digital-to-Analog Converter positive reference. |

|                                                                  | DAC3VREF+                      | AN           | _    | Digital-to-Analog Converter positive reference. |

|                                                                  | DAC4VREF+                      | AN           | _    | Digital-to-Analog Converter positive reference. |

| A4/C1OUT/OPA1IN+/T0CKI                                           | RA4                            | TTL/ST       | CMOS | General purpose I/O.                            |

|                                                                  | C10UT                          | _            | CMOS | Comparator C1 output.                           |

|                                                                  | OPA1IN+                        | AN           | _    | Operational Amplifier 1 non-inverting input.    |

|                                                                  | TOCKI                          | ST           | _    | Timer0 clock input.                             |

| A5/AN4/C2OUT/OPA1IN-/                                            | RA5                            | TTL/ST       | CMOS | General purpose I/O.                            |

| S <sup>(1)</sup> /DAC2OUT1                                       | AN4                            | AN           | _    | ADC Channel 4 input.                            |

|                                                                  | C2OUT                          |              | CMOS | Comparator C2 output.                           |

|                                                                  | OPA1IN-                        | AN           | _    | Operational Amplifier 1 inverting input.        |

|                                                                  | SS                             | ST           | _    | Slave Select input.                             |

|                                                                  | DAC2OUT1                       |              | AN   | Digital-to-Analog Converter output.             |

PIC16(L)F1789 PINOUT DESCRIPTION **TABLE 1-3:**

XTAL = Crystal Note 1: Pin functions can be assigned to one of two locations via software. See Register 13-1.

2: All pins have interrupt-on-change functionality.

HV = High Voltage

levels

#### 3.2.1.1 STATUS Register

The STATUS register, shown in Register 3-1, contains:

- · the arithmetic status of the ALU

- · the Reset status

**REGISTER 3-1:**

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the  $\overline{TO}$  and  $\overline{PD}$  bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

#### 3.3 **Register Definitions: Status**

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits (Refer to Section 30.0 "Instruction Set Summary").

| Note: | The C and DC bits operate as Borrow and |  |  |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|--|--|

|       | Digit Borrow out bits, respectively, in |  |  |  |  |  |  |

|       | subtraction.                            |  |  |  |  |  |  |

| U-0 | U-0 | U-0 | R-1/q | R-1/g |  |

|-----|-----|-----|-------|-------|--|

STATUS: STATUS REGISTER

| U-0                                                                                                                                                      | U-0                | U-0                                  | R-1/q         | R-1/q                  | R/W-0/u                    | R/W-0/u           | R/W-0/u          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------------------------|---------------|------------------------|----------------------------|-------------------|------------------|

|                                                                                                                                                          | _                  |                                      | TO            | PD                     | Z                          | DC <sup>(1)</sup> | C <sup>(1)</sup> |

| bit 7                                                                                                                                                    |                    |                                      |               |                        |                            |                   | bit (            |

|                                                                                                                                                          |                    |                                      |               |                        |                            |                   |                  |

| Legend:                                                                                                                                                  |                    |                                      |               |                        |                            |                   |                  |

| R = Readab                                                                                                                                               | le bit             | W = Writable I                       | oit           | U = Unimpler           | mented bit, read           | l as '0'          |                  |

| u = Bit is une                                                                                                                                           | changed            | x = Bit is unkn                      | own           | -n/n = Value a         | at POR and BO              | R/Value at all o  | ther Resets      |

| '1' = Bit is se                                                                                                                                          | et                 | '0' = Bit is clea                    | ared          | q = Value der          | pends on condit            | ion               |                  |

|                                                                                                                                                          |                    |                                      |               |                        |                            |                   |                  |

| bit 7-5                                                                                                                                                  | Unimplemen         | ted: Read as '0                      | )'            |                        |                            |                   |                  |

| bit 4                                                                                                                                                    | TO: Time-Out       | t bit                                |               |                        |                            |                   |                  |

|                                                                                                                                                          |                    | er-up, CLRWDT                        |               | r SLEEP <b>instruc</b> | tion                       |                   |                  |

|                                                                                                                                                          |                    | me-out occurred                      | t l           |                        |                            |                   |                  |

| bit 3                                                                                                                                                    | PD: Power-D        | own bit                              |               |                        |                            |                   |                  |

|                                                                                                                                                          |                    | er-up or by the                      |               |                        |                            |                   |                  |

| 1.1.0                                                                                                                                                    |                    | tion of the SLEE                     | P Instruction | 1                      |                            |                   |                  |

| bit 2                                                                                                                                                    | <b>Z:</b> Zero bit |                                      |               |                        |                            |                   |                  |

|                                                                                                                                                          |                    | t of an arithmet<br>t of an arithmet | <b>U</b> 1    |                        | ero                        |                   |                  |

| bit 1                                                                                                                                                    |                    |                                      | •             |                        | SUBWF instruction          | ons)(1)           |                  |

|                                                                                                                                                          | -                  |                                      |               |                        |                            | 0110)             |                  |

| <ul> <li>1 = A carry-out from the 4th low-order bit of the result occurred</li> <li>0 = No carry-out from the 4th low-order bit of the result</li> </ul> |                    |                                      |               |                        |                            |                   |                  |

| bit 0                                                                                                                                                    |                    | ow bit <sup>(1)</sup> (ADDW          |               |                        | structions) <sup>(1)</sup> |                   |                  |

|                                                                                                                                                          | 1 = A carry-or     | ut from the Mos                      | t Significant | bit of the result      | occurred                   |                   |                  |

|                                                                                                                                                          | 0 = No carry-      | out from the Mo                      | st Significan | t bit of the resu      | It occurred                |                   |                  |

| Note 1: F                                                                                                                                                | or Borrow, the po  | larity is reverse                    | d A subtract  | tion is executed       | l by adding the            | two's complem     | ent of the       |

Note 1: For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand.

| SSINTOSC/                      | - LEINTORC (FROM and WOY disablad)                                                                    |

|--------------------------------|-------------------------------------------------------------------------------------------------------|

| HFINTOSC/                      |                                                                                                       |

| MENTOSC                        | Clarbus Time - Scovile Bync                                                                           |

| LFINTOSC                       |                                                                                                       |

| IRCF <3:0>                     | $\neq 0$ $\neq 0$ $= 0$                                                                               |

| System Clock                   |                                                                                                       |

|                                |                                                                                                       |

|                                |                                                                                                       |

|                                | <ul> <li>UFINTOSC (Elliner PSCM or WOT enabled)</li> </ul>                                            |

| MENTORS                        | • • • • • • • • • • • • • • • • • • •                                                                 |

| HFINTOSC/                      | , munt (munt) kunne sunne vanne kunne sunnemmennemmennemmennemmennemmennemmennemmennemmennemmennemmen |

|                                |                                                                                                       |

| LFINTOSC                       |                                                                                                       |

| IRCF <3:0>                     | $\neq 0$ $\chi = 0$                                                                                   |

| System Clock                   |                                                                                                       |

| Cystem clock                   |                                                                                                       |

|                                |                                                                                                       |

|                                |                                                                                                       |

|                                |                                                                                                       |

|                                | - NEWYORCANFINITORC<br>LEVELOSC tume of unave 7457 or FSOM is enabled                                 |

| LEINTOSC                       | 1,87487330 turne off university or 83.086 is enabled                                                  |

|                                |                                                                                                       |

| LEPTOSC<br>HERTOSC/            | LEUCIOC turns off units a VET or FSOM is enabled                                                      |

| LERECSC                        | LFURTOBC turns off unities WEAT or FISOM is enabled                                                   |

| LEWIOSC<br>HENTOSC/<br>MENTOSC | LEVELOSC turns off univers 9457 or FSOM is enabled                                                    |

### 7.0 REFERENCE CLOCK MODULE

The reference clock module provides the ability to send a divided clock to the clock output pin of the device (CLKR). This module is available in all oscillator configurations and allows the user to select a greater range of clock submultiples to drive external devices in the application. The reference clock module includes the following features:

- System clock is the source

- Available in all oscillator configurations

- · Programmable clock divider

- Output enable to a port pin

- Selectable duty cycle

- · Slew rate control

The reference clock module is controlled by the CLKRCON register (Register 7-1) and is enabled when setting the CLKREN bit. To output the divided clock signal to the CLKR port pin, the CLKROE bit must be set. The CLKRDIV<2:0> bits enable the selection of eight different clock divider options. The CLKRDC<1:0> bits can be used to modify the duty cycle of the output clock<sup>(1)</sup>. The CLKRSLR bit controls slew rate limiting.

Note 1: If the base clock rate is selected without a divider, the output clock will always have a duty cycle equal to that of the source clock, unless a 0% duty cycle is selected. If the clock divider is set to base clock/2, then 25% and 75% duty cycle accuracy will be dependent upon the source clock.

#### 7.1 Slew Rate

The slew rate limitation on the output port pin can be disabled. The slew rate limitation is removed by clearing the CLKRSLR bit in the CLKRCON register.

#### 7.2 Effects of a Reset

Upon any device Reset, the reference clock module is disabled. The user's firmware is responsible for initializing the module before enabling the output. The registers are reset to their default values.

#### 7.3 Operation During Sleep

As the reference clock module relies on the system clock as its source, and the system clock is disabled in Sleep, the module does not function in Sleep, even if an external clock source or the Timer1 clock source is configured as the system clock. The module outputs will remain in their current state until the device exits Sleep.

| FIGURE 8  | 8-2: I       | NTERRUPT      |                   |                  |             |             |             |             |

|-----------|--------------|---------------|-------------------|------------------|-------------|-------------|-------------|-------------|

|           |              |               |                   |                  |             |             |             |             |

| OSC1      | M            |               |                   |                  |             |             |             |             |

|           | Q1 Q2 Q3 Q4  | Q1 Q2 Q3 Q4   | Q1 Q2 Q3 Q4       | Q1 Q2 Q3 Q4      | Q1 Q2 Q3 Q4 | Q1 Q2 Q3 Q4 | Q1 Q2 Q3 Q4 | Q1 Q2 Q3 Q4 |

| CLKR      |              |               | Interru<br>during | pt Sampled<br>Q1 |             |             |             |             |

| Interrupt |              |               |                   |                  |             |             |             |             |

| GIE       |              |               |                   |                  |             |             |             |             |

| PC        | PC-1         | РС            | PC                | +1               | 0004h       | 0005h       |             |             |

| Execute   | 1 Cycle Inst | ruction at PC | Inst(PC)          | NOP              | NOP         | Inst(0004h) |             |             |

|           |              | <br>          |                   |                  |             |             |             |             |

| Interrupt |              |               |                   |                  |             |             |             |             |

| GIE       |              |               |                   |                  |             |             |             |             |

| PC        | PC-1         | PC            | PC+1/FSR<br>ADDR  | New PC/<br>PC+1  | 0004h       | 0005h       |             |             |

| Execute-  | 2 Cycle Inst | ruction at PC | Inst(PC)          | NOP              | NOP         | Inst(0004h) |             |             |

|           |              |               |                   |                  |             |             |             |             |

| Interrupt |              |               |                   |                  |             |             |             |             |

| GIE       |              |               |                   |                  |             |             |             |             |

| PC        | PC-1         | PC            | FSR ADDR          | PC+1             | PC+2        | 0004h       | 0005h       |             |

| Execute   | 3 Cycle Inst | ruction at PC | INST(PC)          | NOP              | NOP         | NOP         | Inst(0004h) | Inst(0005h) |

| Interrupt |              |               |                   |                  |             |             |             |             |

| GIE       |              |               |                   |                  |             |             |             |             |

| PC        | PC-1         | РС            | FSR ADDR          | PC+1             | РС          | +2          | 0004h       | 0005h       |

| Execute   | 3 Cycle Inst | ruction at PC | INST(PC)          | NOP              | NOP         | NOP         | NOP         | Inst(0004h) |

|           |              |               |                   |                  |             |             |             |             |

#### 9.1.1 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction

- SLEEP instruction will execute as a NOP.

- WDT and WDT prescaler will not be cleared

- TO bit of the STATUS register will not be set

- PD bit of the STATUS register will not be cleared.

- If the interrupt occurs **during or after** the execution of a **SLEEP** instruction

- SLEEP instruction will be completely executed

- Device will immediately wake-up from Sleep

- WDT and WDT prescaler will be cleared

- TO bit of the STATUS register will be set

- PD bit of the STATUS register will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

| CLKIN <sup>(1)</sup><br>CLKOUT <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                         |                               |                |                 | Q1 Q2 Q3 Q4<br>/~_/~_/<br>\/          | Q1 Q2 Q3 Q4<br>/\_/\_/ | Q1 Q2 Q3 Q4<br>                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------|-----------------|---------------------------------------|------------------------|---------------------------------------|

| Interrupt flag                                                                                                                                                                                                                                                                                                                                                                                                                                        |                               |                | Interrupt Laten | су <sup>(4)</sup>                     |                        | · · · · · · · · · · · · · · · · · · · |

| GIE bit<br>(INTCON reg.                                                                                                                                                                                                                                                                                                                                                                                                                               | Processor<br>Sleep            | in<br>✦        |                 |                                       |                        |                                       |

| Instruction Flow<br>PC                                                                                                                                                                                                                                                                                                                                                                                                                                |                               | <u>C + 2 X</u> | PC + 2          | PC+2                                  | X 0004h                | X 0005h                               |

| Instruction {                                                                                                                                                                                                                                                                                                                                                                                                                                         | Inst(PC) = Sleep Inst(PC + 1) | <u> </u>       | Inst(PC + 2)    | · · · · · · · · · · · · · · · · · · · | Inst(0004h)            | Inst(0005h)                           |

| Instruction {<br>Executed {                                                                                                                                                                                                                                                                                                                                                                                                                           | Inst(PC - 1) Sleep            | 1<br>1<br>1    | Inst(PC + 1)    | Forced NOP                            | Forced NOP             | Inst(0004h)                           |

| <ul> <li>Note 1: External clock. High, Medium, Low mode assumed.</li> <li>2: CLKOUT is shown here for timing reference.</li> <li>3: Tost = 1024 Tosc; This delay does not apply to EC, RC and INTOSC Oscillator modes or Two-Speed Start-up (See Section 6.4 "Two-Speed Clock Start-up Mode").</li> <li>4: GIE = 1 assumed. In this case after wake-up, the processor calls the ISR at 0004h. If GIE = 0, execution will continue in-line.</li> </ul> |                               |                |                 |                                       |                        |                                       |

#### FIGURE 9-1: WAKE-UP FROM SLEEP THROUGH INTERRUPT

#### 12.2 Using the Data EEPROM

The data EEPROM is a high-endurance, byte addressable array that has been optimized for the storage of frequently changing information (e.g., program variables or other data that are updated often). When variables in one section change frequently, while variables in another section do not change, it is possible to exceed the total number of write cycles to the EEPROM without exceeding the total number of write cycles to a single byte. Refer to **Section 31.0 "Electrical Specifications"**. If this is the case, then a refresh of the array must be performed. For this reason, variables that change infrequently (such as constants, IDs, calibration, etc.) should be stored in Flash program memory.

#### 12.2.1 READING THE DATA EEPROM MEMORY

To read a data memory location, the user must write the address to the EEADRL register, clear the EEPGD and CFGS control bits of the EECON1 register, and then set control bit RD. The data is available at the very next cycle, in the EEDATL register; therefore, it can be read in the next instruction. EEDATL will hold this value until another read or until it is written to by the user (during a write operation).

#### EXAMPLE 12-1: DATA EEPROM READ

| BANKSEL | EEADRL      | ;                         |

|---------|-------------|---------------------------|

| MOVLW   | DATA_EE_ADI | DR ;                      |

| MOVWF   | EEADRL      | ;Data Memory              |

|         |             | ;Address to read          |

| BCF     | EECON1, CFG | GS ;Deselect Config space |

| BCF     | EECON1, EED | PGD;Point to DATA memory  |

| BSF     | EECON1, RD  | ;EE Read                  |

| MOVF    | EEDATL, W   | ;W = EEDATL               |

|         |             |                           |

### Note: Data EEPROM can be read regardless of the setting of the CPD bit.

### 12.2.2 WRITING TO THE DATA EEPROM MEMORY

To write an EEPROM data location, the user must first write the address to the EEADRL register and the data to the EEDATL register. Then the user must follow a specific sequence to initiate the write for each byte.

The write will not initiate if the above sequence is not followed exactly (write 55h to EECON2, write AAh to EECON2, then set the WR bit) for each byte. Interrupts should be disabled during this code segment.

Additionally, the WREN bit in EECON1 must be set to enable write. This mechanism prevents accidental writes to data EEPROM due to errant (unexpected) code execution (i.e., lost programs). The user should keep the WREN bit clear at all times, except when updating EEPROM. The WREN bit is not cleared by hardware.

After a write sequence has been initiated, clearing the WREN bit will not affect this write cycle. The WR bit will be inhibited from being set unless the WREN bit is set.

At the completion of the write cycle, the WR bit is cleared in hardware and the EE Write Complete Interrupt Flag bit (EEIF) is set. The user can either enable this interrupt or poll this bit. EEIF must be cleared by software.

### 12.2.3 PROTECTION AGAINST SPURIOUS WRITE

There are conditions when the user may not want to write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been built-in. On power-up, WREN is cleared. Also, the Power-up Timer (64 ms duration) prevents EEPROM write.

The write initiate sequence and the WREN bit together help prevent an accidental write during:

- Brown-out

- · Power Glitch

- Software Malfunction

#### 12.2.4 DATA EEPROM OPERATION DURING CODE-PROTECT

Data memory can be code-protected by programming the  $\overline{CPD}$  bit in the Configuration Words to '0'.

When the data memory is code-protected, only the CPU is able to read and write data to the data EEPROM. It is recommended to code-protect the program memory when code-protecting data memory. This prevents anyone from replacing your program with a program that will access the contents of the data EEPROM.

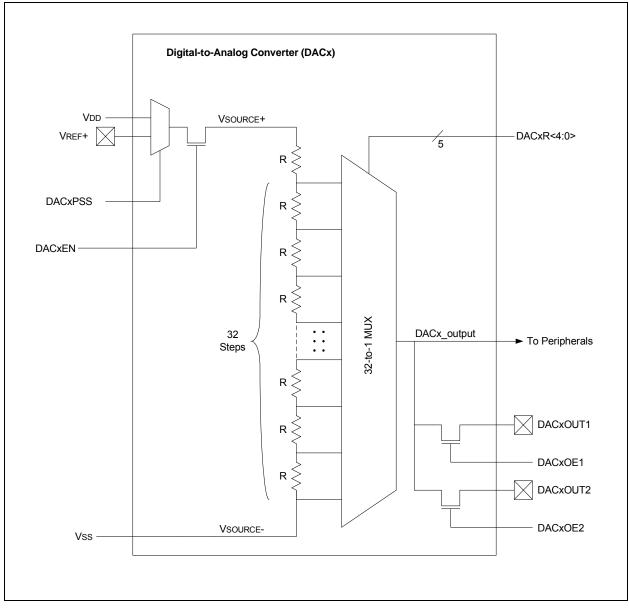

#### 19.0 8-BIT DIGITAL-TO-ANALOG CONVERTER (DAC) MODULE

The Digital-to-Analog Converter supplies a variable voltage reference, ratiometric with the input source, with 256 selectable output levels.

The input of the DAC can be connected to:

- External VREF pins

- VDD supply voltage

- FVR (Fixed Voltage Reference)

The output of the DAC can be configured to supply a reference voltage to the following:

- Comparator positive input

- Op amp positive input

- ADC input channel

- DAC1OUT1 pin

- DAC1OUT2 pin

The Digital-to-Analog Converter (DAC) is enabled by setting the DAC1EN bit of the DAC1CON0 register.

#### 19.1 Output Voltage Selection

The DAC has 256 voltage level ranges. The 256 levels are set with the DAC1R<7:0> bits of the DAC1CON1 register.

The DAC output voltage is determined by Equation 19-1:

#### EQUATION 19-1: DAC OUTPUT VOLTAGE

$$\frac{IF DACxEN = 1}{VOUT} = \left( (VSOURCE+ - VSOURCE-) \times \frac{DACxR[7:0]}{2^8} \right) + VSOURCE-$$

$$VSOURCE+ = VDD, VREF, or FVR BUFFER 2$$

$$VSOURCE- = VSS$$

#### 19.2 Ratiometric Output Level

The DAC output value is derived using a resistor ladder with each end of the ladder tied to a positive and negative voltage reference input source. If the voltage of either input source fluctuates, a similar fluctuation will result in the DAC output value.

The value of the individual resistors within the ladder can be found in **Section 31.0** "**Electrical Specifications**".

#### **19.3 DAC Voltage Reference Output**

The DAC voltage can be output to the DAC1OUT1 and DAC1OUT2 pins by setting the respective DAC1OE1 and DAC1OE2 pins of the DAC1CON0 register. Selecting the DAC reference voltage for output on either DAC1OUTx pin automatically overrides the digital output buffer and digital input threshold detector functions of that pin. Reading the DAC1OUTx pin when it has been configured for DAC reference voltage output will always return a '0'.

Due to the limited current drive capability, a buffer must be used on the DAC voltage reference output for external connections to either DAC1OUTx pin. Figure 19-2 shows an example buffering technique.

© 2013-2015 Microchip Technology Inc.

#### FIGURE 20-1: DIGITAL-TO-ANALOG CONVERTER BLOCK DIAGRAM

#### 24.1 Timer2 Operation

The clock input to the Timer2 modules is the system instruction clock (Fosc/4).

A 4-bit counter/prescaler on the clock input allows direct input, divide-by-4 and divide-by-16 prescale options. These options are selected by the prescaler control bits, T2CKPS<1:0> of the T2CON register. The value of TMR2 is compared to that of the Period register, PR2, on each clock cycle. When the two values match, the comparator generates a match signal as the timer output. This signal also resets the value of TMR2 to 00h on the next cycle and drives the output counter/postscaler (see Section 24.2 "Timer2 Interrupt").

The TMR2 and PR2 registers are both directly readable and writable. The TMR2 register is cleared on any device Reset, whereas the PR2 register initializes to FFh. Both the prescaler and postscaler counters are cleared on the following events:

- · a write to the TMR2 register

- · a write to the T2CON register

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- MCLR Reset

- Watchdog Timer (WDT) Reset

- · Stack Overflow Reset

- Stack Underflow Reset

- RESET Instruction

| Note:    | TMR2 | is | not | cleared | when | T2CON | is |

|----------|------|----|-----|---------|------|-------|----|

| written. |      |    |     |         |      |       |    |

#### 24.2 Timer2 Interrupt

Timer2 can also generate an optional device interrupt. The Timer2 output signal (TMR2-to-PR2 match) provides the input for the 4-bit counter/postscaler. This counter generates the TMR2 match interrupt flag which is latched in TMR2IF of the PIR1 register. The interrupt is enabled by setting the TMR2 Match Interrupt Enable bit, TMR2IE, of the PIE1 register.

A range of 16 postscale options (from 1:1 through 1:16 inclusive) can be selected with the postscaler control bits, T2OUTPS<3:0>, of the T2CON register.

#### 24.3 Timer2 Output

The unscaled output of TMR2 is available primarily to the CCP modules, where it is used as a time base for operations in PWM mode.

Timer2 can be optionally used as the shift clock source for the MSSP module operating in SPI mode. Additional information is provided in Section 27.0 "Master Synchronous Serial Port (MSSP) Module"

#### 24.4 Timer2 Operation During Sleep

The Timer2 timers cannot be operated while the processor is in Sleep mode. The contents of the TMR2 and PR2 registers will remain unchanged while the processor is in Sleep mode.

#### 25.1.2 TIMER1 MODE RESOURCE

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

See Section 23.0 "Timer1 Module with Gate Control" for more information on configuring Timer1.

#### 25.1.3 SOFTWARE INTERRUPT MODE

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit of the PIEx register clear to avoid false interrupts. Additionally, the user should clear the CCPxIF interrupt flag bit of the PIRx register following any change in Operating mode.

| Note: | Clocking Timer1 from the system clock<br>(Fosc) should not be used in Capture<br>mode. In order for Capture mode to<br>recognize the trigger event on the CCPx<br>pin, Timer1 must be clocked from the<br>instruction clock (Fosc/4) or from an |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | external clock source.                                                                                                                                                                                                                          |

#### 25.1.4 CCP PRESCALER

There are four prescaler settings specified by the CCPxM<3:0> bits of the CCPxCON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCPxCON register before changing the prescaler. Equation 25-1 demonstrates the code to perform this function.

#### EXAMPLE 25-1: CHANGING BETWEEN CAPTURE PRESCALERS

| BANKSEL | CCPxCON     | ;Set Bank bits to point |

|---------|-------------|-------------------------|

|         |             | ;to CCPxCON             |

| CLRF    | CCPxCON     | ;Turn CCP module off    |

| MOVLW   | NEW_CAPT_PS | ;Load the W reg with    |

|         |             | ;the new prescaler      |

|         |             | ;move value and CCP ON  |

| MOVWF   | CCPxCON     | ;Load CCPxCON with this |

|         |             | ;value                  |

#### 25.1.5 CAPTURE DURING SLEEP

Capture mode depends upon the Timer1 module for proper operation. There are two options for driving the Timer1 module in Capture mode. It can be driven by the instruction clock (FOSC/4), or by an external clock source.

When Timer1 is clocked by Fosc/4, Timer1 will not increment during Sleep. When the device wakes from Sleep, Timer1 will continue from its previous state.

Capture mode will operate during Sleep when Timer1 is clocked by an external clock source.

#### 25.1.6 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function register APFCON. To determine which pins can be moved and what their default locations are upon a Reset, see **Section 13.1 "Alternate Pin Function**" for more information.

#### 25.2 Compare Mode

The Compare mode function described in this section is available and identical for all CCP modules.

Compare mode makes use of the 16-bit Timer1 resource. The 16-bit value of the CCPRxH:CCPRxL register pair is constantly compared against the 16-bit value of the TMR1H:TMR1L register pair. When a match occurs, one of the following events can occur:

- Toggle the CCPx output

- · Set the CCPx output

- Clear the CCPx output

- · Generate an Auto-conversion Trigger

- · Generate a Software Interrupt

The action on the pin is based on the value of the CCPxM<3:0> control bits of the CCPxCON register. At the same time, the interrupt flag CCPxIF bit is set.

All Compare modes can generate an interrupt.

Figure 25-2 shows a simplified diagram of the compare operation.

#### 26.3.12 3-PHASE PWM

The 3-Phase mode of operation is used in 3-phase power supply and motor drive applications configured as three half-bridges. A half-bridge configuration consists of two power driver devices in series, between the positive power rail (high side) and negative power rail (low side). The three outputs come from the junctions between the two drivers in each half-bridge. When the steering control selects a phase drive, power flows from the positive rail through a high-side power device to the load and back to the power supply through a low-side power device.

In this mode of operation, all six PSMC outputs are used, but only two are active at a time.

The two active outputs consist of a high-side driver and low-side driver output.

#### 26.3.12.1 Mode Features

- · No dead-band control is available

- · PWM can be steered to the following six pairs:

- PSMCxA and PSMCxD

- PSMCxA and PSMCxF

- PSMCxC and PSMCxF

- PSMCxC and PSMCxB

- PSMCxE and PSMCxB

- PSMCxE and PSMCxD

#### 26.3.12.2 Waveform Generation

3-phase steering has a more complex waveform generation scheme than the other modes. There are several factors which go into what waveforms are created.

The PSMC outputs are grouped into three sets of drivers: one for each phase. Each phase has two associated PWM outputs: one for the high-side drive and one for the low-side drive.

High Side drives are indicated by 1H, 2H and 3H.

Low Side drives are indicated by 1L, 2L, 3L.

Phase grouping is mapped as shown in Table 26-1. There are six possible phase drive combinations. Each phase drive combination activates two of the six outputs and deactivates the other four. Phase drive is selected with the steering control as shown in Table 26-2.

| PSMC grouping |    |  |  |  |  |  |  |  |

|---------------|----|--|--|--|--|--|--|--|

| PSMCxA        | 1H |  |  |  |  |  |  |  |

| PSMCxB        | 1L |  |  |  |  |  |  |  |

| PSMCxC        | 2H |  |  |  |  |  |  |  |

| PSMCxD        | 2L |  |  |  |  |  |  |  |

| PSMCxE        | 3H |  |  |  |  |  |  |  |

| PSMCxF        | 3L |  |  |  |  |  |  |  |

#### TABLE 26-1: PHASE GROUPING

| TADLE 20-2 | . <b>3</b> -FTI | ASL STELL                      |          | <b>NOL</b> |          |          |          |          |  |  |  |

|------------|-----------------|--------------------------------|----------|------------|----------|----------|----------|----------|--|--|--|

|            |                 | PSMCxSTR0 Value <sup>(1)</sup> |          |            |          |          |          |          |  |  |  |

| PSMC ou    | utputs          | 00h                            | 01h      | 02h        | 04h      | 08h      | 10h      | 20h      |  |  |  |

| PSMCxA     | 1H              | inactive                       | active   | active     | inactive | inactive | inactive | inactive |  |  |  |

| PSMCxB     | 1L              | inactive                       | inactive | inactive   | inactive | active   | active   | inactive |  |  |  |

| PSMCxC     | 2H              | inactive                       | inactive | inactive   | active   | active   | inactive | inactive |  |  |  |

| PSMCxD     | 2L              | inactive                       | active   | inactive   | inactive | inactive | inactive | active   |  |  |  |

| PSMCxE     | 3H              | inactive                       | inactive | inactive   | inactive | inactive | active   | active   |  |  |  |

| PSMCxF     | 3L              | inactive                       | inactive | active     | active   | inactive | inactive | inactive |  |  |  |

#### TABLE 26-2: 3-PHASE STEERING CONTROL

**Note 1:** Steering for any value other than those shown will default to the output combination of the Least Significant steering bit that is set.

#### High/Low Side Modulation Enable

It is also possible to enable the PWM output on the low side or high side drive independently using the PxLSMEN and PXHSMEN bits of the PSMC Steering Control 1 (PSMCxSTR1) register (Register 26-33).

When the PxHSMEN bit is set, the active-high side output listed in Table 26-2 is modulated using the normal rising edge and falling edge events.

When the PxLSMEN bit is set, the active-low side output listed in Table 26-2 is modulated using the normal rising edge and falling edge events.

When both the PxHSMEN and PxLSMEN bits are cleared, the active outputs listed in Table 26-2 go immediately to the rising edge event states and do not change.

#### Rising Edge Event

- Active outputs are set to their active states

- Falling Edge Event

- · Active outputs are set to their inactive state

#### 28.1 EUSART Asynchronous Mode

The EUSART transmits and receives data using the standard non-return-to-zero (NRZ) format. NRZ is implemented with two levels: a VOH mark state which represents a '1' data bit, and a VOL space state which represents a '0' data bit. NRZ refers to the fact that consecutively transmitted data bits of the same value stay at the output level of that bit without returning to a neutral level between each bit transmission. An NRZ transmission port idles in the Mark state. Each character transmission consists of one Start bit followed by eight or nine data bits and is always terminated by one or more Stop bits. The Start bit is always a space and the Stop bits are always marks. The most common data format is eight bits. Each transmitted bit persists for a period of 1/(Baud Rate). An on-chip dedicated 8-bit/16-bit Baud Rate Generator is used to derive standard baud rate frequencies from the system oscillator. See Table 28-5 for examples of baud rate configurations.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent, but share the same data format and baud rate. Parity is not supported by the hardware, but can be implemented in software and stored as the ninth data bit.

#### 28.1.1 EUSART ASYNCHRONOUS TRANSMITTER

The EUSART transmitter block diagram is shown in Figure 28-1. The heart of the transmitter is the serial Transmit Shift Register (TSR), which is not directly accessible by software. The TSR obtains its data from the transmit buffer, which is the TXREG register.

#### 28.1.1.1 Enabling the Transmitter

The EUSART transmitter is enabled for asynchronous operations by configuring the following three control bits:

- TXEN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the TXEN bit of the TXSTA register enables the transmitter circuitry of the EUSART. Clearing the SYNC bit of the TXSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the EUSART and automatically configures the TX/CK I/O pin as an output. If the TX/CK pin is shared with an analog peripheral, the analog I/O function must be disabled by clearing the corresponding ANSEL bit.

Note: The TXIF Transmitter Interrupt flag is set when the TXEN enable bit is set.

#### 28.1.1.2 Transmitting Data

A transmission is initiated by writing a character to the TXREG register. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXREG is immediately transferred to the TSR register. If the TSR still contains all or part of a previous character, the new character data is held in the TXREG until the Stop bit of the previous character has been transmitted. The pending character in the TXREG is then transferred to the TSR in one TCY immediately following the Stop bit sequence commences immediately following the transfer of the data to the TSR from the TXREG.

#### 28.1.1.3 Transmit Data Polarity

The polarity of the transmit data can be controlled with the SCKP bit of the BAUDxCON register. The default state of this bit is '0' which selects high true transmit idle and data bits. Setting the SCKP bit to '1' will invert the transmit data resulting in low true idle and data bits. The SCKP bit controls transmit data polarity in Asynchronous mode only. In Synchronous mode, the SCKP bit has a different function. See **Section 28.5.1.2 "Clock Polarity"**.

#### 28.1.1.4 Transmit Interrupt Flag

The TXIF interrupt flag bit of the PIR1 register is set whenever the EUSART transmitter is enabled and no character is being held for transmission in the TXREG. In other words, the TXIF bit is only clear when the TSR is busy with a character and a new character has been queued for transmission in the TXREG. The TXIF flag bit is not cleared immediately upon writing TXREG. TXIF becomes valid in the second instruction cycle following the write execution. Polling TXIF immediately following the TXREG write will return invalid results. The TXIF bit is read-only, it cannot be set or cleared by software.

The TXIF interrupt can be enabled by setting the TXIE interrupt enable bit of the PIE1 register. However, the TXIF flag bit will be set whenever the TXREG is empty, regardless of the state of TXIE enable bit.

To use interrupts when transmitting data, set the TXIE bit only when there is more data to send. Clear the TXIE interrupt enable bit upon writing the last character of the transmission to the TXREG.

#### 28.2 Clock Accuracy with Asynchronous Operation

The factory calibrates the internal oscillator block output (INTOSC). However, the INTOSC frequency may drift as VDD or temperature changes, and this directly affects the asynchronous baud rate. Two methods may be used to adjust the baud rate clock, but both require a reference clock source of some kind.

The first (preferred) method uses the OSCTUNE register to adjust the INTOSC output. Adjusting the value in the OSCTUNE register allows for fine resolution changes to the system clock source. See **Section 6.2.2** "Internal Clock Sources" for more information.

The other method adjusts the value in the Baud Rate Generator. This can be done automatically with the Auto-Baud Detect feature (see **Section 28.4.1** "**Auto-Baud Detect**"). There may not be fine enough resolution when adjusting the Baud Rate Generator to compensate for a gradual change in the peripheral clock frequency.

|        | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |            |                             |                   |            |                             |                |            |                             |                |            |                             |

|--------|------------------------------------------------------|------------|-----------------------------|-------------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fosc = 32.000 MHz                                    |            | Fosc                        | Fosc = 20.000 MHz |            | Fosc = 18.432 MHz           |                |            | Fosc = 11.0592 MHz          |                |            |                             |

| RATE   | Actual<br>Rate                                       | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0                                                | 0.00       | 26666                       | 300.0             | 0.00       | 16665                       | 300.0          | 0.00       | 15359                       | 300.0          | 0.00       | 9215                        |

| 1200   | 1200                                                 | 0.00       | 6666                        | 1200              | -0.01      | 4166                        | 1200           | 0.00       | 3839                        | 1200           | 0.00       | 2303                        |

| 2400   | 2400                                                 | 0.01       | 3332                        | 2400              | 0.02       | 2082                        | 2400           | 0.00       | 1919                        | 2400           | 0.00       | 1151                        |

| 9600   | 9604                                                 | 0.04       | 832                         | 9597              | -0.03      | 520                         | 9600           | 0.00       | 479                         | 9600           | 0.00       | 287                         |

| 10417  | 10417                                                | 0.00       | 767                         | 10417             | 0.00       | 479                         | 10425          | 0.08       | 441                         | 10433          | 0.16       | 264                         |

| 19.2k  | 19.18k                                               | -0.08      | 416                         | 19.23k            | 0.16       | 259                         | 19.20k         | 0.00       | 239                         | 19.20k         | 0.00       | 143                         |

| 57.6k  | 57.55k                                               | -0.08      | 138                         | 57.47k            | -0.22      | 86                          | 57.60k         | 0.00       | 79                          | 57.60k         | 0.00       | 47                          |

| 115.2k | 115.9k                                               | 0.64       | 68                          | 116.3k            | 0.94       | 42                          | 115.2k         | 0.00       | 39                          | 115.2k         | 0.00       | 23                          |

### TABLE 28-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|        |                  |            |                             | SYNC = 0         | , BRGH     | = 1, BRG16                  | = 1 or SY      | ′NC = 1,   | BRG16 = 1                   |                |            |                             |

|--------|------------------|------------|-----------------------------|------------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fosc = 8.000 MHz |            | Fos                         | Fosc = 4.000 MHz |            | Fosc = 3.6864 MHz           |                |            | Fosc = 1.000 MHz            |                |            |                             |

| RATE   | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0            | 0.00       | 6666                        | 300.0            | 0.01       | 3332                        | 300.0          | 0.00       | 3071                        | 300.1          | 0.04       | 832                         |

| 1200   | 1200             | -0.02      | 1666                        | 1200             | 0.04       | 832                         | 1200           | 0.00       | 767                         | 1202           | 0.16       | 207                         |

| 2400   | 2401             | 0.04       | 832                         | 2398             | 0.08       | 416                         | 2400           | 0.00       | 383                         | 2404           | 0.16       | 103                         |

| 9600   | 9615             | 0.16       | 207                         | 9615             | 0.16       | 103                         | 9600           | 0.00       | 95                          | 9615           | 0.16       | 25                          |

| 10417  | 10417            | 0          | 191                         | 10417            | 0.00       | 95                          | 10473          | 0.53       | 87                          | 10417          | 0.00       | 23                          |

| 19.2k  | 19.23k           | 0.16       | 103                         | 19.23k           | 0.16       | 51                          | 19.20k         | 0.00       | 47                          | 19.23k         | 0.16       | 12                          |

| 57.6k  | 57.14k           | -0.79      | 34                          | 58.82k           | 2.12       | 16                          | 57.60k         | 0.00       | 15                          | —              | _          | _                           |

| 115.2k | 117.6k           | 2.12       | 16                          | 111.1k           | -3.55      | 8                           | 115.2k         | 0.00       | 7                           | _              | _          | _                           |

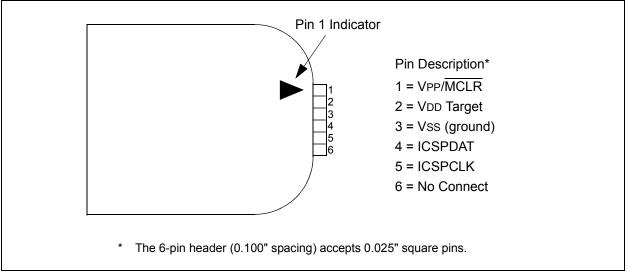

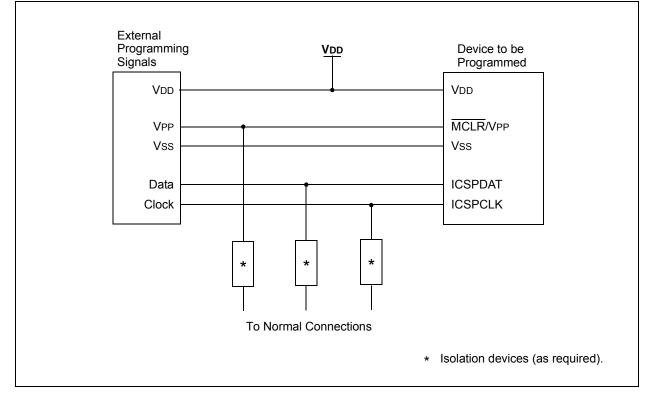

#### FIGURE 29-3: TYPICAL CONNECTION FOR ICSP™ PROGRAMMING

| PIC16LF1                     | 788/9                   |                                  | Operating Conditions: (unless otherwise stated)<br>Low-Power Sleep Mode |       |        |       |            |                                 |  |  |  |  |

|------------------------------|-------------------------|----------------------------------|-------------------------------------------------------------------------|-------|--------|-------|------------|---------------------------------|--|--|--|--|

| PIC16F17                     | /88/9                   | Low-Power Sleep Mode, VREGPM = 1 |                                                                         |       |        |       |            |                                 |  |  |  |  |

| Param Device Characteristics |                         | Min                              | r                                                                       | Max.  | Max.   | Unite | Conditions |                                 |  |  |  |  |

| No.                          | Device Characteristics  | Min.                             | Ain. Typ†                                                               | +85°C | +125°C | Units | Vdd        | Note                            |  |  |  |  |

|                              | Power-down Base Current | (IPD) <sup>(2)</sup>             |                                                                         |       |        |       |            |                                 |  |  |  |  |

| D029                         |                         | _                                | 0.05                                                                    | 2     | 9      | μA    | 1.8        | ADC Current (Note 3),           |  |  |  |  |

|                              |                         | — 0.08                           |                                                                         | 3     | 10     | μA    | 3.0        | no conversion in progress       |  |  |  |  |

| D029                         |                         | —                                | 0.3                                                                     | 4     | 12     | μA    | 2.3        | ADC Current (Note 3),           |  |  |  |  |

|                              |                         | _                                | 0.4                                                                     | 5     | 13     | μA    | 3.0        | no conversion in progress       |  |  |  |  |

|                              |                         | —                                | 0.5                                                                     | 7     | 16     | μA    | 5.0        |                                 |  |  |  |  |

| D030                         |                         | _                                | 250                                                                     | —     | —      | μA    | 1.8        | ADC Current (Note 3),           |  |  |  |  |

|                              |                         | —                                | 280                                                                     | —     | —      | μA    | 3.0        | conversion in progress          |  |  |  |  |

| D030                         |                         |                                  | 230                                                                     | —     | —      | μA    | 2.3        | ADC Current (Note 3, Note 4,    |  |  |  |  |

|                              |                         |                                  | 250                                                                     | —     | —      | μA    | 3.0        | Note 5), conversion in progress |  |  |  |  |

|                              |                         |                                  | 350                                                                     | —     | —      | μA    | 5.0        |                                 |  |  |  |  |

| D031                         |                         | —                                | 250                                                                     | 650   | —      | μA    | 3.0        | Op Amp (High power)             |  |  |  |  |

| D031                         |                         |                                  | 250                                                                     | 650   | _      | μA    | 3.0        | Op Amp (High power) (Note 5)    |  |  |  |  |

|                              |                         | —                                | 350                                                                     | 850   | _      | μA    | 5.0        |                                 |  |  |  |  |

| D032                         |                         |                                  | 250                                                                     | 650   | _      | μA    | 1.8        | Comparator, Normal-Power mode   |  |  |  |  |

|                              |                         | —                                | 300                                                                     | 700   | —      | μA    | 3.0        |                                 |  |  |  |  |

| D032                         |                         |                                  | 280                                                                     | 650   | —      | μA    | 2.3        | Comparator, Normal-Power mode   |  |  |  |  |

|                              |                         |                                  | 300                                                                     | 700   | —      | μA    | 3.0        | (Note 5)                        |  |  |  |  |

|                              |                         | —                                | 310                                                                     | 700   | —      | μA    | 5.0        |                                 |  |  |  |  |

#### TABLE 31-3: POWER-DOWN CURRENTS (IPD)<sup>(1,2,4)</sup> (CONTINUED)

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IPD and the additional current consumed when this peripheral is enabled. The peripheral △ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to Vss.

**3:** ADC oscillator source is FRC.

4: 0.1  $\mu$ F capacitor on VCAP.

5: VREGPM = 0.

\*

#### TABLE 31-17: 5-BIT DIGITAL-TO-ANALOG CONVERTER (DAC) SPECIFICATIONS

| <b>Operating Conditions:</b> VDD = 3V, Temperature = 25°C (unless otherw |               |

|--------------------------------------------------------------------------|---------------|

|                                                                          | vian stated)  |

| TODEIAUNG CONGINONS. VDD - SV. TEMDEIAIUTE - ZS C TUMESS OMEN            | vise sialeo). |

| oporating    |       |                              |      |        |       |       |          |  |  |  |

|--------------|-------|------------------------------|------|--------|-------|-------|----------|--|--|--|

| Param<br>No. | Sym.  | Characteristics              | Min. | Тур.   | Max.  | Units | Comments |  |  |  |

| DAC01*       | CLSB5 | Step Size                    | _    | VDD/32 | _     | V     |          |  |  |  |

| DAC02*       | CACC5 | Absolute Accuracy            | _    | —      | ± 1/2 | LSb   |          |  |  |  |

| DAC03*       | CR5   | Unit Resistor Value (R)      | _    | 5K     | —     | Ω     |          |  |  |  |

| DAC04*       | CST5  | Settling Time <sup>(2)</sup> |      | _      | 10    | μS    |          |  |  |  |

These parameters are characterized but not tested.

Note 1: See Section 32.0 "DC and AC Characteristics Graphs and Charts" for operating characterization.

2: Settling time measured while DACR<7:0> transitions from '00000' to '01111'.

#### TABLE 31-18: 8-BIT DIGITAL-TO-ANALOG CONVERTER (DAC) SPECIFICATIONS

| Operating    | <b>Operating Conditions:</b> VDD = 3V, Temperature = 25°C (unless otherwise stated). |                                  |            |         |       |       |          |  |  |

|--------------|--------------------------------------------------------------------------------------|----------------------------------|------------|---------|-------|-------|----------|--|--|

| Param<br>No. | Sym.                                                                                 | Characteristics                  | Min.       | Тур.    | Max.  | Units | Comments |  |  |

| DAC05*       | CLSB8                                                                                | Step Size                        | —          | VDD/256 | _     | V     |          |  |  |

| DAC06*       | CACC8                                                                                | Absolute Accuracy                |            | —       | ± 1.5 | LSb   |          |  |  |

| DAC07*       | CR8                                                                                  | Unit Resistor Value (R)          | _          | 600     | _     | Ω     |          |  |  |

| DAC08*       | CST8                                                                                 | Settling Time <sup>(1)</sup>     |            | _       | 10    | μS    |          |  |  |

| *            | These na                                                                             | rameters are characterized but r | not tastad |         |       |       |          |  |  |

These parameters are characterized but not tested.

Note 1: Settling time measured while DACR<7:0> transitions from ' $0 \times 00$ ' to ' $0 \times FF$ '.

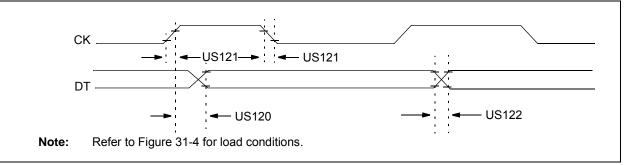

#### FIGURE 31-14: EUSART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

#### TABLE 31-19: EUSART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated) |          |                                   |                |   |      |       |            |  |

|---------------------------------------------------------|----------|-----------------------------------|----------------|---|------|-------|------------|--|

| Param.<br>No.                                           | Symbol   | Characteristic                    | Characteristic |   | Max. | Units | Conditions |  |

| US120                                                   | ТскН2ртV | SYNC XMIT (Master and Slave)      | 3.0-5.5V       | _ | 80   | ns    |            |  |

|                                                         |          | Clock high to data-out valid      | 1.8-5.5V       | — | 100  | ns    |            |  |

| US121                                                   | TCKRF    | Clock out rise time and fall time | 3.0-5.5V       |   | 45   | ns    |            |  |

|                                                         |          | (Master mode)                     | 1.8-5.5V       |   | 50   | ns    |            |  |