Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                               |

| Number of I/O              | 24                                                                        |

| Program Memory Size        | 28KB (16K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 2K x 8                                                                    |

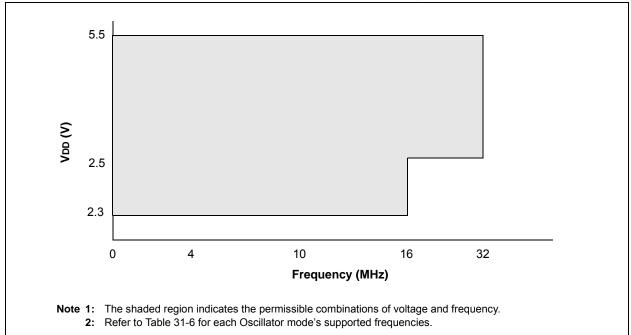

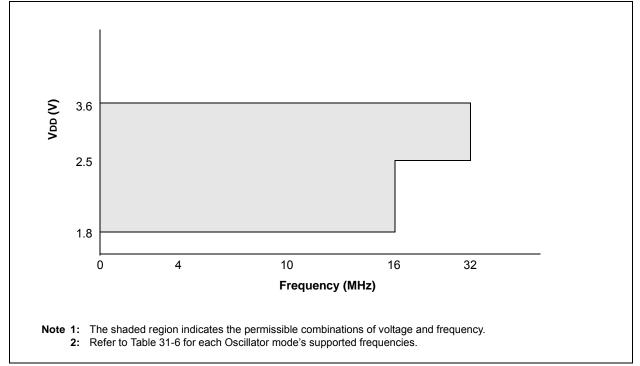

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 11x12b; D/A 1x8b, 3x5b                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1788-i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### REGISTER 4-1: CONFIG1: CONFIGURATION WORD 1 (CONTINUED)

- bit 2-0 FOSC<2:0>: Oscillator Selection bits

- 111 = ECH: External Clock, High-Power mode (4-20 MHz): device clock supplied to CLKIN pin

- 110 = ECM: External Clock, Medium-Power mode (0.5-4 MHz): device clock supplied to CLKIN pin

- 101 = ECL: External Clock, Low-Power mode (0-0.5 MHz): device clock supplied to CLKIN pin

- 100 = INTOSC oscillator: I/O function on CLKIN pin

- 011 = EXTRC oscillator: External RC circuit connected to CLKIN pin

- 010 = HS oscillator: High-speed crystal/resonator connected between OSC1 and OSC2 pins

- 001 = XT oscillator: Crystal/resonator connected between OSC1 and OSC2 pins

- 000 = LP oscillator: Low-power crystal connected between OSC1 and OSC2 pins

- **Note 1:** The entire data EEPROM will be erased when the code protection is turned off during an erase.Once the Data Code Protection bit is enabled, (CPD = 0), the Bulk Erase Program Memory Command (through ICSP) can disable the Data Code Protection (CPD =1). When a Bulk Erase Program Memory Command is executed, the entire Program Flash Memory, Data EEPROM and configuration memory will be erased.

#### 9.3 Register Definitions: Voltage Regulator Control

#### REGISTER 9-1: VREGCON: VOLTAGE REGULATOR CONTROL REGISTER<sup>(1)</sup>

| U-0             | U-0 | U-0           | U-0 | U-0 | U-0             | R/W-0/0 | R/W-1/1  |

|-----------------|-----|---------------|-----|-----|-----------------|---------|----------|

| —               |     | —             | _   | _   | —               | VREGPM  | Reserved |

| bit 7           |     |               |     |     |                 |         | bit 0    |

|                 |     |               |     |     |                 |         |          |

| Legend:         |     |               |     |     |                 |         |          |

| R = Readable bi | +   | M = M/ritable | hit |     | monted hit read | ae 'O'  |          |

| -                    |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-2 Unimplemented: Read as '0'

bit 1 VREGPM: Voltage Regulator Power Mode Selection bit

- 1 = Low-Power Sleep mode enabled in Sleep<sup>(2)</sup> Draws lowest current in Sleep, slower wake-up

- Normal-Power mode enabled in Sleep<sup>(2)</sup>

Draws higher current in Sleep, faster wake-up

- bit 0 Reserved: Read as '1'. Maintain this bit set.

Note 1: "F" devices only.

2: See Section 31.0 "Electrical Specifications".

| Name    | Bit 7    | Bit 6          | Bit 5         | Bit 4    | Bit 3         | Bit 2        | Bit 1    | Bit 0    | Register on<br>Page |  |  |

|---------|----------|----------------|---------------|----------|---------------|--------------|----------|----------|---------------------|--|--|

| INTCON  | GIE      | PEIE           | TMR0IE        | INTE     | IOCIE         | TMR0IF       | INTF     | RAIF     | 97                  |  |  |

| IOCBF   | IOCBF7   | IOCBF6         | IOCBF5        | IOCBF4   | IOCBF3        | IOCBF2       | IOCBF1   | IOCBF0   | 164                 |  |  |

| IOCBN   | IOCBN7   | IOCBN6         | IOCBN5        | IOCBN4   | IOCBN3        | IOCBN2       | IOCBN1   | IOCBN0   | 163                 |  |  |

| IOCBP   | IOCBP7   | IOCBP6         | IOCBP5        | IOCBP4   | IOCBP3        | IOCBP2       | IOCBP1   | IOCBP0   | 163                 |  |  |

| PIE1    | TMR1GIE  | ADIE           | RCIE          | TXIE     | SSP1IE        | CCP1IE       | TMR2IE   | TMR1IE   | 98                  |  |  |

| PIE2    | OSFIE    | C2IE           | C1IE          | EEIE     | BCL1IE        | C4IE         | C3IE     | CCP2IE   | 99                  |  |  |

| PIE3    | _        | —              | _             | CCP3IE   | —             | —            | _        | —        | 100                 |  |  |

| PIE4    | PSMC4TIE | PSMC3TIE       | PSMC2TIE      | PSMC1TIE | PSMC4SIE      | PSMC3SIE     | PSMC2SIE | PSMC1SIE | 101                 |  |  |

| PIR1    | TMR1GIF  | ADIF           | RCIF          | TXIF     | SSP1IF        | CCP1IF       | TMR2IF   | TMR1IF   | 98                  |  |  |

| PIR2    | OSFIF    | C2IF           | C1IF          | EEIF     | BCL1IF        | C4IF         | C3IF     | CCP2IF   | 103                 |  |  |

| PIR3    | _        | —              | _             | CCP3IF   | —             | —            | _        | —        | 104                 |  |  |

| PIR4    | PSMC4TIF | PSMC3TIF       | PSMC2TIF      | PSMC1TIF | PSMC4SIF      | PSMC3SIF     | PSMC2SIF | PSMC1SIF | 105                 |  |  |

| STATUS  | _        | —              | _             | TO       | PD            | Z            | DC       | С        | 31                  |  |  |

| VREGCON | —        | —              | —             | _        | —             | —            | VREGPM   | Reserved | 110                 |  |  |

| WDTCON  | _        | _              |               |          | WDTPS<4:0>    |              |          | SWDTEN   | 114                 |  |  |

| Logondi |          | مناهمها امماهم | n road on 'o' |          | and making ad | In Davis Dav |          |          |                     |  |  |

#### TABLE 9-1: SUMMARY OF REGISTERS ASSOCIATED WITH POWER-DOWN MODE

Legend: — = unimplemented location, read as '0'. Shaded cells are not used in Power-Down mode.

| Name   | Bit 7  | Bit 6 | Bit 5     | Bit 4 | Bit 3     | Bit 2 | Bit 1    | Bit 0  | Register<br>on Page |

|--------|--------|-------|-----------|-------|-----------|-------|----------|--------|---------------------|

| OSCCON | SPLLEN |       | IRCF<3:0> |       |           | —     | SCS<1:0> |        | 86                  |

| STATUS | —      | _     | —         | TO    | PD        | Z     | DC       | С      | 31                  |

| WDTCON |        |       |           | ١     | VDTPS<4:0 | >     |          | SWDTEN | 114                 |

#### TABLE 11-3: SUMMARY OF REGISTERS ASSOCIATED WITH WATCHDOG TIMER

**Legend:** x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by Watchdog Timer.

#### TABLE 11-4: SUMMARY OF CONFIGURATION WORD WITH WATCHDOG TIMER

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2   | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|------------|---------|---------|---------------------|

|         | 13:8 | _       | _       | FCMEN    | IESO     | CLKOUTEN | BOREN<1:0> |         | CPD     | 58                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDTE     | E<1:0>   | FOSC<2:0>  |         |         | 00                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Watchdog Timer.

#### 13.1 Alternate Pin Function

The Alternate Pin Function Control (APFCON1 and APFCON2) registers are used to steer specific peripheral input and output functions between different pins. The APFCON1 and APFCON2 registers are shown in Register 13-1 and Register 13-2. For this device family, the following functions can be moved between different pins.

- C2OUT output

- CCP1 output

- SDO output

- · SCL/SCK output

- SDA/SDI output

- TX/RX output

- CCP2 output

- CCP3 output

- SS input

These bits have no effect on the values of any TRIS register. PORT and TRIS overrides will be routed to the correct pin. The unselected pin will be unaffected.

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u        | R/W-x/u      |

|------------------|---------|-------------------|---------|----------------|------------------|----------------|--------------|

|                  |         |                   | AD<     | 11:4>          |                  |                |              |

| bit 7            |         |                   |         |                |                  |                | bit 0        |

|                  |         |                   |         |                |                  |                |              |

| Legend:          |         |                   |         |                |                  |                |              |

| R = Readable     | bit     | W = Writable t    | oit     | U = Unimpler   | nented bit, read | d as '0'       |              |

| u = Bit is unch  | anged   | x = Bit is unkn   | own     | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                |              |

#### **REGISTER 17-4:** ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 0

bit 7-0 AD<11:4>: ADC Result Register bits Upper eight bits of 12-bit conversion result

#### **REGISTER 17-5:** ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 0

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         | AD<     | 3:0>    |         | —       | —       | —       | ADSIGN  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 AD<3:0>: ADC Result Register bits Lower four bits of 12-bit conversion result

bit 3-1 Extended LSb bits: These are cleared to zero by DC conversion.

bit 0 ADSIGN: ADC Result Sign bit

#### **18.4** Register Definitions: Op Amp Control

#### REGISTER 18-1: OPAxCON: OPERATIONAL AMPLIFIERS (OPAx) CONTROL REGISTERS

| R/W-0/0                           | R/W-0/0                                           | U-0               | U-0            | U-0          | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |  |  |

|-----------------------------------|---------------------------------------------------|-------------------|----------------|--------------|------------------|------------------|--------------|--|--|--|

| OPAxEN                            | OPAxSP                                            |                   | —              | _            |                  | OPAxCH<2:0>      |              |  |  |  |

| bit 7                             |                                                   |                   |                |              | ·                |                  | bit 0        |  |  |  |

|                                   |                                                   |                   |                |              |                  |                  |              |  |  |  |

| Legend:                           |                                                   |                   |                |              |                  |                  |              |  |  |  |

| R = Readable bit W = Writable bit |                                                   |                   |                | U = Unimpler | mented bit, read | l as '0'         |              |  |  |  |

| u = Bit is unch                   | anged                                             | x = Bit is unkr   | nown           | -n/n = Value | at POR and BO    | R/Value at all c | other Resets |  |  |  |

| '1' = Bit is set                  |                                                   | '0' = Bit is clea | ared           | q = Value de | pends on condit  | ion              |              |  |  |  |

|                                   |                                                   |                   |                |              |                  |                  |              |  |  |  |

| bit 7                             | OPAxEN: Op                                        | Amp Enable b      | it             |              |                  |                  |              |  |  |  |

|                                   | 1 = Op amp i                                      |                   |                |              |                  |                  |              |  |  |  |

|                                   | 0 = Op amp i                                      | s disabled and    | consumes no    | active power |                  |                  |              |  |  |  |

| bit 6                             | OPAxSP: Op                                        | Amp Speed/Po      | ower Select bi | it           |                  |                  |              |  |  |  |

|                                   |                                                   | tor operates in   | high GBWP m    | node         |                  |                  |              |  |  |  |

|                                   | 0 = Reserved                                      | I. Do not use.    |                |              |                  |                  |              |  |  |  |

| bit 5-3                           | Unimplemen                                        | ted: Read as '    | D'             |              |                  |                  |              |  |  |  |

| bit 2-0                           | OPAxCH<2:0>: Non-inverting Channel Selection bits |                   |                |              |                  |                  |              |  |  |  |

|                                   | $111 = Non_{-in}$                                 | verting input co  | nnects to DA   |              |                  |                  |              |  |  |  |

- 111 = Non-inverting input connects to DAC4\_output

- 110 = Non-inverting input connects to DAC3\_output

- 101 = Non-inverting input connects to DAC2\_output

- 100 = Non-inverting input connects to DAC1\_output

- 011 = Non-inverting input connects to FVR Buffer 2 output

- 010 = Reserved do not use

- 001 = Reserved do not use

- 000 = Non-inverting input connects to OPAxIN+ pin

| Name                   | Bit 7         | Bit 6      | Bit 5   | Bit 4   | Bit 3  | Bit 2   | Bit 1  | Bit 0   | Register<br>on Page |  |

|------------------------|---------------|------------|---------|---------|--------|---------|--------|---------|---------------------|--|

| ANSELA                 | ANSA7         | _          | ANSA5   | ANSA4   | ANSA3  | ANSA2   | ANSA1  | ANSA0   | 137                 |  |

| ANSELB                 | —             | ANSB6      | ANSB5   | ANSB4   | ANSB3  | ANSB2   | ANSB1  | ANSB0   | 143                 |  |

| DAC1CON0               | DAC1EN        | _          | DAC10E1 | DAC10E2 | DAC1PS | SS<1:0> | _      | 192     |                     |  |

| DAC1CON1               |               | DAC1R<7:0> |         |         |        |         |        |         |                     |  |

| OPA1CON                | OPA1EN        | OPA1SP     | —       | _       | _      | —       | OPA1P0 | CH<1:0> | 187                 |  |

| OPA2CON                | OPA2EN        | OPA2SP     | —       | _       | _      | —       | OPA2P0 | CH<1:0> | 187                 |  |

| OPA3CON <sup>(1)</sup> | <b>OPA3EN</b> | OPA3SP     | —       | _       | _      | —       | OPA3P0 | CH<1:0> | 187                 |  |

| TRISA                  | TRISA7        | TRISA6     | TRISA5  | TRISA4  | TRISA3 | TRISA2  | TRISA1 | TRISA0  | 136                 |  |

| TRISB                  | TRISB7        | TRISB6     | TRISB5  | TRISB4  | TRISB3 | TRISB2  | TRISB1 | TRISB0  | 142                 |  |

| TRISC                  | TRISC7        | TRISC6     | TRISC5  | TRISC4  | TRISC3 | TRISC2  | TRISC1 | TRISC0  | 147                 |  |

#### TABLE 18-1: SUMMARY OF REGISTERS ASSOCIATED WITH OP AMPS

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by op amps.

**Note 1:** PIC16(L)F1789 only

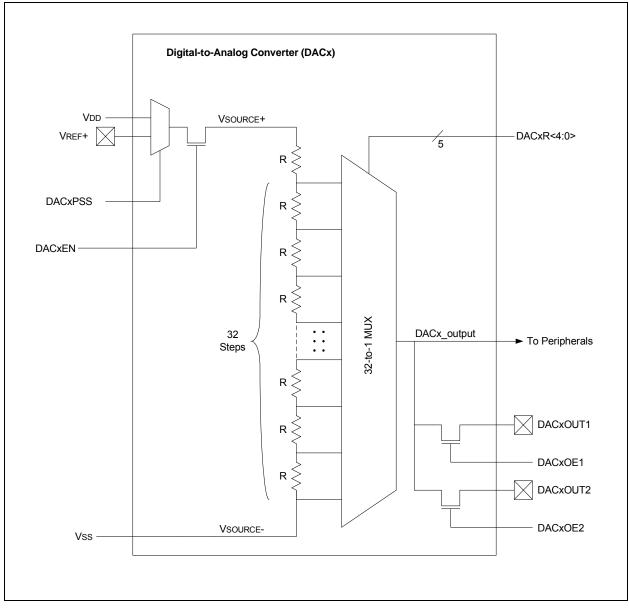

#### FIGURE 20-1: DIGITAL-TO-ANALOG CONVERTER BLOCK DIAGRAM

| R/W-0/0         | R/W-0/0                                                                                                                                                      | R/W-0/0                                                                                                                                            | U-0          | U-0               | U-0                | U-0            | R/W-0/0           |  |  |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------|--------------------|----------------|-------------------|--|--|--|

| PxASE           | PxASDEN                                                                                                                                                      | PxARSEN                                                                                                                                            | —            | —                 | _                  | _              | PxASDOV           |  |  |  |

| bit 7           | ·                                                                                                                                                            | •                                                                                                                                                  |              |                   |                    |                | bit 0             |  |  |  |

|                 |                                                                                                                                                              |                                                                                                                                                    |              |                   |                    |                |                   |  |  |  |

| Legend:         |                                                                                                                                                              |                                                                                                                                                    |              |                   |                    |                |                   |  |  |  |

| R = Readab      |                                                                                                                                                              | W = Writable                                                                                                                                       |              | •                 | nented bit, read   |                |                   |  |  |  |

| u = Bit is un   | changed                                                                                                                                                      | x = Bit is unkr                                                                                                                                    | Iown         | -n/n = Value a    | at POR and BOP     | R/Value at all | other Resets      |  |  |  |

| '1' = Bit is se | et                                                                                                                                                           | '0' = Bit is clea                                                                                                                                  | ared         |                   |                    |                |                   |  |  |  |

|                 |                                                                                                                                                              |                                                                                                                                                    |              | (4)               |                    |                |                   |  |  |  |

| bit 7           |                                                                                                                                                              | M Auto-Shutdov                                                                                                                                     |              |                   |                    |                |                   |  |  |  |

|                 | <ul> <li>1 = A shutdown event has occurred, PWM outputs are inactive and in their shutdown states</li> <li>0 = PWM outputs are operating normally</li> </ul> |                                                                                                                                                    |              |                   |                    |                |                   |  |  |  |

|                 |                                                                                                                                                              |                                                                                                                                                    | 0            | <b>,</b>          |                    |                |                   |  |  |  |

| bit 6           |                                                                                                                                                              | <b>PxASDEN:</b> PWM Auto-Shutdown Enable bit<br>1 = Auto-shutdown is enabled. If any of the sources in PSMCxASDS assert a logic '1', then the out- |              |                   |                    |                |                   |  |  |  |

|                 |                                                                                                                                                              |                                                                                                                                                    |              |                   |                    |                | 1', then the out- |  |  |  |

|                 |                                                                                                                                                              | ll go into their au<br>nutdown is disab                                                                                                            |              | state and PSIV    | ICXSIF liag will i | Je sel.        |                   |  |  |  |

| bit 5           |                                                                                                                                                              | PWM Auto-Rest                                                                                                                                      |              |                   |                    |                |                   |  |  |  |

| bit o           |                                                                                                                                                              | estarts automati                                                                                                                                   |              |                   | ndition is remove  | ed             |                   |  |  |  |

|                 |                                                                                                                                                              | ASE bit must be                                                                                                                                    |              |                   |                    |                | wn condition is   |  |  |  |

|                 | cleared                                                                                                                                                      | l.                                                                                                                                                 |              |                   |                    |                |                   |  |  |  |

| bit 4-1         | Unimpleme                                                                                                                                                    | nted: Read as '                                                                                                                                    | )'           |                   |                    |                |                   |  |  |  |

| bit 0           | PxASDOV:                                                                                                                                                     | PWM Auto-Shut                                                                                                                                      | down Overrid | e bit             |                    |                |                   |  |  |  |

|                 | PxASDEN =                                                                                                                                                    | <u>1:</u>                                                                                                                                          |              |                   |                    |                |                   |  |  |  |

|                 |                                                                                                                                                              | PxASDL[n] level                                                                                                                                    |              |                   | out causing a P    | SMCxSIF inte   | errupt            |  |  |  |

|                 | 0 = Norma                                                                                                                                                    | PWM and auto                                                                                                                                       | -shutdown ex | ecution           |                    |                |                   |  |  |  |

|                 | <u>PxASDEN =</u><br>No effect                                                                                                                                | 0:                                                                                                                                                 |              |                   |                    |                |                   |  |  |  |

|                 | NU ellect                                                                                                                                                    |                                                                                                                                                    |              |                   |                    |                |                   |  |  |  |

|                 | ASE bit may be                                                                                                                                               | set in software.                                                                                                                                   | When this oc | curs the function | onality is the san | ne as that cau | used by           |  |  |  |

| h               | ardware.                                                                                                                                                     |                                                                                                                                                    |              |                   |                    |                |                   |  |  |  |

#### REGISTER 26-16: PSMCxASDC: PSMC AUTO-SHUTDOWN CONTROL REGISTER

#### REGISTER 26-21: PSMCxPHL: PSMC PHASE COUNT LOW BYTE REGISTER

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|-------------|

|                  |         |                   | PSMCx   | PHL<7:0>       |                  |                  |             |

| bit 7            |         |                   |         |                |                  |                  | bit 0       |

|                  |         |                   |         |                |                  |                  |             |

| Legend:          |         |                   |         |                |                  |                  |             |

| R = Readable     | bit     | W = Writable      | bit     | U = Unimpler   | nented bit, read | as '0'           |             |

| u = Bit is unch  | anged   | x = Bit is unkr   | nown    | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                  |             |

bit 7-0

**—**

**PSMCxPHL<7:0>:** 16-bit Phase Count Least Significant bits = PSMCxPH<7:0>

REGISTER 26-22: PSMCxPHH: PSMC PHASE COUNT HIGH BYTE REGISTER

# R/W-0/0 <t

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **PSMCxPHH<7:0>:** 16-bit Phase Count Most Significant bits

= PSMCxPH<15:8>

#### 27.2 SPI Mode Overview

The Serial Peripheral Interface (SPI) bus is a synchronous serial data communication bus that operates in Full-Duplex mode. Devices communicate in a master/slave environment where the master device initiates the communication. A slave device is controlled through a Chip Select known as Slave Select.

The SPI bus specifies four signal connections:

- Serial Clock (SCK)

- Serial Data Out (SDO)

- Serial Data In (SDI)

- Slave Select (SS)

Figure 27-1 shows the block diagram of the MSSP module when operating in SPI mode.

The SPI bus operates with a single master device and one or more slave devices. When multiple slave devices are used, an independent Slave Select connection is required from the master device to each slave device.

Figure 27-4 shows a typical connection between a master device and multiple slave devices.

The master selects only one slave at a time. Most slave devices have tri-state outputs so their output signal appears disconnected from the bus when they are not selected.

Transmissions involve two shift registers, eight bits in size, one in the master and one in the slave. With either the master or the slave device, data is always shifted out one bit at a time, with the Most Significant bit (MSb) shifted out first. At the same time, a new Least Significant bit (LSb) is shifted into the same register.

Figure 27-5 shows a typical connection between two processors configured as master and slave devices.

Data is shifted out of both shift registers on the programmed clock edge and latched on the opposite edge of the clock.

The master device transmits information out on its SDO output pin which is connected to, and received by, the slave's SDI input pin. The slave device transmits information out on its SDO output pin, which is connected to, and received by, the master's SDI input pin.

To begin communication, the master device first sends out the clock signal. Both the master and the slave devices should be configured for the same clock polarity.

The master device starts a transmission by sending out the MSb from its shift register. The slave device reads this bit from that same line and saves it into the LSb position of its shift register. During each SPI clock cycle, a full-duplex data transmission occurs. This means that while the master device is sending out the MSb from its shift register (on its SDO pin) and the slave device is reading this bit and saving it as the LSb of its shift register, that the slave device is also sending out the MSb from its shift register (on its SDO pin) and the master device is reading this bit and saving it as the LSb of its shift register.

After eight bits have been shifted out, the master and slave have exchanged register values.

If there is more data to exchange, the shift registers are loaded with new data and the process repeats itself.

Whether the data is meaningful or not (dummy data), depends on the application software. This leads to three scenarios for data transmission:

- Master sends useful data and slave sends dummy data.

- Master sends useful data and slave sends useful data.

- Master sends dummy data and slave sends useful data.

Transmissions may involve any number of clock cycles. When there is no more data to be transmitted, the master stops sending the clock signal and it deselects the slave.

Every slave device connected to the bus that has not been selected through its slave select line must disregard the clock and transmission signals and must not transmit out any data of its own.

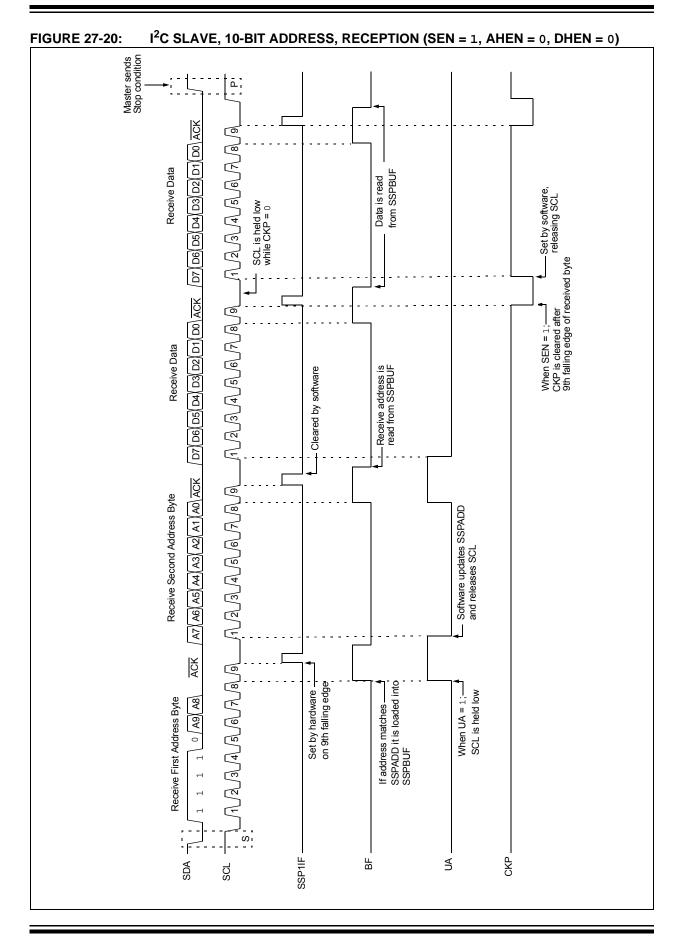

#### 27.5.4 SLAVE MODE 10-BIT ADDRESS RECEPTION

This section describes a standard sequence of events for the MSSP module configured as an  $I^2C$  slave in 10-bit Addressing mode.

Figure 27-19 is used as a visual reference for this description.

This is a step by step process of what must be done by slave software to accomplish  $I^2C$  communication.

- 1. Bus starts Idle.

- Master sends Start condition; S bit of SSPSTAT is set; SSP1IF is set if interrupt on Start detect is enabled.

- 3. Master sends matching high address with R/W bit clear; UA bit of the SSPSTAT register is set.

- 4. Slave sends ACK and SSP1IF is set.

- 5. Software clears the SSP1IF bit.

- 6. Software reads received address from SSPBUF clearing the BF flag.

- 7. Slave loads low address into SSPADD, releasing SCL.

- 8. Master sends matching low address byte to the slave; UA bit is set.

**Note:** Updates to the SSPADD register are not allowed until after the ACK sequence.

- 9. Slave sends ACK and SSP1IF is set.

- **Note:** If the low address does not match, SSP1IF and UA are still set so that the slave software can set SSPADD back to the high address. BF is not set because there is no match. CKP is unaffected.

- 10. Slave clears SSP1IF.

- 11. Slave reads the received matching address from SSPBUF clearing BF.

- 12. Slave loads high address into SSPADD.

- Master clocks a data byte to the slave and clocks out the slaves ACK on the 9th SCL pulse; SSP1IF is set.

- 14. If SEN bit of SSPCON2 is set, CKP is cleared by hardware and the clock is stretched.

- 15. Slave clears SSP1IF.

- 16. Slave reads the received byte from SSPBUF clearing BF.

- 17. If SEN is set the slave sets CKP to release the SCL.

- 18. Steps 13-17 repeat for each received byte.

- 19. Master sends Stop to end the transmission.

### 27.5.5 10-BIT ADDRESSING WITH ADDRESS OR DATA HOLD

Reception using 10-bit addressing with AHEN or DHEN set is the same as with 7-bit modes. The only difference is the need to update the SSPADD register using the UA bit. All functionality, specifically when the CKP bit is cleared and SCL line is held low are the same. Figure 27-20 can be used as a reference of a slave in 10-bit addressing with AHEN set.

Figure 27-21 shows a standard waveform for a slave transmitter in 10-bit Addressing mode.

| R/W-0/0          | R/W-0/0                                                                                                                                            | R/W-0/0                                                                                                        | R/W-0/0         | R/W-0/0        | R-0/0            | R-0/0            | R-0/0        |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------|----------------|------------------|------------------|--------------|--|--|--|--|

| SPEN             | RX9                                                                                                                                                | SREN                                                                                                           | CREN            | ADDEN          | FERR             | OERR             | RX9D         |  |  |  |  |

| bit 7            |                                                                                                                                                    | •                                                                                                              |                 | ·              |                  |                  | bit (        |  |  |  |  |

| Legend:          |                                                                                                                                                    |                                                                                                                |                 |                |                  |                  |              |  |  |  |  |

| R = Readable     | e bit                                                                                                                                              | W = Writable                                                                                                   | bit             | U = Unimplei   | mented bit, read | l as '0'         |              |  |  |  |  |

| u = Bit is unc   | hanged                                                                                                                                             | x = Bit is unk                                                                                                 | nown            | -n/n = Value   | at POR and BO    | R/Value at all c | other Resets |  |  |  |  |

| '1' = Bit is set | t                                                                                                                                                  | '0' = Bit is cle                                                                                               | ared            |                |                  |                  |              |  |  |  |  |

| bit 7            | SPEN: Seria                                                                                                                                        | al Port Enable b                                                                                               | it              |                |                  |                  |              |  |  |  |  |

|                  |                                                                                                                                                    | ort enabled (co<br>ort disabled (he                                                                            |                 | T and TX/CK p  | ins as serial po | rt pins)         |              |  |  |  |  |

| bit 6            | <b>RX9:</b> 9-bit R                                                                                                                                | eceive Enable                                                                                                  | bit             |                |                  |                  |              |  |  |  |  |

|                  |                                                                                                                                                    | 9-bit reception<br>8-bit reception                                                                             |                 |                |                  |                  |              |  |  |  |  |

| bit 5            | SREN: Sing                                                                                                                                         | le Receive Ena                                                                                                 | ble bit         |                |                  |                  |              |  |  |  |  |

|                  | <u>Asynchronou</u>                                                                                                                                 | Asynchronous mode:                                                                                             |                 |                |                  |                  |              |  |  |  |  |

|                  | Don't care<br><u>Synchronous</u>                                                                                                                   | Don't care<br><u>Synchronous mode – Master</u> :                                                               |                 |                |                  |                  |              |  |  |  |  |

|                  | 1 = Enables                                                                                                                                        | 1 = Enables single receive                                                                                     |                 |                |                  |                  |              |  |  |  |  |

|                  |                                                                                                                                                    | 0 = Disables single receive                                                                                    |                 |                |                  |                  |              |  |  |  |  |

|                  |                                                                                                                                                    | This bit is cleared after reception is complete.<br>Synchronous mode – Slave                                   |                 |                |                  |                  |              |  |  |  |  |

|                  | Synchronous mode – Slave<br>Don't care                                                                                                             |                                                                                                                |                 |                |                  |                  |              |  |  |  |  |

| bit 4            |                                                                                                                                                    | CREN: Continuous Receive Enable bit                                                                            |                 |                |                  |                  |              |  |  |  |  |

|                  |                                                                                                                                                    | Asynchronous mode:                                                                                             |                 |                |                  |                  |              |  |  |  |  |

|                  | -                                                                                                                                                  | 1 = Enables receiver                                                                                           |                 |                |                  |                  |              |  |  |  |  |

|                  |                                                                                                                                                    | 0 = Disables receiver                                                                                          |                 |                |                  |                  |              |  |  |  |  |

|                  | -                                                                                                                                                  | Synchronous mode:                                                                                              |                 |                |                  |                  |              |  |  |  |  |

|                  | <ul> <li>1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN)</li> <li>0 = Disables continuous receive</li> </ul> |                                                                                                                |                 |                |                  |                  |              |  |  |  |  |

| bit 3            |                                                                                                                                                    |                                                                                                                |                 |                |                  |                  |              |  |  |  |  |

|                  |                                                                                                                                                    | ADDEN: Address Detect Enable bit<br>Asynchronous mode 9-bit (RX9 = 1):                                         |                 |                |                  |                  |              |  |  |  |  |

|                  | •                                                                                                                                                  | 1 = Enables address detection, enable interrupt and load the receive buffer when RSR<8> is set                 |                 |                |                  |                  |              |  |  |  |  |

|                  |                                                                                                                                                    | <ul> <li>Disables address detection, all bytes are received and ninth bit can be used as parity bit</li> </ul> |                 |                |                  |                  |              |  |  |  |  |

|                  |                                                                                                                                                    | Asynchronous mode 8-bit (RX9 = 0):                                                                             |                 |                |                  |                  |              |  |  |  |  |

|                  | Don't care                                                                                                                                         |                                                                                                                |                 |                |                  |                  |              |  |  |  |  |

| bit 2            |                                                                                                                                                    | FERR: Framing Error bit                                                                                        |                 |                |                  |                  |              |  |  |  |  |

|                  | <ul> <li>1 = Framing error (can be updated by reading RCREG register and receive next valid byte)</li> <li>0 = No framing error</li> </ul>         |                                                                                                                |                 |                |                  |                  |              |  |  |  |  |

| bit 1            | OERR: Over                                                                                                                                         | rrun Error bit                                                                                                 |                 |                |                  |                  |              |  |  |  |  |

|                  | 1 = Overrun<br>0 = No over                                                                                                                         | n error (can be o<br>run error                                                                                 | cleared by clea | iring bit CREN | )                |                  |              |  |  |  |  |

| bit 0            | RX9D: Ninth                                                                                                                                        | bit of Received                                                                                                | d Data          |                |                  |                  |              |  |  |  |  |

|                  |                                                                                                                                                    |                                                                                                                |                 |                |                  |                  |              |  |  |  |  |

#### REGISTER 28-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER

| MOVIW            | Move INDFn to W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVIW ++FSRn<br>[ <i>label</i> ] MOVIWFSRn<br>[ <i>label</i> ] MOVIW FSRn++<br>[ <i>label</i> ] MOVIW FSRn<br>[ <i>label</i> ] MOVIW k[FSRn]                                                                                                                                                                                                                                                                                                                                              |

| Operands:        | $\begin{array}{l} n \in [0,1] \\ mm \in [00,01,10,11] \\ \textbf{-32} \leq k \leq 31 \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                          |

| Operation:       | $\label{eq:interm} \begin{array}{l} \text{INDFn} \rightarrow \text{W} \\ \text{Effective address is determined by} \\ \bullet \ \text{FSR} + 1 \ (\text{preincrement}) \\ \bullet \ \text{FSR} - 1 \ (\text{predecrement}) \\ \bullet \ \text{FSR} + k \ (\text{relative offset}) \\ \text{After the Move, the FSR value will} \\ \text{be either:} \\ \bullet \ \text{FSR} + 1 \ (\text{all increments}) \\ \bullet \ \text{FSR} - 1 \ (\text{all decrements}) \\ \bullet \ \text{Unchanged} \end{array}$ |

| Status Affected: | Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Mode          | Syntax | mm |

|---------------|--------|----|

| Preincrement  | ++FSRn | 00 |

| Predecrement  | FSRn   | 01 |

| Postincrement | FSRn++ | 10 |

| Postdecrement | FSRn   | 11 |

Description:

This instruction is used to move data between W and one of the indirect registers (INDFn). Before/ after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

**Note:** The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h -FFFFh. Incrementing/ decrementing it beyond these bounds will cause it to wraparound.

| MOVLB            | Move literal to BSR                                                  |

|------------------|----------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]MOVLB k                                              |

| Operands:        | $0 \leq k \leq 31$                                                   |

| Operation:       | $k \rightarrow BSR$                                                  |

| Status Affected: | None                                                                 |

| Description:     | The 5-bit literal 'k' is loaded into the Bank Select Register (BSR). |

| MOVLP            | Move literal to PCLATH                                               |

| Syntax:          | [ <i>label</i> ]MOVLP_k                                              |

| Operands:        | $0 \leq k \leq 127$                                                  |

| Operation:       | $k \rightarrow PCLATH$                                               |

|                  |                                                                      |

| Status Affected: | None                                                                 |

| MOVLW            | Move literal to W                                                                         |

|------------------|-------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                  |

| Operands:        | $0 \leq k \leq 255$                                                                       |

| Operation:       | $k \rightarrow (W)$                                                                       |

| Status Affected: | None                                                                                      |

| Description:     | The 8-bit literal 'k' is loaded into W register. The "don't cares" will assemble as '0's. |

| Words:           | 1                                                                                         |

| Cycles:          | 1                                                                                         |

| Example:         | MOVLW 0x5A                                                                                |

|                  | After Instruction<br>W = 0x5A                                                             |

PCLATH register.

| PIC16LF      | 1788/9                                   | Standard Operating Conditions (unless otherwise stated) |      |      |    |            |                                                              |  |

|--------------|------------------------------------------|---------------------------------------------------------|------|------|----|------------|--------------------------------------------------------------|--|

| PIC16F1788/9 |                                          |                                                         |      |      |    |            |                                                              |  |

| Param        | Device                                   | <b>N</b> /1-10                                          |      |      |    | Conditions |                                                              |  |

| No.          | Characteristics Min. Typ† Max. Units VDD |                                                         | Note |      |    |            |                                                              |  |

| D009         | LDO Regulator                            | _                                                       | 75   |      | μA | _          | High Power mode, normal operation                            |  |

|              |                                          | —                                                       | 15   | _    | μA | —          | Sleep VREGCON<1> = 0                                         |  |

|              |                                          | _                                                       | 0.3  | —    | μA | _          | Sleep VREGCON<1> = 1                                         |  |

| D010         |                                          |                                                         | 8    | 20   | μA | 1.8        | Fosc = 32 kHz                                                |  |

|              |                                          | —                                                       | 12   | 24   | μA | 3.0        | LP Oscillator mode (Note 4),<br>-40°C $\leq$ TA $\leq$ +85°C |  |

| D010         |                                          |                                                         | 18   | 63   | μA | 2.3        | Fosc = 32 kHz                                                |  |

|              |                                          |                                                         | 20   | 74   | μA | 3.0        | LP Oscillator mode (Note 4, 5),                              |  |

|              |                                          |                                                         | 22   | 79   | μA | 5.0        | $-$ -40°C $\leq$ TA $\leq$ +85°C                             |  |

| D012         |                                          | _                                                       | 160  | 650  | μA | 1.8        | Fosc = 4 MHz                                                 |  |

|              |                                          | —                                                       | 320  | 1000 | μA | 3.0        | XT Oscillator mode                                           |  |

| D012         |                                          | —                                                       | 260  | 700  | μA | 2.3        | Fosc = 4 MHz                                                 |  |

|              |                                          |                                                         | 330  | 1100 | μA | 3.0        | XT Oscillator mode (Note 5)                                  |  |

|              |                                          | _                                                       | 380  | 1300 | μA | 5.0        |                                                              |  |

#### TABLE 31-2: SUPPLY VOLTAGE (IDD)<sup>(1,2)</sup>

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

**3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in kΩ.

4: FVR and BOR are disabled.

5: 0.1  $\mu$ F capacitor on VCAP.

6: 8 MHz crystal oscillator with 4x PLL enabled.

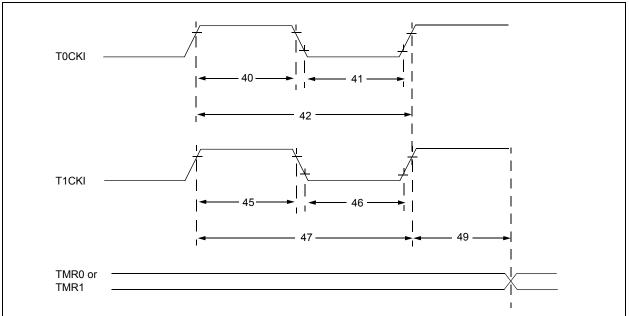

#### FIGURE 31-10: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

| TABLE 31-11: | TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS |

|--------------|-----------------------------------------------|

|--------------|-----------------------------------------------|

| Standa       | rd Operating                              | Conditions (u                       | Inless otherwis                         | e stated)      |                                           |        |        |            |                                    |

|--------------|-------------------------------------------|-------------------------------------|-----------------------------------------|----------------|-------------------------------------------|--------|--------|------------|------------------------------------|

| Param<br>No. | Sym.                                      |                                     | Characteristi                           | Min.           | Тур†                                      | Max.   | Units  | Conditions |                                    |

| 40* TT0H     |                                           | T0CKI High Pulse Width No Prescaler |                                         |                | 0.5 Tcy + 20                              | _      | _      | ns         |                                    |

|              |                                           | With Prescaler                      |                                         | With Prescaler | 10                                        |        |        | ns         |                                    |

| 41*          | T⊤0L                                      | T0CKI Low F                         | Pulse Width                             | No Prescaler   | 0.5 Tcy + 20                              |        |        | ns         |                                    |

|              |                                           |                                     |                                         | With Prescaler | 10                                        |        |        | ns         |                                    |

| 42*          | Тт0Р                                      | T0CKI Period                        | t                                       |                | Greater of:<br>20 or <u>Tcy + 40</u><br>N | —      | —      | ns         | N = prescale value<br>(2, 4,, 256) |

| 45*          | T⊤1H                                      | T1CKI High                          | Synchronous, No Prescaler               |                | 0.5 Tcy + 20                              | _      |        | ns         |                                    |

|              |                                           | Time                                | Synchronous,<br>with Prescaler          |                | 15                                        | —      | _      | ns         |                                    |

|              |                                           |                                     | Asynchronous                            |                | 30                                        |        |        | ns         |                                    |

| 46*          | T⊤1L                                      | T1CKI Low<br>Time                   | Synchronous, No Prescaler               |                | 0.5 Tcy + 20                              |        |        | ns         |                                    |

|              |                                           |                                     | Synchronous, with Prescaler             |                | 15                                        |        | _      | ns         |                                    |

|              |                                           |                                     | Asynchronous                            |                | 30                                        |        | _      | ns         |                                    |

| 47*          | 7* TT1P T1CKI Input Synchronous<br>Period |                                     | Synchronous                             |                | Greater of:<br>30 or <u>Tcy + 40</u><br>N | —      | _      | ns         | N = prescale value<br>(1, 2, 4, 8) |

|              |                                           |                                     | Asynchronous                            |                | 60                                        | —      |        | ns         |                                    |

| 48           | F⊤1                                       |                                     | lator Input Freque<br>abled by setting  |                | 32.4                                      | 32.768 | 33.1   | kHz        |                                    |

| 49*          | TCKEZTMR1                                 | Delay from E<br>Increment           | Delay from External Clock Edge to Timer |                |                                           | —      | 7 Tosc | —          | Timers in Sync<br>mode             |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1 µF, TA = 25°C.

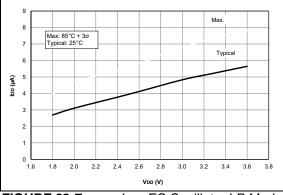

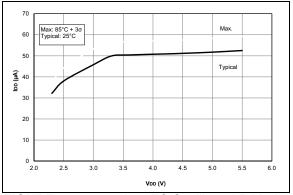

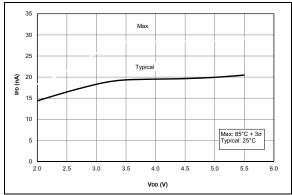

**FIGURE 32-7:** IDD, EC Oscillator LP Mode, Fosc = 32 kHz, PIC16LF1788/9 Only.

FIGURE 32-8: IDD, EC Oscillator LP Mode, Fosc = 32 kHz, PIC16F1788/9 Only.

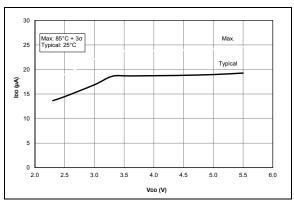

FIGURE 32-9: IDD, EC Oscillator LP Mode, Fosc = 500 kHz, PIC16LF1788/9 Only.

FIGURE 32-10: IDD, EC Oscillator LP Mode, Fosc = 500 kHz, PIC16F1788/9 Only.

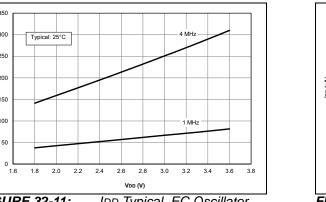

FIGURE 32-11: IDD Typical, EC Oscillator MP Mode, PIC16LF1788/9 Only.

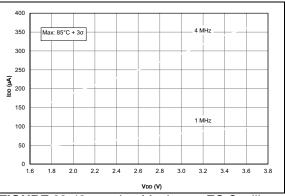

FIGURE 32-12: IDD Maximum, EC Oscillator MP Mode, PIC16LF1788/9 Only.

350

300

250

<u>ک</u> 200

<u></u> 150

100

50

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

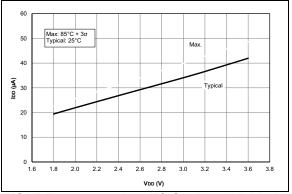

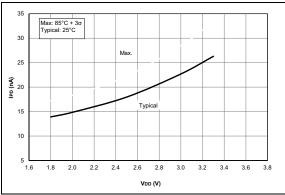

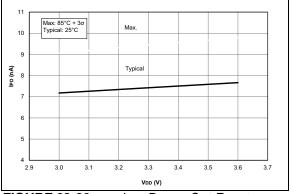

FIGURE 32-37: IPD, Fixed Voltage Reference (FVR), PIC16LF1788/9 Only.

FIGURE 32-38: IPD, Fixed Voltage Reference (FVR), PIC16F1788/9 Only.

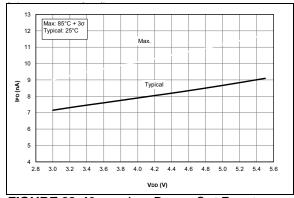

FIGURE 32-39: IPD, Brown-Out Reset (BOR), BORV = 1, PIC16LF1788/9 Only.

FIGURE 32-40: IPD, Brown-Out Reset (BOR), BORV = 1, PIC16F1788/9 Only.

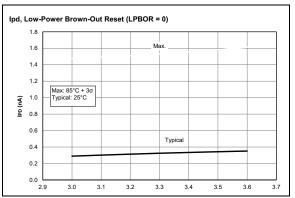

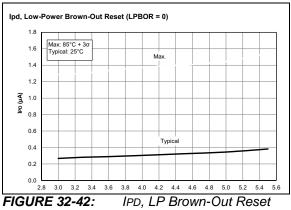

FIGURE 32-41: IPD, LP Brown-Out Reset (LPBOR = 0), PIC16LF1788/9 Only.

(LPBOR = 0), PIC16F1788/9 Only.

#### THE MICROCHIP WEBSITE

Microchip provides online support via our website site at www.microchip.com. This website is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the website contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

### CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip website at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

#### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- · Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the website at: http://microchip.com/support