Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betails                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                                |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 11x12b; D/A 1x8b, 3x5b                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1788t-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                                                                      | Function                | Input<br>Type | Output<br>Type         | Description                                     |  |  |  |

|---------------------------------------------------------------------------|-------------------------|---------------|------------------------|-------------------------------------------------|--|--|--|

| RA0/AN0/C1IN0-/C2IN0-/                                                    | RA0                     | TTL/ST        | CMOS                   | General purpose I/O.                            |  |  |  |

| C3IN0-/C4IN0-/ <del>SS<sup>(1)</sup></del>                                | AN0                     | AN            | —                      | ADC Channel 0 input.                            |  |  |  |

|                                                                           | C1IN0-                  | AN            | —                      | Comparator C1 negative input.                   |  |  |  |

|                                                                           | C2IN0-                  | AN            | _                      | Comparator C2 negative input.                   |  |  |  |

|                                                                           | C3IN0-                  | AN            | _                      | Comparator C3 negative input.                   |  |  |  |

|                                                                           | C4IN0-                  | AN            | _                      | Comparator C4 negative input.                   |  |  |  |

|                                                                           | SS                      | ST            | _                      | Slave Select input.                             |  |  |  |

| RA1/AN1/C1IN1-/C2IN1-/                                                    | RA1                     | TTL/ST        | CMOS                   | General purpose I/O.                            |  |  |  |

| C3IN1-/C4IN1-/OPA1OUT                                                     | AN1                     | AN            | _                      | ADC Channel 1 input.                            |  |  |  |

|                                                                           | C1IN1-                  | AN            | _                      | Comparator C1 negative input.                   |  |  |  |

|                                                                           | C2IN1-                  | AN            | _                      | Comparator C2 negative input.                   |  |  |  |

|                                                                           | C3IN1-                  | AN            | _                      | Comparator C3 negative input.                   |  |  |  |

|                                                                           | C4IN1-                  | AN            | _                      | Comparator C4 negative input.                   |  |  |  |

|                                                                           | OPA1OUT                 | _             | AN                     | Operational Amplifier 1 output.                 |  |  |  |

| RA2/AN2/C1IN0+/C2IN0+/                                                    | RA2                     | TTL/ST        | CMOS                   | General purpose I/O.                            |  |  |  |

| C3IN0+/C4IN0+/DAC1OUT1/                                                   | AN2                     | AN            | _                      | ADC Channel 2 input.                            |  |  |  |

| VREF-/DAC1VREF-                                                           | C1IN0+                  | AN            | —                      | Comparator C1 positive input.                   |  |  |  |

|                                                                           | C2IN0+                  | AN            | —                      | Comparator C2 positive input.                   |  |  |  |

|                                                                           | C3IN0+                  | AN            | —                      | Comparator C3 positive input.                   |  |  |  |

|                                                                           | C4IN0+                  | AN            | _                      | Comparator C4 positive input.                   |  |  |  |

|                                                                           | DAC1OUT1                | _             | AN                     | Digital-to-Analog Converter output.             |  |  |  |

|                                                                           | VREF-                   | AN            | _                      | ADC Negative Voltage Reference input.           |  |  |  |

|                                                                           | DAC1VREF-               | AN            | _                      | Digital-to-Analog Converter negative reference. |  |  |  |

| RA3/AN3/VREF+/C1IN1+/                                                     | RA3                     | TTL/ST        | CMOS                   | General purpose I/O.                            |  |  |  |

| DAC1VREF+/DAC2VREF+/                                                      | AN3                     | AN            | _                      | ADC Channel 3 input.                            |  |  |  |

| DAC3VREF+/DAC4VREF+                                                       | VREF+                   | AN            | _                      | ADC Voltage Reference input.                    |  |  |  |

|                                                                           | C1IN1+                  | AN            | _                      | Comparator C1 positive input.                   |  |  |  |

|                                                                           | DAC1VREF+               | AN            | _                      | Digital-to-Analog Converter positive reference. |  |  |  |

|                                                                           | DAC2VREF+               | AN            | _                      | Digital-to-Analog Converter positive reference. |  |  |  |

|                                                                           | DAC3VREF+               | AN            | _                      | Digital-to-Analog Converter positive reference. |  |  |  |

|                                                                           | DAC4VREF+               | AN            | _                      | Digital-to-Analog Converter positive reference. |  |  |  |

| RA4/C1OUT/OPA1IN+/T0CKI                                                   | RA4                     | TTL/ST        | CMOS                   | General purpose I/O.                            |  |  |  |

|                                                                           | C1OUT                   | _             | CMOS                   | Comparator C1 output.                           |  |  |  |

|                                                                           | OPA1IN+                 | AN            | _                      | Operational Amplifier 1 non-inverting input.    |  |  |  |

|                                                                           | TOCKI                   | ST            | _                      | Timer0 clock input.                             |  |  |  |

| RA5/AN4/C2OUT/OPA1IN-/                                                    | RA5                     | TTL/ST        | CMOS                   | General purpose I/O.                            |  |  |  |

| SS <sup>(1)</sup> /DAC2OUT1                                               | AN4                     | AN            | _                      | ADC Channel 4 input.                            |  |  |  |

|                                                                           | C2OUT                   | _             | CMOS                   | Comparator C2 output.                           |  |  |  |

|                                                                           | OPA1IN-                 | AN            | _                      | Operational Amplifier 1 inverting input.        |  |  |  |

|                                                                           | SS                      | ST            | _                      | Slave Select input.                             |  |  |  |

|                                                                           | DAC2OUT1                | _             | AN                     | Digital-to-Analog Converter output.             |  |  |  |

| Legend: AN = Analog input or<br>TTL = TTL compatible<br>HV = High Voltage | output CMOS<br>input ST |               | compatil<br>tt Trigger |                                                 |  |  |  |

TABLE 1-3: PIC16(L)F1789 PINOUT DESCRIPTION

2: All pins have interrupt-on-change functionality.

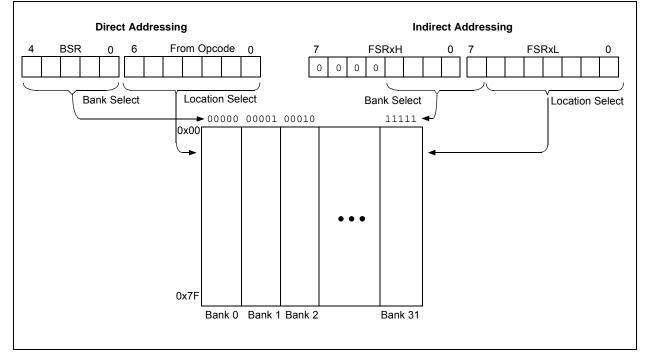

#### 3.6.1 TRADITIONAL DATA MEMORY

The traditional data memory is a region from FSR address 0x000 to FSR address 0xFFF. The addresses correspond to the absolute addresses of all SFR, GPR and common registers.

## FIGURE 6-7: INTERNAL OSCILLATOR SWITCH TIMING

| HFINTOSC/    |   |

|--------------|---|

| LFINTOSC     |   |

| IRCF <3:0>   | X |

| System Clock |   |

|              |   |

|              |   |

| HFINTOSC/    |   |

| LFINTOSC     |   |

| IRCF <3:0>   | X |

| System Clock |   |

## 6.4.2 TWO-SPEED START-UP SEQUENCE

- 1. Wake-up from Power-on Reset or Sleep.

- 2. Instructions begin execution by the internal oscillator at the frequency set in the IRCF<3:0> bits of the OSCCON register.

- 3. OST enabled to count 1024 clock cycles.

- 4. OST timed out, wait for falling edge of the internal oscillator.

- 5. OSTS is set.

- 6. System clock held low until the next falling edge of new clock (LP, XT or HS mode).

- 7. System clock is switched to external clock source.

##

#### FIGURE 6-8: TWO-SPEED START-UP

## 6.4.3 CHECKING TWO-SPEED CLOCK STATUS

Checking the state of the OSTS bit of the OSCSTAT register will confirm if the microcontroller is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Words, or the internal oscillator.

| U-0              | U-0                                     | U-0                               | R/W-0/0  | U-0                                                   | U-0              | U-0    | U-0   |  |  |

|------------------|-----------------------------------------|-----------------------------------|----------|-------------------------------------------------------|------------------|--------|-------|--|--|

| —                | —                                       | —                                 | CCP3IE   | —                                                     | —                | —      | —     |  |  |

| bit 7            |                                         |                                   |          |                                                       |                  |        | bit 0 |  |  |

|                  |                                         |                                   |          |                                                       |                  |        |       |  |  |

| Legend:          |                                         |                                   |          |                                                       |                  |        |       |  |  |

| R = Readable     | bit                                     | W = Writable I                    | bit      | U = Unimpler                                          | mented bit, read | as '0' |       |  |  |

| u = Bit is uncha | u = Bit is unchanged x = Bit is unknown |                                   | iown     | -n/n = Value at POR and BOR/Value at all other Resets |                  |        |       |  |  |

| '1' = Bit is set |                                         | '0' = Bit is clea                 | ared     |                                                       |                  |        |       |  |  |

|                  |                                         |                                   |          |                                                       |                  |        |       |  |  |

| bit 7-5          | Unimplemen                              | ted: Read as '                    | כ'       |                                                       |                  |        |       |  |  |

| bit 4            | CCP3IE: CCF                             | 3 Interrupt Ena                   | able bit |                                                       |                  |        |       |  |  |

|                  |                                         | the CCP3 intern<br>the CCP3 inter |          |                                                       |                  |        |       |  |  |

| bit 3-0          | Unimplemen                              | ted: Read as 'o                   | )'       |                                                       |                  |        |       |  |  |

## REGISTER 8-4: PIE3: PERIPHERAL INTERRUPT ENABLE REGISTER 3

| R/W-0/0        | R/W-0/0                                                                                                                                                | R/W-0/0                                                              | R/W-0/0                                         | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------|----------------|------------------|------------------|--------------|

| PSMC4T         | IF PSMC3TIF                                                                                                                                            | PSMC2TIF                                                             | PSMC1TIF                                        | PSMC4SIF       | PSMC3SIF         | PSMC2SIF         | PSMC1SIF     |

| bit 7          |                                                                                                                                                        | •                                                                    | •                                               | •              |                  |                  | bit          |

|                |                                                                                                                                                        |                                                                      |                                                 |                |                  |                  |              |

| Legend:        |                                                                                                                                                        |                                                                      |                                                 |                |                  |                  |              |

| R = Reada      | ble bit                                                                                                                                                | W = Writable                                                         | bit                                             | U = Unimpler   | mented bit, read | d as '0'         |              |

| u = Bit is u   | 0                                                                                                                                                      | x = Bit is unkr                                                      | nown                                            | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is s | set                                                                                                                                                    | '0' = Bit is clea                                                    | ared                                            |                |                  |                  |              |

| bit 7          | PSMC4TIF: F                                                                                                                                            | SMC4 Time B                                                          | ase Interrupt F                                 | -lag bit       |                  |                  |              |

|                | 1 = Interrupt i                                                                                                                                        |                                                                      |                                                 | 0              |                  |                  |              |

|                | 0 = Interrupt i                                                                                                                                        | s not pending                                                        |                                                 |                |                  |                  |              |

| bit 6          | PSMC3TIF: F                                                                                                                                            | SMC3 Time B                                                          | ase Interrupt F                                 | lag bit        |                  |                  |              |

|                | 1 = Interrupt i<br>0 = Interrupt i                                                                                                                     |                                                                      |                                                 |                |                  |                  |              |

| bit 5          | -                                                                                                                                                      | SMC2 Time B                                                          | ase Interrupt F                                 | -lag bit       |                  |                  |              |

|                | 1 = Interrupt i                                                                                                                                        |                                                                      | ·                                               | 0              |                  |                  |              |

|                | 0 = Interrupt i                                                                                                                                        | s not pending                                                        |                                                 |                |                  |                  |              |

| bit 4          | PSMC1TIF: F                                                                                                                                            | SMC1 Time B                                                          | ase Interrupt F                                 | -lag bit       |                  |                  |              |

|                | 1 = Interrupt i<br>0 = Interrupt i                                                                                                                     |                                                                      |                                                 |                |                  |                  |              |

| bit 3          | -                                                                                                                                                      | PSMC4 Auto-sh                                                        | nutdown Flag                                    | bit            |                  |                  |              |

|                | 1 = Interrupt i                                                                                                                                        |                                                                      | 0                                               |                |                  |                  |              |

|                | 0 = Interrupt i                                                                                                                                        |                                                                      |                                                 |                |                  |                  |              |

| bit 2          | PSMC3SIF: F                                                                                                                                            | PSMC3 Auto-sh                                                        | nutdown Flag                                    | bit            |                  |                  |              |

|                | 1 = Interrupt i                                                                                                                                        |                                                                      |                                                 |                |                  |                  |              |

|                | 0 = Interrupt i                                                                                                                                        | s not pending                                                        |                                                 |                |                  |                  |              |

| bit 1          |                                                                                                                                                        | PSMC2 Auto-sh                                                        | nutdown Flag                                    | bit            |                  |                  |              |

|                | 1 = Interrupt i                                                                                                                                        |                                                                      |                                                 |                |                  |                  |              |

| <b>L</b> H 0   | 0 = Interrupt i                                                                                                                                        |                                                                      |                                                 | L : 1          |                  |                  |              |

| bit 0          |                                                                                                                                                        | PSMC1 Auto-sh                                                        | hutdown Flag                                    | DIT            |                  |                  |              |

|                | 1 = Interrupt i<br>0 = Interrupt i                                                                                                                     |                                                                      |                                                 |                |                  |                  |              |

|                | Interrupt flag bits a<br>condition occurs, r<br>its corresponding<br>Enable bit, GIE, c<br>User software<br>appropriate interru<br>prior to enabling a | egardless of the<br>enable bit or th<br>of the INTCON<br>should ensu | e state of<br>le Global<br>register.<br>ure the |                |                  |                  |              |

## REGISTER 8-9: PIR4: PERIPHERAL INTERRUPT REQUEST REGISTER 4

| Name       | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|------------|---------|---------|---------|---------|---------|---------|---------|---------|---------------------|

| ANSELA     | ANSA7   | _       | ANSA5   | ANSA4   | ANSA3   | ANSA2   | ANSA1   | ANSA0   | 137                 |

| INLVLA     | INLVLA7 | INLVLA6 | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 | 138                 |

| LATA       | LATA7   | LATA6   | LATA5   | LATA4   | LATA3   | LATA2   | LATA1   | LATA0   | 136                 |

| ODCONA     | ODA7    | ODA6    | ODA5    | ODA4    | ODA3    | ODA2    | ODA1    | ODA0    | 138                 |

| OPTION_REG | WPUEN   | INTEDG  | TMR0CS  | TMR0SE  | PSA     |         | PS<2:0> |         |                     |

| PORTA      | RA7     | RA6     | RA5     | RA4     | RA3     | RA2     | RA1     | RA0     | 136                 |

| SLRCONA    | SLRA7   | SLRA6   | SLRA5   | SLRA4   | SLRA3   | SLRA2   | SLRA1   | SLRA0   | 138                 |

| TRISA      | TRISA7  | TRISA6  | TRISA5  | TRISA4  | TRISA3  | TRISA2  | TRISA1  | TRISA0  | 136                 |

| WPUA       | WPUA7   | WPUA6   | WPUA5   | WPUA4   | WPUA3   | WPUA2   | WPUA1   | WPUA0   | 137                 |

### TABLE 13-3: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

#### TABLE 13-4: SUMMARY OF CONFIGURATION WORD WITH PORTA

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2   | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|------------|---------|---------|---------------------|

| 0015104 | 13:8 | _       | _       | FCMEN    | IESO     | CLKOUTEN | BOREN<1:0> |         | CPD     | 50                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDTE     | E<1:0>   | FOSC<2:0>  |         |         | 58                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by PORTA.

'1' = Bit is set

| R/W-0/0                                 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0                                               | R/W-0/0          | R/W-0/0 | R/W-0/0 |  |  |

|-----------------------------------------|---------|---------|---------|-------------------------------------------------------|------------------|---------|---------|--|--|

| ODD7                                    | ODD6    | ODD5    | ODD4    | ODD3                                                  | ODD2             | ODD1    | ODD0    |  |  |

| bit 7                                   |         |         |         |                                                       |                  |         | bit 0   |  |  |

|                                         |         |         |         |                                                       |                  |         |         |  |  |

| Legend:                                 |         |         |         |                                                       |                  |         |         |  |  |

| R = Readable bit W = Writable bit       |         |         | bit     | U = Unimpler                                          | nented bit, read | as '0'  |         |  |  |

| u = Bit is unchanged x = Bit is unknown |         |         |         | -n/n = Value at POR and BOR/Value at all other Resets |                  |         |         |  |  |

bit 7-0 ODD<7:0>: PORTD Open-Drain Enable bits

For RD<7:0> pins, respectively

1 = Port pin operates as open-drain drive (sink current only)

0 = Port pin operates as standard push-pull drive (source and sink current)

## **REGISTER 13-32: SLRCOND: PORTD SLEW RATE CONTROL REGISTER**

'0' = Bit is cleared

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| SLRD7   | SLRD6   | SLRD5   | SLRD4   | SLRD3   | SLRD2   | SLRD1   | SLRD0   |

| bit 7   |         | •       | •       |         |         | •       | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SLRD<7:0>: PORTD Slew Rate Enable bits For RD<7:0> pins, respectively 1 = Port pin slew rate is limited 0 = Port pin slews at maximum rate

## **REGISTER 13-33: INLVLD: PORTD INPUT LEVEL CONTROL REGISTER**

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| INLVLD7 | INLVLD6 | INLVLD5 | INLVLD4 | INLVLD3 | INLVLD2 | INLVLD1 | INLVLD0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

INLVLD<7:0>: PORTD Input Level Select bits

For RD<7:0> pins, respectively

1 = ST input used for PORT reads and interrupt-on-change

0 = TTL input used for PORT reads and interrupt-on-change

| Name   | Bit 7        | Bit 6                    | Bit 5     | Bit 4    | Bit 3  | Bit 2   | Bit 1          | Bit 0  | Register<br>on Page |

|--------|--------------|--------------------------|-----------|----------|--------|---------|----------------|--------|---------------------|

| ADCON0 | ADRMD        |                          |           | CHS<4:0> |        |         | GO/DONE        | ADON   | 177                 |

| ADCON1 | ADFM         |                          | ADCS<2:0> |          | —      | ADNREF  | ADPRE          | F<1:0> | 178                 |

| ADCON2 |              | TRIGSE                   | EL<3:0>   |          |        | CHSN    | <b>\</b> <3:0> |        | 179                 |

| ADRESH | A/D Result I | A/D Result Register High |           |          |        |         |                |        | 180, 181            |

| ADRESL | A/D Result I | D Result Register Low    |           |          |        |         |                |        | 180, 181            |

| ANSELA | ANSA7        | —                        | ANSA5     | ANSA4    | ANSA3  | ANSA2   | ANSA1          | ANSA0  | 137                 |

| ANSELB | —            | ANSB6                    | ANSB5     | ANSB4    | ANSB3  | ANSB2   | ANSB1          | ANSB0  | 143                 |

| INTCON | GIE          | PEIE                     | TMR0IE    | INTE     | IOCIE  | TMR0IF  | INTF           | IOCIF  | 97                  |

| PIE1   | TMR1GIE      | ADIE                     | RCIE      | TXIE     | SSP1IE | CCP1IE  | TMR2IE         | TMR1IE | 98                  |

| PIR1   | TMR1GIF      | ADIF                     | RCIF      | TXIF     | SSP1IF | CCP1IF  | TMR2IF         | TMR1IF | 102                 |

| TRISA  | TRISA7       | TRISA6                   | TRISA5    | TRISA4   | TRISA3 | TRISA2  | TRISA1         | TRISA0 | 136                 |

| TRISB  | TRISB7       | TRISB6                   | TRISB5    | TRISB4   | TRISB3 | TRISB2  | TRISB1         | TRISB0 | 142                 |

| FVRCON | FVREN        | FVRRDY                   | TSEN      | TSRNG    | CDAFV  | /R<1:0> | ADFVF          | ۲<1:0> | 167                 |

TABLE 17-3: SUMMARY OF REGISTERS ASSOCIATED WITH ADC

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends on condition. Shaded cells are not used for the ADC module.

## 23.11 Register Definitions: Timer1 Control

т

## REGISTER 23-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0/u          | R/W-0/u                      | R/W-0/u                                   | R/W-0/u          | R/W-0/u          | R/W-0/u          | U-0            | R/W-0/u      |

|------------------|------------------------------|-------------------------------------------|------------------|------------------|------------------|----------------|--------------|

| TMR1CS<1:0>      |                              | T1CKP                                     | S<1:0>           | T1OSCEN          | T1SYNC           | _              | TMR10N       |

| bit 7            |                              |                                           |                  |                  |                  |                | bit          |

|                  |                              |                                           |                  |                  |                  |                |              |

| Legend:          |                              |                                           |                  |                  |                  |                |              |

| R = Readable     |                              | W = Writable                              |                  | •                | nented bit, read |                |              |

| u = Bit is unc   | •                            | x = Bit is unkn                           |                  | -n/n = Value a   | at POR and BOF   | R/Value at all | other Resets |

| '1' = Bit is set |                              | '0' = Bit is clea                         | ared             |                  |                  |                |              |

| bit 7-6          | TMR1CS<1:                    | 0>: Timer1 Cloc                           | k Source Sele    | ect bits         |                  |                |              |

|                  | 11 = Reserv                  | ed, do not use.                           |                  |                  |                  |                |              |

|                  | 10 = Timer1                  | clock source is                           | pin or oscillat  | or:              |                  |                |              |

|                  |                              | CEN = 0:                                  |                  |                  |                  |                |              |

|                  |                              | I clock from T10                          | KI pin (on the   | e rising eage)   |                  |                |              |

|                  |                              | oscillator on T1                          | OSI/T1OSO p      | ins              |                  |                |              |

|                  | 01 = Timer1                  | clock source is                           | system clock     | (Fosc)           |                  |                |              |

|                  | 00 = Timer1                  | clock source is                           | instruction clo  | ock (Fosc/4)     |                  |                |              |

| bit 5-4          | T1CKPS<1:                    | 0>: Timer1 Inpu                           | Clock Presca     | ale Select bits  |                  |                |              |

|                  | 11 = 1:8 Pre                 |                                           |                  |                  |                  |                |              |

|                  | 10 = 1:4 Pre<br>01 = 1:2 Pre |                                           |                  |                  |                  |                |              |

|                  | 01 = 1.2 Fie                 |                                           |                  |                  |                  |                |              |

| bit 3            | T1OSCEN:                     | _P Oscillator En                          | able Control b   | bit              |                  |                |              |

|                  | 1 = Dedicate                 | dicated Timer1 oscillator circuit enabled |                  |                  |                  |                |              |

|                  | 0 = Dedicate                 | ed Timer1 oscilla                         | ator circuit dis | abled            |                  |                |              |

| bit 2            |                              | mer1 Synchroniz                           |                  |                  |                  |                |              |

|                  |                              | synchronize asy                           |                  |                  | · · / <b>-</b> ` |                |              |

|                  | -                            | nize asynchron                            |                  | it with system c | lock (Fosc)      |                |              |

| bit 1            | -                            | nted: Read as '                           | )´               |                  |                  |                |              |

| bit 0            | TMR1ON: T                    |                                           |                  |                  |                  |                |              |

|                  | 1 = Enables                  |                                           | Time and moto    | flin flor        |                  |                |              |

|                  | $0 = Stops \Pi$              | mer1 and clears                           | s niner i gate   | шр-пор           |                  |                |              |

| Name    | Bit 7      | Bit 6          | Bit 5                            | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|------------|----------------|----------------------------------|-------|--------|--------|--------|--------|---------------------|

| CCP2CON | —          | _              | DC2B                             | <1:0> |        | CCP2N  | /<3:0> |        | 231                 |

| INTCON  | GIE        | PEIE           | TMR0IE                           | INTE  | IOCIE  | TMR0IF | INTF   | IOCIF  | 97                  |

| PIE1    | TMR1GIE    | ADIE           | RCIE                             | TXIE  | SSP1IE | CCP1IE | TMR2IE | TMR1IE | 98                  |

| PIR1    | TMR1GIF    | ADIF           | RCIF                             | TXIF  | SSP1IF | CCP1IF | TMR2IF | TMR1IF | 102                 |

| PR2     | Timer2 Mo  | dule Period    | le Period Register               |       |        |        | 220*   |        |                     |

| T2CON   | _          |                | T2OUTPS<3:0> TMR2ON T2CKPS<1:0>  |       |        |        | 222    |        |                     |

| TMR2    | Holding Re | gister for the | ster for the 8-bit TMR2 Register |       |        |        |        | 220*   |                     |

## TABLE 24-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER2

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for Timer2 module.

\* Page provides register information.

## 26.5 Output Steering

Output steering allows for PWM signals generated by the PSMC module to be placed on different pins under software control. Synchronized steering will hold steering changes until the first period event after the PSMCxLD bit is set. Unsynchronized steering changes will take place immediately.

Output steering is available in the following modes:

- 3-phase PWM

- Single PWM

- Complementary PWM

#### 26.5.1 3-PHASE STEERING

3-phase steering is available in the 3-Phase Modulation mode only. For more details on 3-phase steering refer to **Section 26.3.12 "3-Phase PWM"**.

#### 26.5.2 SINGLE PWM STEERING

In Single PWM Steering mode, the single PWM signal can be routed to any combination of the PSMC output pins. Examples of unsynchronized single PWM steering are shown in Figure 26-16.

| PxSTRB                                                                                                |  |

|-------------------------------------------------------------------------------------------------------|--|

| PxSTR <u>C</u>                                                                                        |  |

|                                                                                                       |  |

|                                                                                                       |  |

| PxSTRF<br>PSMCxF<br>With synchronization disabled, it is possible to get glitches on the PWM outputs. |  |

|                                                                                                       |  |

| R/W-0/0          | R/W-0/0                                                                   | R/W-0/0                                                                                                                                             | U-0                                                      | R/W-0/0                                                | R/W-0/0          | R/W-0/0           | R/W-0/0      |

|------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------|------------------|-------------------|--------------|

| PxMDLEN          | PxMDLPOL                                                                  | PxMDLBIT                                                                                                                                            | _                                                        |                                                        | PxMSR            | C<3:0>            |              |

| bit 7            |                                                                           | · · · ·                                                                                                                                             |                                                          |                                                        |                  |                   | bit          |

|                  |                                                                           |                                                                                                                                                     |                                                          |                                                        |                  |                   |              |

| Legend:          |                                                                           |                                                                                                                                                     |                                                          |                                                        |                  |                   |              |

| R = Readable     | bit                                                                       | W = Writable b                                                                                                                                      | it                                                       | -                                                      | nented bit, read |                   |              |

| u = Bit is unch  | anged                                                                     | x = Bit is unkno                                                                                                                                    | own                                                      | -n/n = Value a                                         | at POR and BO    | R/Value at all o  | other Resets |

| '1' = Bit is set |                                                                           | '0' = Bit is clear                                                                                                                                  | red                                                      |                                                        |                  |                   |              |

| bit 7            | PxMDLEN: P                                                                | SMC Periodic N                                                                                                                                      | lodulation I                                             | Mode Enable bit                                        |                  |                   |              |

|                  |                                                                           | is active when in module is alway                                                                                                                   |                                                          | selected by PxMS                                       | SRC<3:0> is in i | ts active state ( | see PxMPOL   |

| bit 6            |                                                                           | PSMC Periodic                                                                                                                                       |                                                          | Polarity bit                                           |                  |                   |              |

|                  | 1 = PSMCx                                                                 | is active when the                                                                                                                                  | he PSMCx                                                 | Modulation sour<br>Modulation sour                     |                  |                   |              |

|                  | 0 = PSMCx<br>PxMDLEN = 0                                                  | is active when the                                                                                                                                  | he PxMDLI<br>N = 1 and F                                 | POL equals logic<br>POL equals logic<br>PxMSRC<3:0> <: | : '1'            |                   |              |

| bit 4            |                                                                           | ted: Read as '0'                                                                                                                                    |                                                          |                                                        |                  |                   |              |

| bit 3-0          | •                                                                         |                                                                                                                                                     |                                                          | ion Source Selec                                       | tion bits        |                   |              |

|                  | 0111 = Reset<br>0110 = PSM0<br>0101 = PSM0<br>0100 = Reset<br>0011 = PSM0 | rved<br>rved<br>rved<br>rved<br>rved<br>Cx Modulation S<br>rved<br>Cx Modulation S<br>rved<br>Cx Modulation S<br>Cx Modulation S<br>Cx Modulation S | ource is C(<br>ource is C(<br>ource is sy<br>ource is sy | CP2<br>CP1<br>nc_C3OUT<br>nc_C2OUT                     |                  |                   |              |

## REGISTER 26-2: PSMCxMDL: PSMC MODULATION CONTROL REGISTER

| U-0              | U-0        | R/W-0/0                            | R/W-0/0                | R/W-0/0                | R/W-0/0                | R/W-0/0          | R/W-0/0     |

|------------------|------------|------------------------------------|------------------------|------------------------|------------------------|------------------|-------------|

| _                | —          | PxASDLF <sup>(1)</sup>             | PxASDLE <sup>(1)</sup> | PxASDLD <sup>(1)</sup> | PxASDLC <sup>(1)</sup> | PxASDLB          | PxASDLA     |

| bit 7            |            |                                    |                        |                        |                        |                  | bit C       |

|                  |            |                                    |                        |                        |                        |                  |             |

| Legend:          |            |                                    |                        |                        |                        |                  |             |

| R = Readable     | bit        | W = Writable                       | bit                    | U = Unimplem           | ented bit, read        | as '0'           |             |

| u = Bit is unch  | anged      | x = Bit is unkn                    | iown                   | -n/n = Value a         | t POR and BOF          | R/Value at all o | ther Resets |

| '1' = Bit is set |            | '0' = Bit is clea                  | ared                   |                        |                        |                  |             |

|                  |            |                                    |                        |                        |                        |                  |             |

| bit 7-6          | Unimplemen | ted: Read as '                     | )'                     |                        |                        |                  |             |

| bit 5            | PxASDLF: P | SMCx Output F                      | Auto-Shutdov           | wn Pin Level bi        | t(1)                   |                  |             |

|                  |            | uto-shutdown is                    |                        |                        |                        |                  |             |

|                  |            | uto-shutdown is                    | •                      |                        | •                      |                  |             |

| bit 4            | PxASDLE: P | SMCx Output E                      | E Auto-Shutdo          | wn Pin Level bi        | it(1)                  |                  |             |

|                  |            | uto-shutdown is                    | · •                    |                        | 0                      |                  |             |

|                  |            | uto-shutdown is                    |                        |                        | •                      |                  |             |

| bit 3            |            | SMCx Output E                      |                        |                        |                        |                  |             |

|                  |            | uto-shutdown is                    |                        |                        |                        |                  |             |

| bit 2            |            | uto-shutdown is                    |                        |                        | •                      |                  |             |

| DIL 2            |            | SMCx Output (                      |                        |                        |                        |                  |             |

|                  |            | uto-shutdown is<br>uto-shutdown is |                        |                        |                        |                  |             |

| bit 1            |            | SMCx Output E                      | -                      |                        | -                      |                  |             |

|                  |            | uto-shutdown is                    |                        |                        |                        |                  |             |

|                  |            | uto-shutdown is                    | · •                    |                        | 0                      |                  |             |

| bit 0            | PxASDLA: P | SMCx Output A                      | Auto-Shutdo            | wn Pin Level b         | it                     |                  |             |

|                  |            | uto-shutdown is                    |                        |                        |                        |                  |             |

|                  | 0 = When a | uto-shutdown is                    | s asserted, pin        | PSMCxA will            | drive logic '0'        |                  |             |

## REGISTER 26-17: PSMCxASDL: PSMC AUTO-SHUTDOWN OUTPUT LEVEL REGISTER

**Note 1:** These bits are not implemented on PSMC2.

| R/W-0/0          | U-0            | U-0              | R/W-0/0       | R/W-0/0        | R/W-0/0          | R/W-0/0          | U-0         |

|------------------|----------------|------------------|---------------|----------------|------------------|------------------|-------------|

| PxASDSIN         | _              | _                | PxASDSC4      | PxASDSC3       | PxASDSC2         | PxASDSC1         | _           |

| bit 7            |                |                  | ļ             |                |                  | I                | bit 0       |

|                  |                |                  |               |                |                  |                  |             |

| Legend:          |                |                  |               |                |                  |                  |             |

| R = Readable     | bit            | W = Writable     | bit           | U = Unimpler   | nented bit, read | as '0'           |             |

| u = Bit is uncha | anged          | x = Bit is unkr  | nown          | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is set |                | '0' = Bit is cle | ared          |                |                  |                  |             |

|                  |                |                  |               |                |                  |                  |             |

| bit 7            | PxASDSIN: A    | Auto-shutdown    | occurs on PSI | MCxIN pin      |                  |                  |             |

|                  |                | utdown will occ  |               |                | true             |                  |             |

|                  | 0 = PSMCxI     | N pin will not c | ause auto-shu | utdown         |                  |                  |             |

| bit 6-5          | Unimplemen     | ted: Read as '   | 0'            |                |                  |                  |             |

| bit 4            | PxASDSC4:      | Auto-shutdown    | occurs on syr | nc_C4OUT ou    | tput             |                  |             |

|                  |                | utdown will occ  |               |                | it goes true     |                  |             |

|                  | $0 = sync_C^2$ | 40UT will not c  | ause auto-shu | utdown         |                  |                  |             |

| bit 3            | PxASDSC3:      | Auto-shutdown    | occurs on syr | nc_C3OUT ou    | tput             |                  |             |

|                  |                | utdown will occ  |               |                | it goes true     |                  |             |

|                  | $0 = sync_C3$  | 30UT will not c  | ause auto-shu | utdown         |                  |                  |             |

| bit 2            | PxASDSC2:      | Auto-shutdown    | occurs on syr | nc_C2OUT ou    | tput             |                  |             |

|                  |                | utdown will occ  |               |                | it goes true     |                  |             |

|                  | $0 = sync_C2$  | 20UT will not c  | ause auto-shu | utdown         |                  |                  |             |

| bit 1            | PxASDSC1:      | Auto-shutdown    | occurs on syr | nc_C1OUT ou    | tput             |                  |             |

|                  |                | utdown will occ  |               |                | goes true        |                  |             |

|                  |                | 1OU will not ca  |               | down           |                  |                  |             |

| bit 0            | Unimplemen     | ted: Read as '   | 0'            |                |                  |                  |             |

|                  |                |                  |               |                |                  |                  |             |

## REGISTER 26-18: PSMCxASDS: PSMC AUTO-SHUTDOWN SOURCE REGISTER

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|-------------|

|                  |         |                   | PSMCxB  | LKR<7:0>       |                  |                  |             |

| bit 7            |         |                   |         |                |                  |                  | bit 0       |

|                  |         |                   |         |                |                  |                  |             |

| Legend:          |         |                   |         |                |                  |                  |             |

| R = Readable     | bit     | W = Writable      | bit     | U = Unimpler   | nented bit, read | l as '0'         |             |

| u = Bit is uncha | anged   | x = Bit is unkr   | nown    | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                  |             |

### REGISTER 26-30: PSMCxBLKR: PSMC RISING EDGE BLANKING TIME REGISTER

bit 7-0

**PSMCxBLKR<7:0>:** Rising Edge Blanking Time bits

= Unsigned number of PSMCx psmc\_clk clock periods in rising edge blanking

#### REGISTER 26-31: PSMCxBLKF: PSMC FALLING EDGE BLANKING TIME REGISTER

| R/W-0/0 | R/W-0/0 | R/W-0/0         | R/W-0/0  | R/W-0/0                                           | R/W-0/0 | R/W-0/0 |

|---------|---------|-----------------|----------|---------------------------------------------------|---------|---------|

|         |         | PSMCxBl         | _KF<7:0> |                                                   |         |         |

|         |         |                 |          |                                                   |         | bit 0   |

|         | R/W-0/0 | R/W-0/0 R/W-0/0 |          | R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0<br>PSMCxBLKF<7:0> |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **PSMCxBLKF<7:0>:** Falling Edge Blanking Time bits

= Unsigned number of PSMCx psmc\_clk clock periods in falling edge blanking

#### 27.2.3 SPI MASTER MODE

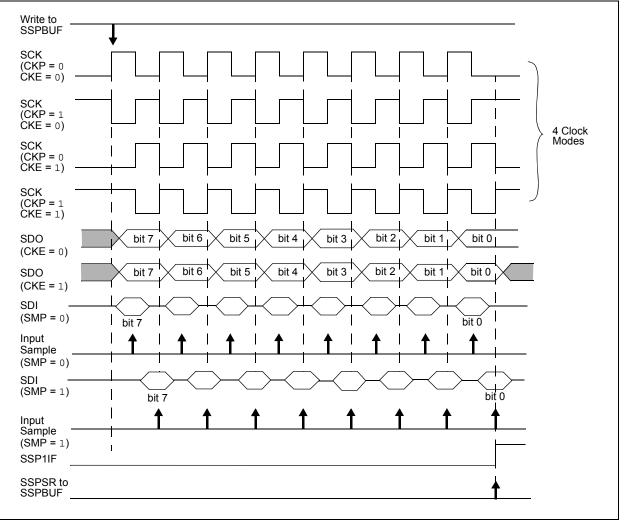

The master can initiate the data transfer at any time because it controls the SCK line. The master determines when the slave (Processor 2, Figure 27-5) is to broadcast data by the software protocol.

In Master mode, the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI is only going to receive, the SDO output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and Status bits appropriately set). The clock polarity is selected by appropriately programming the CKP bit of the SSPCON1 register and the CKE bit of the SSPSTAT register. This then, would give waveforms for SPI communication as shown in Figure 27-6, Figure 27-8 and Figure 27-9, where the MSB is transmitted first. In Master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 \* Tcy)

- Fosc/64 (or 16 \* Tcy)

- Timer2 output/2

- Fosc/(4 \* (SSPADD + 1))

Figure 27-6 shows the waveforms for Master mode.

When the CKE bit is set, the SDO data is valid before there is a clock edge on SCK. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPBUF is loaded with the received data is shown.

FIGURE 27-6: SPI MODE WAVEFORM (MASTER MODE)

## REGISTER 27-1: SSPSTAT: SSP STATUS REGISTER (CONTINUED)

bit 0

BF: Buffer Full Status bit

Receive (SPI and I<sup>2</sup>C modes):

1 = Receive complete, SSPBUF is full

0 = Receive not complete, SSPBUF is empty

Transmit (I<sup>2</sup>C mode only):

- 1 = Data transmit in progress (does not include the ACK and Stop bits), SSPBUF is full

- 0 = Data transmit complete (does not include the  $\overline{ACK}$  and Stop bits), SSPBUF is empty

| BRA              | Relative Branch                                                                                                                                                                                                                                 |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]BRA label<br>[ <i>label</i> ]BRA \$+k                                                                                                                                                                                           |

| Operands:        | -256 $\leq$ label - PC + 1 $\leq$ 255 -256 $\leq$ k $\leq$ 255                                                                                                                                                                                  |

| Operation:       | $(PC) + 1 + k \rightarrow PC$                                                                                                                                                                                                                   |

| Status Affected: | None                                                                                                                                                                                                                                            |

| Description:     | Add the signed 9-bit literal 'k' to<br>the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will<br>be PC + 1 + k. This instruction is<br>a 2-cycle instruction. This branch<br>has a limited range. |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                           |

| Operation:       | <b>skip if (f<b>) =</b> 0</b>                                                                                                                                                                                                 |

| Status Affected: | None                                                                                                                                                                                                                          |

| Description:     | If bit 'b' in register 'f' is '1', the next<br>instruction is executed.<br>If bit 'b', in register 'f', is '0', the<br>next instruction is discarded, and<br>a NOP is executed instead, making<br>this a 2-cycle instruction. |

| BRW              | Relative Branch with W                                                                                                                                                                                        |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BRW                                                                                                                                                                                                 |

| Operands:        | None                                                                                                                                                                                                          |

| Operation:       | $(PC) + (W) \rightarrow PC$                                                                                                                                                                                   |

| Status Affected: | None                                                                                                                                                                                                          |

| Description:     | Add the contents of W (unsigned)<br>to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will<br>be PC + 1 + (W). This instruction<br>is a 2-cycle instruction. |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b < 7 \end{array}$                                                                                                                                                |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                            |

| Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next<br>instruction is discarded and a NOP<br>is executed instead, making this a<br>2-cycle instruction. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]BSF f,b                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | 1 → (f <b>)</b>                                                     |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| CALL             | Call Subroutine                                                                                                                                                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                 |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                    |

| Operation:       | $\begin{array}{l} (PC)+1 \rightarrow TOS, \\ k \rightarrow PC < 10:0>, \\ (PCLATH < 6:3>) \rightarrow PC < 14:11> \end{array}$                                                                                                          |

| Status Affected: | None                                                                                                                                                                                                                                    |

| Description:     | Call Subroutine. First, return<br>address (PC + 1) is pushed onto<br>the stack. The 11-bit immediate<br>address is loaded into PC bits<br><10:0>. The upper bits of the PC<br>are loaded from PCLATH. CALL is<br>a 2-cycle instruction. |