#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                                |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 11x12b; D/A 1x8b, 3x5b                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

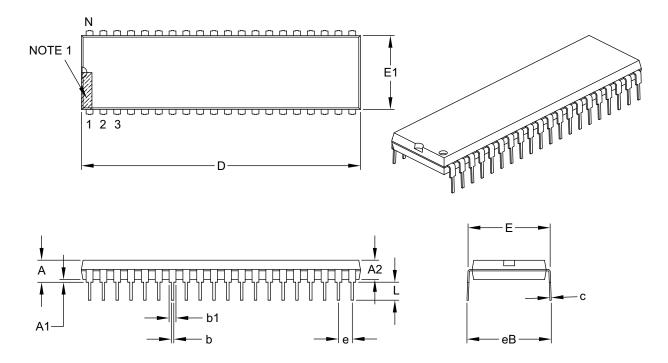

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1788t-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

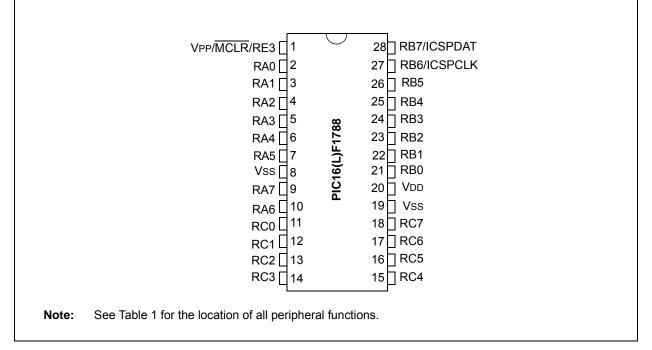

#### Pin Diagram – 28-Pin SPDIP, SOIC, SSOP

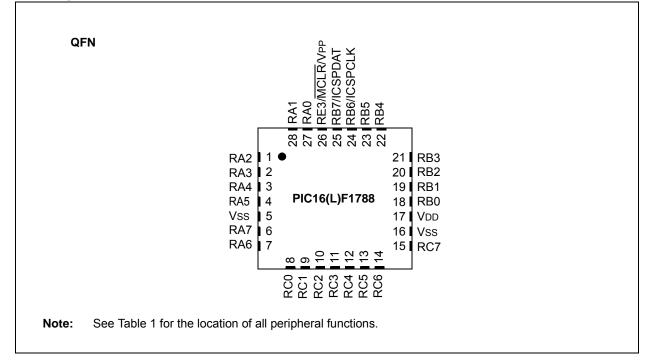

#### Pin Diagram – 28-Pin QFN

| Name                                                                  | Function | Input<br>Type    | Output<br>Type | Description                         |

|-----------------------------------------------------------------------|----------|------------------|----------------|-------------------------------------|

| RB4/AN11/C3IN1+/SS <sup>(1)</sup>                                     | RB4      | TTL/ST           | CMOS           | General purpose I/O.                |

|                                                                       | AN11     | AN               |                | ADC Channel 11 input.               |

|                                                                       | C3IN1+   | AN               | _              | Comparator C3 positive input.       |

|                                                                       | SS       | ST               | _              | Slave Select input.                 |

| RB5/AN13/C4IN2-/T1G/CCP3 <sup>(1)</sup>                               | RB5      | TTL/ST           | CMOS           | General purpose I/O.                |

| SDO <sup>(1)</sup>                                                    | AN13     | AN               | _              | ADC Channel 13 input.               |

|                                                                       | C4IN2-   | AN               | _              | Comparator C4 negative input.       |

|                                                                       | T1G      | ST               | _              | Timer1 gate input.                  |

|                                                                       | CCP3     | ST               | CMOS           | Capture/Compare/PWM3.               |

|                                                                       | SDO      | _                | CMOS           | SPI data output.                    |

| RB6/C4IN1+/TX <sup>(1)</sup> /CK <sup>(1)</sup> /SDI <sup>(1)</sup> / | RB6      | TTL/ST           | CMOS           | General purpose I/O.                |

| SDA <sup>(1)</sup> /ICSPCLK                                           | C4IN1+   | AN               | _              | Comparator C4 positive input.       |

|                                                                       | ТХ       | —                | CMOS           | EUSART asynchronous transmit.       |

|                                                                       | СК       | ST               | CMOS           | EUSART synchronous clock.           |

|                                                                       | SDI      | ST               | _              | SPI data input.                     |

|                                                                       | SDA      | l <sup>2</sup> C | OD             | I <sup>2</sup> C data input/output. |

|                                                                       | ICSPCLK  | ST               | _              | Serial Programming Clock.           |

| RB7/DAC1OUT2/DAC2OUT2/                                                | RB7      | TTL/ST           | CMOS           | General purpose I/O.                |

| DAC3OUT2/DAC4OUT2/RX <sup>(1)</sup> /                                 | DAC10UT2 | _                | AN             | Voltage Reference output.           |

| DT <sup>(1)</sup> /SCK <sup>(1)</sup> /SCL <sup>(1)</sup> /ICSPDAT    | DAC2OUT2 | _                | AN             | Voltage Reference output.           |

|                                                                       | DAC3OUT2 | _                | AN             | Voltage Reference output.           |

|                                                                       | DAC4OUT2 | _                | AN             | Voltage Reference output.           |

|                                                                       | RX       | ST               | _              | EUSART asynchronous input.          |

|                                                                       | DT       | ST               | CMOS           | EUSART synchronous data.            |

|                                                                       | SCK      | ST               | CMOS           | SPI clock.                          |

|                                                                       | SCL      | l <sup>2</sup> C | OD             | I <sup>2</sup> C clock.             |

|                                                                       | ICSPDAT  | ST               | CMOS           | ICSP™ Data I/O.                     |

| RC0/T1OSO/T1CKI/PSMC1A                                                | RC0      | TTL/ST           | CMOS           | General purpose I/O.                |

|                                                                       | T10S0    | XTAL             | XTAL           | Timer1 Oscillator Connection.       |

|                                                                       | T1CKI    | ST               | _              | Timer1 clock input.                 |

|                                                                       | PSMC1A   | _                | CMOS           | PSMC1 output A.                     |

| RC1/T1OSI/PSMC1B/CCP2                                                 | RC1      | TTL/ST           | CMOS           |                                     |

|                                                                       | T10SI    | XTAL             | XTAL           | Timer1 Oscillator Connection.       |

|                                                                       | PSMC1B   | _                | CMOS           | PSMC1 output B.                     |

|                                                                       | CCP2     | ST               | CMOS           | Capture/Compare/PWM2.               |

| RC2/PSMC1C/CCP1                                                       | RC2      | TTL/ST           | CMOS           | General purpose I/O.                |

|                                                                       | PSMC1C   |                  | CMOS           | PSMC1 output C.                     |

|                                                                       | CCP1     | ST               | CMOS           | Capture/Compare/PWM1.               |

| RC3/PSMC1D/SCK/SCL                                                    | RC3      | TTL/ST           | CMOS           | General purpose I/O.                |

|                                                                       | PSMC1D   |                  | CMOS           | PSMC1 output D.                     |

|                                                                       | SCK      | ST               | CMOS           | SPI clock.                          |

|                                                                       | SCL      | I <sup>2</sup> C | OD             | I <sup>2</sup> C clock.             |

| egend: AN = Analog input or c                                         |          |                  |                |                                     |

#### DIC16/I )E1780 DINICIT DESCRIPTION (CONTINUED) TADIE 4 9.

HV = High Voltage XTAL = Crystal

levels

Note 1: Pin functions can be assigned to one of two locations via software. See Register 13-1.

2: All pins have interrupt-on-change functionality.

### EXAMPLE 3-2: ACCESSING PROGRAM MEMORY VIA FSR

| constants    |                             |

|--------------|-----------------------------|

| DW           | DATA0 ;First constant       |

| DW           | DATA1 ;Second constant      |

| DW           | DATA2                       |

| DW           | DATA3                       |

| my_function  | 1                           |

| ; LOTS       | OF CODE                     |

| MOVLW        | DATA_INDEX                  |

| ADDLW        | LOW constants               |

| MOVWF        | FSR1L                       |

| MOVLW        | HIGH constants ;MSb is set  |

| automatical  | ly                          |

| MOVWF        | FSR1H                       |

| BTFSC        | STATUS,C ;carry from ADDLW? |

| INCF         | FSR1H,f ;yes                |

| MOVIW        | 0[FSR1]                     |

| ; THE PROGRA | AM MEMORY IS IN W           |

| 1            |                             |

#### 3.2.1.1 STATUS Register

The STATUS register, shown in Register 3-1, contains:

- · the arithmetic status of the ALU

- · the Reset status

**REGISTER 3-1:**

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the  $\overline{TO}$  and  $\overline{PD}$  bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

#### 3.3 **Register Definitions: Status**

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits (Refer to Section 30.0 "Instruction Set Summary").

| Note: | The C and DC bits operate as Borrow and |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|

|       | Digit Borrow out bits, respectively, in |  |  |  |  |

|       | subtraction.                            |  |  |  |  |

| U-0 | U-0 | U-0 | R-1/q | R-1/g |  |

|-----|-----|-----|-------|-------|--|

STATUS: STATUS REGISTER

| U-0             | U-0                                                       | U-0                                                                                       | R-1/q         | R-1/q                  | R/W-0/u          | R/W-0/u           | R/W-0/u          |  |  |

|-----------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------|------------------------|------------------|-------------------|------------------|--|--|

|                 | _                                                         |                                                                                           | TO            | PD                     | Z                | DC <sup>(1)</sup> | C <sup>(1)</sup> |  |  |

| bit 7           |                                                           |                                                                                           |               |                        |                  |                   | bit (            |  |  |

|                 |                                                           |                                                                                           |               |                        |                  |                   |                  |  |  |

| Legend:         |                                                           |                                                                                           |               |                        |                  |                   |                  |  |  |

| R = Readab      | le bit                                                    | W = Writable I                                                                            | oit           | U = Unimpler           | mented bit, read | l as '0'          |                  |  |  |

| u = Bit is une  | changed                                                   | x = Bit is unkn                                                                           | own           | -n/n = Value a         | at POR and BO    | R/Value at all o  | ther Resets      |  |  |

| '1' = Bit is se | et                                                        | '0' = Bit is clea                                                                         | ared          | q = Value der          | pends on condit  | ion               |                  |  |  |

|                 |                                                           |                                                                                           |               |                        |                  |                   |                  |  |  |

| bit 7-5         | Unimplemen                                                | ted: Read as '0                                                                           | )'            |                        |                  |                   |                  |  |  |

| bit 4           | TO: Time-Out                                              | t bit                                                                                     |               |                        |                  |                   |                  |  |  |

|                 |                                                           | er-up, CLRWDT                                                                             |               | r SLEEP <b>instruc</b> | tion             |                   |                  |  |  |

|                 |                                                           | me-out occurred                                                                           | t l           |                        |                  |                   |                  |  |  |

| bit 3           | PD: Power-D                                               | own bit                                                                                   |               |                        |                  |                   |                  |  |  |

|                 |                                                           | er-up or by the                                                                           |               |                        |                  |                   |                  |  |  |

| 1.1.0           |                                                           | tion of the SLEE                                                                          | P Instruction | 1                      |                  |                   |                  |  |  |

| bit 2           | <b>Z:</b> Zero bit                                        |                                                                                           |               |                        |                  |                   |                  |  |  |

|                 |                                                           | t of an arithmet<br>t of an arithmet                                                      | <b>U</b> 1    |                        | ero              |                   |                  |  |  |

| bit 1           |                                                           |                                                                                           | •             |                        |                  | ons)(1)           |                  |  |  |

|                 | -                                                         | DC: Digit Carry/Digit Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup> |               |                        |                  |                   |                  |  |  |

|                 | 0 = No carry-out from the 4th low-order bit of the result |                                                                                           |               |                        |                  |                   |                  |  |  |

| bit 0           |                                                           |                                                                                           |               |                        |                  |                   |                  |  |  |

|                 | 1 = A carry-or                                            | ut from the Mos                                                                           | t Significant | bit of the result      | occurred         |                   |                  |  |  |

|                 | 0 = No carry-                                             | out from the Mo                                                                           | st Significan | t bit of the resu      | It occurred      |                   |                  |  |  |

| Note 1: F       | or Borrow, the po                                         | larity is reverse                                                                         | d A subtract  | tion is executed       | l by adding the  | two's complem     | ent of the       |  |  |

Note 1: For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand.

#### 6.2.2.1 HFINTOSC

The High-Frequency Internal Oscillator (HFINTOSC) is a factory calibrated 16 MHz internal clock source. The frequency of the HFINTOSC can be altered via software using the OSCTUNE register (Register 6-3).

The output of the HFINTOSC connects to a postscaler and multiplexer (see Figure 6-1). One of multiple frequencies derived from the HFINTOSC can be selected via software using the IRCF<3:0> bits of the OSCCON register. See **Section 6.2.2.7** "Internal Oscillator Clock Switch Timing" for more information.

The HFINTOSC is enabled by:

- Configure the IRCF<3:0> bits of the OSCCON register for the desired HF frequency, and

- FOSC<2:0> = 100, or

- Set the System Clock Source (SCS) bits of the OSCCON register to '1x'.

A fast startup oscillator allows internal circuits to power up and stabilize before switching to HFINTOSC.

The High Frequency Internal Oscillator Ready bit (HFIOFR) of the OSCSTAT register indicates when the HFINTOSC is running.

The High Frequency Internal Oscillator Status Locked bit (HFIOFL) of the OSCSTAT register indicates when the HFINTOSC is running within 2% of its final value.

The High Frequency Internal Oscillator Stable bit (HFIOFS) of the OSCSTAT register indicates when the HFINTOSC is running within 0.5% of its final value.

#### 6.2.2.2 MFINTOSC

The Medium-Frequency Internal Oscillator (MFINTOSC) is a factory calibrated 500 kHz internal clock source. The frequency of the MFINTOSC can be altered via software using the OSCTUNE register (Register 6-3).

The output of the MFINTOSC connects to a postscaler and multiplexer (see Figure 6-1). One of nine frequencies derived from the MFINTOSC can be selected via software using the IRCF<3:0> bits of the OSCCON register. See **Section 6.2.2.7** "Internal Oscillator Clock Switch Timing" for more information.

The MFINTOSC is enabled by:

- Configure the IRCF<3:0> bits of the OSCCON register for the desired HF frequency, and

- FOSC<2:0> = 100, or

- Set the System Clock Source (SCS) bits of the OSCCON register to '1x'

The Medium Frequency Internal Oscillator Ready bit (MFIOFR) of the OSCSTAT register indicates when the MFINTOSC is running.

#### 6.2.2.3 Internal Oscillator Frequency Adjustment

The 500 kHz internal oscillator is factory calibrated. This internal oscillator can be adjusted in software by writing to the OSCTUNE register (Register 6-3). Since the HFINTOSC and MFINTOSC clock sources are derived from the 500 kHz internal oscillator a change in the OSCTUNE register value will apply to both.

The default value of the OSCTUNE register is '0'. The value is a 6-bit two's complement number. A value of 1Fh will provide an adjustment to the maximum frequency. A value of 20h will provide an adjustment to the minimum frequency.

When the OSCTUNE register is modified, the oscillator frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

OSCTUNE does not affect the LFINTOSC frequency. Operation of features that depend on the LFINTOSC clock source frequency, such as the Power-up Timer (PWRT), Watchdog Timer (WDT), Fail-Safe Clock Monitor (FSCM) and peripherals, are *not* affected by the change in frequency.

#### 6.2.2.4 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is an uncalibrated 31 kHz internal clock source.

The output of the LFINTOSC connects to a multiplexer (see Figure 6-1). Select 31 kHz, via software, using the IRCF<3:0> bits of the OSCCON register. See Section 6.2.2.7 "Internal Oscillator Clock Switch Timing" for more information. The LFINTOSC is also the frequency for the Power-up Timer (PWRT), Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The LFINTOSC is enabled by selecting 31 kHz (IRCF<3:0> bits of the OSCCON register = 000) as the system clock source (SCS bits of the OSCCON register = 1x), or when any of the following are enabled:

- Configure the IRCF<3:0> bits of the OSCCON register for the desired LF frequency, and

- FOSC<2:0> = 100, or

- Set the System Clock Source (SCS) bits of the OSCCON register to '1x'

Peripherals that use the LFINTOSC are:

- Power-up Timer (PWRT)

- Watchdog Timer (WDT)

- Fail-Safe Clock Monitor (FSCM)

The Low-Frequency Internal Oscillator Ready bit (LFIOFR) of the OSCSTAT register indicates when the LFINTOSC is running.

### 6.6 Register Definitions: Oscillator Control

#### REGISTER 6-1: OSCCON: OSCILLATOR CONTROL REGISTER

| R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ) R/W-0/0              | R/W-1/1                                                                                                                                                                   | R/W-1/1                              | R/W-1/1         | U-0             | R/W-0/0         | R/W-0/0      |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------|-----------------|-----------------|--------------|--|

| SPLLEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | N                      | IRCF                                                                                                                                                                      | <3:0>                                |                 | _               | SCS             | <1:0>        |  |

| oit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                        |                                                                                                                                                                           |                                      |                 |                 |                 | bit 0        |  |

| _egend:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                        |                                                                                                                                                                           |                                      |                 |                 |                 |              |  |

| R = Reada                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ıble bit               | W = Writable                                                                                                                                                              | bit                                  | U = Unimplem    | ented bit, rea  | ad as '0'       |              |  |

| u = Bit is u                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | nchanged               | x = Bit is unkr                                                                                                                                                           | nown                                 | -n/n = Value at | t POR and B     | OR/Value at all | other Resets |  |

| 1' = Bit is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | set                    | '0' = Bit is cle                                                                                                                                                          | ared                                 |                 |                 |                 |              |  |

| oit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | If PLLEN in SPLLEN bit | Configuration W                                                                                                                                                           | ′ <u>ords = 1:</u><br>LL is always e | nabled (subject | to oscillator r | equirements)    |              |  |

| bit 6-3<br>$IRCF<3:0>: Internal Oscillator Frequency Select bits$ $1111 = 16 \text{ MHz HF or 32 MHz HF}^{(2)}$ $1110 = 8 \text{ MHz or 32 MHz HF}^{(2)}$ $1101 = 4 \text{ MHz HF}$ $1000 = 2 \text{ MHz HF}$ $1010 = 500 \text{ kHz HF}^{(1)}$ $1001 = 250 \text{ kHz HF}^{(1)}$ $1000 = 125 \text{ kHz HF}^{(1)}$ $0111 = 500 \text{ kHz MF} (default upon Reset)$ $0110 = 250 \text{ kHz MF}$ $0101 = 125 \text{ kHz MF}$ $0101 = 125 \text{ kHz MF}$ $0101 = 31.25 \text{ kHz HF}^{(1)}$ $000x = 31 \text{ kHz LF}$ |                        |                                                                                                                                                                           |                                      |                 |                 |                 |              |  |

| oit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Unimpleme              | Unimplemented: Read as '0'                                                                                                                                                |                                      |                 |                 |                 |              |  |

| oit 1-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1x = Interna           | <b>SCS&lt;1:0&gt;:</b> System Clock Select bits<br>1x = Internal oscillator block<br>01 = Timer1 oscillator<br>00 = Clock determined by FOSC<2:0> in Configuration Words. |                                      |                 |                 |                 |              |  |

2: 32 MHz when SPLLEN bit is set. Refer to Section 6.2.2.6 "32 MHz Internal Oscillator Frequency Selection".

| R-1/q                                                                                                                                                                                                                     | R-0/q                                                                                                       | R-q/q                                                     | R-0/q          | R-0/q          | R-q/q                    | R-0/0            | R-0/q        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|----------------|----------------|--------------------------|------------------|--------------|

| T1OSCR                                                                                                                                                                                                                    | PLLR                                                                                                        | OSTS                                                      | HFIOFR         | HFIOFL         | MFIOFR                   | LFIOFR           | HFIOFS       |

| bit 7                                                                                                                                                                                                                     |                                                                                                             |                                                           |                |                |                          |                  | bit 0        |

|                                                                                                                                                                                                                           |                                                                                                             |                                                           |                |                |                          |                  |              |

| Legend:                                                                                                                                                                                                                   |                                                                                                             |                                                           |                |                |                          |                  |              |

| R = Readable                                                                                                                                                                                                              | bit                                                                                                         | W = Writable                                              | bit            | U = Unimpler   | mented bit, read         | l as '0'         |              |

| u = Bit is unch                                                                                                                                                                                                           | anged                                                                                                       | x = Bit is unkr                                           | nown           | -n/n = Value a | at POR and BO            | R/Value at all o | other Resets |

| '1' = Bit is set                                                                                                                                                                                                          |                                                                                                             | '0' = Bit is cle                                          | ared           | q = Condition  | al                       |                  |              |

| bit 7 <b>T1OSCR:</b> Timer1 Oscillator Ready bit<br><u>If T1OSCEN = 1</u> :<br>1 = Timer1 oscillator is ready<br>0 = Timer1 oscillator is not ready<br><u>If T1OSCEN = 0</u> :<br>1 = Timer1 clock source is always ready |                                                                                                             |                                                           |                |                |                          |                  |              |

| bit 6                                                                                                                                                                                                                     | <b>PLLR</b> 4x PLI<br>1 = 4x PLL<br>0 = 4x PLL                                                              | is ready                                                  |                |                |                          |                  |              |

| bit 5                                                                                                                                                                                                                     | 1 = Running                                                                                                 | lator Start-up Ti<br>g from the clock<br>g from an intern | defined by the | e FOSC<2:0> I  | oits of the Confi<br>00) | guration Word    | S            |

| bit 4                                                                                                                                                                                                                     | 1 = HFINTO                                                                                                  | h-Frequency lr<br>SC is ready<br>SC is not ready          |                | or Ready bit   |                          |                  |              |

| bit 3                                                                                                                                                                                                                     | 1 = HFINTO                                                                                                  | h-Frequency In<br>SC is at least 2<br>SC is not 2% a      | % accurate     | or Locked bit  |                          |                  |              |

| bit 2 MFIOFR: Medium-Frequency Internal Oscillator Ready bit<br>1 = MFINTOSC is ready<br>0 = MFINTOSC is not ready                                                                                                        |                                                                                                             |                                                           |                |                |                          |                  |              |

| bit 1                                                                                                                                                                                                                     | 1 LFIOFR: Low-Frequency Internal Oscillator Ready bit<br>1 = LFINTOSC is ready<br>0 = LFINTOSC is not ready |                                                           |                |                |                          |                  |              |

| bit 0                                                                                                                                                                                                                     |                                                                                                             |                                                           |                |                |                          |                  |              |

#### REGISTER 6-2: OSCSTAT: OSCILLATOR STATUS REGISTER

#### 8.6 Register Definitions: Interrupt Control

| R/W-0/0         | R/W-0/0                                                                                                                                                                                                   | R/W-0/0                                                    | R/W-0/0          | R/W-0/0      | R/W-0/0          | R/W-0/0 | R-0/0                |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|------------------|--------------|------------------|---------|----------------------|

| GIE             | PEIE                                                                                                                                                                                                      | TMR0IE                                                     | INTE             | IOCIE        | TMR0IF           | INTF    | IOCIF <sup>(1)</sup> |

| bit 7           |                                                                                                                                                                                                           |                                                            |                  |              |                  |         | bit (                |

| Legend:         |                                                                                                                                                                                                           |                                                            |                  |              |                  |         |                      |

| R = Readable    | bit                                                                                                                                                                                                       | W = Writable                                               | bit              | U = Unimplen | nented bit, read | as '0'  |                      |

| u = Bit is unch |                                                                                                                                                                                                           | x = Bit is unki                                            |                  | •            | at POR and BO    |         | ther Resets          |

| 1' = Bit is set |                                                                                                                                                                                                           | '0' = Bit is cle                                           |                  |              |                  |         |                      |

| bit 7           | GIE: Global II                                                                                                                                                                                            | nterrupt Enable                                            | > hit            |              |                  |         |                      |

|                 |                                                                                                                                                                                                           | all active interru                                         |                  |              |                  |         |                      |

| pit 6           | 1 = Enables a                                                                                                                                                                                             | eral Interrupt E<br>all active periph<br>all peripheral ir | neral interrupts | 3            |                  |         |                      |

| bit 5           | 1 = Enables t                                                                                                                                                                                             | er0 Overflow Ir<br>he Timer0 inte<br>the Timer0 inte       | rrupt            | e bit        |                  |         |                      |

| bit 4           | 1 = Enables t                                                                                                                                                                                             | ternal Interrupt<br>he INT externa<br>the INT externa      | l interrupt      |              |                  |         |                      |

| oit 3           | <b>IOCIE:</b> Interrupt-on-Change Enable bit<br>1 = Enables the interrupt-on-change<br>0 = Disables the interrupt-on-change                                                                               |                                                            |                  |              |                  |         |                      |

| bit 2           | <ul> <li>TMR0IF: Timer0 Overflow Interrupt Flag bit</li> <li>1 = TMR0 register has overflowed</li> <li>0 = TMR0 register did not overflow</li> </ul>                                                      |                                                            |                  |              |                  |         |                      |

| bit 1           | <ul> <li>INTF: INT External Interrupt Flag bit</li> <li>1 = The INT external interrupt occurred</li> <li>0 = The INT external interrupt did not occur</li> </ul>                                          |                                                            |                  |              |                  |         |                      |

| bit 0           | <b>IOCIF:</b> Interrupt-on-Change Interrupt Flag bit <sup>(1)</sup><br>1 = When at least one of the interrupt-on-change pins changed state<br>0 = None of the interrupt-on-change pins have changed state |                                                            |                  |              |                  |         |                      |

#### REGISTER 8-1: INTCON: INTERRUPT CONTROL REGISTER

**Note 1:** The IOCIF Flag bit is read-only and cleared when all the Interrupt-on-change flags in the IOCBF register have been cleared by software.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### EXAMPLE 12-5: WRITING TO FLASH PROGRAM MEMORY

|                      | LE 12-J.    |                    |                                                                         |

|----------------------|-------------|--------------------|-------------------------------------------------------------------------|

| ; This               | write rout  | tine assumes the f | ollowing:                                                               |

| ; 1. Tł              | ne 16 bytes | s of data are load | led, starting at the address in DATA_ADDR                               |

| ; 2. Ea              | ach word of | f data to be writt | en is made up of two adjacent bytes in DATA_ADDR,                       |

| ; st                 | tored in li | ittle endian forma | t                                                                       |

| ; 3. A               | valid star  | rting address (the | e least significant bits = 0000) is loaded in ADDRH:ADDRL               |

| ; 4. AI              | DDRH and AI | DDRL are located i | n shared data memory 0x70 - 0x7F (common RAM)                           |

| ;                    |             |                    |                                                                         |

|                      | BCF         | INTCON,GIE         | ; Disable ints so required sequences will execute properly              |

|                      | BANKSEL     | EEADRH             | ; Bank 3                                                                |

|                      | MOVF        | ADDRH,W            | ; Load initial address                                                  |

|                      | MOVWF       | EEADRH             | ;                                                                       |

|                      | MOVF        | ADDRL,W            | ;                                                                       |

|                      | MOVWF       | EEADRL             | ;                                                                       |

|                      | MOVLW       | LOW DATA_ADDR      | ; Load initial data address                                             |

|                      | MOVWF       | FSROL              | ;                                                                       |

|                      | MOVLW       | HIGH DATA_ADDR     | ; Load initial data address                                             |

|                      | MOVWF       | FSROH              | ;                                                                       |

|                      | BSF         | EECON1, EEPGD      | ; Point to program memory                                               |

|                      | BCF         | EECON1,CFGS        | ; Not configuration space                                               |

|                      | BSF         |                    | ; Enable writes                                                         |

|                      | BSF         | EECON1,LWLO        | ; Only Load Write Latches                                               |

| LOOP                 |             | -                  |                                                                         |

|                      | MOVIW       | FSR0++             | ; Load first data byte into lower                                       |

|                      | MOVWF       |                    | i                                                                       |

|                      | MOVIW       | FSR0++             | ; Load second data byte into upper                                      |

|                      | MOVWF       | EEDATH             | i                                                                       |

|                      |             |                    |                                                                         |

|                      | MOVF        | EEADRL,W           | ; Check if lower bits of address are '000'                              |

|                      | XORLW       | 0x0F               | ; Check if we're on the last of 16 addresses                            |

|                      | ANDLW       | 0x0F               | ;                                                                       |

|                      | BTFSC       | STATUS, Z          | ; Exit if last of 16 words,                                             |

|                      | GOTO        | START_WRITE        | ;                                                                       |

|                      | MOVLW       | 55h                | ; Start of required write sequence:                                     |

|                      | MOVWF       |                    | ; Write 55h                                                             |

| 0                    | MOVLW       |                    | ;                                                                       |

| ed<br>nce            | MOVWF       |                    | ; Write AAh                                                             |

| Required<br>Sequence | BSF         |                    | ; Set WR bit to begin write                                             |

| Seq                  | NOP         |                    | ; Any instructions here are ignored as processor                        |

| ш (у                 | NOT         |                    | ; halts to begin write sequence                                         |

|                      | NOP         |                    | ; Processor will stop here and wait for write to complete.              |

|                      |             |                    | ; After write processor continues with 3rd instruction.                 |

|                      | TNGE        |                    |                                                                         |

|                      | INCF        |                    | ; Still loading latches Increment address<br>; Write next latches       |

|                      | GOTO        | TOOL               | , WIILE MEAL LAUGHES                                                    |

| START_V              | WR T T F    |                    |                                                                         |

| DIANI_               | BCF         | EECON1,LWLO        | ; No more loading latches - Actually start Flash program                |

|                      | 201         |                    | <pre>/ memory write</pre>                                               |

|                      |             |                    |                                                                         |

|                      | MOVLW       | 55h                | ; Start of required write sequence:                                     |

|                      | MOVWF       |                    | / Write 55h                                                             |

| ъg                   | MOVLW       |                    | ;                                                                       |

| enc                  | MOVWF       |                    | ; Write AAh                                                             |

| Required<br>Sequence | BSF         |                    | ; Set WR bit to begin write                                             |

| Se                   | NOP         |                    | ; Any instructions here are ignored as processor                        |

|                      |             |                    | ; halts to begin write sequence                                         |

|                      | NOP         |                    | ; Processor will stop here and wait for write complete.                 |

| L                    |             |                    | · ofter write processor continues with 2nd instanction                  |

|                      | DCF         |                    | ; after write processor continues with 3rd instruction ; Disable writes |

|                      | BCF<br>BSF  |                    | ; Disable writes<br>; Enable interrupts                                 |

|                      | 101         | THICON, GTE        | , maste meetrapes                                                       |

|                      |             |                    |                                                                         |

### 13.2 Register Definitions: Alternate Pin Function Control

#### REGISTER 13-1: APFCON1: ALTERNATE PIN FUNCTION CONTROL 1 REGISTER

| R/W-0/0          | R/W-0/0                     | R/W-0/0                                                                                  | R/W-0/0         | R/W-0/0         | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |  |  |

|------------------|-----------------------------|------------------------------------------------------------------------------------------|-----------------|-----------------|------------------|------------------|--------------|--|--|--|

| C2OUTSEL         | CCP1SEL                     | SDOSEL                                                                                   | SCKSEL          | SDISEL          | TXSEL            | RXSEL            | CCP2SEL      |  |  |  |

| bit 7            | •                           |                                                                                          |                 |                 |                  | •                | bit (        |  |  |  |

| Legend:          |                             |                                                                                          |                 |                 |                  |                  |              |  |  |  |

| R = Readable     | bit                         | W = Writable                                                                             | bit             | U = Unimplen    | nented bit, read | l as '0'         |              |  |  |  |

| u = bit is uncha | anged                       | x = Bit is unkr                                                                          | nown            | -n/n = Value a  | at POR and BO    | R/Value at all o | other Resets |  |  |  |

| '1' = Bit is set | -                           | '0' = Bit is clea                                                                        | ared            |                 |                  |                  |              |  |  |  |

|                  |                             |                                                                                          |                 |                 |                  |                  |              |  |  |  |

| bit 7            |                             | C2OUT Pin Se                                                                             | lection bit     |                 |                  |                  |              |  |  |  |

|                  | 1 = C2OUT<br>0 = C2OUT      |                                                                                          |                 |                 |                  |                  |              |  |  |  |

| bit 6            |                             | •                                                                                        | out Pin Selecti | on bit          |                  |                  |              |  |  |  |

|                  |                             | <b>CCP1SEL</b> : CCP1 Input/Output Pin Selection bit<br>1 = CCP1 is on pin RB0           |                 |                 |                  |                  |              |  |  |  |

|                  |                             | 0 = CCP1 is on pin RC2                                                                   |                 |                 |                  |                  |              |  |  |  |

| bit 5            | SDOSEL: MS                  | SDOSEL: MSSP SDO Pin Selection bit                                                       |                 |                 |                  |                  |              |  |  |  |

|                  | 1 = SDO is on pin RB5       |                                                                                          |                 |                 |                  |                  |              |  |  |  |

|                  | 0 = SDO is on pin RC5       |                                                                                          |                 |                 |                  |                  |              |  |  |  |

| bit 4            |                             | SSP Serial Clock (SCL/SCK) Pin Selection bit                                             |                 |                 |                  |                  |              |  |  |  |

|                  | 1 = SCL/SCK is on pin RB7   |                                                                                          |                 |                 |                  |                  |              |  |  |  |

|                  |                             | 0 = SCL/SCK is on pin RC3<br>SDISEL: MSSP Serial Data (SDA/SDI) Output Pin Selection bit |                 |                 |                  |                  |              |  |  |  |

| bit 3            |                             | I is on pin RB6                                                                          | (SDA/SDI) OU    | Itput Pin Selec | tion dit         |                  |              |  |  |  |

|                  |                             | l is on pin RC4                                                                          |                 |                 |                  |                  |              |  |  |  |

| bit 2            |                             | Pin Selection bit                                                                        |                 |                 |                  |                  |              |  |  |  |

| 5.1 2            | 1 = TX is on pin RB6        |                                                                                          |                 |                 |                  |                  |              |  |  |  |

|                  | 0 = TX is on pin RC6        |                                                                                          |                 |                 |                  |                  |              |  |  |  |

| bit 1            | RXSEL: RX Pin Selection bit |                                                                                          |                 |                 |                  |                  |              |  |  |  |

|                  | 1 = RX is on pin RB7        |                                                                                          |                 |                 |                  |                  |              |  |  |  |

|                  | 0 = RX is on pin RC7        |                                                                                          |                 |                 |                  |                  |              |  |  |  |

| bit 0            | CCP2SEL: C                  | CP2 Input/Outp                                                                           | out Pin Selecti | on bit          |                  |                  |              |  |  |  |

|                  | 1 = CCP2 is                 |                                                                                          |                 |                 |                  |                  |              |  |  |  |

|                  | 0 = CCP2 is                 | on pin RC1                                                                               |                 |                 |                  |                  |              |  |  |  |

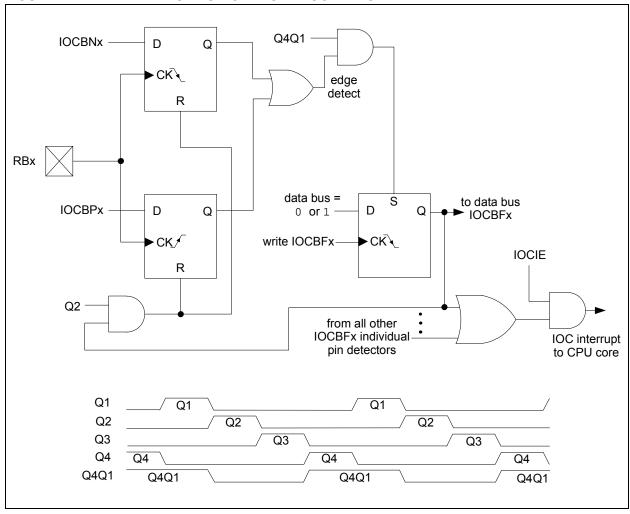

#### FIGURE 14-1: INTERRUPT-ON-CHANGE BLOCK DIAGRAM

### 17.1 ADC Configuration

When configuring and using the ADC the following functions must be considered:

- · Port configuration

- · Channel selection

- Single-ended

- Differential

- ADC voltage reference selection

- ADC conversion clock source

- · Interrupt control

- · Result formatting

#### 17.1.1 PORT CONFIGURATION

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ANSEL bits. Refer to **Section 13.0 "I/O Ports"** for more information.

| Note: | Analog voltages on any pin that is defined |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|

|       | as a digital input may cause the input     |  |  |  |  |  |

|       | buffer to conduct excess current.          |  |  |  |  |  |

#### 17.1.2 CHANNEL SELECTION

There are up to 18 channel selections available:

- AN<13:8, 4:0> pins (PIC16(L)F1788 only)

- AN<21, 13:0> pins (PIC16(L)F1789 only)

- Temperature Indicator

- DAC\_output

- FVR (Fixed Voltage Reference) Output

Refer to Section 15.0 "Fixed Voltage Reference (FVR)" and Section 16.0 "Temperature Indicator Module" for more information on these channel selections.

When converting differential signals, the negative input for the channel is selected with the CHSN<3:0> bits of the ADCON2 register. Any positive input can be paired with any negative input to determine the differential channel.

The CHS<4:0> bits of the ADCON0 register determine which positive channel is selected.

When CHSN<3:0> = 1111 then the ADC is effectively a single ended ADC converter.

When changing channels, a delay is required before starting the next conversion.

#### 17.1.3 ADC VOLTAGE REFERENCE

The ADPREF bits of the ADCON1 register provide control of the positive voltage reference. The positive voltage reference can be:

- VREF+

- VDD

- FVR Buffer1

The ADNREF bits of the ADCON1 register provide control of the negative voltage reference. The negative voltage reference can be:

- VREF- pin

- Vss

See **Section 15.0** "Fixed Voltage Reference (FVR)" for more details on the Fixed Voltage Reference.

#### 17.1.4 CONVERSION CLOCK

The source of the conversion clock is software selectable via the ADCS bits of the ADCON1 register. There are seven possible clock options:

- Fosc/2

- Fosc/4

- Fosc/8

- Fosc/16

- Fosc/32

- Fosc/64

- FRC (dedicated internal FRC oscillator)

The time to complete one bit conversion is defined as TAD. One full 12-bit conversion requires 15 TAD periods as shown in Figure 17-2.

For correct conversion, the appropriate TAD specification must be met. Refer to the ADC conversion requirements in **Section 31.0 "Electrical Specifications"** for more information. Table 17-1 gives examples of appropriate ADC clock selections.

**Note:** Unless using the FRC, any changes in the system clock frequency will change the ADC clock frequency, which may adversely affect the ADC result.

### 23.11 Register Definitions: Timer1 Control

т

#### REGISTER 23-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0/u          | R/W-0/u                                                                                                                                        | R/W-0/u                                        | R/W-0/u         | R/W-0/u          | R/W-0/u          | U-0            | R/W-0/u      |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-----------------|------------------|------------------|----------------|--------------|--|--|--|

| TMR1             | CS<1:0>                                                                                                                                        | T1CKP                                          | S<1:0>          | T1OSCEN          | T1SYNC           | —              | TMR10N       |  |  |  |

| bit 7            |                                                                                                                                                |                                                |                 |                  |                  |                |              |  |  |  |

|                  |                                                                                                                                                |                                                |                 |                  |                  |                |              |  |  |  |

| Legend:          |                                                                                                                                                |                                                |                 |                  |                  |                |              |  |  |  |

| R = Readable     |                                                                                                                                                | W = Writable I                                 |                 | •                | nented bit, read |                |              |  |  |  |

| u = Bit is unc   | •                                                                                                                                              | x = Bit is unkn                                |                 | -n/n = Value a   | at POR and BOF   | R/Value at all | other Resets |  |  |  |

| '1' = Bit is set | t                                                                                                                                              | '0' = Bit is clea                              | ared            |                  |                  |                |              |  |  |  |

| bit 7-6          | TMR1CS<1:                                                                                                                                      | 0>: Timer1 Cloc                                | k Source Sele   | ect bits         |                  |                |              |  |  |  |

|                  | 11 = Reserved, do not use.                                                                                                                     |                                                |                 |                  |                  |                |              |  |  |  |

|                  | 10 = Timer1                                                                                                                                    | 10 = Timer1 clock source is pin or oscillator: |                 |                  |                  |                |              |  |  |  |

|                  |                                                                                                                                                | If TIOSCEN = 0:                                |                 |                  |                  |                |              |  |  |  |

|                  | External clock from T1CKI pin (on the rising edge)<br>I <u>f T1OSCEN = 1</u> :                                                                 |                                                |                 |                  |                  |                |              |  |  |  |

|                  | Crystal oscillator on T1OSI/T1OSO pins                                                                                                         |                                                |                 |                  |                  |                |              |  |  |  |

|                  | 01 = Timer1 clock source is system clock (Fosc)                                                                                                |                                                |                 |                  |                  |                |              |  |  |  |

|                  | 00 = Timer1                                                                                                                                    | clock source is                                | instruction clo | ock (Fosc/4)     |                  |                |              |  |  |  |

| bit 5-4          | T1CKPS<1:0>: Timer1 Input Clock Prescale Select bits                                                                                           |                                                |                 |                  |                  |                |              |  |  |  |

|                  | 11 = 1:8 Prescale value                                                                                                                        |                                                |                 |                  |                  |                |              |  |  |  |

|                  | 10 = 1:4 Prescale value                                                                                                                        |                                                |                 |                  |                  |                |              |  |  |  |

|                  | 01 = 1:2 Prescale value<br>00 = 1:1 Prescale value                                                                                             |                                                |                 |                  |                  |                |              |  |  |  |

| bit 3            | T1OSCEN:                                                                                                                                       | LP Oscillator En                               | able Control b  | bit              |                  |                |              |  |  |  |

|                  | 1 = Dedicated Timer1 oscillator circuit enabled                                                                                                |                                                |                 |                  |                  |                |              |  |  |  |

|                  | 0 = Dedicated Timer1 oscillator circuit disabled                                                                                               |                                                |                 |                  |                  |                |              |  |  |  |

| bit 2            | T1SYNC: Timer1 Synchronization Control bit                                                                                                     |                                                |                 |                  |                  |                |              |  |  |  |

|                  | <ul> <li>1 = Do not synchronize asynchronous clock input</li> <li>0 = Synchronize asynchronous clock input with system clock (Fosc)</li> </ul> |                                                |                 |                  |                  |                |              |  |  |  |

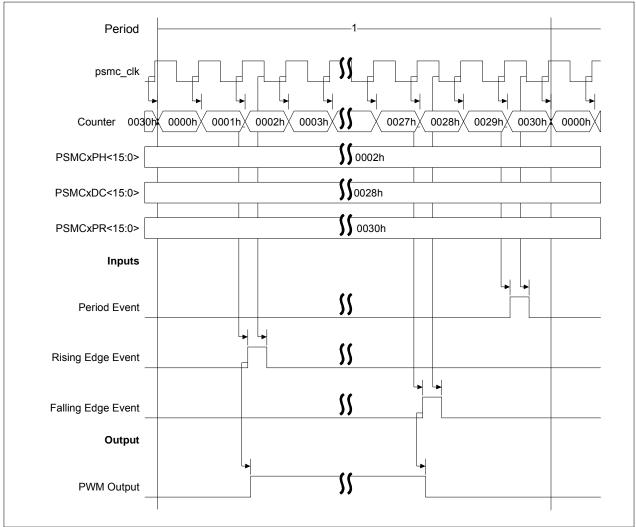

|                  | -                                                                                                                                              |                                                | •               | it with system c | lock (Fosc)      |                |              |  |  |  |