Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betalls                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                               |

| Number of I/O              | 35                                                                        |

| Program Memory Size        | 28KB (16K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 2K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 14x12b; D/A 1x8b, 3x5b                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 44-QFN (8x8)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1789-e-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **PIN ALLOCATION TABLE**

| TAB        | LE 1:                       |             | 28   | -PIN ALLO                                                 | OCATIO                               | N TABLI                 | E (PIC16(I                                   | _)F1788        | B)                                           | ÷                   | -                                      |                                          | -          | _       | ÷                      |

|------------|-----------------------------|-------------|------|-----------------------------------------------------------|--------------------------------------|-------------------------|----------------------------------------------|----------------|----------------------------------------------|---------------------|----------------------------------------|------------------------------------------|------------|---------|------------------------|

| 0/1        | 28-Pin SPDIP,<br>SOIC, SSOP | 28-Pin QFN, | ADC  | Reference                                                 | Comparator                           | Operation<br>Amplifiers | 8-bit/<br>5-bit DAC                          | Timers         | PSMC                                         | ССР                 | EUSART                                 | MSSP                                     | Interrupt  | dn-llud | Basic                  |

| RA0        | 2                           | 27          | AN0  | —                                                         | C1IN0-<br>C2IN0-<br>C3IN0-<br>C4IN0- |                         | —                                            | _              | _                                            | _                   |                                        | SS <sup>(1)</sup>                        | IOC        | Y       | —                      |

| RA1        | 3                           | 28          | AN1  | _                                                         | C1IN1-<br>C2IN1-<br>C3IN1-<br>C4IN1- | OPA1OUT                 | _                                            | _              | _                                            | _                   | _                                      | _                                        | IOC        | Y       | —                      |

| RA2        | 4                           | 1           | AN2  | VREF-<br>DAC1VREF-                                        | C1IN0+<br>C2IN0+<br>C3IN0+<br>C4IN0+ |                         | DAC1OUT1                                     | _              | _                                            | _                   | _                                      | -                                        | IOC        | Y       | _                      |

| RA3        | 5                           | 2           | AN3  | VREF+<br>DAC1VREF+<br>DAC2VREF+<br>DAC3VREF+<br>DAC4VREF+ | C1IN1+                               |                         | _                                            | _              | _                                            | _                   |                                        | _                                        | IOC        | Y       | _                      |

| RA4        | 6                           | 3           |      | —                                                         | C10UT                                | OPA1IN+                 | DAC4OUT1                                     | T0CKI          | _                                            | _                   |                                        | _                                        | IOC        | Y       |                        |

| RA5        | 7                           | 4           | AN4  | —                                                         | C2OUT                                | OPA1IN-                 | DAC2OUT1                                     | —              | —                                            | _                   |                                        | SS                                       | IOC        | Υ       | —                      |

| RA6        | 10                          | 7           | _    | _                                                         | C2OUT <sup>(1)</sup>                 | _                       | _                                            | -              | _                                            | -                   | —                                      | _                                        | IOC        | Y       | VCAP<br>OSC2<br>CLKOUT |

| RA7        | 9                           | 6           | _    | _                                                         | _                                    | _                       | _                                            | _              | PSMC1CLK<br>PSMC2CLK<br>PSMC3CLK<br>PSMC4CLK | —                   | _                                      | -                                        | IOC        | Y       | CLKIN<br>OSC1          |

| RB0        | 21                          | 18          | AN12 | _                                                         | C2IN1+                               | _                       | _                                            | —              | PSMC1IN<br>PSMC2IN<br>PSMC3IN<br>PSMC4IN     | CCP1 <sup>(1)</sup> | _                                      | —                                        | INT<br>IOC | Y       | —                      |

| RB1        | 22                          | 19          | AN10 | _                                                         | C1IN3-<br>C2IN3-<br>C3IN3-<br>C4IN3- | OPA2OUT                 | _                                            | —              | _                                            | —                   | _                                      | _                                        | IOC        | Y       | —                      |

| RB2        | 23                          | 20          | AN8  | —                                                         | -                                    | OPA2IN-                 | DAC3OUT1                                     | _              | _                                            | _                   |                                        | —                                        | IOC        | Υ       | CLKR                   |

| RB3        | 24                          | 21          | AN9  | _                                                         | C1IN2-<br>C2IN2-<br>C3IN2-           | OPA2IN+                 | _                                            | —              | _                                            | CCP2 <sup>(1)</sup> | -                                      | -                                        | IOC        | Y       | —                      |

| RB4        | 25                          | 22          | AN11 | —                                                         | C3IN1+                               | 1                       | —                                            | —              | —                                            | —                   | -                                      | SS <sup>(1)</sup>                        | IOC        | Υ       | —                      |

| RB5<br>RB6 | 26<br>27                    | 23<br>24    | AN13 | -                                                         | C4IN2-<br>C3OUT<br>C4IN1+            | -                       | -                                            | T1G            | -                                            | CCP3 <sup>(1)</sup> | —<br>TX <sup>(1)</sup>                 | SDO <sup>(1)</sup>                       |            | Y       | -<br>ICSPCLK           |

| RDU        | 21                          | 24          | _    | _                                                         | C4IN1+                               | _                       | _                                            | _              | _                                            | _                   | CK <sup>(1)</sup>                      | SDA <sup>(1)</sup>                       | 100        | T       | ICOPULK                |

| RB7        | 28                          | 25          | _    | _                                                         | -                                    | _                       | DAC1OUT2<br>DAC2OUT2<br>DAC3OUT2<br>DAC4OUT2 | _              | -                                            | _                   | RX <sup>(1)</sup><br>DT <sup>(1)</sup> | SCK <sup>(1)</sup><br>SCL <sup>(1)</sup> | IOC        | Y       | ICSPDAT                |

| RC0        | 11                          | 8           |      | —                                                         | —                                    | —                       | —                                            | T1CKI<br>T1OSO | PSMC1A                                       | —                   |                                        | —                                        | IOC        | Y       | —                      |

| RC1        | 12                          | 9           | -    | _                                                         | _                                    | _                       | _                                            | T10SI          | PSMC1B                                       | CCP2                | -                                      | -                                        | IOC        | Y       | —                      |

| RC2        | 13                          | 10          | -    | —                                                         | _                                    | —                       | _                                            | _              | PSMC1C<br>PSMC3B                             | CCP1                | _                                      | -                                        | 100        | Y       | —                      |

| RC3        | 14<br>15                    | 11<br>12    | -    | _                                                         | _                                    | _                       | _                                            | _              | PSMC1D<br>PSMC4A<br>PSMC1E                   | _                   | _                                      | SCK<br>SCL<br>SDI                        | IOC        | Y       | _                      |

| RC4        | 15                          | 12          |      | _                                                         | _                                    | _                       | _                                            | _              | PSMC1E<br>PSMC4B<br>PSMC1F                   | _                   | _                                      | SDI<br>SDA<br>SDO                        | IOC        | ř<br>Y  | _                      |

| Note       | 1.                          |             |      | function select                                           |                                      |                         |                                              |                | PSMC3A                                       |                     |                                        | -                                        |            |         |                        |

| TABLE 1: | 28-PIN ALLOCATION TABLE (PIC16(L)F1788) |

|----------|-----------------------------------------|

| IABLE 1: | 28-PIN ALLUCATION TABLE (PICTO(L)FT/88) |

Note 1: Alternate pin function selected with the APFCON1 (Register 13-1) and APFCON2 (Register 13-2) registers.

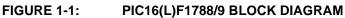

### 1.0 DEVICE OVERVIEW

The PIC16(L)F1788/9 are described within this data sheet. The block diagram of these devices are shown in Figure 1-1. The available peripherals are shown in Table 1-1, and the pin out descriptions are shown in Tables 1-2 and 1-3.

| Peripheral                        |                 | PIC16(L)F1782 | PIC16(L)F1783 | PIC16(L)F1784 | PIC16(L)F1786 | PIC16(L)F1787 | PIC16(L)F1788 | PIC16(L)F1789 |

|-----------------------------------|-----------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|

| Analog-to-Digital Converter (ADC) | ٠               | •             | •             | •             | •             | •             | •             |               |

| Fixed Voltage Reference (FVR)     |                 | ٠             | •             | •             | ٠             | ٠             | ٠             | ٠             |

| Reference Clock Module            |                 | ٠             | •             | •             | •             | •             | ٠             | •             |

| Temperature Indicator             |                 | ٠             | •             | •             | •             | •             | ٠             | •             |

| Capture/Compare/PWM (CCP/ECCF     | P) Modules      |               | •             |               |               |               |               |               |

|                                   | CCP1            | ٠             | •             | •             | •             | •             | •             | •             |

|                                   | CCP2            | ٠             | •             | •             | •             | •             | •             | •             |

|                                   | CCP3            |               |               | •             | •             | •             | •             | •             |

| Comparators                       |                 |               |               |               |               |               |               |               |

|                                   | C1              | ٠             | •             | •             | •             | •             | •             | •             |

|                                   | C2              | ٠             | •             | •             | •             | •             | ٠             | ٠             |

|                                   | C3              | ٠             | •             | •             | •             | •             | ٠             | •             |

|                                   | C4              |               |               | •             | •             | •             | •             | •             |

| Digital-to-Analog Converter (DAC) | •               |               |               | -             |               |               |               |               |

|                                   | (8-bit DAC) D1  | ٠             | •             | •             | •             | •             | •             | •             |

|                                   | (5-bit DAC) D2  |               |               |               |               |               | •             | •             |

|                                   | (5-bit DAC) D3  |               |               |               |               |               | •             | •             |

|                                   | (5-bit DAC) D4  |               |               |               |               |               | •             | •             |

| Enhanced Universal Synchronous/As | ynchronous Rece | iver/Trar     | nsmitter      | (EUSAR        | T)            |               |               |               |

|                                   | EUSART          | •             | •             | •             | •             | •             | •             | •             |

| Master Synchronous Serial Ports   |                 |               |               |               |               |               |               |               |

|                                   | MSSP            | ٠             | •             | •             | •             | •             | •             | •             |

| Op Amp                            | •               |               |               | -             |               |               |               |               |

|                                   | Op Amp 1        | •             | •             | •             | •             | •             | •             | •             |

|                                   | Op Amp 2        | •             | •             | •             | •             | •             | •             | •             |

|                                   | Op Amp 3        |               |               | •             |               | •             |               | •             |

| Programmable Switch Mode Control  | ler (PSMC)      |               |               |               |               |               |               |               |

|                                   | PSMC1           | •             | •             | •             | •             | •             | •             | •             |

|                                   | PSMC2           | •             | •             | •             | •             | •             | •             | •             |

|                                   | PSMC3           |               |               | •             | •             | •             | •             | •             |

|                                   | PSMC4           |               |               |               |               |               | •             | •             |

| Timers                            |                 |               |               |               |               |               |               |               |

|                                   | Timer0          | •             | •             | •             | •             | •             | •             | •             |

|                                   | Timer1          | •             | •             | •             | •             | •             | •             | •             |

|                                   | Timer2          | •             | •             | •             | •             | •             | •             | •             |

## PIC16(L)F1788/9

# PIC16(L)F1788/9

| <b>TABLE 3-12:</b> | SPECIAL FUNCTION REGISTER SUMMARY ( | (CONTINUED) | 1 |

|--------------------|-------------------------------------|-------------|---|

|                    |                                     |             |   |

| TABLE 3-12: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) |                 |                |               |          |          |          |                |                |         |                      |                                 |

|-----------------------------------------------------------|-----------------|----------------|---------------|----------|----------|----------|----------------|----------------|---------|----------------------|---------------------------------|

| Addr                                                      | Name            | Bit 7          | Bit 6         | Bit 5    | Bit 4    | Bit 3    | Bit 2          | Bit 1          | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

| Banl                                                      | c 29 (Continued | d)             |               |          |          |          |                |                |         |                      |                                 |

| EB1h                                                      | PSMC2CON        | PSMC2EN        | PSMC2LD       | P2DBFE   | P2DBRE   |          | P2MOD          | )E<3:0>        |         | 0000 0000            | 0000 0000                       |

| EB2h                                                      | PSMC2MDL        | P2MDLEN        | P2MDLPOL      | P2MDLBIT | —        |          | P2MSR          | RC<3:0>        |         | 000- 0000            | 000- 0000                       |

| EB3h                                                      | PSMC2SYNC       | P2POFST        | P2PRPOL       | P2DCPOL  |          | —        |                | P2SYNC<2:0>    | •       | 000000               | 000000                          |

| EB4h                                                      | PSMC2CLK        | —              | _             | P2CPF    | RE<1:0>  | —        | —              | P2CSR          | C<1:0>  | 0000                 | 0000                            |

| EB5h                                                      | PSMC2OEN        | —              | —             | —        |          | —        | —              | P2OEB          | P2OEA   | 00                   | 00                              |

| EB6h                                                      | PSMC2POL        | —              | P2INPOL       | —        |          | —        | —              | P2POLB         | P2POLA  | -000                 | -000                            |

| EB7h                                                      | PSMC2BLNK       | —              | _             | P2FEB    | M<1:0>   | —        | —              | P2REB          | M<1:0>  | 0000                 | 0000                            |

| EB8h                                                      | PSMC2REBS       | P2REBSIN       | _             | —        | P2REBSC4 | P2REBSC3 | P2REBSC2       | P2REBSC1       | _       | 00 000-              | 00 000-                         |

| EB9h                                                      | PSMC2FEBS       | P2FEBSIN       |               | —        | P2FEBSC4 | P2FEBSC3 | P2FEBSC2       | P2FEBSC1       | —       | 00 000-              | 00 000-                         |

| EBAh                                                      | PSMC2PHS        | P2PHSIN        |               | —        | P2PHSC4  | P2PHSC3  | P2PHSC2        | P2PHSC1        | P2PHST  | 00 0000              | 00 0000                         |

| EBBh                                                      | PSMC2DCS        | P2DCSIN        |               | —        | P2DCSC4  | P2DCSC3  | P2DCSC2        | P2DCSC1        | P2DCST  | 00 0000              | 00 0000                         |

| EBCh                                                      | PSMC2PRS        | P2PRSIN        |               | —        | P2PRSC4  | P2PRSC3  | P2PRSC2        | P2PRSC1        | P2PRST  | 00 0000              | 00 0000                         |

| EBDh                                                      | PSMC2ASDC       | P2ASE          | P2ASDEN       | P2ARSEN  |          | —        | —              | —              | P2ASDOV | 0000                 | 0000                            |

| EBEh                                                      | PSMC2ASDL       | —              | _             | —        |          | —        | —              | P2ASDLB        | P2ASDLA | 00                   | 00                              |

| EBFh                                                      | PSMC2ASDS       | P2ASDSIN       | _             | —        | P2ASDSC4 | P2ASDSC3 | P2ASDSC2       | P2ASDSC1       | _       | 00 000-              | 00 000-                         |

| EC0h                                                      | PSMC2INT        | P2TOVIE        | P2TPHIE       | P2TDCIE  | P2TPRIE  | P2TOVIF  | P2TPHIF        | P2TDCIF        | P2TPRIF | 0000 0000            | 0000 0000                       |

| EC1h                                                      | PSMC2PHL        | Phase Low Co   | unt           |          |          |          |                |                |         | 0000 0000            | 0000 0000                       |

| EC2h                                                      | PSMC2PHH        | Phase High Co  | ount          |          |          |          |                |                |         | 0000 0000            | 0000 0000                       |

| EC3h                                                      | PSMC2DCL        | Duty Cycle Lov | w Count       |          |          |          |                |                |         | 0000 0000            | 0000 0000                       |

| EC4h                                                      | PSMC2DCH        | Duty Cycle Hig | gh Count      |          |          |          |                |                |         | 0000 0000            | 0000 0000                       |

| EC5h                                                      | PSMC2PRL        | Period Low Co  | ount          |          |          |          |                |                |         | 0000 0000            | 0000 0000                       |

| EC6h                                                      | PSMC2PRH        | Period High Co | ount          |          |          |          |                |                |         | 0000 0000            | 0000 0000                       |

| EC7h                                                      | PSMC2TMRL       | Time base Lov  | v Counter     |          |          |          |                |                |         | 0000 0001            | 0000 0001                       |

| EC8h                                                      | PSMC2TMRH       | Time base Hig  | h Counter     |          |          |          |                |                |         | 0000 0000            | 0000 0000                       |

| EC9h                                                      | PSMC2DBR        | Rising Edge D  | ead-band Cou  | unter    |          |          |                |                |         | 0000 0000            | 0000 0000                       |

| ECAh                                                      | PSMC2DBF        | Falling Edge D | ead-band Co   | unter    |          |          |                |                |         | 0000 0000            | 0000 0000                       |

| ECBh                                                      | PSMC2BLKR       | Rising Edge B  | lanking Count | er       |          |          |                |                |         | 0000 0000            | 0000 0000                       |

| ECCh                                                      | PSMC2BLKF       | Falling Edge B | lanking Count | ter      |          |          |                |                |         | 0000 0000            | 0000 0000                       |

| ECDh                                                      | PSMC2FFA        | —              | —             | —        | —        | Frac     | tional Frequer | ncy Adjust Reg | ister   | 0000                 | 0000                            |

| ECEh                                                      | PSMC2STR0       | —              | —             | _        | _        | _        | _              | P2STRB         | P2STRA  | 01                   | 01                              |

| ECFh                                                      | PSMC2STR1       | P2SSYNC        | —             | _        | _        | _        | —              | P2LSMEN        | P2HSMEN | 000                  | 000                             |

| ED0h                                                      | _               | Unimplemente   | d             |          |          |          |                |                |         | _                    | _                               |

Legend:

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.

Shaded locations are unimplemented, read as '0'. Note 1:

These registers can be addressed from any bank. Unimplemented, read as '1'. 2:

3:

PIC16(L)F1789 only.

4: PIC16F1788/9 only.

#### 6.2 Clock Source Types

Clock sources can be classified as external or internal.

External clock sources rely on external circuitry for the clock source to function. Examples are: oscillator modules (EC mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes) and Resistor-Capacitor (RC) mode circuits.

Internal clock sources are contained within the oscillator module. The internal oscillator block has two internal oscillators and a dedicated Phase-Lock Loop (HFPLL) that are used to generate three internal system clock sources: the 16 MHz High-Frequency Internal Oscillator (HFINTOSC), 500 kHz (MFINTOSC) and the 31 kHz Low-Frequency Internal Oscillator (LFINTOSC).

The system clock can be selected between external or internal clock sources via the System Clock Select (SCS) bits in the OSCCON register. See **Section 6.3 "Clock Switching"** for additional information.

#### 6.2.1 EXTERNAL CLOCK SOURCES

An external clock source can be used as the device system clock by performing one of the following actions:

- Program the FOSC<2:0> bits in the Configuration Words to select an external clock source that will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to:

- Timer1 oscillator during run-time, or

- An external clock source determined by the value of the FOSC bits.

See Section 6.3 "Clock Switching" for more information.

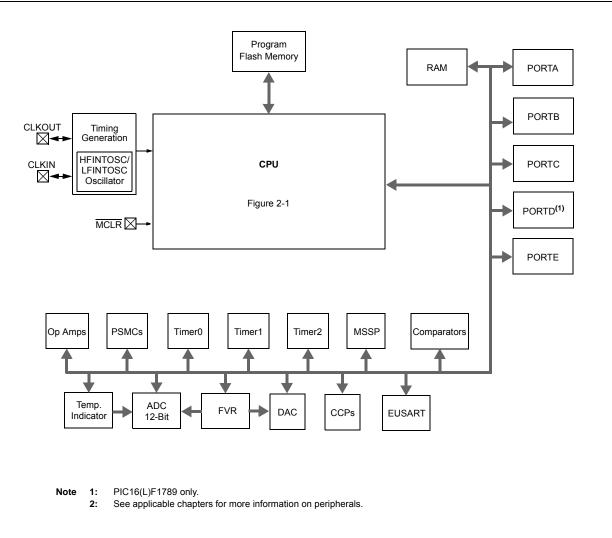

#### 6.2.1.1 EC Mode

The External Clock (EC) mode allows an externally generated logic level signal to be the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input. OSC2/CLKOUT is available for general purpose I/O or CLKOUT. Figure 6-2 shows the pin connections for EC mode.

EC mode has three power modes to select from through Configuration Words:

- High power, 4-32 MHz (FOSC = 111)

- Medium power, 0.5-4 MHz (FOSC = 110)

- Low power, 0-0.5 MHz (FOSC = 101)

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

#### EXTERNAL CLOCK (EC) MODE OPERATION

#### 6.2.1.2 LP, XT, HS Modes

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 6-3). The three modes select a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

**LP** Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 6-3 and Figure 6-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

#### 17.3 Register Definitions: ADC Control

#### REGISTER 17-1: ADCON0: ADC CONTROL REGISTER 0

| R/W-0/0          | R/W-0/0                                            | R/W-0/0                  | R/W-0/0          | R/W-0/0              | R/W-0/0           | R/W-0/0            | R/W-0/0 |

|------------------|----------------------------------------------------|--------------------------|------------------|----------------------|-------------------|--------------------|---------|

| ADRMD            |                                                    |                          | CHS<4:0>         |                      |                   | GO/DONE            | ADON    |

| it 7             |                                                    |                          |                  |                      |                   |                    | bit     |

|                  |                                                    |                          |                  |                      |                   |                    |         |

| egend:           |                                                    |                          |                  |                      |                   |                    |         |

| R = Readable     | bit                                                | W = Writable bi          | t                | U = Unimpleme        | ented bit, read a | is '0'             |         |

| u = Bit is uncha | anged                                              | x = Bit is unkno         | wn               | -n/n = Value at      | POR and BOR       | Value at all other | Resets  |

| 1' = Bit is set  |                                                    | '0' = Bit is clear       | ed               |                      |                   |                    |         |

|                  |                                                    |                          |                  |                      |                   |                    |         |

| bit 7            |                                                    | Result Mode bit          |                  |                      |                   |                    |         |

|                  |                                                    | and ADRESH pro           |                  |                      |                   |                    |         |

|                  |                                                    | and ADRESH pro           | ovide data form  | atted for a 12-bit   | result            |                    |         |

|                  | See Figure 17                                      |                          |                  | Calaat hita          |                   |                    |         |

| bit 6-2          |                                                    | ositive Differential     |                  |                      |                   |                    |         |

|                  | 11111 = FVF<br>11110 = DA(                         | R (Fixed Voltage R       |                  |                      |                   |                    |         |

|                  |                                                    | perature Indicato        | <sub>r</sub> (4) |                      |                   |                    |         |

|                  | 11100 = DA                                         |                          | 1 - 7            |                      |                   |                    |         |

|                  | 11011 = Res                                        |                          |                  |                      |                   |                    |         |

|                  | 11011 = Res                                        |                          |                  |                      |                   |                    |         |

|                  | 11001 = DA                                         |                          |                  |                      |                   |                    |         |

|                  | 11000 = DA                                         | C4 output <sup>(5)</sup> |                  |                      |                   |                    |         |

|                  | •                                                  |                          |                  |                      |                   |                    |         |

|                  | •                                                  |                          |                  |                      |                   |                    |         |

|                  | •                                                  |                          |                  |                      |                   |                    |         |

|                  | 10110 = Res                                        | erved. No channe         | el connected     |                      |                   |                    |         |

|                  | 10101 = AN2                                        | 21 <sup>(1)</sup>        |                  |                      |                   |                    |         |

|                  | 10100 = Res                                        | erved. No channe         | el connected     |                      |                   |                    |         |

|                  | •                                                  |                          |                  |                      |                   |                    |         |

|                  | •                                                  |                          |                  |                      |                   |                    |         |

|                  | •                                                  | and Marsham              |                  |                      |                   |                    |         |

|                  |                                                    | erved. No channe         | el connected.    |                      |                   |                    |         |

|                  | $01101 = AN^{2}$                                   |                          |                  |                      |                   |                    |         |

|                  | $01100 = AN^{2}$                                   |                          |                  |                      |                   |                    |         |

|                  | 01011 = AN <sup>2</sup><br>01010 = AN <sup>2</sup> |                          |                  |                      |                   |                    |         |

|                  | 01000 = AN                                         |                          |                  |                      |                   |                    |         |

|                  | 01001 = ANS                                        |                          |                  |                      |                   |                    |         |

|                  | 00111 = AN7                                        |                          |                  |                      |                   |                    |         |

|                  | 00110 = AN6                                        | <sub>3</sub> (1)         |                  |                      |                   |                    |         |

|                  | 00101 = ANS                                        | 5(1)                     |                  |                      |                   |                    |         |

|                  | 00100 = AN4                                        |                          |                  |                      |                   |                    |         |

|                  | 00011 = AN3                                        |                          |                  |                      |                   |                    |         |

|                  | 00010 = AN2                                        |                          |                  |                      |                   |                    |         |

|                  | 00001 = AN <sup>2</sup>                            | l                        |                  |                      |                   |                    |         |

|                  | 00000 = ANG                                        | )                        |                  |                      |                   |                    |         |

| oit 1            | GO/DONE: AI                                        | DC Conversion St         | atus bit         |                      |                   |                    |         |

|                  |                                                    | ersion cycle in pro      |                  | this bit starts an A | ADC conversion    | cycle.             |         |

|                  |                                                    | automatically clea       |                  |                      |                   | •                  |         |

|                  |                                                    | ersion completed/        | •                |                      |                   | •                  |         |

| oit O            | ADON: ADC E                                        | •                        |                  |                      |                   |                    |         |

|                  | 1 = ADC is en                                      |                          |                  |                      |                   |                    |         |

|                  |                                                    | abled and consur         | mes no operatir  | ng current           |                   |                    |         |

|                  |                                                    |                          |                  |                      |                   |                    |         |

|                  | C16(L)F1789 only                                   |                          |                  |                      | "for more inf-    | rmation            |         |

|                  |                                                    | 8-Bit Digital-to-A       | -                | • •                  |                   | mation.            |         |

|                  |                                                    | Fixed Voltage Re         |                  | " for more inform:   |                   |                    |         |

- 4: See Section 16.0 "Temperature Indicator Module" for more information.

- 5: See Section 20.0 "5-bit Digital-to-Analog Converter (DAC2/3/4) Modules" for more information.

#### 21.11 Register Definitions: Comparator Control

#### REGISTER 21-1: CMxCON0: COMPARATOR Cx CONTROL REGISTER 0

| R/W-0/0         | R-0/0                                                                                                                                       | R/W-0/0                                                                                                                                                     | R/W-0/0           | R/W-0/0        | R/W-1/1         | R/W-0/0        | R/W-0/0      |  |  |  |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------|-----------------|----------------|--------------|--|--|--|--|--|--|

| CxON            | CxOUT                                                                                                                                       | CxOE                                                                                                                                                        | CxPOL             | CxZLF          | CxSP            | CxHYS          | CxSYNC       |  |  |  |  |  |  |

| bit 7           |                                                                                                                                             |                                                                                                                                                             |                   | ·              |                 | •              | bit 0        |  |  |  |  |  |  |

|                 |                                                                                                                                             |                                                                                                                                                             |                   |                |                 |                |              |  |  |  |  |  |  |

| Legend:         |                                                                                                                                             |                                                                                                                                                             |                   |                |                 |                |              |  |  |  |  |  |  |

| R = Readable    |                                                                                                                                             | W = Writable                                                                                                                                                |                   |                | nented bit, rea |                |              |  |  |  |  |  |  |

| u = Bit is unc  | •                                                                                                                                           | x = Bit is unkr                                                                                                                                             |                   | -n/n = Value a | at POR and BC   | R/Value at all | other Resets |  |  |  |  |  |  |

| '1' = Bit is se | t                                                                                                                                           | '0' = Bit is cle                                                                                                                                            | ared              |                |                 |                |              |  |  |  |  |  |  |

| bit 7           | CxON: Com                                                                                                                                   | parator Enable                                                                                                                                              | bit               |                |                 |                |              |  |  |  |  |  |  |

|                 | 1 = Comparator is enabled                                                                                                                   |                                                                                                                                                             |                   |                |                 |                |              |  |  |  |  |  |  |

|                 | 0 = Comparator is disabled and consumes no active power                                                                                     |                                                                                                                                                             |                   |                |                 |                |              |  |  |  |  |  |  |

| bit 6           | CxOUT: Comparator Output bit                                                                                                                |                                                                                                                                                             |                   |                |                 |                |              |  |  |  |  |  |  |

|                 | $\frac{ f CxPOL = 1 (inverted polarity):}{1 - CxVD < CxVD}$                                                                                 |                                                                                                                                                             |                   |                |                 |                |              |  |  |  |  |  |  |

|                 | 1 = CxVP < CxVN $0 = CxVP > CxVN$                                                                                                           |                                                                                                                                                             |                   |                |                 |                |              |  |  |  |  |  |  |

|                 |                                                                                                                                             | ) (non-inverted )                                                                                                                                           | <u>oolarity):</u> |                |                 |                |              |  |  |  |  |  |  |

|                 | 1 = CxVP >                                                                                                                                  | 1 = CxVP > CxVN                                                                                                                                             |                   |                |                 |                |              |  |  |  |  |  |  |

|                 | 0 = CxVP <                                                                                                                                  | CxVN                                                                                                                                                        |                   |                |                 |                |              |  |  |  |  |  |  |

| bit 5           |                                                                                                                                             | parator Output I                                                                                                                                            |                   |                |                 |                |              |  |  |  |  |  |  |

|                 | 1 = CXOUT is present on the CXOUT pin. Requires that the associated TRIS bit be cleared to actually<br>drive the pin. Not affected by CXON. |                                                                                                                                                             |                   |                |                 |                |              |  |  |  |  |  |  |

|                 |                                                                                                                                             | ) = CxOUT is internal only                                                                                                                                  |                   |                |                 |                |              |  |  |  |  |  |  |

| bit 4           |                                                                                                                                             | nparator Output                                                                                                                                             | Polarity Selec    | ct bit         |                 |                |              |  |  |  |  |  |  |

|                 | 1 = Comparator output is inverted                                                                                                           |                                                                                                                                                             |                   |                |                 |                |              |  |  |  |  |  |  |

|                 | 0 = Compara                                                                                                                                 | 0 = Comparator output is not inverted                                                                                                                       |                   |                |                 |                |              |  |  |  |  |  |  |

| bit 3           | CxZLF: Comparator Zero Latency Filter Enable bit                                                                                            |                                                                                                                                                             |                   |                |                 |                |              |  |  |  |  |  |  |

|                 | 1 = Comparator output is filtered                                                                                                           |                                                                                                                                                             |                   |                |                 |                |              |  |  |  |  |  |  |

|                 | 0 = Comparator output is unfiltered                                                                                                         |                                                                                                                                                             |                   |                |                 |                |              |  |  |  |  |  |  |

| bit 2           |                                                                                                                                             | CxSP: Comparator Speed/Power Select bit                                                                                                                     |                   |                |                 |                |              |  |  |  |  |  |  |

|                 |                                                                                                                                             | ator operates in<br>ator operates in                                                                                                                        |                   |                | mode            |                |              |  |  |  |  |  |  |

| bit 1           | CxHYS: Comparator Hysteresis Enable bit                                                                                                     |                                                                                                                                                             |                   |                |                 |                |              |  |  |  |  |  |  |

|                 | 1 = Comparator hysteresis enabled                                                                                                           |                                                                                                                                                             |                   |                |                 |                |              |  |  |  |  |  |  |

|                 | •                                                                                                                                           | ator hysteresis                                                                                                                                             |                   |                |                 |                |              |  |  |  |  |  |  |

| bit 0           |                                                                                                                                             | omparator Outp                                                                                                                                              | -                 |                |                 |                |              |  |  |  |  |  |  |

|                 |                                                                                                                                             | 1 = Comparator output to Timer1 and I/O pin is synchronous to changes on Timer1 clock source.<br>Output updated on the falling edge of Timer1 clock source. |                   |                |                 |                |              |  |  |  |  |  |  |

|                 |                                                                                                                                             | apdated on the rator output to T                                                                                                                            |                   |                |                 |                |              |  |  |  |  |  |  |

|                 |                                                                                                                                             |                                                                                                                                                             |                   |                | 1003.           |                |              |  |  |  |  |  |  |

| R/W-0/u          | R/W-0/u                                                                                                                                                                            | R/W-0/u                                                                                     | R/W-0/u | R/W/HC-0/u       | R-x/x            | R/W-0/u          | R/W-0/u                                                       |  |  |  |  |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------|------------------|------------------|------------------|---------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| TMR1GE           | T1GPOL                                                                                                                                                                             | T1GTM                                                                                       | T1GSPM  | T1GGO/<br>DONE   | T1GVAL           | T1GSS            | S<1:0>                                                        |  |  |  |  |  |  |  |  |  |  |

| bit 7            |                                                                                                                                                                                    |                                                                                             |         |                  |                  |                  | bit (                                                         |  |  |  |  |  |  |  |  |  |  |

|                  |                                                                                                                                                                                    |                                                                                             |         |                  |                  |                  |                                                               |  |  |  |  |  |  |  |  |  |  |

| Legend:          |                                                                                                                                                                                    |                                                                                             |         |                  |                  |                  |                                                               |  |  |  |  |  |  |  |  |  |  |

| R = Readable     | bit                                                                                                                                                                                | W = Writable                                                                                | bit     | U = Unimplem     | nented bit, read | d as '0'         |                                                               |  |  |  |  |  |  |  |  |  |  |

| u = Bit is unch  | anged                                                                                                                                                                              | x = Bit is unki                                                                             | nown    |                  |                  | R/Value at all o | other Resets                                                  |  |  |  |  |  |  |  |  |  |  |

| '1' = Bit is set |                                                                                                                                                                                    | '0' = Bit is cle                                                                            | ared    | HC = Bit is cle  | eared by hardw   | vare             |                                                               |  |  |  |  |  |  |  |  |  |  |

| bit 7            | TMD1CE. Tin                                                                                                                                                                        | ner1 Gate Ena                                                                               | bla bit |                  |                  |                  |                                                               |  |  |  |  |  |  |  |  |  |  |

| DIL 7            | If TMR10P =                                                                                                                                                                        |                                                                                             |         |                  |                  |                  |                                                               |  |  |  |  |  |  |  |  |  |  |

|                  | This bit is ignored                                                                                                                                                                |                                                                                             |         |                  |                  |                  |                                                               |  |  |  |  |  |  |  |  |  |  |

|                  | $\frac{\text{If TMR1ON} = 1}{2}$                                                                                                                                                   |                                                                                             |         |                  |                  |                  |                                                               |  |  |  |  |  |  |  |  |  |  |

|                  | <ul> <li>1 = Timer1 counting is controlled by the Timer1 gate function</li> <li>0 = Timer1 counts regardless of Timer1 gate function</li> </ul>                                    |                                                                                             |         |                  |                  |                  |                                                               |  |  |  |  |  |  |  |  |  |  |

| bit 6            | <b>T1GPOL:</b> Timer1 Gate Polarity bit                                                                                                                                            |                                                                                             |         |                  |                  |                  |                                                               |  |  |  |  |  |  |  |  |  |  |

|                  | 1 = Timer1 gate is active-high (Timer1 counts when gate is high)                                                                                                                   |                                                                                             |         |                  |                  |                  |                                                               |  |  |  |  |  |  |  |  |  |  |

|                  |                                                                                                                                                                                    |                                                                                             |         | nts when gate is |                  |                  |                                                               |  |  |  |  |  |  |  |  |  |  |

| bit 5            | T1GTM: Timer1 Gate Toggle Mode bit                                                                                                                                                 |                                                                                             |         |                  |                  |                  |                                                               |  |  |  |  |  |  |  |  |  |  |

|                  | 1 = Timer1 Gate Toggle mode is enabled                                                                                                                                             |                                                                                             |         |                  |                  |                  |                                                               |  |  |  |  |  |  |  |  |  |  |

|                  | <ul> <li>Timer1 Gate Toggle mode is disabled and toggle flip-flop is cleared</li> <li>Timer1 gate flip-flop toggles on every rising edge.</li> </ul>                               |                                                                                             |         |                  |                  |                  |                                                               |  |  |  |  |  |  |  |  |  |  |

| bit 4            | 0                                                                                                                                                                                  | ner1 Gate Sing                                                                              | ,       | 0 0              |                  |                  |                                                               |  |  |  |  |  |  |  |  |  |  |

|                  | 1 = Timer1 Gate Single-Pulse mode is enabled and is controlling Timer1 gate                                                                                                        |                                                                                             |         |                  |                  |                  |                                                               |  |  |  |  |  |  |  |  |  |  |

|                  |                                                                                                                                                                                    | ate Single-Pul                                                                              |         |                  |                  |                  |                                                               |  |  |  |  |  |  |  |  |  |  |

| bit 3            |                                                                                                                                                                                    |                                                                                             | •       | Acquisition Sta  |                  |                  |                                                               |  |  |  |  |  |  |  |  |  |  |

|                  | <ul> <li>1 = Timer1 gate single-pulse acquisition is ready, waiting for an edge</li> <li>0 = Timer1 gate single-pulse acquisition has completed or has not been started</li> </ul> |                                                                                             |         |                  |                  |                  |                                                               |  |  |  |  |  |  |  |  |  |  |

| bit 2            | -                                                                                                                                                                                  | ÷ .                                                                                         | -       |                  |                  | i Starteu        |                                                               |  |  |  |  |  |  |  |  |  |  |

| SIL 2            | -                                                                                                                                                                                  | <b>F1GVAL:</b> Timer1 Gate Current State bit ndicates the could be provided to TMR1H:TMR1L. |         |                  |                  |                  |                                                               |  |  |  |  |  |  |  |  |  |  |

|                  | Unaffected by Timer1 Gate Enable (TMR1GE).                                                                                                                                         |                                                                                             |         |                  |                  |                  |                                                               |  |  |  |  |  |  |  |  |  |  |

| bit 1-0          |                                                                                                                                                                                    | : Timer1 Gate                                                                               |         |                  |                  |                  |                                                               |  |  |  |  |  |  |  |  |  |  |

|                  |                                                                                                                                                                                    |                                                                                             |         | d output (sync_  |                  |                  |                                                               |  |  |  |  |  |  |  |  |  |  |

|                  |                                                                                                                                                                                    |                                                                                             |         | a output (sync_  |                  |                  | 10 = Comparator 1 optionally synchronized output (sync_C1OUT) |  |  |  |  |  |  |  |  |  |  |

|                  | 01 = Timer0 overflow output<br>00 = Timer1 gate pin                                                                                                                                |                                                                                             |         |                  |                  |                  |                                                               |  |  |  |  |  |  |  |  |  |  |

#### REGISTER 23-2: T1GCON: TIMER1 GATE CONTROL REGISTER

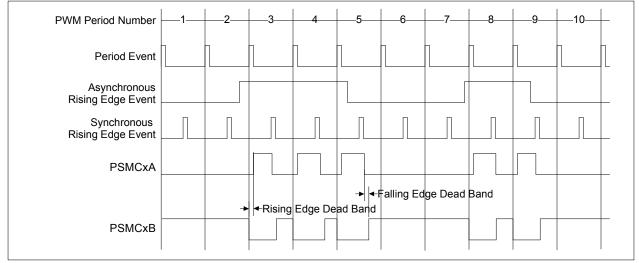

#### 26.3.8 PULSE-SKIPPING PWM WITH COMPLEMENTARY OUTPUTS

The pulse-skipping PWM is used to generate a series of fixed-length pulses that may or not be triggered at each period event. If any of the sources enabled to generate a rising edge event are high when a period event occurs, a pulse will be generated. If the rising edge sources are low at the period event, no pulse will be generated.

The rising edge occurs based upon the value in the PSMCxPH register pair.

The falling edge event always occurs according to the enabled event inputs without qualification between any two inputs.

#### 26.3.8.1 Mode Features

- · Dead-band control is available

- · No steering control available

- Primary PWM is output on only PSMCxA.

- · Complementary PWM is output on only PSMCxB.

#### 26.3.8.2 Waveform Generation

#### Rising Edge Event

If any enabled asynchronous rising edge event = 1 when there is a period event, then upon the next synchronous rising edge event:

- · Complementary output is set inactive

- Dead-band rising is activated (if enabled)

- · Primary output is set active

#### Falling Edge Event

- · Primary output is set inactive

- Dead-band falling is activated (if enabled)

- · Complementary output is set active

Note: To use this mode, an external source must be used for the determination of whether or not to generate the set pulse. If the phase time base is used, it will either always generate a pulse or never generate a pulse based on the PSMCxPH value.

#### FIGURE 26-11: PULSE-SKIPPING WITH COMPLEMENTARY OUTPUT PWM WAVEFORM

#### 26.7 Auto-Shutdown

Auto-shutdown is a method to immediately override the PSMC output levels with specific overrides that allow for safe shutdown of the application.

Auto-shutdown includes a mechanism to allow the application to restart under different conditions.

Auto-shutdown is enabled with the PxASDEN bit of the PSMC Auto-shutdown Control (PSMCxASDC) register (Register 26-16). All auto-shutdown features are enabled when PxASDEN is set and disabled when cleared.

#### 26.7.1 SHUTDOWN

There are two ways to generate a shutdown event:

- Manual

- External Input

#### 26.7.1.1 Manual Override

The auto-shutdown control register can be used to manually override the pin functions. Setting the PxASE bit of the PSMC Auto-shutdown Control (PSMCxASDC) register (Register 26-16) generates a software shut-down event.

The auto-shutdown override will persist as long as PxASE remains set.

#### 26.7.1.2 External Input Source