Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                                |

| Number of I/O              | 35                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 14x12b; D/A 1x8b, 3x5b                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1789t-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

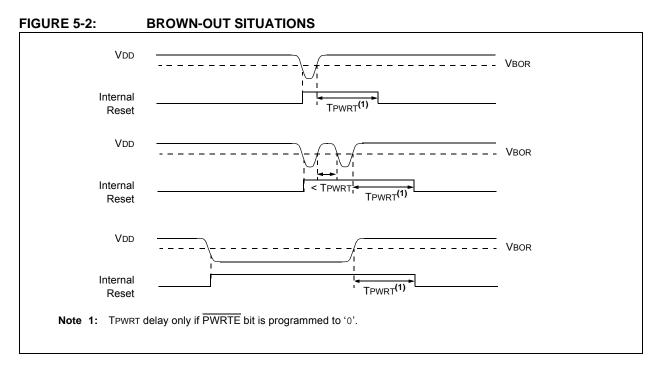

## 5.3 Register Definitions: BOR Control

## REGISTER 5-1: BORCON: BROWN-OUT RESET CONTROL REGISTER

| R/W-1/u | R/W-0/u | U-0 | U-0 | U-0 | U-0 | U-0 | R-q/u  |

|---------|---------|-----|-----|-----|-----|-----|--------|

| SBOREN  | BORFS   | —   | —   | —   | —   | —   | BORRDY |

| bit 7   |         |     |     |     |     |     | bit 0  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | <pre>SBOREN: Software Brown-out Reset Enable bit If BOREN &lt;1:0&gt; in Configuration Words ≠ 01: SBOREN is read/write, but has no effect on the BOR. If BOREN &lt;1:0&gt; in Configuration Words = 01: 1 = BOR Enabled 0 = BOR Disabled</pre>                                                                                                                           |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | BORFS: Brown-out Reset Fast Start bit <sup>(1)</sup><br><u>If BOREN&lt;1:0&gt; = 11 (Always on) or BOREN&lt;1:0&gt; = 00 (Always off)</u><br>BORFS is Read/Write, but has no effect.<br><u>If BOREN&lt;1:0&gt; = 10 (Disabled in Sleep) or BOREN&lt;1:0&gt; = 01 (Under software control):</u><br>1 = Band gap is forced on always (covers sleep/wake-up/operating cases) |

|         | 0 = Band gap operates normally, and may turn off                                                                                                                                                                                                                                                                                                                          |

| bit 5-1 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                |

| bit 0   | BORRDY: Brown-out Reset Circuit Ready Status bit<br>1 = The Brown-out Reset circuit is active<br>0 = The Brown-out Reset circuit is inactive                                                                                                                                                                                                                              |

|         |                                                                                                                                                                                                                                                                                                                                                                           |

**Note 1:** BOREN<1:0> bits are located in Configuration Words.

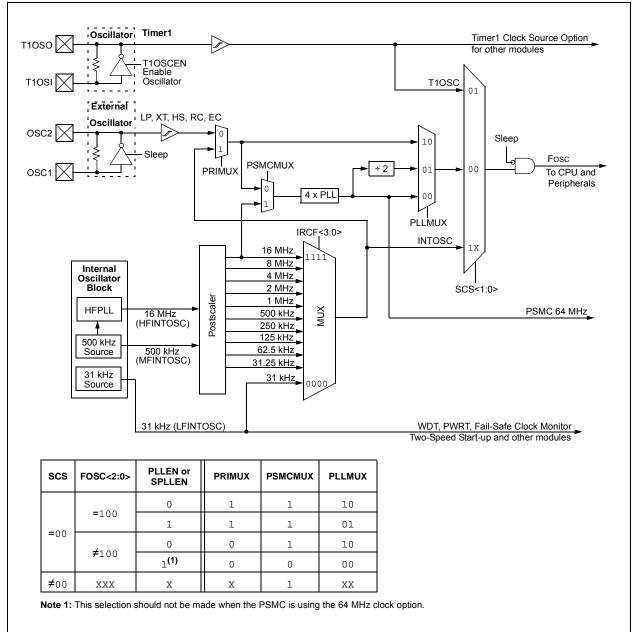

#### FIGURE 6-1: SIMPLIFIED PIC<sup>®</sup> MCU CLOCK SOURCE BLOCK DIAGRAM

## 6.2 Clock Source Types

Clock sources can be classified as external or internal.

External clock sources rely on external circuitry for the clock source to function. Examples are: oscillator modules (EC mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes) and Resistor-Capacitor (RC) mode circuits.

Internal clock sources are contained within the oscillator module. The internal oscillator block has two internal oscillators and a dedicated Phase-Lock Loop (HFPLL) that are used to generate three internal system clock sources: the 16 MHz High-Frequency Internal Oscillator (HFINTOSC), 500 kHz (MFINTOSC) and the 31 kHz Low-Frequency Internal Oscillator (LFINTOSC).

The system clock can be selected between external or internal clock sources via the System Clock Select (SCS) bits in the OSCCON register. See **Section 6.3 "Clock Switching"** for additional information.

#### 6.2.1 EXTERNAL CLOCK SOURCES

An external clock source can be used as the device system clock by performing one of the following actions:

- Program the FOSC<2:0> bits in the Configuration Words to select an external clock source that will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to:

- Timer1 oscillator during run-time, or

- An external clock source determined by the value of the FOSC bits.

See Section 6.3 "Clock Switching" for more information.

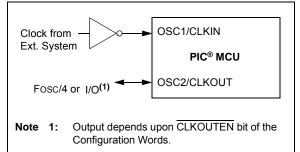

#### 6.2.1.1 EC Mode

The External Clock (EC) mode allows an externally generated logic level signal to be the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input. OSC2/CLKOUT is available for general purpose I/O or CLKOUT. Figure 6-2 shows the pin connections for EC mode.

EC mode has three power modes to select from through Configuration Words:

- High power, 4-32 MHz (FOSC = 111)

- Medium power, 0.5-4 MHz (FOSC = 110)

- Low power, 0-0.5 MHz (FOSC = 101)

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

#### EXTERNAL CLOCK (EC) MODE OPERATION

## 6.2.1.2 LP, XT, HS Modes

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 6-3). The three modes select a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

**LP** Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 6-3 and Figure 6-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

### 11.1 Independent Clock Source

The WDT derives its time base from the 31 kHz LFINTOSC internal oscillator. Time intervals in this chapter are based on a nominal interval of 1 ms. See **Section 31.0 "Electrical Specifications"** for the LFINTOSC tolerances.

### 11.2 WDT Operating Modes

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Words. See Table 11-1.

#### 11.2.1 WDT IS ALWAYS ON

When the WDTE bits of Configuration Words are set to '11', the WDT is always on.

WDT protection is active during Sleep.

#### 11.2.2 WDT IS OFF IN SLEEP

When the WDTE bits of Configuration Words are set to '10', the WDT is on, except in Sleep.

WDT protection is not active during Sleep.

#### 11.2.3 WDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Words are set to '01', the WDT is controlled by the SWDTEN bit of the WDTCON register.

WDT protection is unchanged by Sleep. See Table 11-1 for more details.

| WDTE<1:0> | SWDTEN | Device<br>Mode | WDT<br>Mode |

|-----------|--------|----------------|-------------|

| 11        | х      | Х              | Active      |

| 10        | 37     | Awake          | Active      |

| TO        | X      | Sleep          | Disabled    |

| 0.1       | 1      | х              | Active      |

| 01        | 0      | ~              | Disabled    |

| 00        | х      | Х              | Disabled    |

#### TABLE 11-2: WDT CLEARING CONDITIONS

### 11.3 Time-Out Period

The WDTPS bits of the WDTCON register set the time-out period from 1 ms to 256 seconds (nominal). After a Reset, the default time-out period is two seconds.

## 11.4 Clearing the WDT

The WDT is cleared when any of the following conditions occur:

- Any Reset

- CLRWDT instruction is executed

- · Device enters Sleep

- · Device wakes up from Sleep

- Oscillator fail

- WDT is disabled

- Oscillator Start-up TImer (OST) is running

See Table 11-2 for more information.

## 11.5 Operation During Sleep

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting.

When the device exits Sleep, the WDT is cleared again. The WDT remains clear until the OST, if enabled, completes. See **Section 6.0** "Oscillator **Module (with Fail-Safe Clock Monitor)**" for more information on the OST.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The TO and PD bits in the STATUS register are changed to indicate the event. See **Section 3.0 "Memory Organization"** and Status Register (Register 3-1) for more information.

| Conditions                                               | WDT                          |  |

|----------------------------------------------------------|------------------------------|--|

| WDTE<1:0> = 00                                           |                              |  |

| WDTE<1:0> = 01 and SWDTEN = 0                            |                              |  |

| WDTE<1:0> = 10 and enter Sleep                           | - Cleared                    |  |

| CLRWDT Command                                           |                              |  |

| Oscillator Fail Detected                                 | ]                            |  |

| Exit Sleep + System Clock = T1OSC, EXTRC, INTOSC, EXTCLK |                              |  |

| Exit Sleep + System Clock = XT, HS, LP                   | Cleared until the end of OST |  |

| Change INTOSC divider (IRCF bits)                        | Unaffected                   |  |

## 12.7 Register Definitions: EEPROM and Flash Control

## REGISTER 12-1: EEDATL: EEPROM DATA LOW BYTE REGISTER

| R/W-x/u              | R/W-x/u | R/W-x/u              | R/W-x/u | R/W-x/u           | R/W-x/u              | R/W-x/u             | R/W-x/u |

|----------------------|---------|----------------------|---------|-------------------|----------------------|---------------------|---------|

|                      |         |                      | EEDA    | T<7:0>            |                      |                     |         |

| bit 7                |         |                      |         |                   |                      |                     | bit C   |

|                      |         |                      |         |                   |                      |                     |         |

| Legend:              |         |                      |         |                   |                      |                     |         |

| R = Readable bit     |         | W = Writable bit     |         | U = Unimplemer    | nted bit, read as '0 | ,                   |         |

| u = Bit is unchanged |         | x = Bit is unknown   |         | -n/n = Value at F | POR and BOR/Valu     | ue at all other Res | ets     |

| '1' = Bit is set     |         | '0' = Bit is cleared |         |                   |                      |                     |         |

bit 7-0

EEDAT<7:0>: Read/write value for EEPROM data byte or Least Significant bits of program memory

#### REGISTER 12-2: EEDATH: EEPROM DATA HIGH BYTE REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   |         |         | EEDA    | T<13:8> |         |         |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

|                      |                      |                                                       |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 EEDAT<13:8>: Read/write value for Most Significant bits of program memory

#### REGISTER 12-3: EEADRL: EEPROM ADDRESS REGISTER

| R/W-0/0    | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|------------|---------|---------|---------|---------|---------|---------|---------|

| EEADR<7:0> |         |         |         |         |         |         |         |

| bit 7      |         |         |         |         |         |         | bit 0   |

|            |         |         |         |         |         |         |         |

| Legend:    |         |         |         |         |         |         |         |

| Legena.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

|                      |                      |                                                       |

bit 7-0 EEADR<7:0>: Specifies the Least Significant bits for program memory address or EEPROM address

#### REGISTER 12-4: EEADRH: EEPROM ADDRESS HIGH BYTE REGISTER

| U-1   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|---------|---------|---------|-------------|---------|---------|---------|

| (1)   |         |         |         | EEADR<14:8> |         |         |         |

| bit 7 |         |         |         |             |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7 Unimplemented: Read as '1'

bit 6-0 EEADR<14:8>: Specifies the Most Significant bits for program memory address or EEPROM address

Note 1: Unimplemented, read as '1'.

### 13.4 Register Definitions: PORTA

#### REGISTER 13-3: PORTA: PORTA REGISTER

| R/W-x/x                                 | R/W-x/x | R/W-x/x           | R/W-x/x | R/W-x/x                                               | R/W-x/x | R/W-x/x | R/W-x/x |  |

|-----------------------------------------|---------|-------------------|---------|-------------------------------------------------------|---------|---------|---------|--|

| RA7                                     | RA6     | RA5               | RA4     | RA3                                                   | RA2     | RA1     | RA0     |  |

| bit 7                                   |         |                   |         |                                                       |         |         | bit 0   |  |

|                                         |         |                   |         |                                                       |         |         |         |  |

| Legend:                                 |         |                   |         |                                                       |         |         |         |  |

| R = Readable b                          | bit     | W = Writable b    | oit     | U = Unimplemented bit, read as '0'                    |         |         |         |  |

| u = Bit is unchanged x = Bit is unknown |         |                   | own     | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |

| '1' = Bit is set                        |         | '0' = Bit is clea | red     |                                                       |         |         |         |  |

bit 7-0 RA<7:0>: PORTA I/O Value bits<sup>(1)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

#### REGISTER 13-4: TRISA: PORTA TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISA7  | TRISA6  | TRISA5  | TRISA4  | TRISA3  | TRISA2  | TRISA1  | TRISA0  |

| bit 7   |         |         | •       |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

- TRISA<7:0>: PORTA Tri-State Control bits

- 1 = PORTA pin configured as an input (tri-stated)

0 = PORTA pin configured as an output

#### REGISTER 13-5: LATA: PORTA DATA LATCH REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATA7   | LATA6   | LATA5   | LATA4   | LATA3   | LATA2   | LATA1   | LATA0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-4 LATA<7:0>: PORTA Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

## 19.4 Operation During Sleep

When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the DAC1CON0 register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

## 19.5 Effects of a Reset

A device Reset affects the following:

- DAC is disabled.

- DAC output voltage is removed from the DAC10UT pin.

- The DAC1R<7:0> range select bits are cleared.

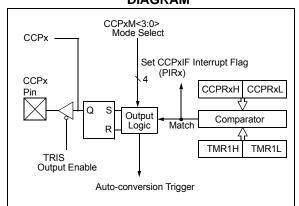

#### FIGURE 25-2: COMPARE MODE OPERATION BLOCK DIAGRAM

## 25.2.1 CCPX PIN CONFIGURATION

The user must configure the CCPx pin as an output by clearing the associated TRIS bit.

The CCP2 pin function can be moved to alternate pins using the APFCON register (Register 13-1). Refer to **Section 13.1 "Alternate Pin Function"** for more details.

| Note: | Clearing the CCPxCON register will force    |

|-------|---------------------------------------------|

|       | the CCPx compare output latch to the        |

|       | default low level. This is not the PORT I/O |

|       | data latch.                                 |

## 25.2.2 TIMER1 MODE RESOURCE

In Compare mode, Timer1 must be running in either Timer mode or Synchronized Counter mode. The compare operation may not work in Asynchronous Counter mode.

See **Section 23.0 "Timer1 Module with Gate Control"** for more information on configuring Timer1.

| Note: | Clocking Timer1 from the system clock   |

|-------|-----------------------------------------|

|       | (Fosc) should not be used in Compare    |

|       | mode. In order for Compare mode to      |

|       | recognize the trigger event on the CCPx |

|       | pin, TImer1 must be clocked from the    |

|       | instruction clock (Fosc/4) or from an   |

|       | external clock source.                  |

#### 25.2.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen (CCPxM<3:0> = 1010), the CCPx module does not assert control of the CCPx pin (see the CCPxCON register).

## 25.2.4 AUTO-CONVERSION TRIGGER

When Auto-conversion Trigger mode is chosen (CCPxM<3:0> = 1011), the CCPx module does the following:

- Resets Timer1

- · Starts an ADC conversion if ADC is enabled

The CCPx module does not assert control of the CCPx pin in this mode.

The Auto-conversion Trigger output of the CCP occurs immediately upon a match between the TMR1H, TMR1L register pair and the CCPRxH, CCPRxL register pair. The TMR1H, TMR1L register pair is not reset until the next rising edge of the Timer1 clock. The Auto-conversion Trigger output starts an ADC conversion (if the ADC module is enabled). This allows the CCPRxH, CCPRxL register pair to effectively provide a 16-bit programmable period register for Timer1.

Refer to **Section 17.2.5 "Auto-Conversion Trigger"** for more information.

- Note 1: The Auto-conversion Trigger from the CCP module does not set interrupt flag bit TMR1IF of the PIR1 register.

- 2: Removing the match condition by changing the contents of the CCPRxH and CCPRxL register pair, between the clock edge that generates the Auto-conversion Trigger and the clock edge that generates the Timer1 Reset, will preclude the Reset from occurring.

#### 25.2.5 COMPARE DURING SLEEP

The Compare mode is dependent upon the system clock (Fosc) for proper operation. Since Fosc is shut down during Sleep mode, the Compare mode will not function properly during Sleep.

## 25.2.6 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function register APFCON. To determine which pins can be moved and what their default locations are upon a Reset, see **Section 13.1 "Alternate Pin Function**"for more information.

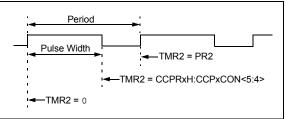

## 25.3 PWM Overview

Pulse-Width Modulation (PWM) is a scheme that provides power to a load by switching quickly between fully on and fully off states. The PWM signal resembles a square wave where the high portion of the signal is considered the on state and the low portion of the signal is considered the off state. The high portion, also known as the pulse width, can vary in time and is defined in steps. A larger number of steps applied, which lengthens the pulse width, also supplies more power to the load. Lowering the number of steps applied, which shortens the pulse width, supplies less power. The PWM period is defined as the duration of one complete cycle or the total amount of on and off time combined.

PWM resolution defines the maximum number of steps that can be present in a single PWM period. A higher resolution allows for more precise control of the pulse width time and in turn the power that is applied to the load.

The term duty cycle describes the proportion of the on time to the off time and is expressed in percentages, where 0% is fully off and 100% is fully on. A lower duty cycle corresponds to less power applied and a higher duty cycle corresponds to more power applied.

Figure 25-3 shows a typical waveform of the PWM signal.

#### 25.3.1 STANDARD PWM OPERATION

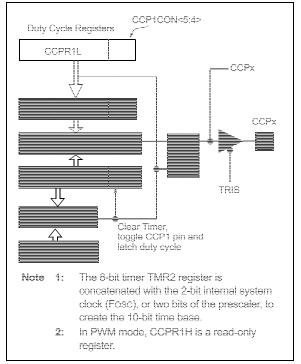

The standard PWM function described in this section is available and identical for all CCP modules.

The standard PWM mode generates a Pulse-Width Modulation (PWM) signal on the CCPx pin with up to ten bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- PR2 registers

- T2CON registers

- · CCPRxL registers

- · CCPxCON registers

Figure 25-4 shows a simplified block diagram of PWM operation.

- Note 1: The corresponding TRIS bit must be cleared to enable the PWM output on the CCPx pin.

- 2: Clearing the CCPxCON register will relinquish control of the CCPx pin.

#### FIGURE 25-3: CCP PWM OUTPUT SIGNAL

SIMPLIFIED PWM BLOCK DIAGRAM

## 26.2 Event Sources

There are two main sources for the period, rising edge and falling edge events:

- Synchronous input

- Time base

- Asynchronous Inputs

- Digital Inputs

- Analog inputs

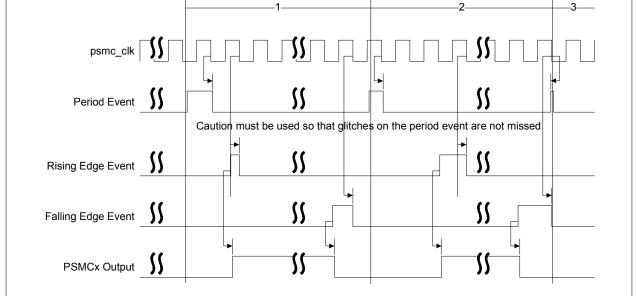

#### 26.2.1 TIME BASE

The Time Base section consists of several smaller pieces.

- 16-bit time base counter

- 16-bit Period register

- 16-bit Phase register (rising edge event)

- 16-bit Duty Cycle register (falling edge event)

- Clock control

- Interrupt Generator

An example of a fully synchronous PWM waveform generated with the time base is shown in Figure 26-2.

The PSMCxLD bit of the PSMCxCON register is provided to synchronize changes to the event Count registers. Changes are withheld from taking action until the first period event Reset after the PSMCxLD bit is set. For example, to change the PWM frequency, while maintaining the same effective duty cycle, the Period and Duty Cycle registers need to be changed. The changes to all four registers take effect simultaneously on the period event Reset after the PSMCxLD bit is set.

## 26.2.1.1 16-bit Counter (Time Base)

The PSMCxTMR is the counter used as a timing reference for each synchronous PWM period. The counter starts at 0000h and increments to FFFFh on the rising edge of the psmc\_clk signal.

When the counter rolls over from FFFFh to 0000h without a period event occurring, the overflow interrupt will be generated, thereby setting the PxTOVIF bit of the PSMC Time Base Interrupt Control (PSMCxINT) register (Register 26-34).

The PSMCxTMR counter is reset on both synchronous and asynchronous period events.

The PSMCxTMR is accessible to software as two 8-bit registers:

- PSMC Time Base Counter Low (PSMCxTMRL) register (Register 26-19)

- PSMC PSMC Time Base Counter High (PSMCxTMRH) register (Register 26-20)

PSMCxTMR is reset to the default POR value when the PSMCxEN bit is cleared.

#### 26.2.1.2 16-bit Period Register

The PSMCxPR Period register is used to determine a synchronous period event referenced to the 16-bit PSMCxTMR digital counter. A match between the PSMCxTMR and PSMCxPR register values will generate a period event.

The match will generate a period match interrupt, thereby setting the PxTPRIF bit of the PSMC Time Base Interrupt Control (PSMCxINT) register (Register 26-34).

The 16-bit period value is accessible to software as two 8-bit registers:

- PSMC Period Count Low Byte (PSMCxPRL) register (Register 26-25)

- PSMC Period Count High Byte (PSMCxPRH) register (Register 26-26)

The 16-bit period value is double-buffered before it is presented to the 16-bit time base for comparison. The buffered registers are updated on the first period event Reset after the PSMCxLD bit of the PSMCxCON register is set.

The synchronous PWM period time can be determined from Equation 26-1.

#### EQUATION 26-1: PWM PERIOD

$$Period = \frac{\text{PSMCxPR[15:0]} + 1}{F_{\text{psmc_clk}}}$$

#### 26.2.1.3 16-bit Phase Register

The PSMCxPH Phase register is used to determine a synchronous rising edge event referenced to the 16-bit PSMCxTMR digital counter. A match between the PSMCxTMR and the PSMCxPH register values will generate a rising edge event.

The match will generate a phase match interrupt, thereby setting the PxTPHIF bit of the PSMC Time Base Interrupt Control (PSMCxINT) register (Register 26-34).

The 16-bit phase value is accessible to software as two 8-bit registers:

- PSMC Phase Count Low Byte (PSMCxPHL) register (Register 26-34)

- PSMC Phase Count High Byte (PSMCxPHH) register (Register 26-34)

The 16-bit phase value is double-buffered before it is presented to the 16-bit PSMCxTMR for comparison. The buffered registers are updated on the first period event Reset after the PSMCxLD bit of the PSMCxCON register is set.

## 26.8 **PSMC** Synchronization

It is possible to synchronize the periods of two or more PSMC modules together, provided that all modules are on the same device.

Synchronization is achieved by sending a sync signal from the master PSMC module to the desired slave modules. This sync signal generates a period event in each slave module, thereby aligning all slaves with the master. This is useful when an application requires different PWM signal generation from each module but the waveforms must be consistent within a PWM period.

#### 26.8.1 SYNCHRONIZATION SOURCES

The synchronization source can be any PSMC module on the same device. For example, in a device with two PSMC modules, the possible sources for each device is as shown below:

- Sources for PSMC1

- PSMC2

- Sources for PSMC2

PSMC1

#### 26.8.1.1 PSMC Internal Connections

The sync signal from the master PSMC module is essentially that modules period event trigger. The slave PSMC modules reset their PSMCxTMR with the sync signal instead of their own period event.

Enabling a module as a slave recipient is done with the PxSYNC bits of the PSMC Synchronization Control (PSMCxSYNC) registers; registers 26-3 and 26-4.

#### 26.8.1.2 Phase Offset Synchronization

The synchronization output signal from the PSMC module is selectable. The sync\_out source may be either:

- Period Event

- Rising Event

Source selection is made with the PxPOFST bit of the PSMCxSYNC registers, registers 26-3, 26-4 and 26-7.

When the PxPOFST bit is set, the sync\_out signal comes from the rising event and the period event replaces the rising event as the start of the active drive period. When PxPOFST is set, duty cycles of up to 100% are achievable in both the slave and master.

When PXPOFST is clear, the sync\_out signal comes from the period event. When PxPOFST is clear, rising events that start after the period event remove the equivalent start delay percentage from the maximum 100% duty cycle.

#### 26.8.1.3 Synchronization Skid

When the sync\_out source is the Period Event, the slave synchronous rising and falling events will lag by one psmc\_clk period. When the sync\_out source is the Rising Event, the synchronous events will lag by two clock periods. To compensate for this, the values in PHH:PHL and DCH:DCL registers can be reduced by the number of lag cycles.

When one device is transmitting a logical one, or letting the line float, and a second device is transmitting a logical zero, or holding the line low, the first device can detect that the line is not a logical one. This detection, when used on the SCL line, is called clock stretching. Clock stretching gives slave devices a mechanism to control the flow of data. When this detection is used on the SDA line, it is called arbitration. Arbitration ensures that there is only one master device communicating at any single time.

## 27.3.1 CLOCK STRETCHING

When a slave device has not completed processing data, it can delay the transfer of more data through the process of clock stretching. An addressed slave device may hold the SCL clock line low after receiving or sending a bit, indicating that it is not yet ready to continue. The master that is communicating with the slave will attempt to raise the SCL line in order to transfer the next bit, but will detect that the clock line has not yet been released. Because the SCL connection is open-drain, the slave has the ability to hold that line low until it is ready to continue communicating.

Clock stretching allows receivers that cannot keep up with a transmitter to control the flow of incoming data.

## 27.3.2 ARBITRATION

Each master device must monitor the bus for Start and Stop bits. If the device detects that the bus is busy, it cannot begin a new message until the bus returns to an Idle state.

However, two master devices may try to initiate a transmission on or about the same time. When this occurs, the process of arbitration begins. Each transmitter checks the level of the SDA data line and compares it to the level that it expects to find. The first transmitter to observe that the two levels do not match, loses arbitration, and must stop transmitting on the SDA line.

For example, if one transmitter holds the SDA line to a logical one (lets it float) and a second transmitter holds it to a logical zero (pulls it low), the result is that the SDA line will be low. The first transmitter then observes that the level of the line is different than expected and concludes that another transmitter is communicating.

The first transmitter to notice this difference is the one that loses arbitration and must stop driving the SDA line. If this transmitter is also a master device, it also must stop driving the SCL line. It then can monitor the lines for a Stop condition before trying to reissue its transmission. In the meantime, the other device that has not noticed any difference between the expected and actual levels on the SDA line continues with its original transmission. It can do so without any complications, because so far, the transmission appears exactly as expected with no other transmitter disturbing the message.

Slave Transmit mode can also be arbitrated, when a master addresses multiple slaves, but this is less common.

If two master devices are sending a message to two different slave devices at the address stage, the master sending the lower slave address always wins arbitration. When two master devices send messages to the same slave address, and addresses can sometimes refer to multiple slaves, the arbitration process must continue into the data stage.

Arbitration usually occurs very rarely, but it is a necessary process for proper multi-master support.

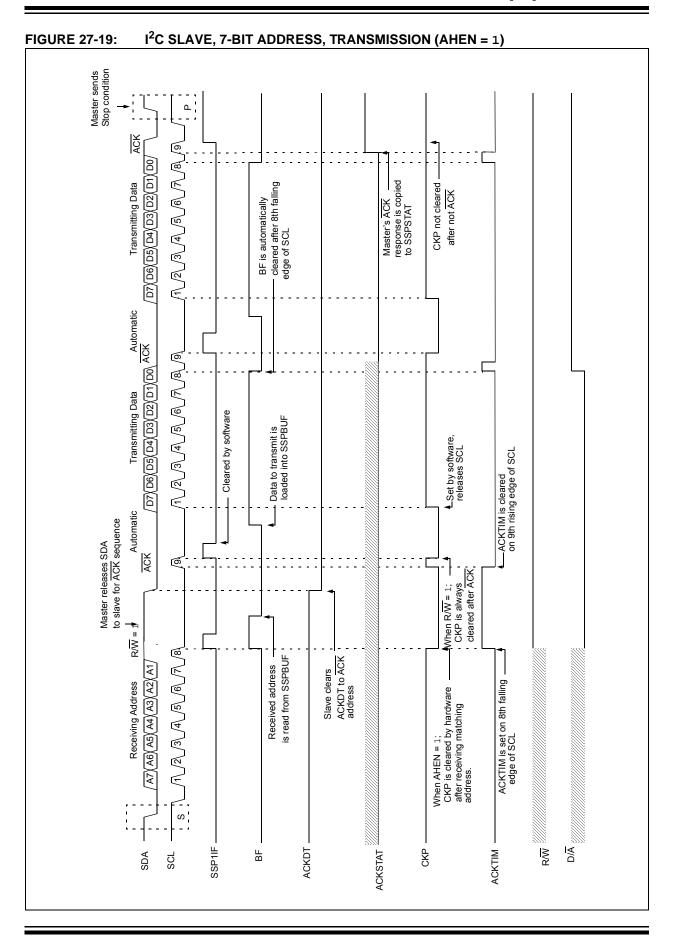

#### 27.5.3.3 7-bit Transmission with Address Hold Enabled

Setting the AHEN bit of the SSPCON3 register enables additional clock stretching and interrupt generation after the 8th falling edge of a received matching address. Once a matching address has been clocked in, CKP is cleared and the SSP1IF interrupt is set.

Figure 27-18 displays a standard waveform of a 7-bit Address Slave Transmission with AHEN enabled.

- 1. Bus starts Idle.

- Master sends Start condition; the S bit of SSPSTAT is set; SSP1IF is set if interrupt on Start detect is enabled.

- Master sends matching address with R/W bit set. After the 8th falling edge of the SCL line the CKP bit is cleared and SSP1IF interrupt is generated.

- 4. Slave software clears SSP1IF.

- 5. Slave software reads ACKTIM bit of SSPCON3 register, and  $R/\overline{W}$  and  $D/\overline{A}$  of the SSPSTAT register to determine the source of the interrupt.

- 6. Slave reads the address value from the SSPBUF register clearing the BF bit.

- 7. Slave software decides from this information if it wishes to ACK or not ACK and sets the ACKDT bit of the SSPCON2 register accordingly.

- 8. Slave sets the CKP bit releasing SCL.

- 9. Master clocks in the  $\overline{ACK}$  value from the slave.

- 10. Slave hardware automatically clears the CKP bit and sets SSP1IF after the ACK if the R/W bit is set.

- 11. Slave software clears SSP1IF.

- 12. Slave loads value to transmit to the master into SSPBUF setting the BF bit.

Note: SSPBUF cannot be loaded until after the ACK.

13. Slave sets the CKP bit releasing the clock.

- 14. Master clocks out the data from the slave and sends an ACK value on the 9th SCL pulse.

- 15. Slave hardware copies the ACK value into the ACKSTAT bit of the SSPCON2 register.

- 16. Steps 10-15 are repeated for each byte transmitted to the master from the slave.

- 17. If the master sends a not  $\overline{ACK}$  the slave releases the bus allowing the master to send a Stop and end the communication.

**Note:** Master must send a not ACK on the last byte to ensure that the slave releases the SCL line to receive a Stop.

| (    | Configuration Bits |      |                     | Baud Rate Formula |  |  |

|------|--------------------|------|---------------------|-------------------|--|--|

| SYNC | BRG16              | BRGH | BRG/EUSART Mode     | Baud Rate Formula |  |  |

| 0    | 0                  | 0    | 8-bit/Asynchronous  | Fosc/[64 (n+1)]   |  |  |

| 0    | 0                  | 1    | 8-bit/Asynchronous  |                   |  |  |

| 0    | 1                  | 0    | 16-bit/Asynchronous | Fosc/[16 (n+1)]   |  |  |

| 0    | 1                  | 1    | 16-bit/Asynchronous |                   |  |  |

| 1    | 0                  | x    | 8-bit/Synchronous   | Fosc/[4 (n+1)]    |  |  |

| 1    | 1                  | x    | 16-bit/Synchronous  |                   |  |  |

#### TABLE 28-3: BAUD RATE FORMULAS

Legend: x = Don't care, n = value of SPBRGH, SPBRGL register pair

#### TABLE 28-4: SUMMARY OF REGISTERS ASSOCIATED WITH THE BAUD RATE GENERATOR

| Name    | Bit 7     | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |

|---------|-----------|-------|-------|-------|-------|-------|-------|-------|---------------------|

| BAUDCON | ABDOVF    | RCIDL | —     | SCKP  | BRG16 | —     | WUE   | ABDEN | 356                 |

| RCSTA   | SPEN      | RX9   | SREN  | CREN  | ADDEN | FERR  | OERR  | RX9D  | 355                 |

| SPBRGL  | BRG<7:0>  |       |       |       |       |       |       |       |                     |

| SPBRGH  | BRG<15:8> |       |       |       |       |       |       |       | 357                 |

| TXSTA   | CSRC      | TX9   | TXEN  | SYNC  | SENDB | BRGH  | TRMT  | TX9D  | 354                 |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used for the Baud Rate Generator.

\* Page provides register information.

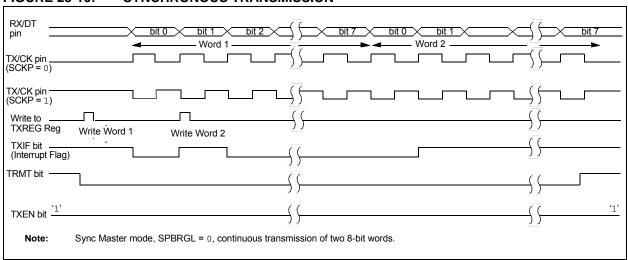

### FIGURE 28-10: SYNCHRONOUS TRANSMISSION

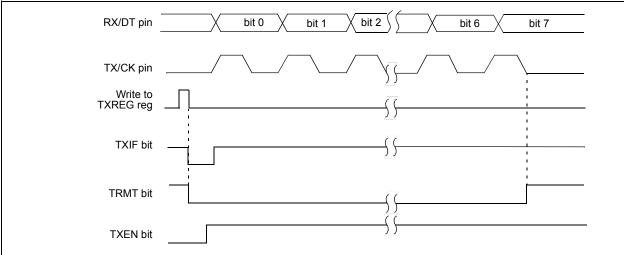

## FIGURE 28-11: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

## TABLE 28-7:SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER<br/>TRANSMISSION

| Name    | Bit 7                         | Bit 6         | Bit 5       | Bit 4        | Bit 3       | Bit 2          | Bit 1       | Bit 0        | Register<br>on Page |

|---------|-------------------------------|---------------|-------------|--------------|-------------|----------------|-------------|--------------|---------------------|

| APFCON1 | C2OUTSEL                      | CC1PSEL       | SDOSEL      | SCKSEL       | SDISEL      | TXSEL          | RXSEL       | CCP2SEL      | 132                 |

| BAUDCON | ABDOVF                        | RCIDL         | —           | SCKP         | BRG16       | —              | WUE         | ABDEN        | 356                 |

| INTCON  | GIE                           | PEIE          | TMR0IE      | INTE         | IOCIE       | TMR0IF         | INTF        | IOCIF        | 97                  |

| PIE1    | TMR1GIE                       | ADIE          | RCIE        | TXIE         | SSP1IE      | CCP1IE         | TMR2IE      | TMR1IE       | 98                  |

| PIR1    | TMR1GIF                       | ADIF          | RCIF        | TXIF         | SSP1IF      | CCP1IF         | TMR2IF      | TMR1IF       | 102                 |

| RCSTA   | SPEN                          | RX9           | SREN        | CREN         | ADDEN       | FERR           | OERR        | RX9D         | 355                 |

| SPBRGL  |                               |               |             | BRG<         | 7:0>        |                |             |              | 357                 |

| SPBRGH  |                               |               |             | BRG<         | 15:8>       |                |             |              | 357                 |

| TRISC   | TRISC7                        | TRISC6        | TRISC5      | TRISC4       | TRISC3      | TRISC2         | TRISC1      | TRISC0       | 147                 |

| TXREG   | EUSART Transmit Data Register |               |             |              |             |                |             |              |                     |

| TXSTA   | CSRC                          | TX9           | TXEN        | SYNC         | SENDB       | BRGH           | TRMT        | TX9D         | 354                 |

| Logond: |                               | ated leastion | read as 'o' | Chadad calls | ore not use | d for overebro | nous mostor | tranamiaaian |                     |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for synchronous master transmission.

\* Page provides register information.

#### TABLE 31-8: PLL CLOCK TIMING SPECIFICATIONS

| Standard Operating Conditions (unless otherwise stated) |                     |                               |        |      |        |       |            |

|---------------------------------------------------------|---------------------|-------------------------------|--------|------|--------|-------|------------|

| Param<br>No.                                            | Sym.                | Characteristic                | Min.   | Тур† | Max.   | Units | Conditions |

| F10                                                     | Fosc                | Oscillator Frequency Range    | 4      |      | 8      | MHz   |            |

| F11                                                     | Fsys                | On-Chip VCO System Frequency  | 16     | _    | 32     | MHz   |            |

| F12                                                     | TRC                 | PLL Start-up Time (Lock Time) | —      | _    | 2      | ms    |            |

| F13*                                                    | $\Delta \text{CLK}$ | CLKOUT Stability (Jitter)     | -0.25% | _    | +0.25% | %     |            |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

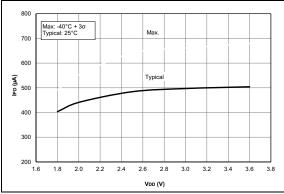

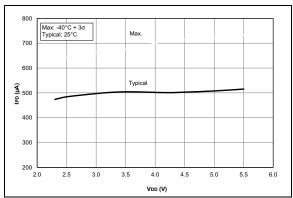

**FIGURE 32-49:** IPD, Comparator, NP Mode (CxSP = 1), PIC16LF1788/9 Only.

**FIGURE 32-50:** IPD, Comparator, NP Mode (CxSP = 1), PIC16F1788/9 Only.

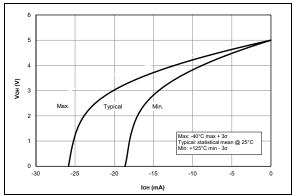

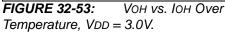

FIGURE 32-51: VOH vs. IOH Over Temperature, VDD = 5.0V, PIC16F1788/9 Only.

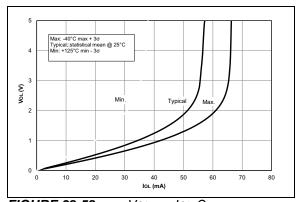

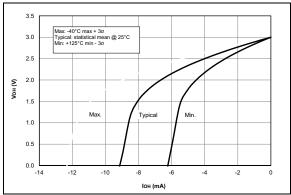

FIGURE 32-52: VOL vs. IOL Over Temperature, VDD = 5.0V, PIC16F1788/9 Only.

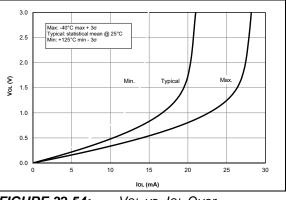

FIGURE 32-54: VOL vs. IOL Over Temperature, VDD = 3.0V.

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

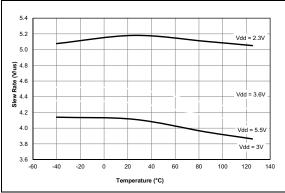

FIGURE 32-115: Op Amp, Output Slew Rate, Falling Edge, PIC16F1788/9 Only.

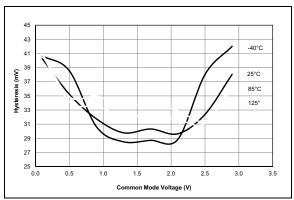

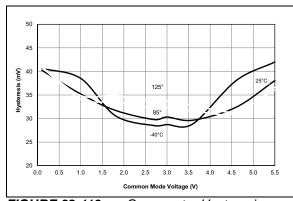

**FIGURE 32-116:** Comparator Hysteresis, NP Mode (CxSP = 1), VDD = 3.0V, Typical Measured Values.

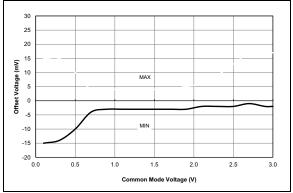

**FIGURE 32-117:** Comparator Offset, NP Mode (CxSP = 1), VDD = 3.0V, Typical Measured Values at 25°C.

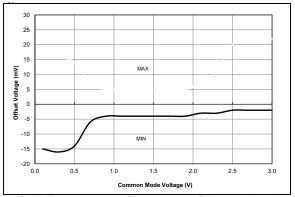

**FIGURE 32-118:** Comparator Offset, NP Mode (CxSP = 1), VDD = 3.0V, Typical Measured Values From -40°C to 125°C.

**FIGURE 32-119:** Comparator Hysteresis, NP Mode (CxSP = 1), VDD = 5.5V, Typical Measured Values, PIC16F1788/9 Only.