RECERCIC

22222

Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                                |

| Number of I/O              | 35                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 14x12b; D/A 1x8b, 3x5b                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 40-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 40-UQFN (5x5)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1789t-i-mv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Digital Peripheral Features:**

- Timer0: 8-Bit Timer/Counter with 8-Bit Programmable Prescaler

- Enhanced Timer1:

- 16-bit timer/counter with prescaler

- External Gate Input mode

- Dedicated low-power 32 kHz oscillator driver

- Timer2: 8-Bit Timer/Counter with 8-Bit Period Register, Prescaler and Postscaler

- Two Capture/Compare/PWM modules (CCP):

- 16-bit capture, maximum resolution 12.5 ns

- 16-bit compare, max resolution 31.25 ns

- 10-bit PWM, max frequency 32 kHz

- Master Synchronous Serial Port (SSP) with SPI and I<sup>2</sup>C with:

- 7-bit address masking

- SMBus/PMBus<sup>™</sup> compatibility

- Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART):

- RS-232, RS-485 and LIN compatible

- Auto-baud detect

- Auto-wake-up on start

# **Oscillator Features:**

- Operate up to 32 MHz from Precision Internal Oscillator:

- Factory calibrated to ±1%, typical

- Software selectable frequency range from 32 MHz to 31 kHz

- 31 kHz Low-Power Internal Oscillator

- 32.768 kHz Timer1 Oscillator:

- Available as system clock

- Low-power RTC

- External Oscillator Block with:

- 4 crystal/resonator modes up to 32 MHz using 4x PLL

- 3 external clock modes up to 32 MHz

- 4x Phase-Locked Loop (PLL)

- Fail-Safe Clock Monitor:

- Detect and recover from external oscillator failure

- Two-Speed Start-up:

- Minimize latency between code execution and external oscillator start-up

# **General Microcontroller Features:**

- · Power-Saving Sleep mode

- · Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR) with Selectable Trip Point

- Extended Watchdog Timer (WDT)

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- In-Circuit Debug (ICD)

- Enhanced Low-Voltage Programming (LVP)

- Operating Voltage Range:

- 1.8V to 3.6V (PIC16LF1788/9)

- 2.3V to 5.5V (PIC16F1788/9)

# 5.12 Determining the Cause of a Reset

Upon any Reset, multiple bits in the STATUS and PCON register are updated to indicate the cause of the Reset. Table 5-3 and Table 5-4 show the Reset conditions of these registers.

| STKOVF | STKUNF | RWDT | RMCLR | RI | POR | BOR | то | PD | Condition                                                         |

|--------|--------|------|-------|----|-----|-----|----|----|-------------------------------------------------------------------|

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 1  | 1  | Power-on Reset                                                    |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 0  | x  | Illegal, $\overline{\text{TO}}$ is set on $\overline{\text{POR}}$ |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | x  | 0  | Illegal, $\overline{PD}$ is set on $\overline{POR}$               |

| 0      | 0      | u    | 1     | 1  | u   | 0   | 1  | 1  | Brown-out Reset                                                   |

| u      | u      | 0    | u     | u  | u   | u   | 0  | u  | WDT Reset                                                         |

| u      | u      | u    | u     | u  | u   | u   | 0  | 0  | WDT Wake-up from Sleep                                            |

| u      | u      | u    | u     | u  | u   | u   | 1  | 0  | Interrupt Wake-up from Sleep                                      |

| u      | u      | u    | 0     | u  | u   | u   | u  | u  | MCLR Reset during normal operation                                |

| u      | u      | u    | 0     | u  | u   | u   | 1  | 0  | MCLR Reset during Sleep                                           |

| u      | u      | u    | u     | 0  | u   | u   | u  | u  | RESET Instruction Executed                                        |

| 1      | u      | u    | u     | u  | u   | u   | u  | u  | Stack Overflow Reset (STVREN = 1)                                 |

| u      | 1      | u    | u     | u  | u   | u   | u  | u  | Stack Underflow Reset (STVREN = 1)                                |

TABLE 5-3: RESET STATUS BITS AND THEIR SIGNIFICANCE

# TABLE 5-4: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 1 1000             | 00 110x          |

| MCLR Reset during normal operation | 0000h                 | u uuuu             | uu Ouuu          |

| MCLR Reset during Sleep            | 0000h                 | 1 Ouuu             | uu Ouuu          |

| WDT Reset                          | 0000h                 | 0 uuuu             | uu uuuu          |

| WDT Wake-up from Sleep             | PC + 1                | 0 Ouuu             | uu uuuu          |

| Brown-out Reset                    | 0000h                 | 1 luuu             | 00 11u0          |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | 1 Ouuu             | uu uuuu          |

| RESET Instruction Executed         | 0000h                 | u uuuu             | uu u0uu          |

| Stack Overflow Reset (STVREN = 1)  | 0000h                 | u uuuu             | lu uuuu          |

| Stack Underflow Reset (STVREN = 1) | 0000h                 | u uuuu             | ul uuuu          |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Enable bit (GIE) is set, the return address is pushed on the stack and PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

# 6.4 Two-Speed Clock Start-up Mode

Two-Speed Start-up mode provides additional power savings by minimizing the latency between external oscillator start-up and code execution. In applications that make heavy use of the Sleep mode, Two-Speed Start-up will remove the external oscillator start-up time from the time spent awake and can reduce the overall power consumption of the device. This mode allows the application to wake-up from Sleep, perform a few instructions using the INTOSC internal oscillator block as the clock source and go back to Sleep without waiting for the external oscillator to become stable.

Two-Speed Start-up provides benefits when the oscillator module is configured for LP, XT or HS modes. The Oscillator Start-up Timer (OST) is enabled for these modes and must count 1024 oscillations before the oscillator can be used as the system clock source.

If the oscillator module is configured for any mode other than LP, XT or HS mode, then Two-Speed Start-up is disabled. This is because the external clock oscillator does not require any stabilization time after POR or an exit from Sleep.

If the OST count reaches 1024 before the device enters Sleep mode, the OSTS bit of the OSCSTAT register is set and program execution switches to the external oscillator. However, the system may never operate from the external oscillator if the time spent awake is very short.

| Note: | Executing a SLEEP instruction will abort    |

|-------|---------------------------------------------|

|       | the oscillator start-up time and will cause |

|       | the OSTS bit of the OSCSTAT register to     |

|       | remain clear.                               |

# TABLE 6-1: OSCILLATOR SWITCHING DELAYS

### Switch From Switch To Frequency **Oscillator Delav** LFINTOSC<sup>(1)</sup> 31 kHz MFINTOSC<sup>(1)</sup> Oscillator Warm-up Delay Twarm<sup>(2)</sup> 31.25 kHz-500 kHz Sleep HFINTOSC<sup>(1)</sup> 31.25 kHz-16 MHz EC, RC<sup>(1)</sup> Sleep/POR DC - 32 MHz 2 cycles EC. RC<sup>(1)</sup> **LFINTOSC** DC - 32 MHz 1 cycle of each Timer1 Oscillator Sleep/POR 32 kHz-20 MHz 1024 Clock Cycles (OST) LP, XT, HS<sup>(1)</sup> MFINTOSC<sup>(1)</sup> 31.25 kHz-500 kHz Any clock source 2 µs (approx.) HFINTOSC<sup>(1)</sup> 31.25 kHz-16 MHz LFINTOSC<sup>(1)</sup> Any clock source 31 kHz 1 cycle of each Any clock source Timer1 Oscillator 32 kHz 1024 Clock Cycles (OST) PLL inactive PLL active 16-32 MHz 2 ms (approx.)

Note 1: PLL inactive.

2: See Section 31.0 "Electrical Specifications".

# 6.4.1 TWO-SPEED START-UP MODE CONFIGURATION

Two-Speed Start-up mode is configured by the following settings:

- IESO (of the Configuration Words) = 1; Internal/External Switchover bit (Two-Speed Start-up mode enabled).

- SCS (of the OSCCON register) = 00.

- FOSC<2:0> bits in the Configuration Words configured for LP, XT or HS mode.

Two-Speed Start-up mode is entered after:

- Power-on Reset (POR) and, if enabled, after Power-up Timer (PWRT) has expired, or

- Wake-up from Sleep.

# 13.6 Register Definitions: PORTB

# REGISTER 13-11: PORTB: PORTB REGISTER

| R/W-x/u                                 | R/W-x/u | R/W-x/u           | R/W-x/u                                               | R/W-x/u                            | R/W-x/u | R/W-x/u | R/W-x/u |  |

|-----------------------------------------|---------|-------------------|-------------------------------------------------------|------------------------------------|---------|---------|---------|--|

| RB7                                     | RB6     | RB5               | RB4                                                   | RB3                                | RB2     | RB1     | RB0     |  |

| bit 7                                   |         |                   |                                                       |                                    |         |         | bit 0   |  |

|                                         |         |                   |                                                       |                                    |         |         |         |  |

| Legend:                                 |         |                   |                                                       |                                    |         |         |         |  |

| R = Readable bit W = Writable bit       |         |                   | bit                                                   | U = Unimplemented bit, read as '0' |         |         |         |  |

| u = Bit is unchanged x = Bit is unknown |         |                   | -n/n = Value at POR and BOR/Value at all other Resets |                                    |         |         |         |  |

| '1' = Bit is set                        |         | '0' = Bit is clea | ared                                                  |                                    |         |         |         |  |

bit 7-0 **RB<7:0>**: PORTB General Purpose I/O Pin bits<sup>(1)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

# REGISTER 13-12: TRISB: PORTB TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISB7  | TRISB6  | TRISB5  | TRISB4  | TRISB3  | TRISB2  | TRISB1  | TRISB0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

TRISB<7:0>: PORTB Tri-State Control bits

1 = PORTB pin configured as an input (tri-stated)

0 = PORTB pin configured as an output

# REGISTER 13-13: LATB: PORTB DATA LATCH REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATB7   | LATB6   | LATB5   | LATB4   | LATB3   | LATB2   | LATB1   | LATB0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 LATB<7:0>: PORTB Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTB are actually written to corresponding LATB register. Reads from PORTB register is return of actual I/O pin values.

**Note 1:** Writes to PORTB are actually written to corresponding LATB register. Reads from PORTB register is return of actual I/O pin values.

| REGISTER         | 17-2: ADC                                                                                                                                                | ON1: ADC CO                                                              | NTROL RE      | GISTER 1          |                  |                |              |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------|-------------------|------------------|----------------|--------------|

| R/W-0/0          | R/W-0/0                                                                                                                                                  | R/W-0/0                                                                  | R/W-0/0       | U-0               | R/W-0/0          | R/W-0/0        | R/W-0/0      |

| ADFM             | ADCS<2:0>                                                                                                                                                |                                                                          |               | —                 | ADPRE            | EF<1:0>        |              |

| bit 7            |                                                                                                                                                          |                                                                          |               |                   |                  |                | bit C        |

|                  |                                                                                                                                                          |                                                                          |               |                   |                  |                |              |

| Legend:          |                                                                                                                                                          |                                                                          |               |                   |                  |                |              |

| R = Readable     | e bit                                                                                                                                                    | W = Writable                                                             | bit           | U = Unimplei      | mented bit, read | d as '0'       |              |

| u = Bit is unc   | hanged                                                                                                                                                   | x = Bit is unkr                                                          | iown          | -n/n = Value      | at POR and BO    | R/Value at all | other Resets |

| '1' = Bit is set | t                                                                                                                                                        | '0' = Bit is clea                                                        | ared          |                   |                  |                |              |

| bit 7<br>bit 6-4 | 1 = 2's com<br>0 = Sign-ma                                                                                                                               | CResult Format<br>plement format.<br>agnitude result for<br>ADC Conversi | ormat.        | <b>-</b> <i>i</i> |                  |                |              |

| Sit 0-4          | 111 = FRC (0<br>110 = Fosc/<br>101 = Fosc/<br>100 = Fosc/                                                                                                | clock supplied fr<br>64<br>16<br>4<br>clock supplied fr<br>32<br>8       | om a dedicate | ed FRC oscillato  |                  |                |              |

| bit 3            | Unimpleme                                                                                                                                                | nted: Read as '                                                          | o'            |                   |                  |                |              |

| bit 2            | ADNREF: ADC Negative Voltage Reference Configuration bit<br>1 = VREF- is connected to external VREF- pin <sup>(1)</sup><br>0 = VREF- is connected to Vss |                                                                          |               |                   |                  |                |              |

| bit 1-0          |                                                                                                                                                          |                                                                          |               |                   |                  |                |              |

**Note 1:** When selecting the FVR or VREF+ pin as the source of the positive reference, be aware that a minimum voltage specification exists. See **Section 31.0 "Electrical Specifications"** for details.

# REGISTER 17-2: ADCON1: ADC CONTROL REGISTER 1

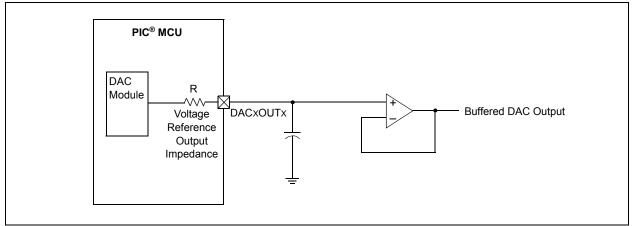

## FIGURE 20-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

# 20.4 Operation During Sleep

When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the DACxCON0 register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

# 20.5 Effects of a Reset

A device Reset affects the following:

- DAC is disabled.

- DAC output voltage is removed from the DACxOUT pin.

- The DACxR<4:0> range select bits are cleared.

# 23.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1 is enabled by configuring the TMR1ON and TMR1GE bits in the T1CON and T1GCON registers, respectively. Table 23-1 displays the Timer1 enable selections.

| TABLE 23-1: | TIMER1 ENABLE |

|-------------|---------------|

|             | SELECTIONS    |

| TMR10N | TMR1GE | Timer1<br>Operation |

|--------|--------|---------------------|

| 0      | 0      | Off                 |

| 0      | 1      | Off                 |

| 1      | 0      | Always On           |

| 1      | 1      | Count Enabled       |

# 23.2 Clock Source Selection

The TMR1CS<1:0> and T1OSCEN bits of the T1CON register are used to select the clock source for Timer1. Table 23-2 displays the clock source selections.

# 23.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected, the TMR1H:TMR1L register pair will increment on multiples of Fosc as determined by the Timer1 prescaler.

When the Fosc internal clock source is selected, the Timer1 register value will increment by four counts every instruction clock cycle. Due to this condition, a 2 LSB error in resolution will occur when reading the Timer1 value. To utilize the full resolution of Timer1, an asynchronous input signal must be used to gate the Timer1 clock input.

The following asynchronous sources may be used:

- Asynchronous event on the T1G pin to Timer1 gate

- C1 or C2 comparator input to Timer1 gate

# 23.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When enabled to count, Timer1 is incremented on the rising edge of the external clock input T1CKI, which can be synchronized to the microcontroller system clock or can run asynchronously.

When used as a timer with a clock oscillator, an external 32.768 kHz crystal can be used in conjunction with the dedicated internal oscillator circuit.

**Note:** In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge after any one or more of the following conditions:

- Timer1 enabled after POR

- Write to TMR1H or TMR1L

- · Timer1 is disabled

- Timer1 is disabled (TMR1ON = 0) when T1CKI is high then Timer1 is enabled (TMR1ON=1) when T1CKI is low.

| TMR1CS<1:0> | T1OSCEN | Clock Source                   |

|-------------|---------|--------------------------------|

| 11          | х       | Reserved                       |

| 10          | 1       | Timer1 Oscillator              |

| 10          | 0       | External Clocking on T1CKI Pin |

| 01          | х       | System Clock (Fosc)            |

| 00          | x       | Instruction Clock (Fosc/4)     |

# TABLE 23-2: CLOCK SOURCE SELECTIONS

# REGISTER 26-25: PSMCxPRL: PSMC PERIOD COUNT LOW BYTE REGISTER

| R/W-0/0                           | R/W-0/0 | R/W-0/0            | R/W-0/0 | R/W-0/0                                          | R/W-0/0 | R/W-0/0 | R/W-0/0     |  |

|-----------------------------------|---------|--------------------|---------|--------------------------------------------------|---------|---------|-------------|--|

|                                   |         |                    | PSMCx   | PRL<7:0>                                         |         |         |             |  |

| bit 7                             |         |                    |         |                                                  |         |         | bit 0       |  |

|                                   |         |                    |         |                                                  |         |         |             |  |

| Legend:                           |         |                    |         |                                                  |         |         |             |  |

| R = Readable bit W = Writable bit |         |                    | bit     | U = Unimplemented bit, read as '0'               |         |         |             |  |

| u = Bit is uncha                  | anged   | x = Bit is unknown |         | -n/n = Value at POR and BOR/Value at all other F |         |         | ther Resets |  |

| '1' = Bit is set                  |         | '0' = Bit is clea  | ared    |                                                  |         |         |             |  |

bit 7-0

**PSMCxPRL<7:0>:** 16-bit Period Time Least Significant bits = PSMCxPR<7:0>

# REGISTER 26-26: PSMCxPRH: PSMC PERIOD COUNT HIGH BYTE REGISTER

| R/W-0/0       | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |

|---------------|---------|---------|---------|---------|---------|---------|---------|--|--|

| PSMCxPRH<7:0> |         |         |         |         |         |         |         |  |  |

| bit 7 bit 0   |         |         |         |         |         |         |         |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **PSMCxPRH<7:0>:** 16-bit Period Time Most Significant bits

= PSMCxPR<15:8>

# REGISTER 26-32: PSMCxSTR0: PSMC STEERING CONTROL REGISTER 0

| bit 1 | PxSTRB: PWM Steering PSMCxB Output Enable bit                                                                                                              |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | If PxMODE<3:0> = 0000 (Single-phase PWM):                                                                                                                  |

|       | <ol> <li>Single PWM output is active on pin PSMCxOUT1</li> <li>Single PWM output is not active on pin PSMCxOUT1. PWM drive is in inactive state</li> </ol> |

|       | If PxMODE<3:0> = 0001 (Complementary Single-phase PWM):                                                                                                    |

|       | 1 = Complementary PWM output is active on pin PSMCxB                                                                                                       |

|       | 0 = Complementary PWM output is not active on pin PSMCxB. PWM drive is in inactive state                                                                   |

|       | <u>IF PxMODE&lt;3:0&gt; = 1100 (3-phase Steering):</u> (1)                                                                                                 |

|       | 1 = PSMCxA and PSMCxF are high. PSMCxB, PMSCxC, PSMCxD and PMSCxE are low.                                                                                 |

|       | <ul><li>0 = 3-phase output combination is not active</li></ul>                                                                                             |

| bit 0 | PxSTRA: PWM Steering PSMCxA Output Enable bit                                                                                                              |

|       | <u>If PxMODE&lt;3:0&gt; = 000x (Single-phase PWM or Complementary PWM):</u>                                                                                |

|       | <ol> <li>Single PWM output is active on pin PSMCxA</li> </ol>                                                                                              |

|       | 0 = Single PWM output is not active on pin PSMCxA. PWM drive is in inactive state                                                                          |

|       | <u>IF PxMODE&lt;3:0&gt; = 1100 (3-phase Steering):</u> (1)                                                                                                 |

|       | 1 = PSMCxA and PSMCxD are high. PSMCxB, PMSCxC, PSMCxE and PMSCxF are low.                                                                                 |

|       | <ul><li>0 = 3-phase output combination is not active</li></ul>                                                                                             |

- **Note 1:** In 3-phase Steering mode, only one PSTRx bit should be set at a time. If more than one is set, then the lowest bit number steering combination has precedence.

- **2:** These bits are not implemented on PSMC2.

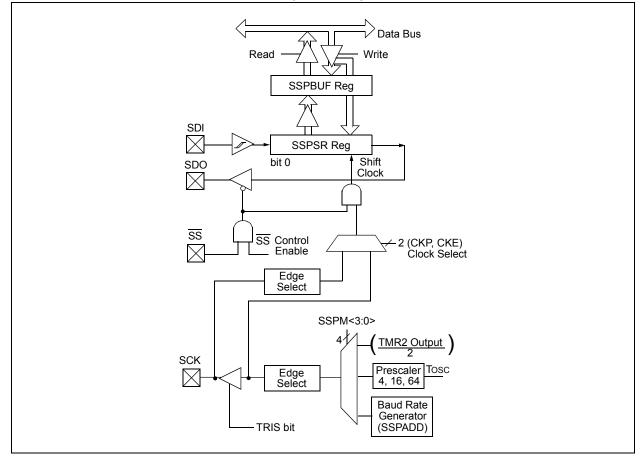

# 27.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

# 27.1 Master SSP (MSSP) Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

The SPI interface supports the following modes and features:

- Master mode

- Slave mode

- · Clock Parity

- Slave Select Synchronization (Slave mode only)

- · Daisy-chain connection of slave devices

Figure 27-1 is a block diagram of the SPI interface module.

# FIGURE 27-1: MSSP BLOCK DIAGRAM (SPI MODE)

| Name     | Bit 7       | Bit 6           | Bit 5          | Bit 4         | Bit 3  | Bit 2  | Bit 1  | Bit 0   | Reset<br>Values on<br>Page: |

|----------|-------------|-----------------|----------------|---------------|--------|--------|--------|---------|-----------------------------|

| APFCON1  | C2OUTSEL    | CCP1SEL         | SDOSEL         | SCKSEL        | SDISEL | TXSEL  | RXSEL  | CCP2SEL | 132                         |

| INTCON   | GIE         | PEIE            | TMR0IE         | INTE          | IOCIE  | TMR0IF | INTF   | IOCIF   | 97                          |

| PIE1     | TMR1GIE     | ADIE            | RCIE           | TXIE          | SSP1IE | CCP1IE | TMR2IE | TMR1IE  | 98                          |

| PIE2     | OSFIE       | C2IE            | C1IE           | EEIE          | BCL1IE | C4IE   | C3IE   | CCP2IE  | 99                          |

| PIR1     | TMR1GIF     | ADIF            | RCIF           | TXIF          | SSP1IF | CCP1IF | TMR2IF | TMR1IF  | 102                         |

| PIR2     | OSFIF       | C2IF            | C1IF           | EEIF          | BCL1IF | C4IF   | C3IF   | CCP2IF  | 103                         |

| SSP1ADD  |             |                 |                | ADD<          | :7:0>  |        |        |         | 343                         |

| SSP1BUF  | Synchronous | s Serial Port F | Receive Buffer | /Transmit Reo | gister |        |        |         | 294*                        |

| SSP1CON1 | WCOL        | SSPOV           | SSPEN          | CKP           |        | SSPM   | <3:0>  |         | 340                         |

| SSP1CON2 | GCEN        | ACKSTAT         | ACKDT          | ACKEN         | RCEN   | PEN    | RSEN   | SEN     | 341                         |

| SSP1CON3 | ACKTIM      | PCIE            | SCIE           | BOEN          | SDAHT  | SBCDE  | AHEN   | DHEN    | 340                         |

| SSP1MSK  |             | MSK<7:0>        |                |               |        |        |        |         | 343                         |

| SSP1STAT | SMP         | CKE             | D/A            | Р             | S      | R/W    | UA     | BF      | 338                         |

| TRISC    | TRISC7      | TRISC6          | TRISC5         | TRISC4        | TRISC3 | TRISC2 | TRISC1 | TRISA0  | 147                         |

| <b>TABLE 27-3</b> : | SUMMARY OF REGISTERS ASSOCIATED WITH I <sup>2</sup> C OPERATION |

|---------------------|-----------------------------------------------------------------|

| IADLL ZI-J.         | SUMMANT OF REGISTERS ASSOCIATED WITHING OF ERATION              |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by the MSSP module in I<sup>2</sup>C mode. \* Page provides register information.

Note 1: PIC16(L)F1789 only.

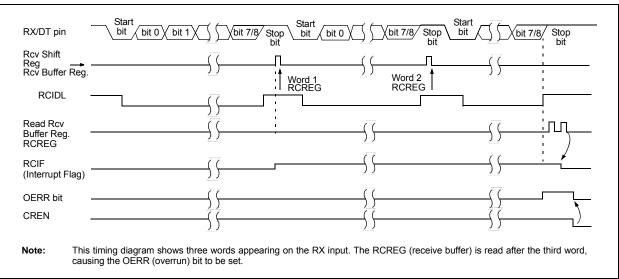

# 28.1.2.8 Asynchronous Reception Set-up:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 28.4 "EUSART Baud Rate Generator (BRG)").

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 4. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit reception is desired, set the RX9 bit.

- 6. Enable reception by setting the CREN bit.

- 7. The RCIF interrupt flag bit will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 8. Read the RCSTA register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

- 9. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register.

- 10. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

# 28.1.2.9 9-bit Address Detection Mode Set-up

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 28.4 "EUSART Baud Rate Generator (BRG)").

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- 3. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. Enable 9-bit reception by setting the RX9 bit.

- 6. Enable address detection by setting the ADDEN bit.

- 7. Enable reception by setting the CREN bit.

- The RCIF interrupt flag bit will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 9. Read the RCSTA register to get the error flags. The ninth data bit will always be set.

- 10. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register. Software determines if this is the device's address.

- 11. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 12. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

# FIGURE 28-5: ASYNCHRONOUS RECEPTION

# 28.5.2 SYNCHRONOUS SLAVE MODE

The following bits are used to configure the EUSART for synchronous slave operation:

- SYNC = 1

- CSRC = 0

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Clearing the CSRC bit of the TXSTA register configures the device as a slave. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the EUSART.

## 28.5.2.1 EUSART Synchronous Slave Transmit

The operation of the Synchronous Master and Slave modes are identical (see **Section 28.5.1.3 "Synchronous Master Transmission")**, except in the case of the Sleep mode. If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- 1. The first character will immediately transfer to the TSR register and transmit.

- 2. The second word will remain in TXREG register.

- 3. The TXIF bit will not be set.

- After the first character has been shifted out of TSR, the TXREG register will transfer the second character to the TSR and the TXIF bit will now be set.

- 5. If the PEIE and TXIE bits are set, the interrupt will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will call the Interrupt Service Routine.

- 28.5.2.2 Synchronous Slave Transmission Set-up:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for the CK pin (if applicable).

- 3. Clear the CREN and SREN bits.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. Enable transmission by setting the TXEN bit.

- 7. If 9-bit transmission is selected, insert the Most Significant bit into the TX9D bit.

- 8. Start transmission by writing the Least Significant eight bits to the TXREG register.

# TABLE 28-9:SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE<br/>TRANSMISSION

| Name    | Bit 7                         | Bit 6   | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0   | Register<br>on Page |

|---------|-------------------------------|---------|--------|--------|--------|--------|--------|---------|---------------------|

| APFCON1 | C2OUTSEL                      | CC1PSEL | SDOSEL | SCKSEL | SDISEL | TXSEL  | RXSEL  | CCP2SEL | 132                 |

| BAUDCON | ABDOVF                        | RCIDL   |        | SCKP   | BRG16  | -      | WUE    | ABDEN   | 356                 |

| INTCON  | GIE                           | PEIE    | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF   | 97                  |

| PIE1    | TMR1GIE                       | ADIE    | RCIE   | TXIE   | SSP1IE | CCP1IE | TMR2IE | TMR1IE  | 98                  |

| PIR1    | TMR1GIF                       | ADIF    | RCIF   | TXIF   | SSP1IF | CCP1IF | TMR2IF | TMR1IF  | 102                 |

| RCSTA   | SPEN                          | RX9     | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D    | 355                 |

| TRISC   | TRISC7                        | TRISC6  | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0  | 147                 |

| TXREG   | EUSART Transmit Data Register |         |        |        |        |        |        | 346*    |                     |

| TXSTA   | CSRC                          | TX9     | TXEN   | SYNC   | SENDB  | BRGH   | TRMT   | TX9D    | 354                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for synchronous slave transmission.

Page provides register information.

# 28.5.2.3 EUSART Synchronous Slave Reception

The operation of the Synchronous Master and Slave modes is identical (Section 28.5.1.5 "Synchronous Master Reception"), with the following exceptions:

- · Sleep

- CREN bit is always set, therefore the receiver is never idle

- SREN bit, which is a "don't care" in Slave mode

A character may be received while in Sleep mode by setting the CREN bit prior to entering Sleep. Once the word is received, the RSR register will transfer the data to the RCREG register. If the RCIE enable bit is set, the interrupt generated will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will branch to the interrupt vector.

- 28.5.2.4 Synchronous Slave Reception Set-up:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for both the CK and DT pins (if applicable).

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. If 9-bit reception is desired, set the RX9 bit.

- 5. Set the CREN bit to enable reception.

- The RCIF bit will be set when reception is complete. An interrupt will be generated if the RCIE bit was set.

- 7. If 9-bit mode is enabled, retrieve the Most Significant bit from the RX9D bit of the RCSTA register.

- 8. Retrieve the eight Least Significant bits from the receive FIFO by reading the RCREG register.

- 9. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

# TABLE 28-10: SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

| Name    | Bit 7                        | Bit 6   | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0   | Register<br>on Page |

|---------|------------------------------|---------|--------|--------|--------|--------|--------|---------|---------------------|

| APFCON1 | C2OUTSEL                     | CC1PSEL | SDOSEL | SCKSEL | SDISEL | TXSEL  | RXSEL  | CCP2SEL | 132                 |

| BAUDCON | ABDOVF                       | RCIDL   | _      | SCKP   | BRG16  | _      | WUE    | ABDEN   | 356                 |

| INTCON  | GIE                          | PEIE    | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF   | 97                  |

| PIE1    | TMR1GIE                      | ADIE    | RCIE   | TXIE   | SSP1IE | CCP1IE | TMR2IE | TMR1IE  | 98                  |

| PIR1    | TMR1GIF                      | ADIF    | RCIF   | TXIF   | SSP1IF | CCP1IF | TMR2IF | TMR1IF  | 102                 |

| RCREG   | EUSART Receive Data Register |         |        |        |        |        |        | 349*    |                     |

| RCSTA   | SPEN                         | RX9     | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D    | 355                 |

| TRISC   | TRISC7                       | TRISC6  | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0  | 147                 |

| TXSTA   | CSRC                         | TX9     | TXEN   | SYNC   | SENDB  | BRGH   | TRMT   | TX9D    | 354                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for synchronous slave reception.

\* Page provides register information.

| RETURN           | Return from Subroutine                                                                                                                                   |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RETURN                                                                                                                                           |

| Operands:        | None                                                                                                                                                     |

| Operation:       | $TOS \rightarrow PC$                                                                                                                                     |

| Status Affected: | None                                                                                                                                                     |

| Description:     | Return from subroutine. The stack<br>is POPed and the top of the stack<br>(TOS) is loaded into the program<br>counter. This is a 2-cycle<br>instruction. |

| RRF              | Rotate Right f through Carry                                                                                                                                                                                          |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RRF f,d                                                                                                                                                                                                       |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                     |

| Operation:       | See description below                                                                                                                                                                                                 |

| Status Affected: | С                                                                                                                                                                                                                     |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry flag. If 'd' is '0', the<br>result is placed in the W register.<br>If 'd' is '1', the result is placed<br>back in register 'f'. |

| → C → | Register f |  |

|-------|------------|--|

|       |            |  |

| RLF                                            | Rotate Left f through Carry                                                                                                                                                                                                                        | SLEEP                            | Enter Sleep mode                                                                                                                                                                                                                                                                                                                                                              |  |  |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:                                        | [label] RLF f,d                                                                                                                                                                                                                                    | Syntax:                          | [label] SLEEP                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| Operands:                                      | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                 | Operands:<br>Operation:          | None $00h \rightarrow WDT$ ,                                                                                                                                                                                                                                                                                                                                                  |  |  |

| Operation:<br>Status Affected:<br>Description: | See description below<br>C<br>The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry flag. If 'd' is '0', the<br>result is placed in the W register.<br>If 'd' is '1', the result is stored<br>back in register 'f'. | Status Affected:<br>Description: | $0 \rightarrow WDT$ prescaler,<br>$1 \rightarrow \overline{TO}$ ,<br>$0 \rightarrow \overline{PD}$<br>$\overline{TO}$ , $\overline{PD}$<br>The power-down Status bit, $\overline{PD}$ is<br>cleared. Time-out Status bit, $\overline{TO}$<br>is set. Watchdog Timer and its<br>prescaler are cleared.<br>The processor is put into Sleep<br>mode with the oscillator stopped. |  |  |

| Words:                                         | 1                                                                                                                                                                                                                                                  |                                  |                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Cycles:                                        | 1                                                                                                                                                                                                                                                  |                                  |                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Example:                                       | RLF REG1,0                                                                                                                                                                                                                                         | SUBLW                            | Subtract W from literal                                                                                                                                                                                                                                                                                                                                                       |  |  |

|                                                | Before Instruction                                                                                                                                                                                                                                 | Syntax:                          | [ <i>label</i> ] SUBLW k                                                                                                                                                                                                                                                                                                                                                      |  |  |

|                                                | REG1 = 1110                                                                                                                                                                                                                                        | Operands:                        | $0 \leq k \leq 255$                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                                                | 0110<br>C = 0                                                                                                                                                                                                                                      | Operation:                       | $k - (W) \to (W)$                                                                                                                                                                                                                                                                                                                                                             |  |  |

|                                                | After Instruction                                                                                                                                                                                                                                  | Status Affected:                 | C, DC, Z                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|                                                | REG1 = 1110<br>0110<br>W = 1100<br>1100                                                                                                                                                                                                            | Description:                     | The W register is subtracted (2's complement method) from the 8-bit literal 'k'. The result is placed in the W register.                                                                                                                                                                                                                                                      |  |  |

|                                                | C = 1                                                                                                                                                                                                                                              |                                  | -                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| <b>C =</b> 0 | W > k           |

|--------------|-----------------|

| <b>C =</b> 1 | $W \leq k$      |

| DC = 0       | W<3:0> > k<3:0> |

| DC = 1       | W<3:0> ≤ k<3:0> |

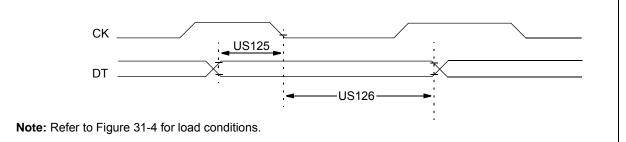

### FIGURE 31-15: EUSART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

# TABLE 31-20: EUSART SYNCHRONOUS RECEIVE REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated) |          |                                                                                |      |      |       |            |  |

|---------------------------------------------------------|----------|--------------------------------------------------------------------------------|------|------|-------|------------|--|

| Param.<br>No.                                           | Symbol   | Characteristic                                                                 | Min. | Max. | Units | Conditions |  |

| US125                                                   | TDTV2CKL | SYNC RCV (Master and Slave)<br>Data-hold before $CK \downarrow$ (DT hold time) | 10   | _    | ns    |            |  |

| US126                                                   | TCKL2DTL | Data-hold after CK $\downarrow$ (DT hold time)                                 | 15   |      | ns    |            |  |

# 33.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

# 33.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

# 33.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 33.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

# **Worldwide Sales and Service**

### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

Dallas Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

Canada - Toronto Tel: 905-673-0699 Fax: 905-673-6509

# ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

China - Chengdu Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

# ASIA/PACIFIC

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7828

Taiwan - Taipei Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351 Fax: 66-2-694-1350

### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820