Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                                |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x12b; D/A 1x8b, 3x5b                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1788-e-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### FIGURE 3-1: PROGRAM MEMORY MAP AND STACK FOR PIC16(L)F1788/9

|                                                                    | PC<14:0>           |                |  |  |  |  |  |

|--------------------------------------------------------------------|--------------------|----------------|--|--|--|--|--|

| CALL, CALLW 15<br>RETURN, RETLW<br>Interrupt, RETFIE Stack Level 0 |                    |                |  |  |  |  |  |

|                                                                    | Stack Level 1      |                |  |  |  |  |  |

|                                                                    | Stack Level 15     |                |  |  |  |  |  |

|                                                                    | Reset Vector       | 0000h          |  |  |  |  |  |

|                                                                    | •                  |                |  |  |  |  |  |

|                                                                    | Interrupt Vector   | 0004h          |  |  |  |  |  |

|                                                                    | Page 0             | 0005h          |  |  |  |  |  |

|                                                                    |                    | 07FFh          |  |  |  |  |  |

|                                                                    | Page 1             | 0800h<br>0FFFh |  |  |  |  |  |

| On-chip                                                            | Page 2             | 1000h          |  |  |  |  |  |

| Program <                                                          | 1 490 2            | 17FFh          |  |  |  |  |  |

| Memory                                                             | Page 3             | 1800h          |  |  |  |  |  |

|                                                                    |                    | 1FFFh          |  |  |  |  |  |

|                                                                    | Page 4             | 2000h          |  |  |  |  |  |

|                                                                    | •<br>•<br>•        |                |  |  |  |  |  |

|                                                                    | Page 7             | 3FFFh          |  |  |  |  |  |

|                                                                    | Rollover to Page 0 | 4000h          |  |  |  |  |  |

|                                                                    | •                  |                |  |  |  |  |  |

|                                                                    | Rollover to Page 7 | 7FFFh          |  |  |  |  |  |

|                                                                    |                    |                |  |  |  |  |  |

### 3.1.1 READING PROGRAM MEMORY AS DATA

There are two methods of accessing constants in program memory. The first method is to use tables of RETLW instructions. The second method is to set an FSR to point to the program memory.

#### 3.1.1.1 RETLW Instruction

The RETLW instruction can be used to provide access to tables of constants. The recommended way to create such a table is shown in Example 3-1.

| constants   |            |                     |

|-------------|------------|---------------------|

| BRW         |            | ;Add Index in W to  |

|             |            | ;program counter to |

|             |            | ;select data        |

| RETLW DAT   | ra0        | ;Index0 data        |

| RETLW DAT   | TA1        | ;Index1 data        |

| RETLW DAT   | ra2        |                     |

| RETLW DAT   | ГАЗ        |                     |

|             |            |                     |

|             |            |                     |

| my_function |            |                     |

| ; LOTS (    | OF CODE    |                     |

| MOVLW       | DATA_IN    | DEX                 |

| call cons   | stants     |                     |

| ; THE CO    | ONSTANT IS | IN W                |

|             |            |                     |

The BRW instruction makes this type of table very simple to implement. If your code must remain portable with previous generations of microcontrollers, then the BRW instruction is not available so the older table read method must be used.

#### 3.1.1.2 Indirect Read with FSR

The program memory can be accessed as data by setting bit 7 of the FSRxH register and reading the matching INDFx register. The MOVIW instruction will place the lower eight bits of the addressed word in the W register. Writes to the program memory cannot be performed via the INDF registers. Instructions that access the program memory via the FSR require one extra instruction cycle to complete. Example 3-2 demonstrates accessing the program memory via an FSR.

The high directive will set bit<7> if a label points to a location in program memory.

#### TABLE 3-12: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

|                                                |            | •••             |       |         |         |                      |            | /       |         |                      |                                 |

|------------------------------------------------|------------|-----------------|-------|---------|---------|----------------------|------------|---------|---------|----------------------|---------------------------------|

| Addr                                           | Name       | Bit 7           | Bit 6 | Bit 5   | Bit 4   | Bit 3                | Bit 2      | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

| Banl                                           | Bank 11-15 |                 |       |         |         |                      |            |         |         |                      |                                 |

| 58Ch                                           |            |                 |       |         |         |                      |            |         |         |                      |                                 |

| <br>590h                                       |            | Unimplemente    | d     |         |         |                      |            |         |         | —                    | —                               |

| 591h                                           | DAC2CON0   | DAC2EN          |       | DAC2OE1 | DAC2OE2 | DAC2P                | SS<1:0>    |         |         | 0-00 00              | 0-00 00                         |

| 592h                                           | DAC2CON1   |                 |       |         |         | DAC2R<4:0>           |            |         | 0 0000  | 0 0000               |                                 |

| 593h                                           | DAC3CON0   | DAC3EN          |       | DAC3OE1 | DAC3OE2 | DAC30E2 DAC3PSS<1:0> |            | 0-00 00 | 0-00 00 |                      |                                 |

| 594h                                           | DAC3CON1   |                 |       |         |         | DAC3R<4:0>           |            | 0 0000  | 0 0000  |                      |                                 |

| 595h                                           | DAC4CON0   | DAC4EN          |       | DAC4OE1 | DAC4OE2 | DAC4P                | SS<1:0>    |         |         | 0-00 00              | 0-00 00                         |

| 596h                                           | DAC4CON1   |                 |       |         |         |                      | DAC4R<4:0> |         |         | 0 0000               | 0 0000                          |

| 597h<br><br>59Fh                               | _          | Unimplemented — |       |         |         |                      |            | _       | _       |                      |                                 |

| Banl                                           | k 16-28    |                 |       |         |         |                      |            |         |         |                      |                                 |

| x0Ch<br>or<br>x8Ch<br>to<br>x1Fh<br>or<br>x9Fh | -          | Unimplemente    | d     |         |         |                      |            |         |         |                      |                                 |

Legend: x = unknown, u = unchanged, g = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

**Note 1:** These registers can be addressed from any bank.

**2:** Unimplemented, read as '1'.

3: PIC16(L)F1789 only.

4: PIC16F1788/9 only.

#### 9.1.1 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction

- SLEEP instruction will execute as a NOP.

- WDT and WDT prescaler will not be cleared

- TO bit of the STATUS register will not be set

- PD bit of the STATUS register will not be cleared.

- If the interrupt occurs **during or after** the execution of a **SLEEP** instruction

- SLEEP instruction will be completely executed

- Device will immediately wake-up from Sleep

- WDT and WDT prescaler will be cleared

- TO bit of the STATUS register will be set

- PD bit of the STATUS register will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

| CLKIN <sup>(1)</sup><br>CLKOUT <sup>(2)</sup> |                                                                                                                                                                                                                                                                                                           |                |                 | Q1 Q2 Q3 Q4<br>/~_/~_/<br>\/          | Q1 Q2 Q3 Q4<br>/\_/\_/ | Q1 Q2 Q3 Q4<br>                       |  |  |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------|---------------------------------------|------------------------|---------------------------------------|--|--|

| Interrupt flag                                |                                                                                                                                                                                                                                                                                                           |                | Interrupt Laten | су <sup>(4)</sup>                     |                        | · · · · · · · · · · · · · · · · · · · |  |  |

| GIE bit<br>(INTCON reg.                       | Processor<br>Sleep                                                                                                                                                                                                                                                                                        | in<br>✦        |                 |                                       |                        |                                       |  |  |

| Instruction Flow<br>PC                        |                                                                                                                                                                                                                                                                                                           | <u>C + 2 X</u> | PC + 2          | PC+2                                  | X 0004h                | X 0005h                               |  |  |

| Instruction {                                 | Inst(PC) = Sleep Inst(PC + 1)                                                                                                                                                                                                                                                                             | <u> </u>       | Inst(PC + 2)    | · · · · · · · · · · · · · · · · · · · | Inst(0004h)            | Inst(0005h)                           |  |  |

| Instruction {<br>Executed {                   | Inst(PC - 1) Sleep                                                                                                                                                                                                                                                                                        | 1<br>1<br>1    | Inst(PC + 1)    | Forced NOP                            | Forced NOP             | Inst(0004h)                           |  |  |

| 2:<br>3:                                      | <ul> <li>Note 1: External clock. High, Medium, Low mode assumed.</li> <li>2: CLKOUT is shown here for timing reference.</li> <li>3: Tost = 1024 Tosc; This delay does not apply to EC, RC and INTOSC Oscillator modes or Two-Speed Start-up (See Section 6.4 "Two-Speed Clock Start-up Mode").</li> </ul> |                |                 |                                       |                        |                                       |  |  |

#### FIGURE 9-1: WAKE-UP FROM SLEEP THROUGH INTERRUPT

#### 9.3 Register Definitions: Voltage Regulator Control

#### REGISTER 9-1: VREGCON: VOLTAGE REGULATOR CONTROL REGISTER<sup>(1)</sup>

| U-0             | U-0 | U-0           | U-0 | U-0 | U-0             | R/W-0/0 | R/W-1/1  |

|-----------------|-----|---------------|-----|-----|-----------------|---------|----------|

| —               |     | —             | _   | _   | —               | VREGPM  | Reserved |

| bit 7           |     |               |     |     |                 |         | bit 0    |

|                 |     |               |     |     |                 |         |          |

| Legend:         |     |               |     |     |                 |         |          |

| R = Readable bi | +   | M = M/ritable | hit |     | monted hit read | ae 'O'  |          |

| -                    |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-2 Unimplemented: Read as '0'

bit 1 VREGPM: Voltage Regulator Power Mode Selection bit

- 1 = Low-Power Sleep mode enabled in Sleep<sup>(2)</sup> Draws lowest current in Sleep, slower wake-up

- Normal-Power mode enabled in Sleep<sup>(2)</sup>

Draws higher current in Sleep, faster wake-up

- bit 0 Reserved: Read as '1'. Maintain this bit set.

Note 1: "F" devices only.

2: See Section 31.0 "Electrical Specifications".

| Name                                                                                         | Bit 7    | Bit 6    | Bit 5                 | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | Register on<br>Page |

|----------------------------------------------------------------------------------------------|----------|----------|-----------------------|----------|----------|----------|----------|----------|---------------------|

| INTCON                                                                                       | GIE      | PEIE     | TMR0IE                | INTE     | IOCIE    | TMR0IF   | INTF     | RAIF     | 97                  |

| IOCBF                                                                                        | IOCBF7   | IOCBF6   | IOCBF5                | IOCBF4   | IOCBF3   | IOCBF2   | IOCBF1   | IOCBF0   | 164                 |

| IOCBN                                                                                        | IOCBN7   | IOCBN6   | IOCBN5                | IOCBN4   | IOCBN3   | IOCBN2   | IOCBN1   | IOCBN0   | 163                 |

| IOCBP                                                                                        | IOCBP7   | IOCBP6   | IOCBP5                | IOCBP4   | IOCBP3   | IOCBP2   | IOCBP1   | IOCBP0   | 163                 |

| PIE1                                                                                         | TMR1GIE  | ADIE     | RCIE                  | TXIE     | SSP1IE   | CCP1IE   | TMR2IE   | TMR1IE   | 98                  |

| PIE2                                                                                         | OSFIE    | C2IE     | C1IE                  | EEIE     | BCL1IE   | C4IE     | C3IE     | CCP2IE   | 99                  |

| PIE3                                                                                         | _        | —        | _                     | CCP3IE   | —        | —        | _        | —        | 100                 |

| PIE4                                                                                         | PSMC4TIE | PSMC3TIE | PSMC2TIE              | PSMC1TIE | PSMC4SIE | PSMC3SIE | PSMC2SIE | PSMC1SIE | 101                 |

| PIR1                                                                                         | TMR1GIF  | ADIF     | RCIF                  | TXIF     | SSP1IF   | CCP1IF   | TMR2IF   | TMR1IF   | 98                  |

| PIR2                                                                                         | OSFIF    | C2IF     | C1IF                  | EEIF     | BCL1IF   | C4IF     | C3IF     | CCP2IF   | 103                 |

| PIR3                                                                                         | _        | —        | _                     | CCP3IF   | —        | —        | _        | —        | 104                 |

| PIR4                                                                                         | PSMC4TIF | PSMC3TIF | PSMC2TIF              | PSMC1TIF | PSMC4SIF | PSMC3SIF | PSMC2SIF | PSMC1SIF | 105                 |

| STATUS                                                                                       | _        | —        | _                     | TO       | PD       | Z        | DC       | С        | 31                  |

| VREGCON                                                                                      | —        | —        | —                     | _        | —        | —        | VREGPM   | Reserved | 110                 |

| WDTCON                                                                                       | _        | _        | WDTPS<4:0> SWDTEN 114 |          |          |          |          |          |                     |

| l agende – unimplemented legetion, read as 'o'. Shaded calls are not used in Dower Down mode |          |          |                       |          |          |          |          |          |                     |

#### TABLE 9-1: SUMMARY OF REGISTERS ASSOCIATED WITH POWER-DOWN MODE

Legend: — = unimplemented location, read as '0'. Shaded cells are not used in Power-Down mode.

### 12.7 Register Definitions: EEPROM and Flash Control

#### REGISTER 12-1: EEDATL: EEPROM DATA LOW BYTE REGISTER

| R/W-x/u              | R/W-x/u | R/W-x/u              | R/W-x/u | R/W-x/u           | R/W-x/u              | R/W-x/u             | R/W-x/u |

|----------------------|---------|----------------------|---------|-------------------|----------------------|---------------------|---------|

|                      |         |                      | EEDA    | T<7:0>            |                      |                     |         |

| bit 7                |         |                      |         |                   |                      |                     | bit C   |

|                      |         |                      |         |                   |                      |                     |         |

| Legend:              |         |                      |         |                   |                      |                     |         |

| R = Readable bit     |         | W = Writable bit     |         | U = Unimplemer    | nted bit, read as '0 | ,                   |         |

| u = Bit is unchanged |         | x = Bit is unknown   |         | -n/n = Value at F | POR and BOR/Valu     | ue at all other Res | ets     |

| '1' = Bit is set     |         | '0' = Bit is cleared |         |                   |                      |                     |         |

bit 7-0

EEDAT<7:0>: Read/write value for EEPROM data byte or Least Significant bits of program memory

#### REGISTER 12-2: EEDATH: EEPROM DATA HIGH BYTE REGISTER

| U-0   | U-0 | R/W-x/u     | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|-------------|---------|---------|---------|---------|---------|

| —     | —   | EEDAT<13:8> |         |         |         |         |         |

| bit 7 |     |             |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

|                      |                      |                                                       |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 EEDAT<13:8>: Read/write value for Most Significant bits of program memory

#### REGISTER 12-3: EEADRL: EEPROM ADDRESS REGISTER

| R/W-0/0    | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |

|------------|---------|---------|---------|---------|---------|---------|---------|--|--|

| EEADR<7:0> |         |         |         |         |         |         |         |  |  |

| bit 7      |         |         |         |         |         |         | bit 0   |  |  |

|            |         |         |         |         |         |         |         |  |  |

| Legend:    |         |         |         |         |         |         |         |  |  |

| Legena.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

|                      |                      |                                                       |

bit 7-0 EEADR<7:0>: Specifies the Least Significant bits for program memory address or EEPROM address

#### REGISTER 12-4: EEADRH: EEPROM ADDRESS HIGH BYTE REGISTER

| U-1   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|---------|---------|---------|-------------|---------|---------|---------|

| (1)   |         |         |         | EEADR<14:8> |         |         |         |

| bit 7 |         |         |         |             |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7 Unimplemented: Read as '1'

bit 6-0 EEADR<14:8>: Specifies the Most Significant bits for program memory address or EEPROM address

Note 1: Unimplemented, read as '1'.

### 13.12 Register Definitions: PORTE

#### REGISTER 13-34: PORTE: PORTE REGISTER

| U-0              | U-0   | U-0               | U-0  | R-x/u                                                 | R/W-x/u            | R/W-x/u            | R/W-x/u            |  |  |

|------------------|-------|-------------------|------|-------------------------------------------------------|--------------------|--------------------|--------------------|--|--|

| 0-0              | 0-0   | 0-0               | 0-0  | 1\-X/U                                                |                    |                    | -                  |  |  |

| —                | —     | —                 | —    | RE3                                                   | RE2 <sup>(1)</sup> | RE1 <sup>(1)</sup> | RE0 <sup>(1)</sup> |  |  |

| bit 7            |       | •                 |      |                                                       |                    |                    | bit C              |  |  |

|                  |       |                   |      |                                                       |                    |                    |                    |  |  |

| Legend:          |       |                   |      |                                                       |                    |                    |                    |  |  |

| R = Readable I   | oit   | W = Writable I    | bit  | U = Unimplemented bit, read as '0'                    |                    |                    |                    |  |  |

| u = Bit is uncha | anged | x = Bit is unkn   | own  | -n/n = Value at POR and BOR/Value at all other Resets |                    |                    |                    |  |  |

| '1' = Bit is set |       | '0' = Bit is clea | ared |                                                       |                    |                    |                    |  |  |

| bit 7-4 | Unimplemented: Read as '0'                  |

|---------|---------------------------------------------|

| bit 3-0 | RE<3:0>: PORTE Input Pin bit <sup>(1)</sup> |

|         | 1 = Port pin is > Vін                       |

|         | 0 = Port pin is < VI∟                       |

|         |                                             |

Note 1: RE<2:0> are available on PIC16(L)F1789 only.

#### REGISTER 13-35: TRISE: PORTE TRI-STATE REGISTER

| U-0   | U-0 | U-0 | U-0 | U-1 <sup>(1)</sup> | R/W-1/1               | R/W-1/1               | R/W-1/1               |

|-------|-----|-----|-----|--------------------|-----------------------|-----------------------|-----------------------|

| _     | —   | _   | _   | _                  | TRISE2 <sup>(2)</sup> | TRISE1 <sup>(2)</sup> | TRISE0 <sup>(2)</sup> |

| bit 7 |     |     |     |                    |                       |                       | bit 0                 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 3 Unimplemented: Read as '1'

bit 2-0 **TRISA<2:0>:** PORTA Tri-State Control bit<sup>(2)</sup> 1 = PORTA pin configured as an input (tri-stated) 0 = PORTA pin configured as an output

**Note 1:** Unimplemented, read as '1'.

2: TRISE<2:0> are available on PIC16(L)F1789 only.

| R/W-0/0         | R/W-0/0                                                    | R/W-0/0                                           | R/W-0/0         | R/W-0/0        | R/W-0/0          | R/W-0/0        | R/W-0/0      |  |  |

|-----------------|------------------------------------------------------------|---------------------------------------------------|-----------------|----------------|------------------|----------------|--------------|--|--|

| TRIGSEL<3:0>    |                                                            |                                                   |                 | CHSN           | I<3:0>           |                |              |  |  |

| bit 7           |                                                            |                                                   |                 | ·              |                  |                | bit          |  |  |

|                 |                                                            |                                                   |                 |                |                  |                |              |  |  |

| Legend:         |                                                            |                                                   |                 |                |                  |                |              |  |  |

| R = Readable    | e bit                                                      | W = Writable                                      | bit             | U = Unimpler   | nented bit, read | d as '0'       |              |  |  |

| u = Bit is unc  | hanged                                                     | x = Bit is unk                                    | nown            | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |  |  |

| '1' = Bit is se | t                                                          | '0' = Bit is cle                                  | ared            |                |                  |                |              |  |  |

|                 |                                                            |                                                   |                 |                |                  |                |              |  |  |

| bit 7-4         | TRIGSEL<3                                                  | :0>: ADC Auto-                                    | conversion Tri  | gger Source Se | election bits    |                |              |  |  |

|                 | 1111 = PSN                                                 | /IC4 Falling Mat                                  | ch Event        |                |                  |                |              |  |  |

|                 |                                                            | /IC4 Rising Mat                                   |                 |                |                  |                |              |  |  |

|                 |                                                            | /IC4 Period Mat                                   |                 |                |                  |                |              |  |  |

|                 |                                                            | AC2 Falling Edg                                   |                 |                |                  |                |              |  |  |

|                 |                                                            | /IC2 Rising Edg<br>/IC2 Period Mat                |                 |                |                  |                |              |  |  |

|                 |                                                            | IC2 Feriod Mat                                    |                 |                |                  |                |              |  |  |

|                 |                                                            | IC1 Rising Edg                                    |                 |                |                  |                |              |  |  |

|                 |                                                            | IC1 Period Mat                                    |                 |                |                  |                |              |  |  |

|                 |                                                            | 011 = Reserved. Auto-conversion Trigger disabled. |                 |                |                  |                |              |  |  |

|                 |                                                            | = CCP2, Auto-conversion Trigger                   |                 |                |                  |                |              |  |  |

|                 |                                                            | P1, Auto-conver                                   | sion Trigger    |                |                  |                |              |  |  |

|                 | 0000 = Disa                                                | abled                                             |                 |                |                  |                |              |  |  |

| bit 3-0         | CHSN<3:0>: Negative Differential Input Channel Select bits |                                                   |                 |                |                  |                |              |  |  |

|                 | When ADON = 0, all multiplexer inputs are disconnected.    |                                                   |                 |                |                  |                |              |  |  |

|                 |                                                            | C Negative refe                                   | erence – select | ed by ADNREF   | =                |                |              |  |  |

|                 | 1110 = AN                                                  |                                                   |                 |                |                  |                |              |  |  |

|                 | 1101 = AN<br>1100 = AN                                     | -                                                 |                 |                |                  |                |              |  |  |

|                 | 1011 = AN                                                  |                                                   |                 |                |                  |                |              |  |  |

|                 | 1010 = AN                                                  |                                                   |                 |                |                  |                |              |  |  |

|                 | 1001 = AN                                                  |                                                   |                 |                |                  |                |              |  |  |

|                 | 1000 = AN                                                  |                                                   |                 |                |                  |                |              |  |  |

|                 | 0111 = AN                                                  | 7(1)                                              |                 |                |                  |                |              |  |  |

|                 | 0110 = AN                                                  |                                                   |                 |                |                  |                |              |  |  |

|                 | 0101 = AN                                                  |                                                   |                 |                |                  |                |              |  |  |

|                 | 0100 = AN<br>0011 = AN                                     |                                                   |                 |                |                  |                |              |  |  |

|                 | 0011 = AN<br>0010 = AN                                     | -                                                 |                 |                |                  |                |              |  |  |

|                 | 0010 = AN<br>0001 = AN                                     |                                                   |                 |                |                  |                |              |  |  |

|                 | 0000 = AN                                                  |                                                   |                 |                |                  |                |              |  |  |

#### Note 1: PIC16(L)F1789 only. For PIC16(L)F1788, "Reserved. No channel connected."

#### 26.7 Auto-Shutdown

Auto-shutdown is a method to immediately override the PSMC output levels with specific overrides that allow for safe shutdown of the application.

Auto-shutdown includes a mechanism to allow the application to restart under different conditions.

Auto-shutdown is enabled with the PxASDEN bit of the PSMC Auto-shutdown Control (PSMCxASDC) register (Register 26-16). All auto-shutdown features are enabled when PxASDEN is set and disabled when cleared.

#### 26.7.1 SHUTDOWN

There are two ways to generate a shutdown event:

- Manual

- External Input

#### 26.7.1.1 Manual Override

The auto-shutdown control register can be used to manually override the pin functions. Setting the PxASE bit of the PSMC Auto-shutdown Control (PSMCxASDC) register (Register 26-16) generates a software shut-down event.

The auto-shutdown override will persist as long as PxASE remains set.

#### 26.7.1.2 External Input Source

Any of the given sources that are available for event generation are also available for system shut-down. This is so that external circuitry can monitor and force a shutdown without any software overhead. Auto-shutdown sources are selected with the PSMC Auto-shutdown Source (PSMCxASDS) register (Register 26-18).

When any of the selected external auto-shutdown sources go high, the PxASE bit is set and an auto-shutdown interrupt is generated.

**Note:** The external shutdown sources are level sensitive, not edge sensitive. The shutdown condition will persist as long as the circuit is driving the appropriate logic level.

#### 26.7.2 PIN OVERRIDE LEVELS

The logic levels driven to the output pins during an auto-shutdown event are determined by the PSMC Auto-shutdown Output Level (PSMCxASDL) register (Register 26-17).

#### 26.7.2.1 PIN Override Enable

Setting the PxASDOV bit of the PSMC Auto-shutdown Control (PSMCxASDC) register (Register 26-16) will also force the override levels onto the pins, exactly like what happens when the auto-shutdown is used. However, whereas setting PxASE causes an auto-shutdown interrupt, setting PxASDOV does not generate an interrupt.

#### 26.7.3 RESTART FROM AUTO-SHUTDOWN

After an auto-shutdown event has occurred, there are two ways for the module to resume operation:

- Manual restart

- · Automatic restart

The restart method is selected with the PxARSEN bit of the PSMC Auto-shutdown Control (PSMCxASDC) register (Register 26-16).

#### 26.7.3.1 Manual Restart

When PxARSEN is cleared, and once the PxASDE bit is set, it will remain set until cleared by software.

The PSMC will restart on the period event after PxASDE bit is cleared in software.

#### 26.7.3.2 Auto-Restart

When PxARSEN is set, the PxASDE bit will clear automatically when the source causing the Reset and no longer asserts the shut-down condition.

The PSMC will restart on the next period event after the auto-shutdown condition is removed.

Examples of manual and automatic restart are shown in Figure 26-20.

Note: Whether manual or auto-restart is selected, the PxASDE bit cannot be cleared in software when the auto-shutdown condition is still present.

| R/W-0/0                                     | U-0                                                 | U-0              | R/W-0/0       | R/W-0/0        | R/W-0/0          | R/W-0/0          | U-0         |

|---------------------------------------------|-----------------------------------------------------|------------------|---------------|----------------|------------------|------------------|-------------|

| PxASDSIN                                    | _                                                   | _                | PxASDSC4      | PxASDSC3       | PxASDSC2         | PxASDSC1         | _           |

| bit 7                                       |                                                     |                  | ļ             |                |                  | I                | bit 0       |

|                                             |                                                     |                  |               |                |                  |                  |             |

| Legend:                                     |                                                     |                  |               |                |                  |                  |             |

| R = Readable                                | bit                                                 | W = Writable     | bit           | U = Unimpler   | nented bit, read | as '0'           |             |

| u = Bit is uncha                            | anged                                               | x = Bit is unkr  | nown          | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is set                            |                                                     | '0' = Bit is cle | ared          |                |                  |                  |             |

|                                             |                                                     |                  |               |                |                  |                  |             |

| bit 7                                       | PxASDSIN: A                                         | Auto-shutdown    | occurs on PSI | MCxIN pin      |                  |                  |             |

|                                             |                                                     | utdown will occ  |               |                | true             |                  |             |

|                                             | 0 = PSMCxI                                          | N pin will not c | ause auto-shu | utdown         |                  |                  |             |

| bit 6-5                                     | Unimplemen                                          | ted: Read as '   | 0'            |                |                  |                  |             |

| bit 4                                       | PxASDSC4:                                           | Auto-shutdown    | occurs on syr | nc_C4OUT ou    | tput             |                  |             |

|                                             |                                                     | utdown will occ  |               |                | it goes true     |                  |             |

|                                             | $0 = sync_C^2$                                      | 40UT will not c  | ause auto-shu | utdown         |                  |                  |             |

| bit 3                                       | PxASDSC3:                                           | Auto-shutdown    | occurs on syr | nc_C3OUT ou    | tput             |                  |             |

|                                             |                                                     | utdown will occ  |               |                | it goes true     |                  |             |

|                                             | $0 = sync_C3$                                       | 30UT will not c  | ause auto-shu | utdown         |                  |                  |             |

| bit 2                                       | PxASDSC2:                                           | Auto-shutdown    | occurs on syr | nc_C2OUT ou    | tput             |                  |             |

|                                             |                                                     | utdown will occ  |               |                | it goes true     |                  |             |

| 0 = sync_C2OUT will not cause auto-shutdown |                                                     |                  |               |                |                  |                  |             |

| bit 1                                       | PxASDSC1: Auto-shutdown occurs on sync_C1OUT output |                  |               |                |                  |                  |             |

|                                             |                                                     | utdown will occ  |               |                | goes true        |                  |             |

|                                             |                                                     | 1OU will not ca  |               | down           |                  |                  |             |

| bit 0                                       | Unimplemen                                          | ted: Read as '   | 0'            |                |                  |                  |             |

|                                             |                                                     |                  |               |                |                  |                  |             |

### REGISTER 26-18: PSMCxASDS: PSMC AUTO-SHUTDOWN SOURCE REGISTER

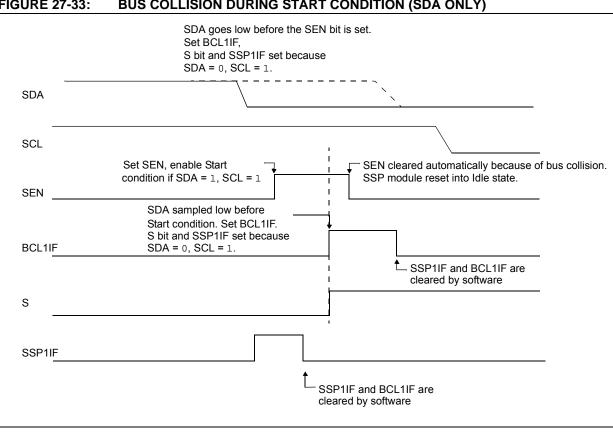

#### 27.6.13.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- SDA or SCL are sampled low at the beginning of the Start condition (Figure 27-32).

- b) SCL is sampled low before SDA is asserted low (Figure 27-33).

During a Start condition, both the SDA and the SCL pins are monitored.

If the SDA pin is already low, or the SCL pin is already low, then all of the following occur:

- the Start condition is aborted,

- · the BCL1IF flag is set and

- · the MSSP module is reset to its Idle state (Figure 27-32).

The Start condition begins with the SDA and SCL pins deasserted. When the SDA pin is sampled high, the Baud Rate Generator is loaded and counts down. If the SCL pin is sampled low while SDA is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 27-34). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to zero; if the SCL pin is sampled as '0' during this time, a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

#### FIGURE 27-33: **BUS COLLISION DURING START CONDITION (SDA ONLY)**

#### REGISTER 27-5: SSPMSK: SSP MASK REGISTER

| R/W-1/1                             | R/W-1/1                                                                                                                                                                                                           | R/W-1/1                                                                                                                                                                                                                                                                                                                                             | R/W-1/1          | R/W-1/1                                               | R/W-1/1          | R/W-1/1  | R/W-1/1 |  |  |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------|------------------|----------|---------|--|--|

|                                     |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                     | MSł              | <<7:0>                                                |                  |          |         |  |  |

| bit 7                               |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                     |                  |                                                       |                  |          | bit 0   |  |  |

|                                     |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                     |                  |                                                       |                  |          |         |  |  |

| Legend:                             |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                     |                  |                                                       |                  |          |         |  |  |

| R = Readable                        | e bit                                                                                                                                                                                                             | W = Writable                                                                                                                                                                                                                                                                                                                                        | W = Writable bit |                                                       | nented bit, read | l as '0' |         |  |  |

| u = Bit is unchanged x = Bit is unk |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                     | nown             | -n/n = Value at POR and BOR/Value at all other Resets |                  |          |         |  |  |

| '1' = Bit is set                    |                                                                                                                                                                                                                   | '0' = Bit is cle                                                                                                                                                                                                                                                                                                                                    | ared             |                                                       |                  |          |         |  |  |

| bit 7-1                             | MSK<7:1>:                                                                                                                                                                                                         | Mask bits                                                                                                                                                                                                                                                                                                                                           |                  |                                                       |                  |          |         |  |  |

|                                     | <ul> <li>1 = The received address bit n is compared to SSPADD<n> to detect I<sup>2</sup>C address match</n></li> <li>0 = The received address bit n is not used to detect I<sup>2</sup>C address match</li> </ul> |                                                                                                                                                                                                                                                                                                                                                     |                  |                                                       |                  |          |         |  |  |

| bit 0                               | I <sup>2</sup> C Slave me<br>1 = The rec                                                                                                                                                                          | <b>MSK&lt;0&gt;:</b> Mask bit for I <sup>2</sup> C Slave mode, 10-bit Address<br>I <sup>2</sup> C Slave mode, 10-bit address (SSPM<3:0> = 0111 or 1111):<br>1 = The received address bit 0 is compared to SSPADD<0> to detect I <sup>2</sup> C address match<br>0 = The received address bit 0 is not used to detect I <sup>2</sup> C address match |                  |                                                       |                  |          |         |  |  |

$I^2C$  Slave mode, 7-bit address, the bit is ignored

'0' = Bit is cleared

### REGISTER 27-6: SSPADD: MSSP ADDRESS AND BAUD RATE REGISTER (I<sup>2</sup>C MODE)

| R/W-0/0         | R/W-0/0 | R/W-0/0         | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|-----------------|---------|-----------------|---------|----------------|------------------|------------------|--------------|

|                 |         |                 | ADD     | <7:0>          |                  |                  |              |

| bit 7           |         |                 |         |                |                  |                  | bit 0        |

|                 |         |                 |         |                |                  |                  |              |

| Legend:         |         |                 |         |                |                  |                  |              |

| R = Readable    | bit     | W = Writable I  | bit     | U = Unimpler   | nented bit, read | d as '0'         |              |

| u = Bit is unch | anged   | x = Bit is unkn | iown    | -n/n = Value a | at POR and BC    | R/Value at all o | other Resets |

#### Master mode:

1' = Bit is set

bit 7-0 ADD<7:0>: Baud Rate Clock Divider bits SCL pin clock period = ((ADD<7:0> + 1) \*4)/Fosc

#### <u>10-Bit Slave mode — Most Significant Address Byte:</u>

- bit 7-3 **Not used:** Unused for Most Significant Address byte. Bit state of this register is a "don't care". Bit pattern sent by master is fixed by I<sup>2</sup>C specification and must be equal to '11110'. However, those bits are compared by hardware and are not affected by the value in this register.

- bit 2-1 ADD<2:1>: Two Most Significant bits of 10-bit address

- bit 0 Not used: Unused in this mode. Bit state is a "don't care".

#### <u>10-Bit Slave mode — Least Significant Address Byte:</u>

bit 7-0 ADD<7:0>: Eight Least Significant bits of 10-bit address

#### 7-Bit Slave mode:

bit 0 Not used: Unused in this mode. Bit state is a "don't care".

#### 28.1.2.4 Receive Framing Error

Each character in the receive FIFO buffer has a corresponding framing error Status bit. A framing error indicates that a Stop bit was not seen at the expected time. The framing error status is accessed via the FERR bit of the RCSTA register. The FERR bit represents the status of the top unread character in the receive FIFO. Therefore, the FERR bit must be read before reading the RCREG.

The FERR bit is read-only and only applies to the top unread character in the receive FIFO. A framing error (FERR = 1) does not preclude reception of additional characters. It is not necessary to clear the FERR bit. Reading the next character from the FIFO buffer will advance the FIFO to the next character and the next corresponding framing error.

The FERR bit can be forced clear by clearing the SPEN bit of the RCSTA register which resets the EUSART. Clearing the CREN bit of the RCSTA register does not affect the FERR bit. A framing error by itself does not generate an interrupt.

| Note: | If all receive characters in the receive  |

|-------|-------------------------------------------|

|       | FIFO have framing errors, repeated reads  |

|       | of the RCREG will not clear the FERR bit. |

#### 28.1.2.5 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before the FIFO is accessed. When this happens the OERR bit of the RCSTA register is set. The characters already in the FIFO buffer can be read but no additional characters will be received until the error is cleared. The error must be cleared by either clearing the CREN bit of the RCSTA register or by resetting the EUSART by clearing the SPEN bit of the RCSTA register.

#### 28.1.2.6 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth and Most Significant data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

#### 28.1.2.7 Address Detection

A special Address Detection mode is available for use when multiple receivers share the same transmission line, such as in RS-485 systems. Address detection is enabled by setting the ADDEN bit of the RCSTA register.

Address detection requires 9-bit character reception. When address detection is enabled, only characters with the ninth data bit set will be transferred to the receive FIFO buffer, thereby setting the RCIF interrupt bit. All other characters will be ignored.

Upon receiving an address character, user software determines if the address matches its own. Upon address match, user software must disable address detection by clearing the ADDEN bit before the next Stop bit occurs. When user software detects the end of the message, determined by the message protocol used, software places the receiver back into the Address Detection mode by setting the ADDEN bit.

|        | SYNC = 0, BRGH = 0, BRG16 = 0 |            |                             |                   |            |                             |                   |            |                             |                    |            |                             |  |

|--------|-------------------------------|------------|-----------------------------|-------------------|------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|------------|-----------------------------|--|

| BAUD   | Fosc = 32.000 MHz             |            |                             | Fosc = 20.000 MHz |            |                             | Fosc = 18.432 MHz |            |                             | Fosc = 11.0592 MHz |            |                             |  |

|        | Actual<br>Rate                | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 300    | _                             |            | _                           |                   |            | _                           | _                 | _          | _                           |                    | _          | _                           |  |

| 1200   | —                             | _          | _                           | 1221              | 1.73       | 255                         | 1200              | 0.00       | 239                         | 1200               | 0.00       | 143                         |  |

| 2400   | 2404                          | 0.16       | 207                         | 2404              | 0.16       | 129                         | 2400              | 0.00       | 119                         | 2400               | 0.00       | 71                          |  |

| 9600   | 9615                          | 0.16       | 51                          | 9470              | -1.36      | 32                          | 9600              | 0.00       | 29                          | 9600               | 0.00       | 17                          |  |

| 10417  | 10417                         | 0.00       | 47                          | 10417             | 0.00       | 29                          | 10286             | -1.26      | 27                          | 10165              | -2.42      | 16                          |  |

| 19.2k  | 19.23k                        | 0.16       | 25                          | 19.53k            | 1.73       | 15                          | 19.20k            | 0.00       | 14                          | 19.20k             | 0.00       | 8                           |  |

| 57.6k  | 55.55k                        | -3.55      | 3                           | —                 | _          | _                           | 57.60k            | 0.00       | 7                           | 57.60k             | 0.00       | 2                           |  |

| 115.2k | —                             | —          | —                           | _                 | —          | —                           | _                 | _          | _                           | —                  | _          | —                           |  |

#### TABLE 28-5: BAUD RATES FOR ASYNCHRONOUS MODES

|        |                  | <b>SYNC</b> = 0, <b>BRGH</b> = 0, <b>BRG16</b> = 0 |                             |                  |            |                             |                   |            |                             |                  |            |                             |  |

|--------|------------------|----------------------------------------------------|-----------------------------|------------------|------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|--|

| BAUD   | Fosc = 8.000 MHz |                                                    |                             | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 1.000 MHz |            |                             |  |

| RATE   | Actual<br>Rate   | %<br>Error                                         | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 300    |                  |                                                    | _                           | 300              | 0.16       | 207                         | 300               | 0.00       | 191                         | 300              | 0.16       | 51                          |  |

| 1200   | 1202             | 0.16                                               | 103                         | 1202             | 0.16       | 51                          | 1200              | 0.00       | 47                          | 1202             | 0.16       | 12                          |  |

| 2400   | 2404             | 0.16                                               | 51                          | 2404             | 0.16       | 25                          | 2400              | 0.00       | 23                          | —                | _          | _                           |  |

| 9600   | 9615             | 0.16                                               | 12                          | _                | _          | _                           | 9600              | 0.00       | 5                           | _                | _          | _                           |  |

| 10417  | 10417            | 0.00                                               | 11                          | 10417            | 0.00       | 5                           | _                 | _          | _                           | _                | _          | _                           |  |

| 19.2k  | _                | _                                                  | _                           | _                | _          | _                           | 19.20k            | 0.00       | 2                           | _                | _          | _                           |  |

| 57.6k  | —                | —                                                  | —                           | —                | _          | —                           | 57.60k            | 0.00       | 0                           | —                | _          | —                           |  |

| 115.2k | —                | _                                                  | _                           | —                | _          | _                           | _                 | _          | —                           | —                | _          | —                           |  |

|        | SYNC = 0, BRGH = 1, BRG16 = 0 |                   |                             |                |                   |                             |                |                   |                             |                |                    |                             |  |

|--------|-------------------------------|-------------------|-----------------------------|----------------|-------------------|-----------------------------|----------------|-------------------|-----------------------------|----------------|--------------------|-----------------------------|--|

| BAUD   | Fosc                          | Fosc = 32.000 MHz |                             |                | Fosc = 20.000 MHz |                             |                | Fosc = 18.432 MHz |                             |                | Fosc = 11.0592 MHz |                             |  |

| RATE   | -                             | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error         | SPBRG<br>value<br>(decimal) |  |

| 300    | —                             | _                 | _                           |                | _                 | _                           | _              | _                 | _                           |                | _                  | _                           |  |

| 1200   | —                             | —                 | —                           | —              |                   | —                           | —              | —                 | —                           | —              | —                  | —                           |  |

| 2400   |                               | _                 | _                           | _              | _                 | _                           | _              | _                 | _                           | _              | _                  | _                           |  |

| 9600   | 9615                          | 0.16              | 207                         | 9615           | 0.16              | 129                         | 9600           | 0.00              | 119                         | 9600           | 0.00               | 71                          |  |

| 10417  | 10417                         | 0.00              | 191                         | 10417          | 0.00              | 119                         | 10378          | -0.37             | 110                         | 10473          | 0.53               | 65                          |  |

| 19.2k  | 19.23k                        | 0.16              | 103                         | 19.23k         | 0.16              | 64                          | 19.20k         | 0.00              | 59                          | 19.20k         | 0.00               | 35                          |  |

| 57.6k  | 57.14k                        | -0.79             | 34                          | 56.82k         | -1.36             | 21                          | 57.60k         | 0.00              | 19                          | 57.60k         | 0.00               | 11                          |  |

| 115.2k | 117.64k                       | 2.12              | 16                          | 113.64k        | -1.36             | 10                          | 115.2k         | 0.00              | 9                           | 115.2k         | 0.00               | 5                           |  |

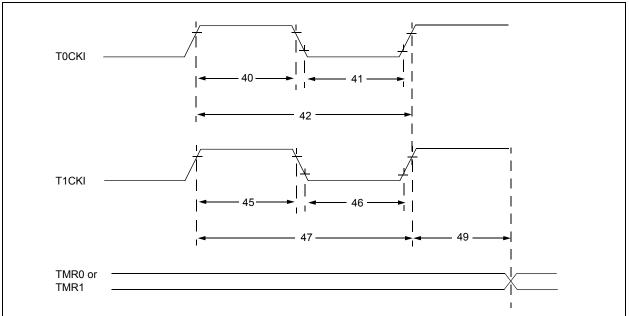

#### FIGURE 31-10: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

| TABLE 31-11: | TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS |

|--------------|-----------------------------------------------|

|--------------|-----------------------------------------------|

| Standa       | rd Operating | Conditions (u                                                                          | Inless otherwis                | e stated)                                 |                                           |        |        |                                    |                                    |

|--------------|--------------|----------------------------------------------------------------------------------------|--------------------------------|-------------------------------------------|-------------------------------------------|--------|--------|------------------------------------|------------------------------------|

| Param<br>No. | Sym.         | Characteristic                                                                         |                                |                                           | Min.                                      | Тур†   | Max.   | Units                              | Conditions                         |

| 40*          | TT0H         | T0CKI High I                                                                           | Pulse Width                    | No Prescaler                              | 0.5 Tcy + 20                              | _      |        | ns                                 |                                    |