#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                                |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x12b; D/A 1x8b, 3x5b                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1788-e-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| IAD  |                             |             | zo-FIN ALLOCATION TABLE (FICTO(L)F1766) (Continued)                                                 |           |            |                         |                     |        |        |      |          |      |           |         |             |

|------|-----------------------------|-------------|-----------------------------------------------------------------------------------------------------|-----------|------------|-------------------------|---------------------|--------|--------|------|----------|------|-----------|---------|-------------|

| 0/1  | 28-Pin SPDIP,<br>SOIC, SSOP | 28-Pin QFN, | ADC                                                                                                 | Reference | Comparator | Operation<br>Amplifiers | 8-bit/<br>5-bit DAC | Timers | PSMC   | ссь  | EUSART   | dSSM | Interrupt | Pull-up | Basic       |

| RC6  | 17                          | 14          | -                                                                                                   | _         | —          | _                       | _                   | -      | PSMC2A | CCP3 | TX<br>CK |      | IOC       | Y       | _           |

| RC7  | 18                          | 15          | Ι                                                                                                   | _         | C4OUT      | Ι                       | _                   | -      | PSMC2B | -    | RX<br>DT |      | IOC       | Y       |             |

| RE3  | 1                           | 26          | Ι                                                                                                   | —         | -          |                         | —                   |        | —      |      | -        |      | IOC       | Y       | MCLR<br>VPP |

| VDD  | 20                          | 17          |                                                                                                     | _         | —          | _                       | —                   | —      | _      | —    | _        | —    |           | —       | Vdd         |

| Vss  | 8,<br>19                    | 5,<br>16    | —                                                                                                   | _         | _          | —                       | _                   | _      | _      | _    | -        |      | —         | —       | Vss         |

| Mate | 4.                          |             | Alternate sin function extend with the ADECONIA (Desider 42.4) and ADECONIA (Desider 42.0) resident |           |            |                         |                     |        |        |      |          |      |           |         |             |

### TABLE 1: 28-PIN ALLOCATION TABLE (PIC16(L)F1788) (Continued)

Note 1: Alternate pin function selected with the APFCON1 (Register 13-1) and APFCON2 (Register 13-2) registers.

| IADI             | LE 3-12:               | SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) |                              |                  |                 |       |                      |                      | 1                    |                      |                                 |

|------------------|------------------------|-----------------------------------------------|------------------------------|------------------|-----------------|-------|----------------------|----------------------|----------------------|----------------------|---------------------------------|

| Addr             | Name                   | Bit 7                                         | Bit 6                        | Bit 5            | Bit 4           | Bit 3 | Bit 2                | Bit 1                | Bit 0                | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

| Ban              | k 4                    |                                               |                              |                  |                 |       |                      |                      |                      |                      |                                 |

| 20Ch             | WPUA                   | WPUA7                                         | WPUA6                        | WPUA5            | WPUA4           | WPUA3 | WPUA2                | WPUA1                | WPUA0                | 1111 1111            | 1111 1111                       |

| 20Dh             | WPUB                   | WPUB7                                         | WPUB6                        | WPUB5            | WPUB4           | WPUB3 | WPUB2                | WPUB1                | WPUB0                | 1111 1111            | 1111 1111                       |

| 20Eh             | WPUC                   | WPUC7                                         | WPUC6                        | WPUC5            | WPUC4           | WPUC3 | WPUC2                | WPUC1                | WPUC0                | 1111 1111            | 1111 1111                       |

| 20Fh             | WPUD <sup>(3)</sup>    | WPUD7                                         | WPUD6                        | WPUD5            | WPUD4           | WPUD3 | WPUD2                | WPUD1                | WPUD0                | 1111 1111            | 1111 1111                       |

| 210h             | WPUE                   | —                                             | —                            | -                | -               | WPUE3 | WPUE2 <sup>(3)</sup> | WPUE1 <sup>(3)</sup> | WPUE0 <sup>(3)</sup> | 1111                 | 1111                            |

| 211h             | SSP1BUF                | Synchronous                                   | Serial Port Re               | ceive Buffer/Tra | ansmit Register |       |                      |                      |                      | XXXX XXXX            | uuuu uuuu                       |

| 212h             | SSP1ADD                |                                               |                              |                  | ADD<            | 7:0>  |                      |                      |                      | 0000 0000            | 0000 0000                       |

| 213h             | SSP1MSK                |                                               |                              |                  | MSK<            | 7:0>  |                      |                      |                      | 1111 1111            | 1111 1111                       |

| 214h             | SSP1STAT               | SMP                                           | CKE                          | D/A              | Р               | S     | R/W                  | UA                   | BF                   | 0000 0000            | 0000 0000                       |

| 215h             | SSP1CON1               | WCOL                                          | SSPOV                        | SSPEN            | СКР             |       | SSPN                 | 1<3:0>               |                      | 0000 0000            | 0000 0000                       |

| 216h             | SSP1CON2               | GCEN                                          | ACKSTAT                      | ACKDT            | ACKEN           | RCEN  | PEN                  | RSEN                 | SEN                  | 0000 0000            | 0000 0000                       |

| 217h             | SSP1CON3               | ACKTIM                                        | PCIE                         | SCIE             | BOEN            | SDAHT | SBCDE                | AHEN                 | DHEN                 | 0000 0000            | 0000 0000                       |

| 218h             |                        |                                               |                              | •                | •               |       | •                    |                      | •                    |                      |                                 |

| <br>21Fh         | -                      | Unimplemente                                  | d                            |                  |                 |       |                      |                      |                      | —                    | _                               |

| Ban              | k 5                    |                                               |                              |                  |                 |       |                      |                      |                      |                      |                                 |

| 28Ch             | ODCONA                 | Open-Drain Co                                 | Open-Drain Control for PORTA |                  |                 |       |                      |                      |                      |                      | 0000 0000                       |

| 28Dh             | ODCONB                 | Open-Drain Control for PORTB                  |                              |                  |                 |       |                      |                      |                      | 0000 0000            | 0000 0000                       |

| 28Eh             | ODCONC                 | Open-Drain Control for PORTC                  |                              |                  |                 |       |                      |                      |                      | 0000 0000            | 0000 0000                       |

| 28Fh             | ODCOND <sup>(3)</sup>  | Open-Drain Control for PORTD                  |                              |                  |                 |       |                      |                      |                      | 0000 0000            | 0000 0000                       |

| 290h             | ODCONE <sup>(3)</sup>  | —                                             | —                            | —                | —               | —     | ODE2                 | ODE1                 | ODE0                 | 000                  | uuu                             |

| 291h             | CCPR1L                 | Capture/Comp                                  | oare/PWM Re                  | gister 1 (LSB)   |                 |       |                      |                      |                      | xxxx xxxx            | uuuu uuuu                       |

| 292h             | CCPR1H                 | Capture/Comp                                  | oare/PWM Re                  | gister 1 (MSB)   |                 |       |                      |                      |                      | xxxx xxxx            | uuuu uuuu                       |

| 293h             | CCP1CON                | —                                             | —                            | DC1E             | 8<1:0>          |       | CCP1I                | V<3:0>               |                      | 00 0000              | 00 0000                         |

| 294h             |                        | Unimplemente                                  | ad                           |                  |                 |       |                      |                      |                      | _                    | _                               |

| 297h             |                        | ommpiemente                                   | ,u                           |                  |                 |       |                      |                      |                      |                      |                                 |

| 298h             | CCPR2L                 | Capture/Comp                                  | oare/PWM Re                  | gister 2 (LSB)   |                 |       |                      |                      |                      | xxxx xxxx            | uuuu uuuu                       |

| 299h             | CCPR2H                 | Capture/Comp                                  | oare/PWM Re                  | gister 2 (MSB)   |                 |       |                      |                      |                      | xxxx xxxx            | uuuu uuuu                       |

| 29Ah             | CCP2CON                | —                                             | —                            | DC2E             | 8<1:0>          |       | CCP2I                | V<3:0>               |                      | 00 0000              | 00 0000                         |

| 29Bh<br><br>29Fh | _                      | Unimplemente                                  | ed                           |                  |                 |       |                      |                      |                      | -                    | -                               |

| Ban              | k 6                    |                                               |                              |                  |                 |       |                      |                      |                      |                      |                                 |

| 30Ch             | SLRCONA                | Slew Rate Cor                                 | ntrol for PORT               | Ā                |                 |       |                      |                      |                      | 0000 0000            | 0000 0000                       |

| 30Dh             | SLRCONB                | Slew Rate Control for PORTB                   |                              |                  |                 |       |                      |                      |                      | 0000 0000            | 0000 0000                       |

| 30Eh             | SLRCONC                | Slew Rate Control for PORTC                   |                              |                  |                 |       |                      |                      | 1                    | 0000 0000            |                                 |

| 30Fh             | SLRCOND(3)             | Slew Rate Cor                                 | ntrol for PORT               | D                |                 |       |                      |                      |                      | 0000 0000            | 0000 0000                       |

| 310h             | SLRCONE <sup>(3)</sup> | —                                             | —                            | —                | —               | —     | SLRE2                | SLRE1                | SLRE0                | 111                  | 111                             |

| 311h             | CCPR3L                 | Capture/Comp                                  | are/PWM Re                   | gister 3 (LSB)   |                 |       |                      |                      |                      | xxxx xxxx            | uuuu uuuu                       |

| 312h             | CCPR3H                 | Capture/Comp                                  | are/PWM Re                   | gister 3 (MSB)   |                 |       |                      |                      |                      | xxxx xxxx            | uuuu uuuu                       |

| 313h             | CCP3CON                | —                                             | —                            | DC3B             | 8<1:0>          |       | CCP3I                | M<3:0>               |                      | 00 0000              | 00 0000                         |

| 314h<br><br>31Fh | _                      | Unimplemented                                 |                              |                  |                 |       |                      |                      | -                    | _                    |                                 |

x = unknown, u = unchanged, g = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. These registers can be addressed from any bank. Unimplemented, read as '1'. PIC16(L)F1789 only. Legend:

Note

1: 2:

3:

PIC16F1788/9 only. 4:

#### SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) TABLE 3-12

| IABI             | LE 3-12: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) |                |                                            |          |          |          |          |             |         |                      |                                 |

|------------------|--------------------------------------------------------|----------------|--------------------------------------------|----------|----------|----------|----------|-------------|---------|----------------------|---------------------------------|

| Addr             | Name                                                   | Bit 7          | Bit 6                                      | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1       | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

| Ban              | Bank 30                                                |                |                                            |          |          |          |          |             |         |                      |                                 |

| F0Ch<br><br>F10h | _                                                      | Unimplemented  |                                            |          |          |          |          |             |         | _                    |                                 |

| F11h             | PSMC4CON                                               | PSMC4EN        | PSMC4LD                                    | P4DBFE   | P4DBRE   |          | P4MOE    | )E<3:0>     |         | 0000 0000            | 0000 0000                       |

| F12h             | PSMC4MDL                                               | P4MDLEN        | P4MDLPOL                                   | P4MDLBIT | _        |          | P4MSR    | RC<3:0>     |         | 000- 0000            | 000- 0000                       |

| F13h             | PSMC4SYNC                                              | P4POFST        | P4PRPOL                                    | P4DCPOL  | _        | _        |          | P4SYNC<2:0> | >       | 000000               | 000000                          |

| F14h             | PSMC4CLK                                               | _              | _                                          | P4CPF    | RE<1:0>  | _        | —        | P4CSR       | RC<1:0> | 0000                 | 0000                            |

| F15h             | PSMC4OEN                                               | _              | _                                          | _        | —        | _        | —        | P4OEB       | P40EA   | 00                   | 00                              |

| F16h             | PSMC4POL                                               | _              | P4INPOL                                    | _        | —        | —        | —        | P4POLB      | P4POLA  | -000                 | -000                            |

| F17h             | PSMC4BLNK                                              | _              | _                                          | P4FEB    | M<1:0>   | —        | —        | P4REB       | M<1:0>  | 0000                 | 0000                            |

| F18h             | PSMC4REBS                                              | P4REBSIN       | —                                          | _        | P4REBSC4 | P4REBSC3 | P4REBSC2 | P4REBSC1    | _       | 00 000-              | 00 000-                         |

| F19h             | PSMC4FEBS                                              | P4FEBSIN       | —                                          | _        | P4FEBSC4 | P4FEBSC3 | P4FEBSC2 | P4FEBSC1    | _       | 00 000-              | 00 000-                         |

| F1Ah             | PSMC4PHS                                               | P4PHSIN        | _                                          | _        | P4PHSC4  | P4PHSC3  | P4PHSC2  | P4PHSC1     | P4PHST  | 00 0000              | 00 0000                         |

| F1Bh             | PSMC4DCS                                               | P4DCSIN        | _                                          | _        | P4DCSC4  | P4DCSC3  | P4DCSC2  | P4DCSC1     | P4DCST  | 00 0000              | 00 0000                         |

| F1Ch             | PSMC4PRS                                               | P4PRSIN        | _                                          | _        | P4PRSC4  | P4PRSC3  | P4PRSC2  | P4PRSC1     | P4PRST  | 00 0000              | 00 0000                         |

| F1Dh             | PSMC4ASDC                                              | P4ASE          | P4ASDEN                                    | P4ARSEN  |          | —        | —        | —           | P4ASDOV | 0000                 | 0000                            |

| F1Eh             | PSMC4ASDL                                              | —              | —                                          | —        |          | —        | —        | P4ASDLB     | P4ASDLA | 00                   | 00                              |

| F1Fh             | PSMC4ASDS                                              | P4ASDSIN       | —                                          | —        | P4ASDSC4 | P4ASDSC3 | P4ASDSC2 | P4ASDSC1    | —       | 00 000-              | 00 000-                         |

| F20h             | PSMC4INT                                               | P4TOVIE        | P4TPHIE                                    | P4TDCIE  | P4TPRIE  | P4TOVIF  | P4TPHIF  | P4TDCIF     | P4TPRIF | 0000 0000            | 0000 0000                       |

| F21h             | PSMC4PHL                                               | Phase Low Co   | unt                                        |          |          |          |          |             |         | 0000 0000            | 0000 0000                       |

| F22h             | PSMC4PHH                                               | Phase High Co  | ount                                       |          |          |          |          |             |         | 0000 0000            | 0000 0000                       |

| F23h             | PSMC4DCL                                               | Duty Cycle Lov | w Count                                    |          |          |          |          |             |         | 0000 0000            | 0000 0000                       |

| F24h             | PSMC4DCH                                               | Duty Cycle Hig | gh Count                                   |          |          |          |          |             |         | 0000 0000            | 0000 0000                       |

| F25h             | PSMC4PRL                                               | Period Low Co  | bunt                                       |          |          |          |          |             |         | 0000 0000            | 0000 0000                       |

| F26h             | PSMC4PRH                                               | Period High Co | ount                                       |          |          |          |          |             |         | 0000 0000            | 0000 0000                       |

| F27h             | PSMC4TMRL                                              | Time base Low  | v Counter                                  |          |          |          |          |             |         | 0000 0001            | 0000 0001                       |

| F28h             | PSMC4TMRH                                              | Time base Hig  | Fime base High Counter                     |          |          |          |          |             |         |                      | 0000 0000                       |

| F29h             | PSMC4DBR                                               | Rising Edge D  | Rising Edge Dead-band Counter              |          |          |          |          |             |         |                      | 0000 0000                       |

| F2Ah             | PSMC4DBF                                               | Falling Edge D | Falling Edge Dead-band Counter             |          |          |          |          |             |         |                      | 0000 0000                       |

| F2Bh             | PSMC4BLKR                                              | Rising Edge B  | Rising Edge Blanking Counter               |          |          |          |          |             |         |                      | 0000 0000                       |

| F2Ch             | PSMC4BLKF                                              | Falling Edge B | Falling Edge Blanking Counter 0000 000 000 |          |          |          |          |             |         |                      | 0000 0000                       |

| F2Dh             | PSMC4FFA                                               | _              | — — — Fractional Frequency Adjust Register |          |          |          |          |             |         |                      | 0000                            |

| F2Eh             | PSMC4STR0                                              | _              | _                                          | _        | _        | —        | —        | P4STRB      | P4STRA  | 01                   | 01                              |

| F2Fh             | PSMC4STR1                                              | P4SSYNC        | _                                          | _        | _        |          | _        | P4LSMEN     | P4HSMEN | 000                  | 000                             |

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. Legend:

Note 1: These registers can be addressed from any bank.

Unimplemented, read as '1'. 2:

3: PIC16(L)F1789 only.

PIC16F1788/9 only. 4:

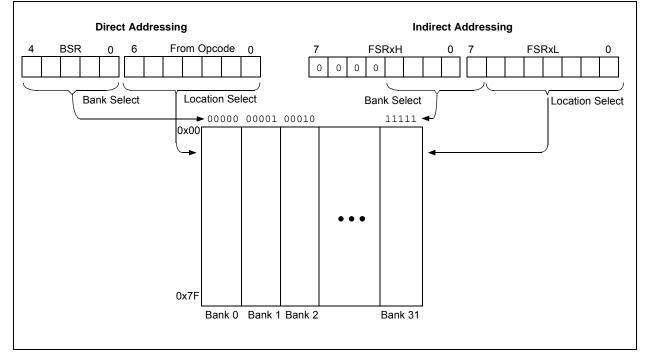

### 3.6.1 TRADITIONAL DATA MEMORY

The traditional data memory is a region from FSR address 0x000 to FSR address 0xFFF. The addresses correspond to the absolute addresses of all SFR, GPR and common registers.

### 4.0 DEVICE CONFIGURATION

Device configuration consists of Configuration Words, Code Protection and Device ID.

### 4.1 Configuration Words

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as Configuration Word 1 at 8007h and Configuration Word 2 at 8008h.

Note: The DEBUG bit in Configuration Words is managed automatically by device development tools including debuggers and programmers. For normal device operation, this bit should be maintained as a '1'.

| W-0/0              | W-0/0  | W-0/0              | W-0/0     | W-0/0            | W-0/0            | W-0/0            | W-0/0       |

|--------------------|--------|--------------------|-----------|------------------|------------------|------------------|-------------|

|                    |        |                    | EEPROM Co | ntrol Register 2 |                  |                  |             |

| bit 7              |        |                    |           |                  |                  |                  | bit 0       |

|                    |        |                    |           |                  |                  |                  |             |

| Legend:            |        |                    |           |                  |                  |                  |             |

| R = Readable bit   |        | W = Writable       | bit       | U = Unimplen     | nented bit, read | as '0'           |             |

| S = Bit can only b | be set | x = Bit is unknown |           | -n/n = Value a   | t POR and BO     | R/Value at all o | ther Resets |

| '1' = Bit is set   |        | '0' = Bit is cle   | ared      |                  |                  |                  |             |

### REGISTER 12-6: EECON2: EEPROM CONTROL 2 REGISTER

### bit 7-0 Data EEPROM Unlock Pattern bits

To unlock writes, a 55h must be written first, followed by an AAh, before setting the WR bit of the EECON1 register. The value written to this register is used to unlock the writes. There are specific timing requirements on these writes. Refer to **Section 12.2.2** "Writing to the Data EEPROM Memory" for more information.

### TABLE 12-3: SUMMARY OF REGISTERS ASSOCIATED WITH DATA EEPROM

| Name   | Bit 7                                                 | Bit 6 | Bit 5  | Bit 4 | Bit 3  | Bit 2  | Bit 1 | Bit 0  | Register on<br>Page |

|--------|-------------------------------------------------------|-------|--------|-------|--------|--------|-------|--------|---------------------|

| EECON1 | EEPGD                                                 | CFGS  | LWLO   | FREE  | WRERR  | WREN   | WR    | RD     | 128                 |

| EECON2 | 2 EEPROM Control Register 2 (not a physical register) |       |        |       |        |        |       |        | 129*                |

| EEADRL | EEADRL<7:0>                                           |       |        |       |        |        |       |        | 127                 |

| EEADRH | (1) EEADRH<6:0>                                       |       |        |       |        |        |       |        | 127                 |

| EEDATL |                                                       |       |        | EEDAT | L<7:0> |        |       |        | 127                 |

| EEDATH | —                                                     | _     |        |       | EEDAT  | H<5:0> |       |        | 127                 |

| INTCON | GIE                                                   | PEIE  | TMR0IE | INTE  | IOCIE  | TMR0IF | INTF  | IOCIF  | 97                  |

| PIE2   | OSFIE                                                 | C2IE  | C1IE   | EEIE  | BCL1IE | C4IE   | C3IE  | CCP2IE | 99                  |

| PIR2   | OSFIF                                                 | C2IF  | C1IF   | EEIF  | BCL1IF | C4IF   | C3IF  | CCP2IF | 103                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by data EEPROM module.

\* Page provides register information.

2: Unimplemented, read as '1'.

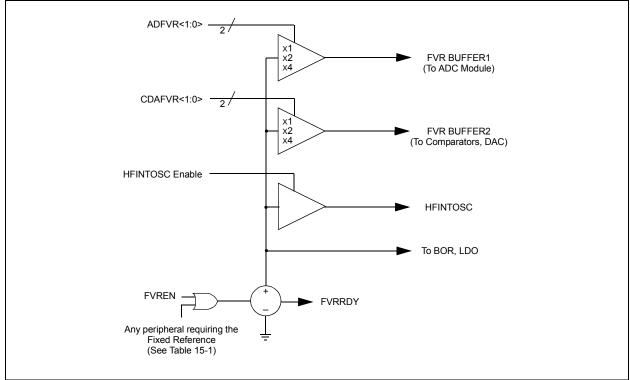

### TABLE 15-1: PERIPHERALS REQUIRING THE FIXED VOLTAGE REFERENCE (FVR)

| Peripheral  | Conditions                                                    | Description                                                  |

|-------------|---------------------------------------------------------------|--------------------------------------------------------------|

| HFINTOSC    | FOSC<2:0> = 100 and<br>IRCF<3:0> ≠ 000x                       | INTOSC is active and device is not in Sleep                  |

|             | BOREN<1:0> = 11                                               | BOR always enabled                                           |

| BOR         | BOREN<1:0> = 10 and BORFS = 1                                 | BOR disabled in Sleep mode, BOR Fast Start enabled.          |

|             | BOREN<1:0> = 01 and BORFS = 1                                 | BOR under software control, BOR Fast Start enabled           |

| LDO         | All PIC16F1788/9 devices, when<br>VREGPM = 1 and not in Sleep | The device runs off of the ULP regulator when in Sleep mode. |

| PSMC 64 MHz | PxSRC<1:0>                                                    | 64 MHz clock forces HFINTOSC on during Sleep.                |

### 22.1.3 SOFTWARE PROGRAMMABLE PRESCALER

A software programmable prescaler is available for exclusive use with Timer0. The prescaler is enabled by clearing the PSA bit of the OPTION\_REG register.

| Note: | The Watchdog Timer (WDT) uses its own |

|-------|---------------------------------------|

|       | independent prescaler.                |

There are eight prescaler options for the Timer0 module ranging from 1:2 to 1:256. The prescale values are selectable via the PS<2:0> bits of the OPTION\_REG register. In order to have a 1:1 prescaler value for the Timer0 module, the prescaler must be disabled by setting the PSA bit of the OPTION\_REG register.

The prescaler is not readable or writable. All instructions writing to the TMR0 register will clear the prescaler.

### 22.1.4 TIMER0 INTERRUPT

Timer0 will generate an interrupt when the TMR0 register overflows from FFh to 00h. The TMR0IF interrupt flag bit of the INTCON register is set every time the TMR0 register overflows, regardless of whether or not the Timer0 interrupt is enabled. The TMR0IF bit can only be cleared in software. The Timer0 interrupt enable is the TMR0IE bit of the INTCON register.

| Note: | The Timer0 interrupt cannot wake the    |

|-------|-----------------------------------------|

|       | processor from Sleep since the timer is |

|       | frozen during Sleep.                    |

### 22.1.5 8-BIT COUNTER MODE SYNCHRONIZATION

When in 8-Bit Counter mode, the incrementing edge on the T0CKI pin must be synchronized to the instruction clock. Synchronization can be accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the instruction clock. The high and low periods of the external clocking source must meet the timing requirements as shown in **Section 31.0 "Electrical Specifications"**.

### 22.1.6 OPERATION DURING SLEEP

Timer0 cannot operate while the processor is in Sleep mode. The contents of the TMR0 register will remain unchanged while the processor is in Sleep mode.

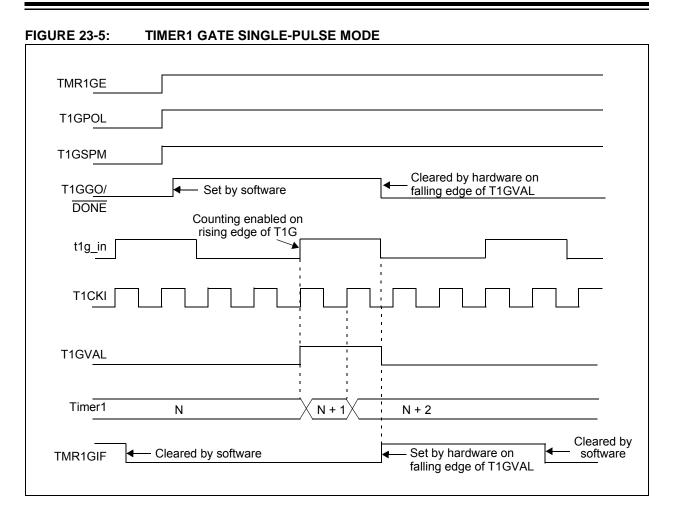

### 23.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1 is enabled by configuring the TMR1ON and TMR1GE bits in the T1CON and T1GCON registers, respectively. Table 23-1 displays the Timer1 enable selections.

| TABLE 23-1: | TIMER1 ENABLE |

|-------------|---------------|

|             | SELECTIONS    |

| TMR10N | TMR1GE | Timer1<br>Operation |

|--------|--------|---------------------|

| 0      | 0      | Off                 |

| 0      | 1      | Off                 |

| 1      | 0      | Always On           |

| 1      | 1      | Count Enabled       |

### 23.2 Clock Source Selection

The TMR1CS<1:0> and T1OSCEN bits of the T1CON register are used to select the clock source for Timer1. Table 23-2 displays the clock source selections.

### 23.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected, the TMR1H:TMR1L register pair will increment on multiples of Fosc as determined by the Timer1 prescaler.

When the Fosc internal clock source is selected, the Timer1 register value will increment by four counts every instruction clock cycle. Due to this condition, a 2 LSB error in resolution will occur when reading the Timer1 value. To utilize the full resolution of Timer1, an asynchronous input signal must be used to gate the Timer1 clock input.

The following asynchronous sources may be used:

- Asynchronous event on the T1G pin to Timer1 gate

- C1 or C2 comparator input to Timer1 gate

### 23.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When enabled to count, Timer1 is incremented on the rising edge of the external clock input T1CKI, which can be synchronized to the microcontroller system clock or can run asynchronously.

When used as a timer with a clock oscillator, an external 32.768 kHz crystal can be used in conjunction with the dedicated internal oscillator circuit.

**Note:** In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge after any one or more of the following conditions:

- Timer1 enabled after POR

- Write to TMR1H or TMR1L

- · Timer1 is disabled

- Timer1 is disabled (TMR1ON = 0) when T1CKI is high then Timer1 is enabled (TMR1ON=1) when T1CKI is low.

| TMR1CS<1:0> | T1OSCEN | Clock Source                   |

|-------------|---------|--------------------------------|

| 11          | х       | Reserved                       |

| 10          | 1       | Timer1 Oscillator              |

| 10          | 0       | External Clocking on T1CKI Pin |

| 01          | х       | System Clock (Fosc)            |

| 00          | x       | Instruction Clock (Fosc/4)     |

### TABLE 23-2: CLOCK SOURCE SELECTIONS

### 24.1 Timer2 Operation

The clock input to the Timer2 modules is the system instruction clock (Fosc/4).

A 4-bit counter/prescaler on the clock input allows direct input, divide-by-4 and divide-by-16 prescale options. These options are selected by the prescaler control bits, T2CKPS<1:0> of the T2CON register. The value of TMR2 is compared to that of the Period register, PR2, on each clock cycle. When the two values match, the comparator generates a match signal as the timer output. This signal also resets the value of TMR2 to 00h on the next cycle and drives the output counter/postscaler (see Section 24.2 "Timer2 Interrupt").

The TMR2 and PR2 registers are both directly readable and writable. The TMR2 register is cleared on any device Reset, whereas the PR2 register initializes to FFh. Both the prescaler and postscaler counters are cleared on the following events:

- · a write to the TMR2 register

- · a write to the T2CON register

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- MCLR Reset

- Watchdog Timer (WDT) Reset

- · Stack Overflow Reset

- Stack Underflow Reset

- RESET Instruction

| Note: | TMR2     | is | not | cleared | when | T2CON | is |

|-------|----------|----|-----|---------|------|-------|----|

|       | written. |    |     |         |      |       |    |

### 24.2 Timer2 Interrupt

Timer2 can also generate an optional device interrupt. The Timer2 output signal (TMR2-to-PR2 match) provides the input for the 4-bit counter/postscaler. This counter generates the TMR2 match interrupt flag which is latched in TMR2IF of the PIR1 register. The interrupt is enabled by setting the TMR2 Match Interrupt Enable bit, TMR2IE, of the PIE1 register.

A range of 16 postscale options (from 1:1 through 1:16 inclusive) can be selected with the postscaler control bits, T2OUTPS<3:0>, of the T2CON register.

### 24.3 Timer2 Output

The unscaled output of TMR2 is available primarily to the CCP modules, where it is used as a time base for operations in PWM mode.

Timer2 can be optionally used as the shift clock source for the MSSP module operating in SPI mode. Additional information is provided in Section 27.0 "Master Synchronous Serial Port (MSSP) Module"

### 24.4 Timer2 Operation During Sleep

The Timer2 timers cannot be operated while the processor is in Sleep mode. The contents of the TMR2 and PR2 registers will remain unchanged while the processor is in Sleep mode.

| Name    | Bit 7      | Bit 6                             | Bit 5        | Bit 4      | Bit 3  | Bit 2      | Bit 1  | Bit 0  | Register<br>on Page |  |  |

|---------|------------|-----------------------------------|--------------|------------|--------|------------|--------|--------|---------------------|--|--|

| CCP2CON | —          | _                                 | DC2B         | <1:0>      |        | CCP2M<3:0> |        |        |                     |  |  |

| INTCON  | GIE        | PEIE                              | TMR0IE       | INTE       | IOCIE  | TMR0IF     | INTF   | IOCIF  | 97                  |  |  |

| PIE1    | TMR1GIE    | ADIE                              | RCIE         | TXIE       | SSP1IE | CCP1IE     | TMR2IE | TMR1IE | 98                  |  |  |

| PIR1    | TMR1GIF    | ADIF                              | RCIF         | TXIF       | SSP1IF | CCP1IF     | TMR2IF | TMR1IF | 102                 |  |  |

| PR2     | Timer2 Mo  | dule Period                       | Register     |            |        |            |        |        | 220*                |  |  |

| T2CON   | _          | - T2OUTPS<3:0> TMR2ON T2CKPS<1:0> |              |            |        |            |        |        |                     |  |  |

| TMR2    | Holding Re | gister for the                    | e 8-bit TMR2 | 2 Register |        |            |        |        | 220*                |  |  |

### TABLE 24-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER2

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for Timer2 module.

\* Page provides register information.

### 27.6.10 SLEEP OPERATION

While in Sleep mode, the I<sup>2</sup>C slave module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

### 27.6.11 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

### 27.6.12 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit of the SSPSTAT register is set, or the bus is Idle, with both the S and P bits clear. When the bus is busy, enabling the SSP interrupt will generate the interrupt when the Stop condition occurs.

In multi-master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed by hardware with the result placed in the BCL1IF bit.

The states where arbitration can be lost are:

- Address Transfer

- Data Transfer

- A Start Condition

- A Repeated Start Condition

- An Acknowledge Condition

### 27.6.13 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

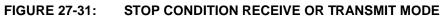

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA, by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin is '0', then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCL1IF and reset the I<sup>2</sup>C port to its Idle state (Figure 27-31).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are deasserted and the SSPBUF can be written to. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are deasserted and the respective control bits in the SSPCON2 register are cleared. When the user services the bus collision Interrupt Service Routine and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDA and SCL pins. If a Stop condition occurs, the SSP1IF bit will be set.

A write to the SSPBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPSTAT register, or the bus is Idle and the S and P bits are cleared.

|        |                   | SYNC = 0, BRGH = 0, BRG16 = 0 |                             |                   |            |                             |                   |            |                             |                    |            |                             |  |  |  |

|--------|-------------------|-------------------------------|-----------------------------|-------------------|------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|------------|-----------------------------|--|--|--|

| BAUD   | Fosc = 32.000 MHz |                               |                             | Fosc = 20.000 MHz |            |                             | Fosc = 18.432 MHz |            |                             | Fosc = 11.0592 MHz |            |                             |  |  |  |

| DATE   | Actual<br>Rate    | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |

| 300    | _                 |                               | _                           |                   |            | _                           | _                 | _          | _                           |                    | _          | _                           |  |  |  |

| 1200   | —                 | _                             | _                           | 1221              | 1.73       | 255                         | 1200              | 0.00       | 239                         | 1200               | 0.00       | 143                         |  |  |  |

| 2400   | 2404              | 0.16                          | 207                         | 2404              | 0.16       | 129                         | 2400              | 0.00       | 119                         | 2400               | 0.00       | 71                          |  |  |  |

| 9600   | 9615              | 0.16                          | 51                          | 9470              | -1.36      | 32                          | 9600              | 0.00       | 29                          | 9600               | 0.00       | 17                          |  |  |  |

| 10417  | 10417             | 0.00                          | 47                          | 10417             | 0.00       | 29                          | 10286             | -1.26      | 27                          | 10165              | -2.42      | 16                          |  |  |  |

| 19.2k  | 19.23k            | 0.16                          | 25                          | 19.53k            | 1.73       | 15                          | 19.20k            | 0.00       | 14                          | 19.20k             | 0.00       | 8                           |  |  |  |

| 57.6k  | 55.55k            | -3.55                         | 3                           | —                 | _          | _                           | 57.60k            | 0.00       | 7                           | 57.60k             | 0.00       | 2                           |  |  |  |

| 115.2k | —                 | —                             | —                           | _                 | —          | —                           | _                 | _          | _                           | —                  | _          | —                           |  |  |  |

### TABLE 28-5: BAUD RATES FOR ASYNCHRONOUS MODES

|           |                  | SYNC = 0, BRGH = 0, BRG16 = 0 |                             |                |                  |                             |                |                   |                             |                |                  |                             |  |

|-----------|------------------|-------------------------------|-----------------------------|----------------|------------------|-----------------------------|----------------|-------------------|-----------------------------|----------------|------------------|-----------------------------|--|

| BAUD      | Fosc = 8.000 MHz |                               |                             | Fos            | Fosc = 4.000 MHz |                             |                | Fosc = 3.6864 MHz |                             |                | Fosc = 1.000 MHz |                             |  |

| RATE Actu | Actual<br>Rate   | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) |  |

| 300       |                  |                               | _                           | 300            | 0.16             | 207                         | 300            | 0.00              | 191                         | 300            | 0.16             | 51                          |  |

| 1200      | 1202             | 0.16                          | 103                         | 1202           | 0.16             | 51                          | 1200           | 0.00              | 47                          | 1202           | 0.16             | 12                          |  |

| 2400      | 2404             | 0.16                          | 51                          | 2404           | 0.16             | 25                          | 2400           | 0.00              | 23                          | _              | _                | _                           |  |

| 9600      | 9615             | 0.16                          | 12                          | _              | _                | _                           | 9600           | 0.00              | 5                           | _              | _                | _                           |  |

| 10417     | 10417            | 0.00                          | 11                          | 10417          | 0.00             | 5                           | _              | _                 | _                           | _              | _                | _                           |  |

| 19.2k     | _                | _                             | _                           | _              | _                | _                           | 19.20k         | 0.00              | 2                           | _              | _                | _                           |  |

| 57.6k     | —                | _                             | —                           | —              | _                | —                           | 57.60k         | 0.00              | 0                           | —              | _                | —                           |  |

| 115.2k    | —                | _                             | _                           | —              | _                | _                           | _              | _                 | —                           | —              | _                | —                           |  |

|        |                   | SYNC = 0, BRGH = 1, BRG16 = 0 |                             |                   |            |                             |                   |            |                             |                    |            |                             |  |

|--------|-------------------|-------------------------------|-----------------------------|-------------------|------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|------------|-----------------------------|--|

| BAUD   | Fosc = 32.000 MHz |                               |                             | Fosc = 20.000 MHz |            |                             | Fosc = 18.432 MHz |            |                             | Fosc = 11.0592 MHz |            |                             |  |

| RATE   | Actual<br>Rate    | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 300    | —                 | _                             | _                           |                   | _          | _                           | _                 | _          | _                           |                    | _          | —                           |  |

| 1200   | —                 | —                             | —                           | —                 |            | —                           | —                 | —          | —                           | —                  | —          | —                           |  |

| 2400   |                   | _                             | _                           | _                 | _          | _                           | _                 | _          | _                           | _                  | _          | _                           |  |

| 9600   | 9615              | 0.16                          | 207                         | 9615              | 0.16       | 129                         | 9600              | 0.00       | 119                         | 9600               | 0.00       | 71                          |  |

| 10417  | 10417             | 0.00                          | 191                         | 10417             | 0.00       | 119                         | 10378             | -0.37      | 110                         | 10473              | 0.53       | 65                          |  |

| 19.2k  | 19.23k            | 0.16                          | 103                         | 19.23k            | 0.16       | 64                          | 19.20k            | 0.00       | 59                          | 19.20k             | 0.00       | 35                          |  |

| 57.6k  | 57.14k            | -0.79                         | 34                          | 56.82k            | -1.36      | 21                          | 57.60k            | 0.00       | 19                          | 57.60k             | 0.00       | 11                          |  |

| 115.2k | 117.64k           | 2.12                          | 16                          | 113.64k           | -1.36      | 10                          | 115.2k            | 0.00       | 9                           | 115.2k             | 0.00       | 5                           |  |

### 28.5.2 SYNCHRONOUS SLAVE MODE

The following bits are used to configure the EUSART for synchronous slave operation:

- SYNC = 1

- CSRC = 0

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Clearing the CSRC bit of the TXSTA register configures the device as a slave. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the EUSART.

### 28.5.2.1 EUSART Synchronous Slave Transmit

The operation of the Synchronous Master and Slave modes are identical (see **Section 28.5.1.3 "Synchronous Master Transmission")**, except in the case of the Sleep mode. If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- 1. The first character will immediately transfer to the TSR register and transmit.

- 2. The second word will remain in TXREG register.

- 3. The TXIF bit will not be set.

- After the first character has been shifted out of TSR, the TXREG register will transfer the second character to the TSR and the TXIF bit will now be set.

- 5. If the PEIE and TXIE bits are set, the interrupt will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will call the Interrupt Service Routine.

- 28.5.2.2 Synchronous Slave Transmission Set-up:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for the CK pin (if applicable).

- 3. Clear the CREN and SREN bits.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. Enable transmission by setting the TXEN bit.

- 7. If 9-bit transmission is selected, insert the Most Significant bit into the TX9D bit.

- 8. Start transmission by writing the Least Significant eight bits to the TXREG register.

### TABLE 28-9:SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE<br/>TRANSMISSION

| Name    | Bit 7    | Bit 6                         | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0   | Register<br>on Page |  |

|---------|----------|-------------------------------|--------|--------|--------|--------|--------|---------|---------------------|--|

| APFCON1 | C2OUTSEL | CC1PSEL                       | SDOSEL | SCKSEL | SDISEL | TXSEL  | RXSEL  | CCP2SEL | 132                 |  |

| BAUDCON | ABDOVF   | RCIDL                         |        | SCKP   | BRG16  |        | WUE    | ABDEN   | 356                 |  |

| INTCON  | GIE      | PEIE                          | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF   | 97                  |  |

| PIE1    | TMR1GIE  | ADIE                          | RCIE   | TXIE   | SSP1IE | CCP1IE | TMR2IE | TMR1IE  | 98                  |  |

| PIR1    | TMR1GIF  | ADIF                          | RCIF   | TXIF   | SSP1IF | CCP1IF | TMR2IF | TMR1IF  | 102                 |  |

| RCSTA   | SPEN     | RX9                           | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D    | 355                 |  |

| TRISC   | TRISC7   | TRISC6                        | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0  | 147                 |  |

| TXREG   |          | EUSART Transmit Data Register |        |        |        |        |        |         |                     |  |

| TXSTA   | CSRC     | TX9                           | TXEN   | SYNC   | SENDB  | BRGH   | TRMT   | TX9D    | 354                 |  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for synchronous slave transmission.

Page provides register information.

### 33.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

### 33.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

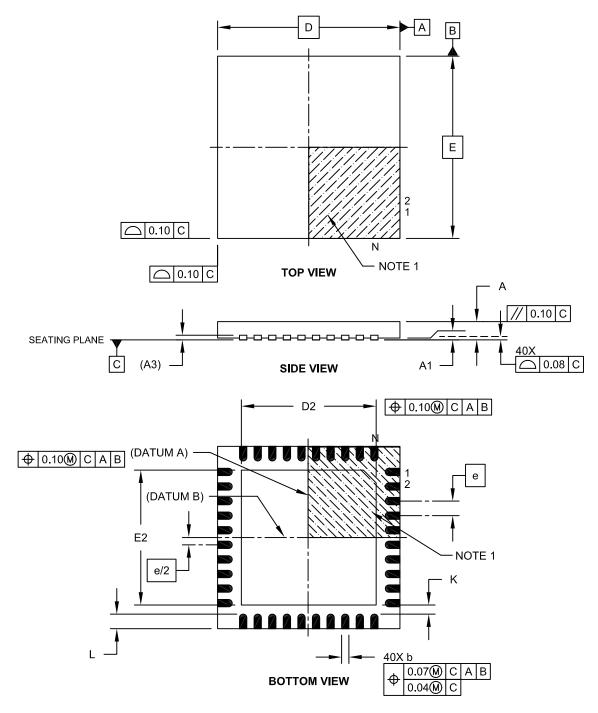

### 40-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) – 5x5x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-156A Sheet 1 of 2

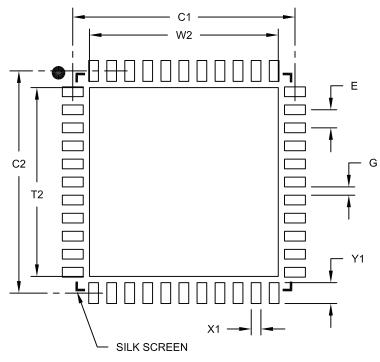

44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| RECOMMENDED | LAND PATTERN |

|-------------|--------------|

|-------------|--------------|

|                            | Units    |          |      |      |  |  |

|----------------------------|----------|----------|------|------|--|--|

| Dimensio                   | n Limits | MIN      | NOM  | MAX  |  |  |

| Contact Pitch              | E        | 0.65 BSC |      |      |  |  |

| Optional Center Pad Width  | W2       |          |      | 6.60 |  |  |

| Optional Center Pad Length | T2       |          |      | 6.60 |  |  |

| Contact Pad Spacing        | C1       |          | 8.00 |      |  |  |

| Contact Pad Spacing        | C2       |          | 8.00 |      |  |  |

| Contact Pad Width (X44)    | X1       |          |      | 0.35 |  |  |

| Contact Pad Length (X44)   | Y1       |          |      | 0.85 |  |  |

| Distance Between Pads      | G        | 0.25     |      |      |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

1

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2103B

### **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

Dallas Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

Canada - Toronto Tel: 905-673-0699 Fax: 905-673-6509

### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

China - Chengdu Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

### ASIA/PACIFIC

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7828

Taiwan - Taipei Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820