Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                                |

| Number of I/O              | 35                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 14x12b; D/A 1x8b, 3x5b                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 40-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 40-UQFN (5x5)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1789-e-mv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0 Device Overview                                                            |     |

|--------------------------------------------------------------------------------|-----|

| 2.0 Enhanced Mid-Range CPU                                                     |     |

| 3.0 Memory Organization                                                        |     |

| 4.0 Device Configuration                                                       |     |

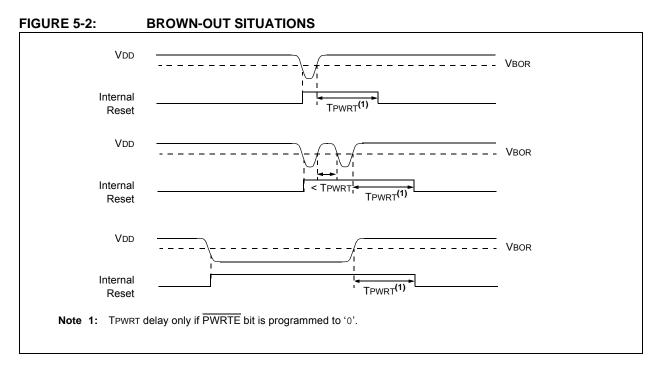

| 5.0 Resets                                                                     | 63  |

| 6.0 Oscillator Module (with Fail-Safe Clock Monitor)                           |     |

| 7.0 Reference Clock Module                                                     |     |

| 8.0 Interrupts                                                                 |     |

| 9.0 Power-Down Mode (Sleep)                                                    | 107 |

| 10.0 Low Dropout (LDO) Voltage Regulator                                       | 111 |

| 11.0 Watchdog Timer (WDT)                                                      |     |

| 12.0 Data EEPROM and Flash Program Memory Control                              | 116 |

| 13.0 I/O Ports                                                                 | 130 |

| 14.0 Interrupt-On-Change                                                       | 161 |

| 15.0 Fixed Voltage Reference (FVR)                                             | 165 |

| 16.0 Temperature Indicator Module                                              | 168 |

| 17.0 Analog-to-Digital Converter (ADC) Module                                  | 170 |

| 18.0 Operational Amplifier (OPA) Modules                                       | 185 |

| 19.0 8-Bit Digital-to-Analog Converter (DAC) Module                            |     |

| 20.0 5-bit Digital-to-Analog Converter (DAC2/3/4) Modules                      | 193 |

| 21.0 Comparator Module                                                         | 197 |

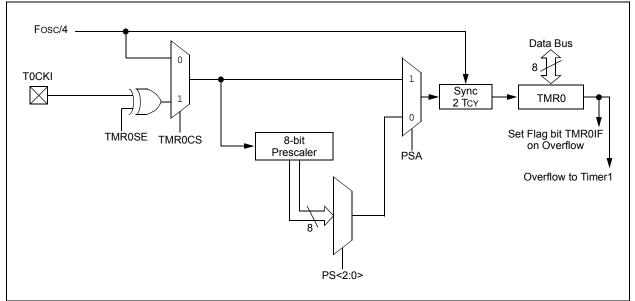

| 22.0 Timer0 Module                                                             | 206 |

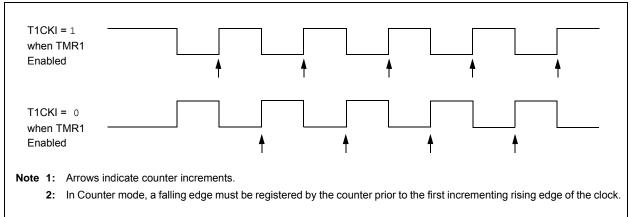

| 23.0 Timer1 Module with Gate Control                                           | 209 |

| 24.0 Timer2 Module                                                             | 220 |

| 25.0 Capture/Compare/PWM Modules                                               | 224 |

| 26.0 Programmable Switch Mode Control (PSMC)                                   | 232 |

| 27.0 Master Synchronous Serial Port (MSSP) Module                              |     |

| 28.0 Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) |     |

| 29.0 In-Circuit Serial Programming™ (ICSP™)                                    |     |

| 30.0 Instruction Set Summary                                                   |     |

| 31.0 Electrical Specifications                                                 | 389 |

| 32.0 DC and AC Characteristics Graphs and Charts                               | 422 |

| 33.0 Development Support                                                       | 446 |

| 34.0 Packaging Information                                                     | 450 |

| Appendix A: Data Sheet Revision History                                        | 470 |

| The Microchip Website                                                          | 471 |

| Customer Change Notification Service                                           | 471 |

| Customer Support                                                               |     |

| Product Identification System                                                  | 472 |

#### TABLE 1-2: PIC16(L)F1788 PINOUT DESCRIPTION (CONTINUED)

| Name                   | Function | Input<br>Type    | Output<br>Type | Description                         |

|------------------------|----------|------------------|----------------|-------------------------------------|

| RC3/PSMC1D/PSMC4A/SCK/ | RC3      | TTL/ST           | CMOS           | General purpose I/O.                |

| SCL                    | PSMC1D   | —                | CMOS           | PSMC1 output D.                     |

|                        | PSMC4A   | —                | CMOS           | PSMC4 output A.                     |

|                        | SCK      | ST               | CMOS           | SPI clock.                          |

|                        | SCL      | l <sup>2</sup> C | OD             | I <sup>2</sup> C clock.             |

| RC4/PSMC1E/PSMC4B/SDI/ | RC4      | TTL/ST           | CMOS           | General purpose I/O.                |

| SDA                    | PSMC1E   | —                | CMOS           | PSMC1 output E.                     |

|                        | PSMC4B   | _                | CMOS           | PSMC4 output B.                     |

|                        | SDI      | ST               | _              | SPI data input.                     |

|                        | SDA      | l <sup>2</sup> C | OD             | I <sup>2</sup> C data input/output. |

| RC5/PSMC1F/PSMC3A/SDO  | RC5      | TTL/ST           | CMOS           | General purpose I/O.                |

|                        | PSMC1F   | _                | CMOS           | PSMC1 output F.                     |

|                        | PSMC3A   | —                | CMOS           | PSMC3 output A.                     |

|                        | SDO      | _                | CMOS           | SPI data output.                    |

| RC6/PSMC2A/TX/CK/CCP3  | RC6      | TTL/ST           | CMOS           | General purpose I/O.                |

|                        | PSMC2A   | —                | CMOS           | PSMC2 output A.                     |

|                        | ТΧ       | _                | CMOS           | EUSART asynchronous transmit.       |

|                        | СК       | ST               | CMOS           | EUSART synchronous clock.           |

|                        | CCP3     | ST               | CMOS           | Capture/Compare/PWM3.               |

| RC7/C4OUT/PSMC2B/RX/DT | RC7      | TTL/ST           | CMOS           | General purpose I/O.                |

|                        | C4OUT    | —                | CMOS           | Comparator C4 output.               |

|                        | PSMC2B   | _                | CMOS           | PSMC2 output B.                     |

|                        | RX       | ST               | _              | EUSART asynchronous input.          |

|                        | DT       | ST               | CMOS           | EUSART synchronous data.            |

| RE3/MCLR/VPP           | RE3      | TTL/ST           | —              | General purpose input.              |

|                        | MCLR     | ST               | —              | Master Clear with internal pull-up. |

|                        | Vpp      | ΗV               |                | Programming voltage.                |

| Vdd                    | Vdd      | Power            | _              | Positive supply.                    |

| Vss                    | Vss      | Power            | _              | Ground reference.                   |

Legend: AN = Analog input or output CMOS = CMOS compatible input or output OD = Open-Drain

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C$  = Schmitt Trigger input with  $I^2C$ HV = High Voltage XTAL = Crystal levels

Note 1: Pin functions can be assigned to one of two locations via software. See Register 13-1.

**2:** All pins have interrupt-on-change functionality.

#### 3.5 Stack

All devices have a 16-level x 15-bit wide hardware stack (refer to Figure 3-1). The stack space is not part of either program or data space. The PC is PUSHed onto the stack when CALL or CALLW instructions are executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer if the STVREN bit is programmed to '0' (Configuration Words). This means that after the stack has been PUSHed sixteen times, the seventeenth PUSH overwrites the value that was stored from the first PUSH. The eighteenth PUSH overwrites the second PUSH (and so on). The STKOVF and STKUNF flag bits will be set on an Overflow/Underflow, regardless of whether the Reset is enabled.

Note: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, CALLW, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

#### 3.5.1 ACCESSING THE STACK

The stack is available through the TOSH, TOSL and STKPTR registers. STKPTR is the current value of the Stack Pointer. TOSH:TOSL register pair points to the TOP of the stack. Both registers are read/writable. TOS is split into TOSH and TOSL due to the 15-bit size of the PC. To access the stack, adjust the value of STKPTR, which will position TOSH:TOSL, then read/write to TOSH:TOSL. STKPTR is five bits to allow detection of overflow and underflow.

| Note: | Care should be taken when modifying the |

|-------|-----------------------------------------|

|       | STKPTR while interrupts are enabled.    |

During normal program operation, CALL, CALLW and interrupts will increment STKPTR while RETLW, RETURN, and RETFIE will decrement STKPTR. At any time, STKPTR can be inspected to see how much stack is left. The STKPTR always points at the currently used place on the stack. Therefore, a CALL or CALLW will increment the STKPTR and then write the PC, and a return will unload the PC and then decrement the STKPTR.

Reference Figure 3-4 through Figure 3-7 for examples of accessing the stack.

#### FIGURE 3-4: ACCESSING THE STACK EXAMPLE 1

| TOSH:TOSL 0x0F        | STKPTR = 0x1F Stack Reset Disabled (STVREN = 0)                                       |

|-----------------------|---------------------------------------------------------------------------------------|

| √ 0x0E                |                                                                                       |

| 0x0D                  |                                                                                       |

| 0x0C                  |                                                                                       |

| 0x0B                  |                                                                                       |

| 0x0A                  | Initial Stack Configuration                                                           |

| 0x09                  | Initial Stack Configuration:                                                          |

| 0x08                  | After Reset, the stack is empty. The empty stack is initialized so the Stack          |

| 0x07                  | Pointer is pointing at 0x1F. If the Stack<br>Overflow/Underflow Reset is enabled, the |

| 0x06                  | TOSH/TOSL registers will return '0'. If<br>the Stack Overflow/Underflow Reset is      |

| 0x05                  | disabled, the TOSH/TOSL registers will<br>return the contents of stack address 0x0F.  |

| 0x04                  |                                                                                       |

| 0x03                  |                                                                                       |

| 0x02                  |                                                                                       |

| 0x01                  |                                                                                       |

| 0x00                  |                                                                                       |

| TOSH:TOSL 0x1F 0x0000 | Stack Reset Enabled<br>(STVREN = 1)                                                   |

|                       | N                                                                                     |

# 5.3 Register Definitions: BOR Control

## REGISTER 5-1: BORCON: BROWN-OUT RESET CONTROL REGISTER

| R/W-1/u | R/W-0/u | U-0 | U-0 | U-0 | U-0 | U-0 | R-q/u  |

|---------|---------|-----|-----|-----|-----|-----|--------|

| SBOREN  | BORFS   | —   | —   | —   | —   | —   | BORRDY |

| bit 7   |         |     |     |     |     |     | bit 0  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | <pre>SBOREN: Software Brown-out Reset Enable bit If BOREN &lt;1:0&gt; in Configuration Words ≠ 01: SBOREN is read/write, but has no effect on the BOR. If BOREN &lt;1:0&gt; in Configuration Words = 01: 1 = BOR Enabled 0 = BOR Disabled</pre>                                                                                                                           |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | BORFS: Brown-out Reset Fast Start bit <sup>(1)</sup><br><u>If BOREN&lt;1:0&gt; = 11 (Always on) or BOREN&lt;1:0&gt; = 00 (Always off)</u><br>BORFS is Read/Write, but has no effect.<br><u>If BOREN&lt;1:0&gt; = 10 (Disabled in Sleep) or BOREN&lt;1:0&gt; = 01 (Under software control):</u><br>1 = Band gap is forced on always (covers sleep/wake-up/operating cases) |

|         | 0 = Band gap operates normally, and may turn off                                                                                                                                                                                                                                                                                                                          |

| bit 5-1 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                |

| bit 0   | BORRDY: Brown-out Reset Circuit Ready Status bit<br>1 = The Brown-out Reset circuit is active<br>0 = The Brown-out Reset circuit is inactive                                                                                                                                                                                                                              |

|         |                                                                                                                                                                                                                                                                                                                                                                           |

**Note 1:** BOREN<1:0> bits are located in Configuration Words.

# 12.6 Write Verify

Depending on the application, good programming practice may dictate that the value written to the data EEPROM or program memory should be verified (see Example 12-8) to the desired value to be written. Example 12-8 shows how to verify a write to EEPROM.

#### EXAMPLE 12-8: EEPROM WRITE VERIFY

| BANKSEI | L EEDATL   | ;                    |

|---------|------------|----------------------|

| MOVF    | EEDATL, W  | ;EEDATL not changed  |

|         |            | ;from previous write |

| BSF     | EECON1, RD | ;YES, Read the       |

|         |            | ;value written       |

| XORWF   | EEDATL, W  | ;                    |

| BTFSS   | STATUS, Z  | ;Is data the same    |

| GOTO    | WRITE_ERR  | ;No, handle error    |

| :       |            | ;Yes, continue       |

|         |            |                      |

| R/W-0/0                               | R/W-0/0                                                    | R/W-0/0                            | R/W-0/0         | R/W-0/0        | R/W-0/0          | R/W-0/0        | R/W-0/0      |  |

|---------------------------------------|------------------------------------------------------------|------------------------------------|-----------------|----------------|------------------|----------------|--------------|--|

|                                       | TRIGS                                                      | EL<3:0>                            |                 |                | CHSN             | I<3:0>         |              |  |

| bit 7                                 |                                                            |                                    |                 | ·              |                  |                | bit          |  |

|                                       |                                                            |                                    |                 |                |                  |                |              |  |

| Legend:                               |                                                            |                                    |                 |                |                  |                |              |  |

| R = Readable                          | e bit                                                      | W = Writable                       | bit             | U = Unimpler   | nented bit, read | d as '0'       |              |  |

| u = Bit is unchanged x = Bit is un    |                                                            |                                    | nown            | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |  |

| '1' = Bit is set '0' = Bit is cleared |                                                            |                                    | ared            |                |                  |                |              |  |

|                                       |                                                            |                                    |                 |                |                  |                |              |  |

| bit 7-4                               | TRIGSEL<3                                                  | :0>: ADC Auto-                     | conversion Tri  | gger Source Se | election bits    |                |              |  |

|                                       | 1111 = PSN                                                 | /IC4 Falling Mat                   | ch Event        |                |                  |                |              |  |

|                                       |                                                            | /IC4 Rising Mat                    |                 |                |                  |                |              |  |

|                                       |                                                            | /IC4 Period Mat                    |                 |                |                  |                |              |  |

|                                       |                                                            | AC2 Falling Edg                    |                 |                |                  |                |              |  |

|                                       |                                                            | /IC2 Rising Edg<br>/IC2 Period Mat |                 |                |                  |                |              |  |

|                                       |                                                            | IC2 Fellou Mat                     |                 |                |                  |                |              |  |

|                                       |                                                            | IC1 Rising Edg                     |                 |                |                  |                |              |  |

|                                       |                                                            | IC1 Period Mat                     |                 |                |                  |                |              |  |

|                                       |                                                            | erved. Auto-cor                    |                 | er disabled.   |                  |                |              |  |

|                                       |                                                            | P2, Auto-conver                    |                 |                |                  |                |              |  |

|                                       |                                                            | CP1, Auto-conversion Trigger       |                 |                |                  |                |              |  |

|                                       | 0000 = Disa                                                | abled                              |                 |                |                  |                |              |  |

| bit 3-0                               | CHSN<3:0>: Negative Differential Input Channel Select bits |                                    |                 |                |                  |                |              |  |

|                                       | When ADON = 0, all multiplexer inputs are disconnected.    |                                    |                 |                |                  |                |              |  |

|                                       |                                                            | C Negative refe                    | erence – select | ed by ADNREF   | =                |                |              |  |

|                                       | 1110 = AN                                                  |                                    |                 |                |                  |                |              |  |

|                                       | 1101 = AN<br>1100 = AN                                     | -                                  |                 |                |                  |                |              |  |

|                                       | 1011 = AN                                                  |                                    |                 |                |                  |                |              |  |

|                                       | 1010 = AN                                                  |                                    |                 |                |                  |                |              |  |

|                                       | 1001 = AN                                                  |                                    |                 |                |                  |                |              |  |

|                                       | 1000 = AN                                                  |                                    |                 |                |                  |                |              |  |

|                                       | 0111 = AN                                                  | 7(1)                               |                 |                |                  |                |              |  |

|                                       | 0110 = AN                                                  |                                    |                 |                |                  |                |              |  |

|                                       | 0101 = AN                                                  |                                    |                 |                |                  |                |              |  |

|                                       | 0100 = AN<br>0011 = AN                                     |                                    |                 |                |                  |                |              |  |

|                                       | 0011 = AN<br>0010 = AN                                     | -                                  |                 |                |                  |                |              |  |

|                                       | 0010 = AN<br>0001 = AN                                     |                                    |                 |                |                  |                |              |  |

|                                       | 0000 = AN                                                  |                                    |                 |                |                  |                |              |  |

#### Note 1: PIC16(L)F1789 only. For PIC16(L)F1788, "Reserved. No channel connected."

# 20.0 5-BIT DIGITAL-TO-ANALOG CONVERTER (DAC2/3/4) MODULES

The Digital-to-Analog Converter supplies a variable voltage reference, ratiometric with the input source, with 32 selectable output levels.

The input of the DAC can be connected to:

- External VREF+ pin

- VDD supply voltage

The output of the DAC can be configured to supply a reference voltage to the following:

- · Comparator positive input

- · ADC input channel

- DACxOUT1 pin

- DACxOUT2 pin

The Digital-to-Analog Converter (DACx) can be enabled by setting the DACxEN bit of the DACxCON0 register.

#### EQUATION 20-1: DAC OUTPUT VOLTAGE

$\frac{IF DACxEN = 1}{Vout}$   $Vout = \left( (VSOURCE+ - VSOURCE-) \times \frac{DACxR[4:0]}{2^5} \right) + VSOURCE \frac{IF DACxEN = 0 \text{ and } DACxLPS = 1 \text{ and } DACxR[4:0] = 11111}{Vout}$  Vout = VSOURCE +  $\frac{IF DACxEN = 0 \text{ and } DACxLPS = 0 \text{ and } DACxR[4:0] = 00000}{Vout} = VSOURCE -$  VSOURCE+ = VDD, VREF, or FVR BUFFER 2 VSOURCE- = VSS

#### 20.2 Ratiometric Output Level

The DAC output value is derived using a resistor ladder with each end of the ladder tied to a positive and negative voltage reference input source. If the voltage of either input source fluctuates, a similar fluctuation will result in the DAC output value.

The value of the individual resistors within the ladder can be found in **Section 31.0** "**Electrical Specifications**".

Note: Register names, I/O pins, and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module, when required. The 'x' designator in DACx applies only to DAC2, DAC3, and DAC4.

## 20.1 Output Voltage Selection

The DAC has 32 voltage level ranges. The 32 levels are set with the DACxR<4:0> bits of the DACxCON1 register.

The DAC output voltage is determined by the following equations:

#### 20.3 DAC Voltage Reference Output

The DAC voltage can be output to the DACxOUT1 and DACxOUT2 pins by setting the respective DACxOE1 and DACxOE2 pins of the DACxCON0 register. Selecting the DAC reference voltage for output on either DACxOUTx pin automatically overrides the digital output buffer and digital input threshold detector functions of that pin. Reading the DACxOUTx pin when it has been configured for DAC reference voltage output will always return a '0'.

Due to the limited current drive capability, a buffer must be used on the DAC voltage reference output for external connections to either DACxOUTx pin. Figure 20-2 shows an example buffering technique.

# 22.0 TIMER0 MODULE

The Timer0 module is an 8-bit timer/counter with the following features:

- 8-bit timer/counter register (TMR0)

- 8-bit prescaler (independent of Watchdog Timer)

- Programmable internal or external clock source

- Programmable external clock edge selection

- Interrupt on overflow

- · TMR0 can be used to gate Timer1

Figure 22-1 is a block diagram of the Timer0 module.

# 22.1 Timer0 Operation

The Timer0 module can be used as either an 8-bit timer or an 8-bit counter.

#### 22.1.1 8-BIT TIMER MODE

The Timer0 module will increment every instruction cycle, if used without a prescaler. 8-bit Timer mode is selected by clearing the TMR0CS bit of the OPTION\_REG register.

When TMR0 is written, the increment is inhibited for two instruction cycles immediately following the write.

**Note:** The value written to the TMR0 register can be adjusted, in order to account for the two instruction cycle delay when TMR0 is written.

#### FIGURE 22-1: BLOCK DIAGRAM OF THE TIMER0

#### 22.1.2 8-BIT COUNTER MODE

In 8-Bit Counter mode, the Timer0 module will increment on every rising or falling edge of the TOCKI pin.

8-Bit Counter mode using the T0CKI pin is selected by setting the TMR0CS bit in the OPTION\_REG register to '1'.

The rising or falling transition of the incrementing edge for either input source is determined by the TMR0SE bit in the OPTION\_REG register.

# 23.7 Timer1 Interrupt

The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit of the PIR1 register is set. To enable the interrupt on rollover, you must set these bits:

- TMR1ON bit of the T1CON register

- TMR1IE bit of the PIE1 register

- PEIE bit of the INTCON register

- GIE bit of the INTCON register

The interrupt is cleared by clearing the TMR1IF bit in the Interrupt Service Routine.

Note: The TMR1H:TMR1L register pair and the TMR1IF bit should be cleared before enabling interrupts.

## 23.8 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- TMR1ON bit of the T1CON register must be set

- TMR1IE bit of the PIE1 register must be set

- PEIE bit of the INTCON register must be set

- T1SYNC bit of the T1CON register must be set

- TMR1CS bits of the T1CON register must be configured

- T1OSCEN bit of the T1CON register must be configured

The device will wake-up on an overflow and execute the next instructions. If the GIE bit of the INTCON register is set, the device will call the Interrupt Service Routine.

Timer1 oscillator will continue to operate in Sleep regardless of the T1SYNC bit setting.

## 23.9 CCP Capture/Compare Time Base

The CCP modules use the TMR1H:TMR1L register pair as the time base when operating in Capture or Compare mode.

In Capture mode, the value in the TMR1H:TMR1L register pair is copied into the CCPR1H:CCPR1L register pair on a configured event.

In Compare mode, an event is triggered when the value CCPR1H:CCPR1L register pair matches the value in the TMR1H:TMR1L register pair. This event can be a Auto-conversion Trigger.

For more information, see Section 25.0 "Capture/Compare/PWM Modules".

## 23.10 CCP Auto-Conversion Trigger

When any of the CCP's are configured to trigger a auto-conversion, the trigger will clear the TMR1H:TMR1L register pair. This auto-conversion does not cause a Timer1 interrupt. The CCP module may still be configured to generate a CCP interrupt.

In this mode of operation, the CCPR1H:CCPR1L register pair becomes the period register for Timer1.

Timer1 should be synchronized and Fosc/4 should be selected as the clock source in order to utilize the Auto-conversion Trigger. Asynchronous operation of Timer1 can cause a Auto-conversion Trigger to be missed.

In the event that a write to TMR1H or TMR1L coincides with a Auto-conversion Trigger from the CCP, the write will take precedence.

For more information, see Section 25.2.4 "Auto-Conversion Trigger".

#### FIGURE 23-2: TIMER1 INCREMENTING EDGE

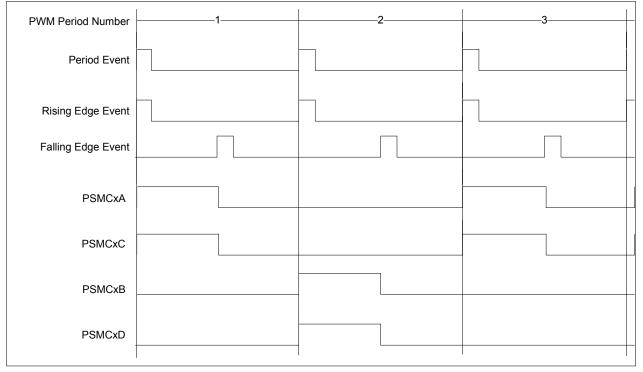

#### 26.3.5 PUSH-PULL PWM WITH FOUR FULL-BRIDGE OUTPUTS

The full-bridge push-pull PWM is used to drive transistor bridge circuits as well as synchronous switches on the secondary side of the bridge.

#### 26.3.5.1 Mode Features

- No Dead-band control

- No Steering control available

- PWM is output on the following four pins only:

- PSMCxA

- PSMCxB

- PSMCxC

- PSMCxD

Note: PSMCxA and PSMCxC are identical waveforms, and PSMCxB and PSMCxD are identical waveforms. Note: This is a subset of the 6-pin output of the push-pull PWM output, which is why pin functions are fixed in these positions, so they are compatible with that mode. See Section 26.3.6 "Push-Pull PWM with Four Full-Bridge and Complementary Outputs".

#### 26.3.5.2 Waveform generation

Push-pull waveforms generate alternating outputs on the output pairs. Therefore, there are two sets of rising edge events and two sets of falling edge events.

Odd numbered period rising edge event:

PSMCxOUT0 and PSMCxOUT2 is set active

Odd numbered period falling edge event:

PSMCxOUT0 and PSMCxOUT2 is set inactive

Even numbered period rising edge event:

· PSMCxOUT1 and PSMCxOUT3 is set active

Even numbered period falling edge event:

• PSMCxOUT1 and PSMCxOUT3 is set inactive

#### FIGURE 26-8: PUSH-PULL PWM WITH 4 FULL-BRIDGE OUTPUTS

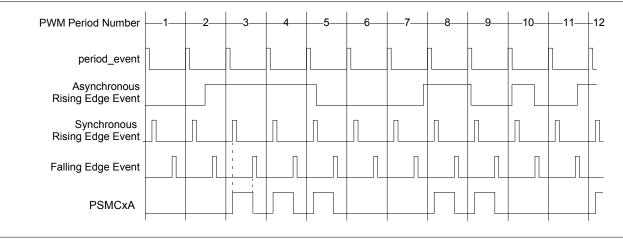

#### 26.3.7 PULSE-SKIPPING PWM

The pulse-skipping PWM is used to generate a series of fixed-length pulses that can be triggered at each period event. A rising edge event will be generated when any enabled asynchronous rising edge input is active when the period event occurs, otherwise no event will be generated.

The rising edge event occurs based upon the value in the PSMCxPH register pair.

The falling edge event always occurs according to the enabled event inputs without qualification between any two inputs.

#### 26.3.7.1 Mode Features

- No dead-band control available

- No steering control available

- PWM is output to only one pin:

- PSMCxA

# 26.3.7.2 Waveform Generation

#### Rising Edge Event

If any enabled asynchronous rising edge event = 1 when there is a period event, then upon the next synchronous rising edge event:

• PSMCxA is set active

Falling Edge Event

· PSMCxA is set inactive

**Note:** To use this mode, an external source must be used for the determination of whether or not to generate the set pulse. If the phase time base is used, it will either always generate a pulse or never generate a pulse based on the PSMCxPH value.

#### FIGURE 26-10: PULSE-SKIPPING PWM WAVEFORM

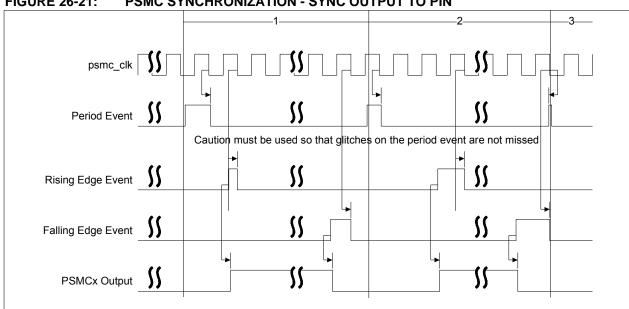

#### 26.8 **PSMC Synchronization**

It is possible to synchronize the periods of two or more PSMC modules together, provided that all modules are on the same device.

Synchronization is achieved by sending a sync signal from the master PSMC module to the desired slave modules. This sync signal generates a period event in each slave module, thereby aligning all slaves with the master. This is useful when an application requires different PWM signal generation from each module but the waveforms must be consistent within a PWM period.

#### SYNCHRONIZATION SOURCES 26.8.1

The synchronization source can be any PSMC module on the same device. For example, in a device with two PSMC modules, the possible sources for each device is as shown below:

- Sources for PSMC1

- PSMC2

- Sources for PSMC2

- PSMC1

#### **FIGURE 26-21: PSMC SYNCHRONIZATION - SYNC OUTPUT TO PIN**

#### 26.8.1.1 **PSMC Internal Connections**

The sync signal from the master PSMC module is essentially that modules period event trigger. The slave PSMC modules reset their PSMCxTMR with the sync signal instead of their own period event.

Enabling a module as a slave recipient is done with the PxSYNC bits of the PSMC Synchronization Control (PSMCxSYNC) registers; registers 26-3 and 26-4.

#### 26.8.1.2 Phase Offset Synchronization

The synchronization output signal from the PSMC module is selectable. The sync\_out source may be either:

- Period Event

- Rising Event

Source selection is made with the PxPOFST bit of the PSMCxSYNC registers, registers 26-3, 26-4 and 26-7.

When the PxPOFST bit is set, the sync out signal comes from the rising event and the period event replaces the rising event as the start of the active drive period. When PxPOFST is set, duty cycles of up to 100% are achievable in both the slave and master.

When PXPOFST is clear, the sync\_out signal comes from the period event. When PxPOFST is clear, rising events that start after the period event remove the equivalent start delay percentage from the maximum 100% duty cycle.

#### 26.8.1.3 Synchronization Skid

When the sync\_out source is the Period Event, the slave synchronous rising and falling events will lag by one psmc clk period. When the sync out source is the Rising Event, the synchronous events will lag by two clock periods. To compensate for this, the values in PHH:PHL and DCH:DCL registers can be reduced by the number of lag cycles.

#### REGISTER 26-25: PSMCxPRL: PSMC PERIOD COUNT LOW BYTE REGISTER

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|-------------|

|                  |         |                   | PSMCx   | PRL<7:0>       |                  |                  |             |

| bit 7            |         |                   |         |                |                  |                  | bit 0       |

|                  |         |                   |         |                |                  |                  |             |

| Legend:          |         |                   |         |                |                  |                  |             |

| R = Readable b   | oit     | W = Writable      | bit     | U = Unimpler   | nented bit, read | as '0'           |             |

| u = Bit is uncha | anged   | x = Bit is unkr   | nown    | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                  |             |

bit 7-0

**PSMCxPRL<7:0>:** 16-bit Period Time Least Significant bits = PSMCxPR<7:0>

# REGISTER 26-26: PSMCxPRH: PSMC PERIOD COUNT HIGH BYTE REGISTER

| R/W-0/0       | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |

|---------------|---------|---------|---------|---------|---------|---------|---------|--|--|

| PSMCxPRH<7:0> |         |         |         |         |         |         |         |  |  |

| bit 7 bit 0   |         |         |         |         |         |         |         |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **PSMCxPRH<7:0>:** 16-bit Period Time Most Significant bits

= PSMCxPR<15:8>

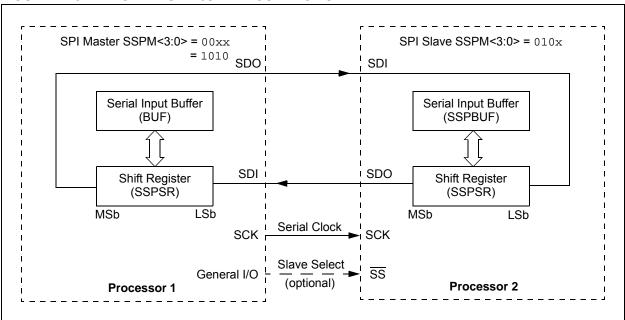

#### 27.2.2 SPI MODE OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPCON1<5:0> and SSPSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- · Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- · Slave Select mode (Slave mode only)

To enable the serial port, SSP Enable bit, SSPEN of the SSPCON1 register, must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, re-initialize the SSPCONx registers and then set the SSPEN bit. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed as follows:

- · SDI must have corresponding TRIS bit set

- · SDO must have corresponding TRIS bit cleared

- SCK (Master mode) must have corresponding TRIS bit cleared

- SCK (Slave mode) must have corresponding

TRIS bit set

- SS must have corresponding TRIS bit set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

The MSSP consists of a transmit/receive shift register (SSPSR) and a buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR until the received data is ready. Once the eight bits of data have been received, that byte is moved to the SSPBUF register. Then, the Buffer Full Detect bit, BF of the SSPSTAT register, and the interrupt flag bit, SSP1IF, are set. This double-buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPBUF reaister durina transmission/reception of data will be ignored and the write collision detect bit WCOL of the SSPCON1 register, will be set. User software must clear the WCOL bit to allow the following write(s) to the SSPBUF register to complete successfully.

When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. The Buffer Full bit, BF of the SSPSTAT register, indicates when SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur.

#### FIGURE 27-5: SPI MASTER/SLAVE CONNECTION

#### 27.2.6 SPI OPERATION IN SLEEP MODE

In SPI Master mode, module clocks may be operating at a different speed than when in Full-Power mode; in the case of the Sleep mode, all clocks are halted.

Special care must be taken by the user when the MSSP clock is much faster than the system clock.

In Slave mode, when MSSP interrupts are enabled, after the master completes sending data, an MSSP interrupt will wake the controller from Sleep.

If an exit from Sleep mode is not desired, MSSP interrupts should be disabled.

In SPI Master mode, when the Sleep mode is selected, all module clocks are halted and the transmission/reception will remain in that state until the device wakes. After the device returns to Run mode, the module will resume transmitting and receiving data.

In SPI Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in Sleep mode and data to be shifted into the SPI Transmit/Receive Shift register. When all eight bits have been received, the MSSP interrupt flag bit will be set and if enabled, will wake the device.

| Name     | Bit 7       | Bit 6           | Bit 5         | Bit 4         | Bit 3   | Bit 2  | Bit 1  | Bit 0   | Register<br>on Page |

|----------|-------------|-----------------|---------------|---------------|---------|--------|--------|---------|---------------------|

| ANSELA   | ANSA7       | _               | ANSA5         | ANSA4         | ANSA3   | ANSA2  | ANSA1  | ANSA0   | 137                 |

| APFCON1  | C2OUTSEL    | CCP1SEL         | SDOSEL        | SCKSEL        | SDISEL  | TXSEL  | RXSEL  | CCP2SEL | 132                 |

| INTCON   | GIE         | PEIE            | TMR0IE        | INTE          | IOCIE   | TMR0IF | INTF   | IOCIF   | 97                  |

| PIE1     | TMR1GIE     | ADIE            | RCIE          | TXIE          | SSP1IE  | CCP1IE | TMR2IE | TMR1IE  | 98                  |

| PIR1     | TMR1GIF     | ADIF            | RCIF          | TXIF          | SSP1IF  | CCP1IF | TMR2IF | TMR1IF  | 102                 |

| SSP1BUF  | Synchronous | s Serial Port F | Receive Buffe | r/Transmit Re | egister |        |        |         | 294*                |

| SSP1CON1 | WCOL        | SSPOV           | SSPEN         | CKP           |         | SSPM   | <3:0>  |         | 340                 |

| SSP1CON3 | ACKTIM      | PCIE            | SCIE          | BOEN          | SDAHT   | SBCDE  | AHEN   | DHEN    | 342                 |

| SSP1STAT | SMP         | CKE             | D/Ā           | Р             | S       | R/W    | UA     | BF      | 338                 |

| TRISA    | TRISA7      | TRISA6          | TRISA5        | TRISA4        | TRISA3  | TRISA2 | TRISA1 | TRISA0  | 136                 |

| TRISC    | TRISC7      | TRISC6          | TRISC5        | TRISC4        | TRISC3  | TRISC2 | TRISC1 | TRISA0  | 147                 |

#### TABLE 27-1: SUMMARY OF REGISTERS ASSOCIATED WITH SPI OPERATION

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the MSSP in SPI mode.

\* Page provides register information.

Note 1: PIC16(L)F1789 only.

|        | SYNC = 0, BRGH = 1, BRG16 = 0 |            |                             |                  |            |                             |                   |            |                             |                  |            |                             |

|--------|-------------------------------|------------|-----------------------------|------------------|------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fosc = 8.000 MHz              |            |                             | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 1.000 MHz |            |                             |

| RATE   | Actual<br>Rate                | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | _                             | _          | _                           |                  |            | _                           |                   | _          | _                           | 300              | 0.16       | 207                         |

| 1200   | —                             | —          | —                           | 1202             | 0.16       | 207                         | 1200              | 0.00       | 191                         | 1202             | 0.16       | 51                          |

| 2400   | 2404                          | 0.16       | 207                         | 2404             | 0.16       | 103                         | 2400              | 0.00       | 95                          | 2404             | 0.16       | 25                          |

| 9600   | 9615                          | 0.16       | 51                          | 9615             | 0.16       | 25                          | 9600              | 0.00       | 23                          | _                | _          | _                           |

| 10417  | 10417                         | 0.00       | 47                          | 10417            | 0.00       | 23                          | 10473             | 0.53       | 21                          | 10417            | 0.00       | 5                           |

| 19.2k  | 19231                         | 0.16       | 25                          | 19.23k           | 0.16       | 12                          | 19.2k             | 0.00       | 11                          | _                | _          | _                           |

| 57.6k  | 55556                         | -3.55      | 8                           | —                | _          | _                           | 57.60k            | 0.00       | 3                           | _                | _          | _                           |

| 115.2k | —                             | _          | —                           |                  |            | —                           | 115.2k            | 0.00       | 1                           |                  | —          | —                           |

# TABLE 28-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|        | SYNC = 0, BRGH = 0, BRG16 = 1 |            |                             |                |            |                             |                |            |                             |                |            |                             |

|--------|-------------------------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fosc = 32.000 MHz             |            | Fosc = 20.000 MHz           |                |            | Fosc                        | : = 18.43      | 2 MHz      | Fosc = 11.0592 MHz          |                |            |                             |

| RATE   | Actual<br>Rate                | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0                         | 0.00       | 6666                        | 300.0          | -0.01      | 4166                        | 300.0          | 0.00       | 3839                        | 300.0          | 0.00       | 2303                        |

| 1200   | 1200                          | -0.02      | 3332                        | 1200           | -0.03      | 1041                        | 1200           | 0.00       | 959                         | 1200           | 0.00       | 575                         |

| 2400   | 2401                          | -0.04      | 832                         | 2399           | -0.03      | 520                         | 2400           | 0.00       | 479                         | 2400           | 0.00       | 287                         |

| 9600   | 9615                          | 0.16       | 207                         | 9615           | 0.16       | 129                         | 9600           | 0.00       | 119                         | 9600           | 0.00       | 71                          |

| 10417  | 10417                         | 0.00       | 191                         | 10417          | 0.00       | 119                         | 10378          | -0.37      | 110                         | 10473          | 0.53       | 65                          |

| 19.2k  | 19.23k                        | 0.16       | 103                         | 19.23k         | 0.16       | 64                          | 19.20k         | 0.00       | 59                          | 19.20k         | 0.00       | 35                          |

| 57.6k  | 57.14k                        | -0.79      | 34                          | 56.818         | -1.36      | 21                          | 57.60k         | 0.00       | 19                          | 57.60k         | 0.00       | 11                          |

| 115.2k | 117.6k                        | 2.12       | 16                          | 113.636        | -1.36      | 10                          | 115.2k         | 0.00       | 9                           | 115.2k         | 0.00       | 5                           |

|        |                  |            |                             |                  | SYNC       | <b>C</b> = 0, BRGH          | H = 0, BRG16 = 1  |            |                             |                  |            |                             |  |

|--------|------------------|------------|-----------------------------|------------------|------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|--|

| BAUD   | Fosc = 8.000 MHz |            |                             | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 1.000 MHz |            |                             |  |

| RATE   | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 300    | 299.9            | -0.02      | 1666                        | 300.1            | 0.04       | 832                         | 300.0             | 0.00       | 767                         | 300.5            | 0.16       | 207                         |  |

| 1200   | 1199             | -0.08      | 416                         | 1202             | 0.16       | 207                         | 1200              | 0.00       | 191                         | 1202             | 0.16       | 51                          |  |

| 2400   | 2404             | 0.16       | 207                         | 2404             | 0.16       | 103                         | 2400              | 0.00       | 95                          | 2404             | 0.16       | 25                          |  |

| 9600   | 9615             | 0.16       | 51                          | 9615             | 0.16       | 25                          | 9600              | 0.00       | 23                          | _                | _          | —                           |  |

| 10417  | 10417            | 0.00       | 47                          | 10417            | 0.00       | 23                          | 10473             | 0.53       | 21                          | 10417            | 0.00       | 5                           |  |

| 19.2k  | 19.23k           | 0.16       | 25                          | 19.23k           | 0.16       | 12                          | 19.20k            | 0.00       | 11                          | _                | _          | _                           |  |

| 57.6k  | 55556            | -3.55      | 8                           | —                | —          | _                           | 57.60k            | 0.00       | 3                           | —                | _          | _                           |  |

| 115.2k | —                | _          | _                           | —                | _          | _                           | 115.2k            | 0.00       | 1                           | —                | _          | _                           |  |

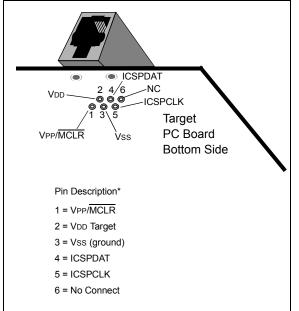

# 29.0 IN-CIRCUIT SERIAL PROGRAMMING<sup>™</sup> (ICSP<sup>™</sup>)

ICSP<sup>™</sup> programming allows customers to manufacture circuit boards with unprogrammed devices. Programming can be done after the assembly process, allowing the device to be programmed with the most recent firmware or a custom firmware. Five pins are needed for ICSP<sup>™</sup> programming:

- ICSPCLK

- ICSPDAT

- MCLR/VPP

- VDD

- Vss

In Program/Verify mode the program memory, user IDs and the Configuration Words are programmed through serial communications. The ICSPDAT pin is a bidirectional I/O used for transferring the serial data and the ICSPCLK pin is the clock input. For more information on ICSP™ refer to the "*PIC16(L)F178X Memory Programming Specification*" (DS41457).

## 29.1 High-Voltage Programming Entry Mode

The device is placed into High-Voltage Programming Entry mode by holding the ICSPCLK and ICSPDAT pins low then raising the voltage on MCLR/VPP to VIHH.

## 29.2 Low-Voltage Programming Entry Mode

The Low-Voltage Programming Entry mode allows the PIC<sup>®</sup> Flash MCUs to be programmed using VDD only, without high voltage. When the LVP bit of Configuration Words is set to '1', the low-voltage ICSP programming entry is enabled. To disable the Low-Voltage ICSP mode, the LVP bit must be programmed to '0'.

Entry into the Low-Voltage Programming Entry mode requires the following steps:

- 1. MCLR is brought to VIL.

- 2. A 32-bit key sequence is presented on ICSPDAT, while clocking ICSPCLK.

Once the key sequence is complete,  $\overline{\text{MCLR}}$  must be held at VIL for as long as Program/Verify mode is to be maintained.

If low-voltage programming is enabled (LVP = 1), the MCLR Reset function is automatically enabled and cannot be disabled. See **Section 5.5 "MCLR"** for more information.

The LVP bit can only be reprogrammed to '0' by using the High-Voltage Programming mode.

## 29.3 Common Programming Interfaces

Connection to a target device is typically done through an ICSP<sup>™</sup> header. A commonly found connector on development tools is the RJ-11 in the 6P6C (6-pin, 6 connector) configuration. See Figure 29-1.

Another connector often found in use with the PICkit<sup>™</sup> programmers is a standard 6-pin header with 0.1 inch spacing. Refer to Figure 29-2.

For additional interface recommendations, refer to your specific device programmer manual prior to PCB design.

It is recommended that isolation devices be used to separate the programming pins from other circuitry. The type of isolation is highly dependent on the specific application and may include devices such as resistors, diodes, or even jumpers. See Figure 29-3 for more information.

# PIC16(L)F1788/9

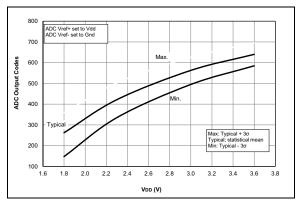

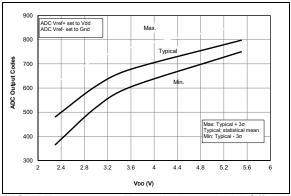

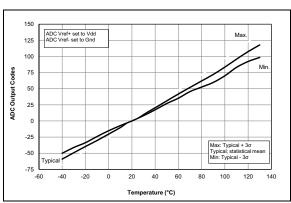

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

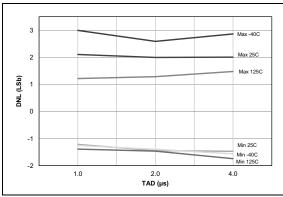

FIGURE 32-97: ADC 12-bit Mode, Single-Ended DNL, VDD = 5.5V, VREF = 5.5V.

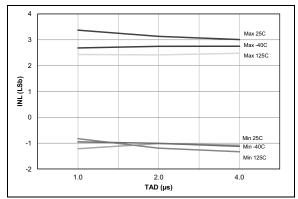

**FIGURE 32-98:** ADC 12-bit Mode, Single-Ended INL, VDD = 5.5V, VREF = 5.5V.

FIGURE 32-99: Temp. Indicator Initial Offset, High Range, Temp. = 20°C, PIC16F1788/9 Only.

**FIGURE 32-101:** Temp. Indicator Initial Offset, Low Range, Temp. = 20°C, PIC16LF1788/9 Only.

**FIGURE 32-100:** Temp. Indicator Initial Offset, Low Range, Temp. = 20°C, PIC16F1788/9 Only.

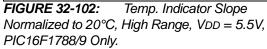

# Package Marking Information (Continued)

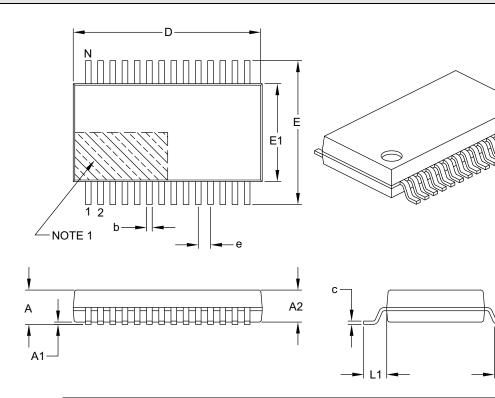

# 28-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units    | MILLIMETERS |          |       |  |  |

|--------------------------|----------|-------------|----------|-------|--|--|

| Dimensio                 | n Limits | MIN         | NOM      | MAX   |  |  |

| Number of Pins           | Ν        |             | 28       |       |  |  |

| Pitch                    | е        |             | 0.65 BSC |       |  |  |

| Overall Height           | А        | -           | -        | 2.00  |  |  |

| Molded Package Thickness | A2       | 1.65        | 1.75     | 1.85  |  |  |

| Standoff                 | A1       | 0.05        | -        | -     |  |  |

| Overall Width            | Е        | 7.40        | 7.80     | 8.20  |  |  |

| Molded Package Width     | E1       | 5.00        | 5.30     | 5.60  |  |  |

| Overall Length           | D        | 9.90        | 10.20    | 10.50 |  |  |

| Foot Length              | L        | 0.55        | 0.75     | 0.95  |  |  |

| Footprint                | L1       | 1.25 REF    |          |       |  |  |

| Lead Thickness           | с        | 0.09        | -        | 0.25  |  |  |

| Foot Angle               | φ        | 0°          | 4°       | 8°    |  |  |

| Lead Width               | b        | 0.22        | -        | 0.38  |  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B