Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                               |

| Number of I/O              | 35                                                                        |

| Program Memory Size        | 28KB (16K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 2K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 14x12b; D/A 1x8b, 3x5b                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1789-i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

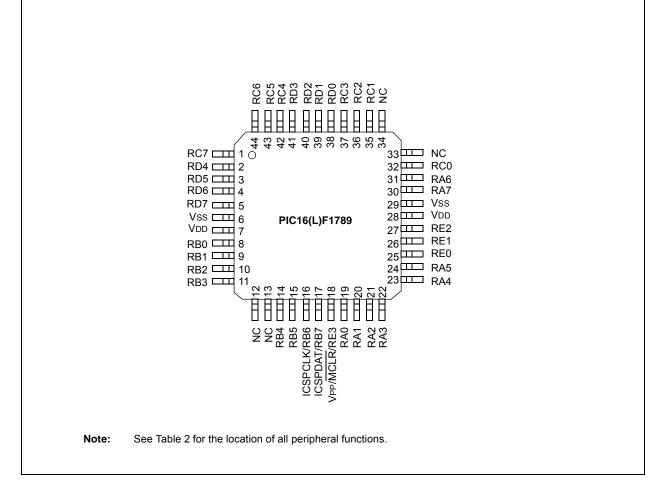

#### Pin Diagram – 44-Pin TQFP

| Name                                       | Function  | Input<br>Type | Output<br>Type | Description                                     |

|--------------------------------------------|-----------|---------------|----------------|-------------------------------------------------|

| RA0/AN0/C1IN0-/C2IN0-/                     | RA0       | TTL/ST        | CMOS           | General purpose I/O.                            |

| C3IN0-/C4IN0-/ <del>SS<sup>(1)</sup></del> | AN0       | AN0 AN        |                | ADC Channel 0 input.                            |

|                                            | C1IN0-    | AN            |                | Comparator C1 negative input.                   |

|                                            | C2IN0-    | AN            |                | Comparator C2 negative input.                   |

|                                            | C3IN0-    | AN            |                | Comparator C3 negative input.                   |

|                                            | C4IN0-    | AN            |                | Comparator C4 negative input.                   |

|                                            | SS        | ST            |                | Slave Select input.                             |

| RA1/AN1/C1IN1-/C2IN1-/                     | RA1       | TTL/ST        | CMOS           | General purpose I/O.                            |

| C3IN1-/C4IN1-/OPA1OUT                      | AN1       | AN            |                | ADC Channel 1 input.                            |

|                                            | C1IN1-    | AN            | —              | Comparator C1 negative input.                   |

|                                            | C2IN1-    | AN            | —              | Comparator C2 negative input.                   |

|                                            | C3IN1-    | AN            | —              | Comparator C3 negative input.                   |

|                                            | C4IN1-    | AN            | —              | Comparator C4 negative input.                   |

|                                            | OPA1OUT   | —             | AN             | Operational Amplifier 1 output.                 |

| RA2/AN2/C1IN0+/C2IN0+/                     | RA2       | TTL/ST        | CMOS           | General purpose I/O.                            |

| C3IN0+/C4IN0+/DAC1OUT1/                    | AN2       | AN            | _              | ADC Channel 2 input.                            |

| VREF-/DAC1VREF-                            | C1IN0+    | AN            | _              | Comparator C1 positive input.                   |

|                                            | C2IN0+    | AN            | _              | Comparator C2 positive input.                   |

|                                            | C3IN0+    | AN            | _              | Comparator C3 positive input.                   |

|                                            | C4IN0+    | AN            |                | Comparator C4 positive input.                   |

|                                            | DAC1OUT1  | _             | AN             | Digital-to-Analog Converter output.             |

|                                            | VREF-     | AN            |                | ADC Negative Voltage Reference input.           |

|                                            | DAC1VREF- | AN            |                | Digital-to-Analog Converter negative reference. |

| RA3/AN3/VREF+/C1IN1+/                      | RA3       | TTL/ST        | CMOS           | General purpose I/O.                            |

| DAC1VREF+/DAC2VREF+/                       | AN3       | AN            | _              | ADC Channel 3 input.                            |

| DAC3VREF+/DAC4VREF+                        | VREF+     | AN            | _              | ADC Voltage Reference input.                    |

|                                            | C1IN1+    | AN            | _              | Comparator C1 positive input.                   |

|                                            | DAC1VREF+ | AN            | _              | Digital-to-Analog Converter positive reference. |

|                                            | DAC2VREF+ | AN            | _              | Digital-to-Analog Converter positive reference. |

|                                            | DAC3VREF+ | AN            | _              | Digital-to-Analog Converter positive reference. |

|                                            | DAC4VREF+ | AN            | _              | Digital-to-Analog Converter positive reference. |

| RA4/C1OUT/OPA1IN+/T0CKI/                   | RA4       | TTL/ST        | CMOS           | General purpose I/O.                            |

| DAC4OUT1                                   | C10UT     | _             | CMOS           | Comparator C1 output.                           |

|                                            | OPA1IN+   | AN            | _              | Operational Amplifier 1 non-inverting input.    |

|                                            | TOCKI     | ST            | _              | Timer0 clock input.                             |

|                                            | DAC4OUT1  | _             | AN             | Digital-to-Analog Converter output.             |

| RA5/AN4/C2OUT/OPA1IN-/                     | RA5       | TTL/ST        | CMOS           | General purpose I/O.                            |

| SS <sup>(1)</sup> /DAC2OUT1                | AN4       | AN            | _              | ADC Channel 4 input.                            |

|                                            | C2OUT     | _             | CMOS           | Comparator C2 output.                           |

|                                            | OPA1IN-   | AN            | _              | Operational Amplifier 1 inverting input.        |

|                                            | SS        | ST            |                | Slave Select input.                             |

|                                            | 50        | <u> </u>      |                | Digital-to-Analog Converter output.             |

TABLE 1-2: PIC16(L)F1788 PINOUT DESCRIPTION

Legend:

AN = Analog input or output

CMOS = CMOS compatible input or output

OD = Open-Drain

TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

I<sup>2</sup>C = Schmitt Trigger input with I<sup>2</sup>C

HV = High Voltage

XTAL = Crystal levels

Note 1: Pin functions can be assigned to one of two locations via software. See Register 13-1.

2: All pins have interrupt-on-change functionality.

The memory maps for Bank 0 through Bank 31 are shown in the tables in this section.

### TABLE 3-3: PIC16(L)F1788 MEMORY MAP (BANKS 0-7)

|      | BANK 0                                     | •    | ,<br>BANK 1                                |      | BANK 2                                     |      | BANK 3                                     |      | BANK 4                                     |      | BANK 5                                     |      | BANK 6                                     |      | BANK 7                                     |

|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|

| 000h |                                            | 080h |                                            | 100h |                                            | 180h |                                            | 200h |                                            | 280h |                                            | 300h |                                            | 380h |                                            |

|      | Core Registers<br>(Table 3-2)              |

| 00Bh |                                            | 08Bh |                                            | 10Bh |                                            | 18Bh |                                            | 20Bh |                                            | 28Bh |                                            | 30Bh |                                            | 38Bh |                                            |

| 00Ch | PORTA                                      | 08Ch | TRISA                                      | 10Ch | LATA                                       | 18Ch | ANSELA                                     | 20Ch | WPUA                                       | 28Ch | ODCONA                                     | 30Ch | SLRCONA                                    | 38Ch | INLVLA                                     |

| 00Dh | PORTB                                      | 08Dh | TRISB                                      | 10Dh | LATB                                       | 18Dh | ANSELB                                     | 20Dh | WPUB                                       | 28Dh | ODCONB                                     | 30Dh | SLRCONB                                    | 38Dh | INLVLB                                     |

| 00Eh | PORTC                                      | 08Eh | TRISC                                      | 10Eh | LATC                                       | 18Eh | ANSELC                                     | 20Eh | WPUC                                       | 28Eh | ODCONC                                     | 30Eh | SLRCONC                                    | 38Eh | INLVLC                                     |

| 00Fh | _                                          | 08Fh | _                                          | 10Fh |                                            | 18Fh | —                                          | 20Fh |                                            | 28Fh | _                                          | 30Fh |                                            | 38Fh | —                                          |

| 010h | PORTE                                      | 090h | TRISE                                      | 110h | —                                          | 190h | —                                          | 210h | WPUE                                       | 290h | -                                          | 310h | _                                          | 390h | INLVLE                                     |

| 011h | PIR1                                       | 091h | PIE1                                       | 111h | CM1CON0                                    | 191h | EEADRL                                     | 211h | SSP1BUF                                    | 291h | CCPR1L                                     | 311h | CCPR3L                                     | 391h | IOCAP                                      |

| 012h | PIR2                                       | 092h | PIE2                                       | 112h | CM1CON1                                    | 192h | EEADRH                                     | 212h | SSP1ADD                                    | 292h | CCPR1H                                     | 312h | CCPR3H                                     | 392h | IOCAN                                      |

| 013h | PIR3                                       | 093h | PIE3                                       | 113h | CM2CON0                                    | 193h | EEDATL                                     | 213h | SSP1MSK                                    | 293h | CCP1CON                                    | 313h | CCP3CON                                    | 393h | IOCAF                                      |

| 014h | PIR4                                       | 094h | PIE4                                       | 114h | CM2CON1                                    | 194h | EEDATH                                     | 214h | SSP1STAT                                   | 294h | —                                          | 314h | —                                          | 394h | IOCBP                                      |

| 015h | TMR0                                       | 095h | OPTION_REG                                 | 115h | CMOUT                                      | 195h | EECON1                                     | 215h | SSP1CON1                                   | 295h | —                                          | 315h | _                                          | 395h | IOCBN                                      |

| 016h | TMR1L                                      | 096h | PCON                                       | 116h | BORCON                                     | 196h | EECON2                                     | 216h | SSP1CON2                                   | 296h | —                                          | 316h | —                                          | 396h | IOCBF                                      |

| 017h | TMR1H                                      | 097h | WDTCON                                     | 117h | FVRCON                                     | 197h | VREGCON <sup>(1)</sup>                     | 217h | SSP1CON3                                   | 297h | —                                          | 317h | _                                          | 397h | IOCCP                                      |

| 018h | T1CON                                      | 098h | OSCTUNE                                    | 118h | DAC1CON0                                   | 198h | —                                          | 218h |                                            | 298h | CCPR2L                                     | 318h | —                                          | 398h | IOCCN                                      |

| 019h | T1GCON                                     | 099h | OSCCON                                     | 119h | DAC1CON1                                   | 199h | RC1REG                                     | 219h |                                            | 299h | CCPR2H                                     | 319h | —                                          | 399h | IOCCF                                      |

| 01Ah | TMR2                                       | 09Ah | OSCSTAT                                    | 11Ah | CM4CON0                                    | 19Ah | TX1REG                                     | 21Ah | —                                          | 29Ah | CCP2CON                                    | 31Ah | —                                          | 39Ah | —                                          |

| 01Bh | PR2                                        | 09Bh | ADRESL                                     | 11Bh | CM4CON1                                    | 19Bh | SP1BRGL                                    | 21Bh | —                                          | 29Bh | —                                          | 31Bh | —                                          | 39Bh | —                                          |

| 01Ch | T2CON                                      | 09Ch | ADRESH                                     | 11Ch | APFCON2                                    | 19Ch | SP1BRGH                                    | 21Ch | —                                          | 29Ch | —                                          | 31Ch | —                                          | 39Ch | —                                          |

| 01Dh | _                                          | 09Dh | ADCON0                                     | 11Dh | APFCON1                                    | 19Dh | RC1STA                                     | 21Dh | _                                          | 29Dh | _                                          | 31Dh | _                                          | 39Dh | —                                          |

| 01Eh | _                                          | 09Eh | ADCON1                                     | 11Eh | CM3CON0                                    | 19Eh | TX1STA                                     | 21Eh | —                                          | 29Eh | —                                          | 31Eh | _                                          | 39Eh | _                                          |

| 01Fh | —                                          | 09Fh | ADCON2                                     | 11Fh | CM3CON1                                    | 19Fh | BAUD1CON                                   | 21Fh |                                            | 29Fh | —                                          | 31Fh | —                                          | 39Fh | —                                          |

| 020h |                                            | 0A0h |                                            | 120h |                                            | 1A0h |                                            | 220h |                                            | 2A0h |                                            | 320h |                                            | 3A0h |                                            |

|      | General<br>Purpose<br>Register<br>80 Bytes |

| 06Fh |                                            | 0EFh |                                            | 16Fh |                                            | 1EFh |                                            | 26Fh |                                            | 2EFh |                                            | 36Fh |                                            | 3EFh |                                            |

| 070h |                                            | 0F0h |                                            | 170h |                                            | 1F0h |                                            | 270h |                                            | 2F0h |                                            | 370h |                                            | 3F0h |                                            |

|      | Common RAM<br>70h – 7Fh                    |      | Accesses<br>70h – 7Fh                      |      | Accesses<br>70h – 7Fh                      |      | Accesses<br>70h – 7Fh                      |      | Accesses<br>70h – 7Fh                      |      | Accesses<br>70h – 7Fh                      |      | Accesses<br>70h – 7Fh                      |      | Accesses<br>70h – 7Fh                      |

| 07Fh |                                            | 0FFh |                                            | 17Fh |                                            | 1FFh |                                            | 27Fh |                                            | 2FFh |                                            | 37Fh |                                            | 3FFh |                                            |

**Legend:** = Unimplemented data memory locations, read as '0'.

Note 1: PIC16F1788 only.

#### 3.5 Stack

All devices have a 16-level x 15-bit wide hardware stack (refer to Figure 3-1). The stack space is not part of either program or data space. The PC is PUSHed onto the stack when CALL or CALLW instructions are executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer if the STVREN bit is programmed to '0' (Configuration Words). This means that after the stack has been PUSHed sixteen times, the seventeenth PUSH overwrites the value that was stored from the first PUSH. The eighteenth PUSH overwrites the second PUSH (and so on). The STKOVF and STKUNF flag bits will be set on an Overflow/Underflow, regardless of whether the Reset is enabled.

Note: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, CALLW, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

#### 3.5.1 ACCESSING THE STACK

The stack is available through the TOSH, TOSL and STKPTR registers. STKPTR is the current value of the Stack Pointer. TOSH:TOSL register pair points to the TOP of the stack. Both registers are read/writable. TOS is split into TOSH and TOSL due to the 15-bit size of the PC. To access the stack, adjust the value of STKPTR, which will position TOSH:TOSL, then read/write to TOSH:TOSL. STKPTR is five bits to allow detection of overflow and underflow.

| Note: | Care should be taken when modifying the |

|-------|-----------------------------------------|

|       | STKPTR while interrupts are enabled.    |

During normal program operation, CALL, CALLW and interrupts will increment STKPTR while RETLW, RETURN, and RETFIE will decrement STKPTR. At any time, STKPTR can be inspected to see how much stack is left. The STKPTR always points at the currently used place on the stack. Therefore, a CALL or CALLW will increment the STKPTR and then write the PC, and a return will unload the PC and then decrement the STKPTR.

Reference Figure 3-4 through Figure 3-7 for examples of accessing the stack.

#### FIGURE 3-4: ACCESSING THE STACK EXAMPLE 1

| TOSH:TOSL 0x0F        | STKPTR = 0x1F Stack Reset Disabled (STVREN = 0)                                       |

|-----------------------|---------------------------------------------------------------------------------------|

| √ 0x0E                |                                                                                       |

| 0x0D                  |                                                                                       |

| 0x0C                  |                                                                                       |

| 0x0B                  |                                                                                       |

| 0x0A                  | Initial Stack Configuration                                                           |

| 0x09                  | Initial Stack Configuration:                                                          |

| 0x08                  | After Reset, the stack is empty. The empty stack is initialized so the Stack          |

| 0x07                  | Pointer is pointing at 0x1F. If the Stack<br>Overflow/Underflow Reset is enabled, the |

| 0x06                  | TOSH/TOSL registers will return '0'. If<br>the Stack Overflow/Underflow Reset is      |

| 0x05                  | disabled, the TOSH/TOSL registers will<br>return the contents of stack address 0x0F.  |

| 0x04                  |                                                                                       |

| 0x03                  |                                                                                       |

| 0x02                  |                                                                                       |

| 0x01                  |                                                                                       |

| 0x00                  |                                                                                       |

| TOSH:TOSL 0x1F 0x0000 | Stack Reset Enabled<br>(STVREN = 1)                                                   |

|                       | N                                                                                     |

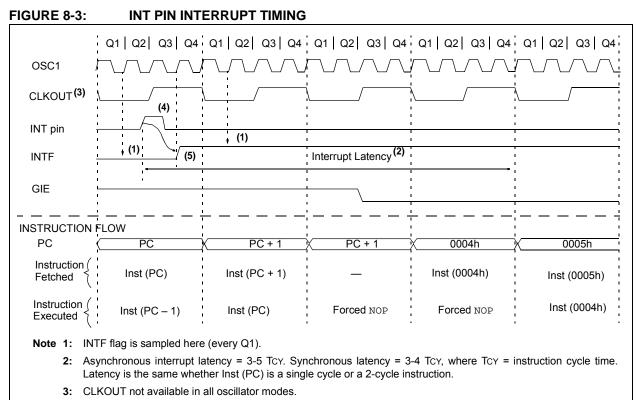

4: For minimum width of INT pulse, refer to AC specifications in Section 31.0 "Electrical Specifications"".

5: INTF is enabled to be set any time during the Q4-Q1 cycles.

#### 9.2 Low-Power Sleep Mode

"F" devices contain an internal Low Dropout (LDO) voltage regulator, which allows the device I/O pins to operate at voltages up to 5.5V while the internal device logic operates at a lower voltage. The LDO and its associated reference circuitry must remain active when the device is in Sleep mode. "F" devices allow the user to optimize the operating current in Sleep, depending on the application requirements.

A Low-Power Sleep mode can be selected by setting the VREGPM bit of the VREGCON register. With this bit set, the LDO and reference circuitry are placed in a low-power state when the device is in Sleep.

## 9.2.1 SLEEP CURRENT VS. WAKE-UP TIME

In the default operating mode, the LDO and reference circuitry remain in the normal configuration while in Sleep. The device is able to exit Sleep mode quickly since all circuits remain active. In Low-Power Sleep mode, when waking up from Sleep, an extra delay time is required for these circuits to return to the normal configuration and stabilize.

The Low-Power Sleep mode is beneficial for applications that stay in Sleep mode for long periods of time. The normal mode is beneficial for applications that need to wake from Sleep quickly and frequently.

#### 9.2.2 PERIPHERAL USAGE IN SLEEP

Some peripherals that can operate in Sleep mode will not operate properly with the Low-Power Sleep mode selected. The LDO will remain in the normal power mode when those peripherals are enabled. The Low-Power Sleep mode is intended for use with these peripherals:

- Brown-Out Reset (BOR)

- Watchdog Timer (WDT)

- · External interrupt pin/Interrupt-on-change pins

- Timer1 (with external clock source)

- Note: "LF" devices do not have a configurable Low-Power Sleep mode. "LF" devices are an unregulated device and are always in the lowest power state when in Sleep, with no wake-up time penalty. These devices have a lower maximum VDD and I/O voltage than "F" devices. See Section 31.0 "Electrical Specifications" for more information.

#### EXAMPLE 12-6: WRITING TO FLASH PROGRAM MEMORY

| (AMPL                | LE 12-6:       | WRITING TO FLA            | ASH PROGRAM MEMORY                                                                                             |

|----------------------|----------------|---------------------------|----------------------------------------------------------------------------------------------------------------|

| This                 | write rout     | ine assumes the f         | ollowing:                                                                                                      |

| 1. Th                | ne 16 bytes    | of data are load          | led, starting at the address in DATA_ADDR                                                                      |

|                      | _              |                           | en is made up of two adjacent bytes in DATA_ADDR,                                                              |

|                      |                | ttle endian forma         |                                                                                                                |

|                      |                |                           | e least significant bits = 0000) is loaded in ADDRH:ADDRL                                                      |

|                      |                |                           | n shared data memory 0x70 - 0x7F (common RAM)                                                                  |

|                      |                |                           |                                                                                                                |

|                      | BCF            | INTCON, GIE               | ; Disable ints so required sequences will execute properly                                                     |

|                      | BANKSEL        | EEADRH                    | ; Bank 3                                                                                                       |

|                      | MOVF           | ADDRH, W                  | ; Load initial address                                                                                         |

|                      | MOVWF          | EEADRH                    | ;                                                                                                              |

|                      | MOVF           | ADDRL,W                   | ;                                                                                                              |

|                      | MOVF<br>MOVWF  | EEADRL                    | ,<br>;                                                                                                         |

|                      | MOVWF<br>MOVLW |                           | ' ; Load initial data address                                                                                  |

|                      | MOVEW          | FSROL                     | ;                                                                                                              |

|                      | MOVLW          |                           | ; Load initial data address                                                                                    |

|                      | MOVEW          |                           | ;                                                                                                              |

|                      |                |                           |                                                                                                                |

|                      | BSF            |                           | ; Point to program memory<br>: Not configuration grade                                                         |

|                      | BCF            |                           | ; Not configuration space                                                                                      |

|                      | BSF            | EECON1, WREN              | ; Enable writes                                                                                                |

| 0.05                 | BSF            | EECON1,LWLO               | ; Only Load Write Latches                                                                                      |

| 00P                  |                | 2220                      |                                                                                                                |

|                      | MOVIW          | FSR0++                    | ; Load first data byte into lower                                                                              |

|                      | MOVWF          | EEDATL                    | ;                                                                                                              |

|                      | MOVIW          | FSR0++                    | ; Load second data byte into upper                                                                             |

|                      | MOVWF          | EEDATH                    | ;                                                                                                              |

|                      |                |                           |                                                                                                                |

|                      | MOVF           | EEADRL,W                  | ; Check if lower bits of address are '000'                                                                     |

|                      | XORLW          | 0x0F                      | ; Check if we're on the last of 16 addresses                                                                   |

|                      | ANDLW          | 0x0F                      | i                                                                                                              |

|                      | BTFSC          | STATUS , Z                | ; Exit if last of 16 words,                                                                                    |

|                      | GOTO           | START_WRITE               | ;                                                                                                              |

|                      |                |                           |                                                                                                                |

|                      | MOVLW          | 55h                       | ; Start of required write sequence:                                                                            |

|                      | MOVWF          | EECON2                    | ; Write 55h                                                                                                    |

| g g                  | MOVLW          | 0AAh                      | i                                                                                                              |

| enc                  | MOVWF          | EECON2                    | ; Write AAh                                                                                                    |

| Required<br>Sequence | BSF            | EECON1,WR                 | ; Set WR bit to begin write                                                                                    |

| s, R                 | NOP            |                           | ; Any instructions here are ignored as processor                                                               |

|                      |                |                           | ; halts to begin write sequence                                                                                |

| 1                    | NOP            |                           | ; Processor will stop here and wait for write to complete.                                                     |

|                      |                |                           |                                                                                                                |

|                      |                |                           | ; After write processor continues with 3rd instruction.                                                        |

|                      |                |                           |                                                                                                                |

|                      | INCF           | EEADRL, F                 | ; Still loading latches Increment address                                                                      |

|                      | GOTO           | LOOP                      | ; Write next latches                                                                                           |

|                      |                |                           |                                                                                                                |

| TART_W               | VRITE          |                           |                                                                                                                |

|                      | BCF            | EECON1,LWLO               | ; No more loading latches - Actually start Flash program                                                       |

|                      |                |                           | ; memory write                                                                                                 |

|                      |                |                           |                                                                                                                |

|                      | MOVLW          | 55h                       | ; Start of required write sequence:                                                                            |

|                      | MOVWF          | EECON2                    | ; Write 55h                                                                                                    |

| မ ရ                  | MOVLW          | 0AAh                      | ;                                                                                                              |

| uire                 | MOVWF          | EECON2                    | ; Write AAh                                                                                                    |

| Required<br>Sequence | BSF            | EECON1,WR                 | ; Set WR bit to begin write                                                                                    |

| Ϋ́ Ϋ́                | NOP            |                           | ; Any instructions here are ignored as processor                                                               |

|                      |                |                           | ; halts to begin write sequence                                                                                |

|                      | NOP            |                           | ; Processor will stop here and wait for write complete.                                                        |

|                      | -              |                           | a arre i i a a anne eer arre tampioool                                                                         |

|                      |                |                           |                                                                                                                |

|                      |                |                           | ; after write processor continues with 3rd instruction                                                         |

|                      | BCF            | EECON1 . WREN             | ; after write processor continues with 3rd instruction ; Disable writes                                        |

|                      | BCF<br>BSF     | EECON1,WREN<br>INTCON,GIE | <pre>; after write processor continues with 3rd instruction<br/>; Disable writes<br/>; Enable interrupts</pre> |

| R/W-1/1                            | R/W-1/1 | R/W-1/1           | R/W-1/1 | R/W-1/1                                             | R/W-1/1 | R/W-1/1 | R/W-1/1 |  |  |

|------------------------------------|---------|-------------------|---------|-----------------------------------------------------|---------|---------|---------|--|--|

| INLVLC7                            | INLVLC6 | INLVLC5           | INLVLC4 | INLVLC3                                             | INLVLC2 | INLVLC1 | INLVLC0 |  |  |

| bit 7                              |         |                   |         |                                                     |         |         | bit 0   |  |  |

|                                    |         |                   |         |                                                     |         |         |         |  |  |

| Legend:                            |         |                   |         |                                                     |         |         |         |  |  |

| R = Readable                       | bit     | W = Writable I    | bit     | U = Unimplemented bit, read as '0'                  |         |         |         |  |  |

| u = Bit is unchanged x = Bit is ur |         |                   | nown    | -n/n = Value at POR and BOR/Value at all other Rese |         |         |         |  |  |

| '1' = Bit is set                   |         | '0' = Bit is clea | ared    |                                                     |         |         |         |  |  |

#### REGISTER 13-25: INLVLC: PORTC INPUT LEVEL CONTROL REGISTER

bit 7-0 INLVLC<7:0>: PORTC Input Level Select bits

For RC<7:0> pins, respectively

1 = ST input used for PORT reads and interrupt-on-change

0 = TTL input used for PORT reads and interrupt-on-change

| Name    | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------------------|

| LATC    | LATC7   | LATC6   | LATC5   | LATC4   | LATC3   | LATC2   | LATC1   | LATC0   | 147                 |

| PORTC   | RC7     | RC6     | RC5     | RC4     | RC3     | RC2     | RC1     | RC0     | 147                 |

| TRISC   | TRISC7  | TRISC6  | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1  | TRISC0  | 147                 |

| WPUC    | WPUC7   | WPUC6   | WPUC5   | WPUC4   | WPUC3   | WPUC2   | WPUC1   | WPUC0   | 148                 |

| INLVLC  | INLVLC7 | INLVLC6 | INLVLC5 | INLVLC4 | INLVLC3 | INLVLC2 | INLVLC1 | INLVLC0 | 149                 |

| LATC    | LATC7   | LATC6   | LATC5   | LATC4   | LATC3   | LATC2   | LATC1   | LATC0   | 147                 |

| ODCONC  | ODC7    | ODC6    | ODC5    | ODC4    | ODC3    | ODC2    | ODC1    | ODC0    | 148                 |

| PORTC   | RC7     | RC6     | RC5     | RC4     | RC3     | RC2     | RC1     | RC0     | 147                 |

| SLRCONC | SLRC7   | SLRC6   | SLRC5   | SLRC4   | SLRC3   | SLRC2   | SLRC1   | SLRC0   | 148                 |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTC.

### 17.1 ADC Configuration

When configuring and using the ADC the following functions must be considered:

- · Port configuration

- · Channel selection

- Single-ended

- Differential

- ADC voltage reference selection

- ADC conversion clock source

- · Interrupt control

- · Result formatting

#### 17.1.1 PORT CONFIGURATION

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ANSEL bits. Refer to **Section 13.0 "I/O Ports"** for more information.

| Note: | Analog voltages on any pin that is defined |  |  |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|--|--|

|       | as a digital input may cause the input     |  |  |  |  |  |  |  |  |  |  |

|       | buffer to conduct excess current.          |  |  |  |  |  |  |  |  |  |  |

#### 17.1.2 CHANNEL SELECTION

There are up to 18 channel selections available:

- AN<13:8, 4:0> pins (PIC16(L)F1788 only)

- AN<21, 13:0> pins (PIC16(L)F1789 only)

- Temperature Indicator

- DAC\_output

- FVR (Fixed Voltage Reference) Output

Refer to Section 15.0 "Fixed Voltage Reference (FVR)" and Section 16.0 "Temperature Indicator Module" for more information on these channel selections.

When converting differential signals, the negative input for the channel is selected with the CHSN<3:0> bits of the ADCON2 register. Any positive input can be paired with any negative input to determine the differential channel.

The CHS<4:0> bits of the ADCON0 register determine which positive channel is selected.

When CHSN<3:0> = 1111 then the ADC is effectively a single ended ADC converter.

When changing channels, a delay is required before starting the next conversion.

#### 17.1.3 ADC VOLTAGE REFERENCE

The ADPREF bits of the ADCON1 register provide control of the positive voltage reference. The positive voltage reference can be:

- VREF+

- VDD

- FVR Buffer1

The ADNREF bits of the ADCON1 register provide control of the negative voltage reference. The negative voltage reference can be:

- VREF- pin

- Vss

See **Section 15.0** "Fixed Voltage Reference (FVR)" for more details on the Fixed Voltage Reference.

#### 17.1.4 CONVERSION CLOCK

The source of the conversion clock is software selectable via the ADCS bits of the ADCON1 register. There are seven possible clock options:

- Fosc/2

- Fosc/4

- Fosc/8

- Fosc/16

- Fosc/32

- Fosc/64

- FRC (dedicated internal FRC oscillator)

The time to complete one bit conversion is defined as TAD. One full 12-bit conversion requires 15 TAD periods as shown in Figure 17-2.

For correct conversion, the appropriate TAD specification must be met. Refer to the ADC conversion requirements in **Section 31.0 "Electrical Specifications"** for more information. Table 17-1 gives examples of appropriate ADC clock selections.

**Note:** Unless using the FRC, any changes in the system clock frequency will change the ADC clock frequency, which may adversely affect the ADC result.

#### **18.4** Register Definitions: Op Amp Control

#### REGISTER 18-1: OPAxCON: OPERATIONAL AMPLIFIERS (OPAx) CONTROL REGISTERS

| R/W-0/0                                                           | R/W-0/0           | U-0               | U-0            | U-0           | R/W-0/0         | R/W-0/0          | R/W-0/0      |

|-------------------------------------------------------------------|-------------------|-------------------|----------------|---------------|-----------------|------------------|--------------|

| OPAxEN                                                            | OPAxSP            |                   | —              | _             |                 | OPAxCH<2:0>      |              |

| bit 7                                                             |                   |                   |                |               | ·               |                  | bit 0        |

|                                                                   |                   |                   |                |               |                 |                  |              |

| Legend:                                                           |                   |                   |                |               |                 |                  |              |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0 |                   |                   |                |               |                 |                  |              |

| u = Bit is unch                                                   | anged             | x = Bit is unkr   | nown           | -n/n = Value  | at POR and BO   | R/Value at all c | other Resets |

| '1' = Bit is set                                                  |                   | '0' = Bit is clea | ared           | q = Value de  | pends on condit | ion              |              |

|                                                                   |                   |                   |                |               |                 |                  |              |

| bit 7                                                             | OPAxEN: Op        | Amp Enable b      | it             |               |                 |                  |              |

|                                                                   | 1 = Op amp i      |                   |                |               |                 |                  |              |

|                                                                   | 0 = Op amp i      | s disabled and    | consumes no    | active power  |                 |                  |              |

| bit 6                                                             | OPAxSP: Op        | Amp Speed/Po      | ower Select bi | it            |                 |                  |              |

|                                                                   |                   | tor operates in   | high GBWP m    | node          |                 |                  |              |

|                                                                   | 0 = Reserved      | I. Do not use.    |                |               |                 |                  |              |

| bit 5-3                                                           | Unimplemen        | ted: Read as '    | D'             |               |                 |                  |              |

| bit 2-0                                                           | OPAxCH<2:0        | >: Non-invertir   | ng Channel Se  | election bits |                 |                  |              |

|                                                                   | $111 = Non_{-in}$ | verting input co  | nnects to DA   |               |                 |                  |              |

- 111 = Non-inverting input connects to DAC4\_output

- 110 = Non-inverting input connects to DAC3\_output

- 101 = Non-inverting input connects to DAC2\_output

- 100 = Non-inverting input connects to DAC1\_output

- 011 = Non-inverting input connects to FVR Buffer 2 output

- 010 = Reserved do not use

- 001 = Reserved do not use

- 000 = Non-inverting input connects to OPAxIN+ pin

| Name                   | Bit 7         | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1        | Bit 0   | Register<br>on Page |

|------------------------|---------------|--------|---------|---------|---------|---------|--------------|---------|---------------------|

| ANSELA                 | ANSA7         | _      | ANSA5   | ANSA4   | ANSA3   | ANSA2   | ANSA1        | ANSA0   | 137                 |

| ANSELB                 | —             | ANSB6  | ANSB5   | ANSB4   | ANSB3   | ANSB2   | ANSB1        | ANSB0   | 143                 |

| DAC1CON0               | DAC1EN        | _      | DAC10E1 | DAC10E2 | DAC1PS  | SS<1:0> | _            | DAC1NSS | 192                 |

| DAC1CON1               |               |        |         | DAC1    | 1R<7:0> |         |              |         | 192                 |

| OPA1CON                | OPA1EN        | OPA1SP | —       | _       | _       | —       | OPA1P0       | CH<1:0> | 187                 |

| OPA2CON                | OPA2EN        | OPA2SP | —       | _       | _       | —       | OPA2P0       | CH<1:0> | 187                 |

| OPA3CON <sup>(1)</sup> | <b>OPA3EN</b> | OPA3SP | —       | _       | _       | —       | OPA3PCH<1:0> |         | 187                 |

| TRISA                  | TRISA7        | TRISA6 | TRISA5  | TRISA4  | TRISA3  | TRISA2  | TRISA1       | TRISA0  | 136                 |

| TRISB                  | TRISB7        | TRISB6 | TRISB5  | TRISB4  | TRISB3  | TRISB2  | TRISB1       | TRISB0  | 142                 |

| TRISC                  | TRISC7        | TRISC6 | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1       | TRISC0  | 147                 |

#### TABLE 18-1: SUMMARY OF REGISTERS ASSOCIATED WITH OP AMPS

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by op amps.

**Note 1:** PIC16(L)F1789 only

### 20.0 5-BIT DIGITAL-TO-ANALOG CONVERTER (DAC2/3/4) MODULES

The Digital-to-Analog Converter supplies a variable voltage reference, ratiometric with the input source, with 32 selectable output levels.

The input of the DAC can be connected to:

- External VREF+ pin

- VDD supply voltage

The output of the DAC can be configured to supply a reference voltage to the following:

- · Comparator positive input

- · ADC input channel

- DACxOUT1 pin

- DACxOUT2 pin

The Digital-to-Analog Converter (DACx) can be enabled by setting the DACxEN bit of the DACxCON0 register.

#### EQUATION 20-1: DAC OUTPUT VOLTAGE

$\frac{IF DACxEN = 1}{Vout}$   $Vout = \left( (VSOURCE+ - VSOURCE-) \times \frac{DACxR[4:0]}{2^5} \right) + VSOURCE \frac{IF DACxEN = 0 \text{ and } DACxLPS = 1 \text{ and } DACxR[4:0] = 11111}{Vout}$  Vout = VSOURCE +  $\frac{IF DACxEN = 0 \text{ and } DACxLPS = 0 \text{ and } DACxR[4:0] = 00000}{Vout} = VSOURCE -$  VSOURCE+ = VDD, VREF, or FVR BUFFER 2 VSOURCE- = VSS

#### 20.2 Ratiometric Output Level

The DAC output value is derived using a resistor ladder with each end of the ladder tied to a positive and negative voltage reference input source. If the voltage of either input source fluctuates, a similar fluctuation will result in the DAC output value.

The value of the individual resistors within the ladder can be found in **Section 31.0** "**Electrical Specifications**".

Note: Register names, I/O pins, and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module, when required. The 'x' designator in DACx applies only to DAC2, DAC3, and DAC4.

#### 20.1 Output Voltage Selection

The DAC has 32 voltage level ranges. The 32 levels are set with the DACxR<4:0> bits of the DACxCON1 register.

The DAC output voltage is determined by the following equations:

#### 20.3 DAC Voltage Reference Output

The DAC voltage can be output to the DACxOUT1 and DACxOUT2 pins by setting the respective DACxOE1 and DACxOE2 pins of the DACxCON0 register. Selecting the DAC reference voltage for output on either DACxOUTx pin automatically overrides the digital output buffer and digital input threshold detector functions of that pin. Reading the DACxOUTx pin when it has been configured for DAC reference voltage output will always return a '0'.

Due to the limited current drive capability, a buffer must be used on the DAC voltage reference output for external connections to either DACxOUTx pin. Figure 20-2 shows an example buffering technique.

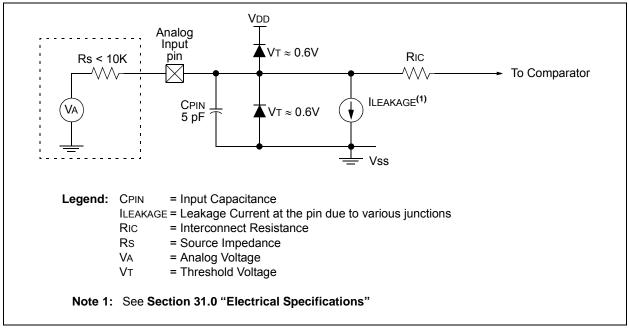

#### 21.10 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 21-4. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

- Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

- 2: Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

#### 21.10.1 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function register APFCON. To determine which pins can be moved and what their default locations are upon a Reset, see **Section 13.1 "Alternate Pin Function**" for more information.

#### FIGURE 21-4: ANALOG INPUT MODEL

#### 26.5.3 COMPLEMENTARY PWM STEERING

In Complementary PWM Steering mode, the primary PWM signal (non-complementary) and complementary signal can be steered according to their respective type.

Primary PWM signal can be steered to any of the following outputs:

- PSMCxA

- PSMCxC

- PSMCxE

The complementary PWM signal can be steered to any of the following outputs:

- PSMCxB

- PSMCxD

- PSMCxE

Examples of unsynchronized complementary steering are shown in Figure 26-17.

## FIGURE 26-17: COMPLEMENTARY PWM STEERING WAVEFORM (NO SYNCHRONIZATION, ZERO DEAD-BAND TIME)

| Base_PWM_signal |                                                                                                                    |

|-----------------|--------------------------------------------------------------------------------------------------------------------|

| PxSTRA          |                                                                                                                    |

| PSMCxA          |                                                                                                                    |

| PSMCxB          |                                                                                                                    |

| PxSTRB          | Arrows indicate where a change in the steering bit automatically forces a change in the corresponding PSMC output. |

| PxSTRC          |                                                                                                                    |

| PSMCxC          |                                                                                                                    |

| PSMCxD          |                                                                                                                    |

| PxSTRD          |                                                                                                                    |

| PxSTRE          |                                                                                                                    |

| PSMCxE          |                                                                                                                    |

| PSMCxF          |                                                                                                                    |

| PxSTRF          |                                                                                                                    |

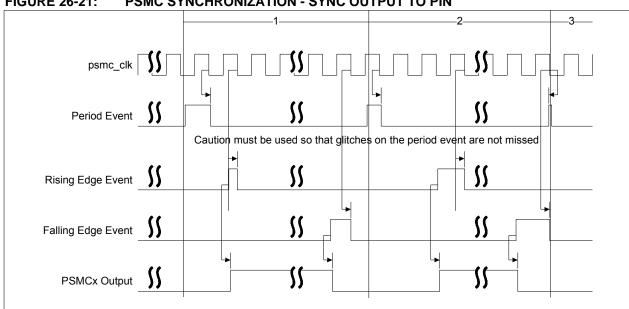

#### 26.8 **PSMC Synchronization**

It is possible to synchronize the periods of two or more PSMC modules together, provided that all modules are on the same device.

Synchronization is achieved by sending a sync signal from the master PSMC module to the desired slave modules. This sync signal generates a period event in each slave module, thereby aligning all slaves with the master. This is useful when an application requires different PWM signal generation from each module but the waveforms must be consistent within a PWM period.

#### SYNCHRONIZATION SOURCES 26.8.1

The synchronization source can be any PSMC module on the same device. For example, in a device with two PSMC modules, the possible sources for each device is as shown below:

- Sources for PSMC1

- PSMC2

- Sources for PSMC2

- PSMC1

#### **FIGURE 26-21: PSMC SYNCHRONIZATION - SYNC OUTPUT TO PIN**

#### 26.8.1.1 **PSMC Internal Connections**

The sync signal from the master PSMC module is essentially that modules period event trigger. The slave PSMC modules reset their PSMCxTMR with the sync signal instead of their own period event.

Enabling a module as a slave recipient is done with the PxSYNC bits of the PSMC Synchronization Control (PSMCxSYNC) registers; registers 26-3 and 26-4.

#### 26.8.1.2 Phase Offset Synchronization

The synchronization output signal from the PSMC module is selectable. The sync\_out source may be either:

- Period Event

- Rising Event

Source selection is made with the PxPOFST bit of the PSMCxSYNC registers, registers 26-3, 26-4 and 26-7.

When the PxPOFST bit is set, the sync out signal comes from the rising event and the period event replaces the rising event as the start of the active drive period. When PxPOFST is set, duty cycles of up to 100% are achievable in both the slave and master.

When PXPOFST is clear, the sync\_out signal comes from the period event. When PxPOFST is clear, rising events that start after the period event remove the equivalent start delay percentage from the maximum 100% duty cycle.

#### 26.8.1.3 Synchronization Skid

When the sync\_out source is the Period Event, the slave synchronous rising and falling events will lag by one psmc clk period. When the sync out source is the Rising Event, the synchronous events will lag by two clock periods. To compensate for this, the values in PHH:PHL and DCH:DCL registers can be reduced by the number of lag cycles.

### 26.12 Register Definitions: PSMC Control

#### REGISTER 26-1: PSMCxCON: PSMC CONTROL REGISTER

| R/W-0/0              | R/W/HC-0/0                                                                                                                | R/W-0/0            | R/W-0/0        | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------|----------------|----------------|------------------|------------------|--------------|--|

| PSMCxEN              | PSMCxLD                                                                                                                   | PxDBFE             | PxDBRE         | PxMODE<3:0>    |                  |                  |              |  |

| bit 7                |                                                                                                                           |                    |                |                |                  |                  | bit C        |  |

|                      |                                                                                                                           |                    |                |                |                  |                  |              |  |

| Legend:              |                                                                                                                           |                    |                |                |                  |                  |              |  |

| R = Readable bit     |                                                                                                                           | W = Writable bit   |                | •              | nented bit, read |                  |              |  |

| u = Bit is unchanged |                                                                                                                           | x = Bit is unknown |                | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |  |

| '1' = Bit is set     |                                                                                                                           | '0' = Bit is cle   | ared           |                |                  |                  |              |  |

| bit 7                |                                                                                                                           | SMC Module I       | -nable bit     |                |                  |                  |              |  |

|                      |                                                                                                                           | module is enal     |                |                |                  |                  |              |  |

|                      |                                                                                                                           | module is disa     |                |                |                  |                  |              |  |

| bit 6                | PSMCxLD: P                                                                                                                | SMC Load But       | fer Enable bit |                |                  |                  |              |  |

|                      | 1 = PSMCx registers are ready to be updated with the appropriate register contents                                        |                    |                |                |                  |                  |              |  |

|                      | 0 = PSMCx buffer update complete                                                                                          |                    |                |                |                  |                  |              |  |

| bit 5                |                                                                                                                           | MC Falling Edg     |                |                |                  |                  |              |  |

|                      | 1 = PSMCx falling edge dead band enabled                                                                                  |                    |                |                |                  |                  |              |  |

|                      | 0 = PSMCx falling edge dead band disabled                                                                                 |                    |                |                |                  |                  |              |  |

| bit 4                | PxDBRE: PSMC Rising Edge Dead-Band Enable bit                                                                             |                    |                |                |                  |                  |              |  |

|                      | <ul> <li>1 = PSMCx rising edge dead band enabled</li> <li>0 = PSMCx rising edge dead band disabled</li> </ul>             |                    |                |                |                  |                  |              |  |

| bit 3-0              |                                                                                                                           | > PSMC Oper        |                |                |                  |                  |              |  |

|                      | 1111 = Rese                                                                                                               | -                  | <b>J</b>       |                |                  |                  |              |  |

|                      | 1110 = Rese                                                                                                               |                    |                |                |                  |                  |              |  |

|                      | 1101 = Rese                                                                                                               |                    | A / N A        |                |                  |                  |              |  |

|                      | 1100 = 3-phase steering PWM<br>1011 = Fixed duty cycle, variable frequency, complementary PWM                             |                    |                |                |                  |                  |              |  |

|                      | 1011 = Fixed duty cycle, variable frequency, complementary PWM<br>1010 = Fixed duty cycle, variable frequency, single PWM |                    |                |                |                  |                  |              |  |

|                      | 1001 = ECCP compatible Full-Bridge forward output                                                                         |                    |                |                |                  |                  |              |  |

|                      | 1000 = ECCP compatible Full-Bridge reverse output                                                                         |                    |                |                |                  |                  |              |  |

|                      | 0111 = Pulse-skipping with complementary output<br>0110 = Pulse-skipping PWM output                                       |                    |                |                |                  |                  |              |  |

|                      | 0110 = Pulse-skipping PVVM output<br>0101 = Push-pull with four full-bridge outputs and complementary outputs             |                    |                |                |                  |                  |              |  |

|                      | 0100 = Push-pull with four full-bridge outputs                                                                            |                    |                |                |                  |                  |              |  |

|                      | 0011 = Push                                                                                                               | n-pull with com    |                |                |                  |                  |              |  |

|                      | 0010 = Push                                                                                                               |                    |                |                | \^/\             |                  |              |  |

|                      | 0001 = Singl0000 = Singl                                                                                                  |                    |                |                | WM steering ca   |                  |              |  |

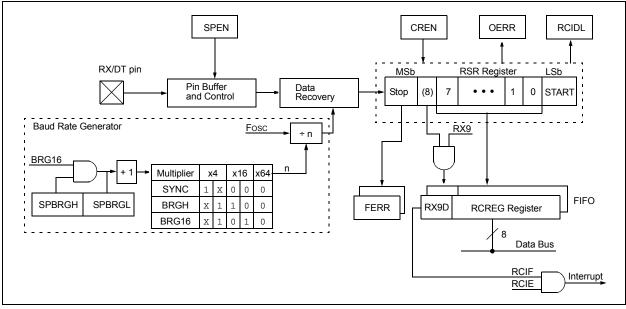

#### FIGURE 28-2: EUSART RECEIVE BLOCK DIAGRAM

The operation of the EUSART module is controlled through three registers:

- Transmit Status and Control (TXSTA)

- Receive Status and Control (RCSTA)

- Baud Rate Control (BAUDCON)

These registers are detailed in Register 28-1, Register 28-2 and Register 28-3, respectively.

When the receiver or transmitter section is not enabled then the corresponding RX or TX pin may be used for general purpose input and output.

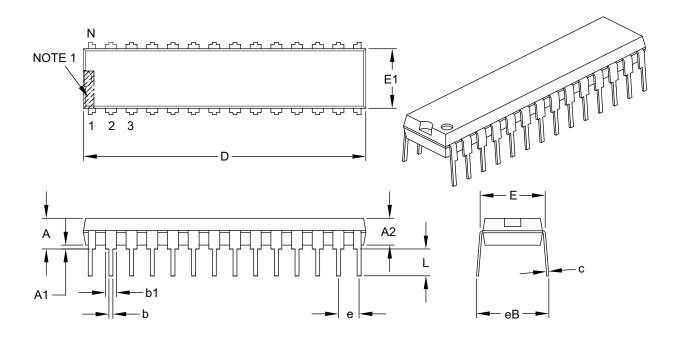

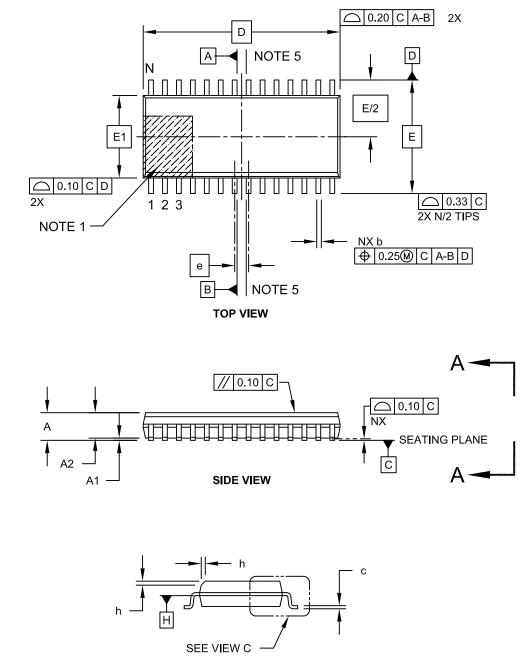

#### 34.2 Package Details

The following sections give the technical details of the packages.

#### 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units            |       | INCHES |       |

|----------------------------|------------------|-------|--------|-------|

|                            | Dimension Limits | MIN   | NOM    | MAX   |

| Number of Pins             | N                |       | 28     | •     |

| Pitch                      | e .100 BSC       |       |        |       |

| Top to Seating Plane       | А                | -     | -      | .200  |

| Molded Package Thickness   | A2               | .120  | .135   | .150  |

| Base to Seating Plane      | A1               | .015  | -      | -     |

| Shoulder to Shoulder Width | E                | .290  | .310   | .335  |

| Molded Package Width       | E1               | .240  | .285   | .295  |

| Overall Length             | D                | 1.345 | 1.365  | 1.400 |

| Tip to Seating Plane       | L                | .110  | .130   | .150  |

| Lead Thickness             | С                | .008  | .010   | .015  |

| Upper Lead Width           | b1               | .040  | .050   | .070  |

| Lower Lead Width           | b                | .014  | .018   | .022  |

| Overall Row Spacing §      |                  | -     | -      | .430  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B

#### 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-052C Sheet 1 of 2

## THE MICROCHIP WEBSITE

Microchip provides online support via our website site at www.microchip.com. This website is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the website contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip website at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- · Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the website at: http://microchip.com/support