Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | AVR                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 16MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 32                                                                        |

| Program Memory Size        | 8KB (4K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 512 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-LCC (J-Lead)                                                           |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega8535-16ju |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

value into the EEPROM. The EEMWE bit must be written to one before a logical one is written to EEWE, otherwise no EEPROM write takes place. The following procedure should be followed when writing the EEPROM (the order of steps 3 and 4 is not essential):

- 1. Wait until EEWE becomes zero.

- 2. Wait until SPMEN in SPMCR becomes zero.

- 3. Write new EEPROM address to EEAR (optional).

- 4. Write new EEPROM data to EEDR (optional).

- 5. Write a logical one to the EEMWE bit while writing a zero to EEWE in EECR.

- 6. Within four clock cycles after setting EEMWE, write a logical one to EEWE.

The EEPROM can not be programmed during a CPU write to the Flash memory. The software must check that the Flash programming is completed before initiating a new EEPROM write. Step 2 is only relevant if the software contains a Boot Loader allowing the CPU to program the Flash. If the Flash is never updated by the CPU, step 2 can be omitted. See "Boot Loader Support – Read-While-Write Self-Programming" on page 224 for details about Boot programming.

**Caution:** An interrupt between step 5 and step 6 will make the write cycle fail, since the EEPROM Master Write Enable will time-out. If an interrupt routine accessing the EEPROM is interrupting another EEPROM access, the EEAR or EEDR Register will be modified, causing the interrupted EEPROM access to fail. It is recommended to have the Global Interrupt Flag cleared during all the steps to avoid these problems.

When the write access time has elapsed, the EEWE bit is cleared by hardware. The user software can poll this bit and wait for a zero before writing the next byte. When EEWE has been set, the CPU is halted for two cycles before the next instruction is executed.

#### • Bit 0 – EERE: EEPROM Read Enable

The EEPROM Read Enable Signal EERE is the read strobe to the EEPROM. When the correct address is set up in the EEAR Register, the EERE bit must be written to a logic one to trigger the EEPROM read. The EEPROM read access takes one instruction, and the requested data is available immediately. When the EEPROM is read, the CPU is halted for four cycles before the next instruction is executed.

The user should poll the EEWE bit before starting the read operation. If a write operation is in progress, it is neither possible to read the EEPROM, nor to change the EEAR Register.

The calibrated Oscillator is used to time the EEPROM accesses. Table 1 lists the typical programming time for EEPROM access from the CPU.

| Table 1. | EEPROM | Programming | Time |

|----------|--------|-------------|------|

|----------|--------|-------------|------|

| Symbol                  | Number of Calibrated<br>RC Oscillator Cycles <sup>(1)</sup> | Typ<br>Programming Time |  |  |

|-------------------------|-------------------------------------------------------------|-------------------------|--|--|

| EEPROM Write (from CPU) | 8448                                                        | 8.4 ms                  |  |  |

Note: 1. Uses 1 MHz clock, independent of CKSEL Fuse settings.

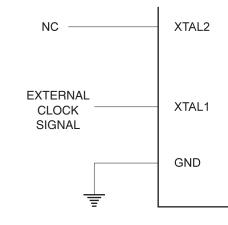

# **External Clock**

To drive the device from an external clock source, XTAL1 should be driven as shown in Figure 14. To run the device on an external clock, the CKSEL Fuses must be programmed to "0000". By programming the CKOPT Fuse, the user can enable an internal 36 pF capacitor between XTAL1 and GND.

### Figure 14. External Clock Drive Configuration

When this clock source is selected, start-up times are determined by the SUT Fuses as shown in Table 12.

| Table 12. Start-up Times for the External Clock Sele | ection |

|------------------------------------------------------|--------|

|------------------------------------------------------|--------|

| SUT10 | Start-up Time from Power-<br>down and Power-save | Additional Delay from<br>Reset (V <sub>CC</sub> = 5.0V) | Recommended Usage   |  |  |  |

|-------|--------------------------------------------------|---------------------------------------------------------|---------------------|--|--|--|

| 00    | 6 CK                                             | _                                                       | BOD enabled         |  |  |  |

| 01    | 6 CK                                             | 4.1 ms                                                  | Fast rising power   |  |  |  |

| 10    | 6 CK                                             | 65 ms                                                   | Slowly rising power |  |  |  |

| 11    | Reserved                                         |                                                         |                     |  |  |  |

When applying an external clock, it is required to avoid sudden changes in the applied clock frequency to ensure stable operation of the MCU. A variation in frequency of more than 2% from one clock cycle to the next can lead to unpredictable behavior. It is required to ensure that the MCU is kept in Reset during such changes in the clock frequency.

# **Timer/Counter Oscillator** For AVR microcontrollers with Timer/Counter Oscillator pins (TOSC1 and TOSC2), the crystal is connected directly between the pins. No external capacitors are needed. The Oscillator is optimized for use with a 32.768 kHz watch crystal. Applying an external clock source to TOSC1 is not recommended.

0b01) or output low ({DDxn, PORTxn} = 0b10) must occur. Normally, the pull-up enabled state is fully acceptable, as a high-impedant environment will not notice the difference between a strong high driver and a pull-up. If this is not the case, the PUD bit in the SFIOR Register can be set to disable all pull-ups in all ports.

Switching between input with pull-up and output low generates the same problem. The user must use either the tri-state ( $\{DDxn, PORTxn\} = 0b00$ ) or the output high state ( $\{DDxn, PORTxn\} = 0b10$ ) as an intermediate step.

Table 21 summarizes the control signals for the pin value.

| DDxn | PORTxn | PUD<br>(in SFIOR) | I/O    | Pull-up | Comment                                     |

|------|--------|-------------------|--------|---------|---------------------------------------------|

| 0    | 0      | Х                 | Input  | No      | Tri-state (Hi-Z)                            |

| 0    | 1      | 0                 | Input  | Yes     | Pxn will source current if ext. pulled low. |

| 0    | 1      | 1                 | Input  | No      | Tri-state (Hi-Z)                            |

| 1    | 0      | Х                 | Output | No      | Output Low (Sink)                           |

| 1    | 1      | Х                 | Output | No      | Output High (Source)                        |

Table 21. Port Pin Configurations

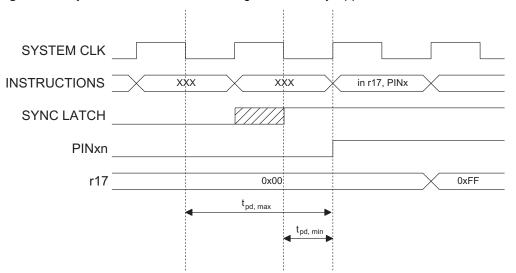

**Reading the Pin Value** Independent of the setting of Data Direction bit DDxn, the port pin can be read through the PINxn Register bit. As shown in Figure 23, the PINxn Register bit and the preceding latch constitute a synchronizer. This is needed to avoid metastability if the physical pin changes value near the edge of the internal clock, but it also introduces a delay. Figure 24 shows a timing diagram of the synchronization when reading an externally applied pin value. The maximum and minimum propagation delays are denoted t<sub>pd,max</sub> and t<sub>pd,min</sub> respectively.

Consider the clock period starting shortly *after* the first falling edge of the system clock. The latch is closed when the clock is low, and goes transparent when the clock is high, as indicated by the shaded region of the "SYNC LATCH" signal. The signal value is latched when the system clock goes low. It is clocked into the PINxn Register at the suc-

(DDD5 set (one)) to serve this function. The OC1A pin is also the output pin for the PWM mode timer function.

• OC1B – Port D, Bit 4

OC1B, Output Compare Match B output: The PD4 pin can serve as an external output for the Timer/Counter1 Output Compare B. The pin has to be configured as an output (DDD4 set (one)) to serve this function. The OC1B pin is also the output pin for the PWM mode timer function.

• INT1 – Port D, Bit 3

INT1, External Interrupt Source 1: The PD3 pin can serve as an external interrupt source.

• INT0 – Port D, Bit 2

INTO, External Interrupt Source 0: The PD2 pin can serve as an external interrupt source.

• TXD – Port D, Bit 1

TXD, Transmit Data (Data output pin for the USART). When the USART Transmitter is enabled, this pin is configured as an output regardless of the value of DDD1.

• RXD – Port D, Bit 0

RXD, Receive Data (Data input pin for the USART). When the USART Receiver is enabled this pin is configured as an input regardless of the value of DDD0. When the USART forces this pin to be an input, the pull-up can still be controlled by the PORTD0 bit.

Table 33 and Table 34 relate the alternate functions of Port D to the overriding signals shown in Figure 26 on page 57.

| Signal Name | PD7/OC2    | PD6/ICP1   | PD5/OC1A    | PD4/OC1B    |

|-------------|------------|------------|-------------|-------------|

| PUOE        | 0          | 0          | 0           | 0           |

| PUOV        | 0          | 0          | 0           | 0           |

| DDOE        | 0          | 0          | 0           | 0           |

| DDOV        | 0          | 0          | 0           | 0           |

| PVOE        | OC2 ENABLE | 0          | OC1A ENABLE | OC1B ENABLE |

| PVOV        | OC2        | 0          | OC1A        | OC1B        |

| DIEOE       | 0          | 0          | 0           | 0           |

| DIEOV       | 0          | 0          | 0           | 0           |

| DI          | -          | ICP1 INPUT | -           | -           |

| AIO         | -          | -          | -           | -           |

**Table 33.** Overriding Signals for Alternate Functions PD7..PD4

Signalize that TCNT0 has reached maximum value.

top

**bottom** Signalize that TCNT0 has reached minimum value (zero).

Depending of the mode of operation used, the counter is cleared, incremented, or decremented at each timer clock ( $clk_{T0}$ ).  $clk_{T0}$  can be generated from an external or internal clock source, selected by the Clock Select bits (CS02:0). When no clock source is selected (CS02:0 = 0) the timer is stopped. However, the TCNT0 value can be accessed by the CPU, regardless of whether  $clk_{T0}$  is present or not. A CPU write overrides (has priority over) all counter clear or count operations.

The counting sequence is determined by the setting of the WGM01 and WGM00 bits located in the Timer/Counter Control Register (TCCR0). There are close connections between how the counter behaves (counts) and how waveforms are generated on the output compare output OC0. For more details about advanced counting sequences and waveform generation, see "Modes of Operation" on page 76.

The Timer/Counter Overflow Flag (TOV0) is set according to the mode of operation selected by the WGM01:0 bits. TOV0 can be used for generating a CPU interrupt.

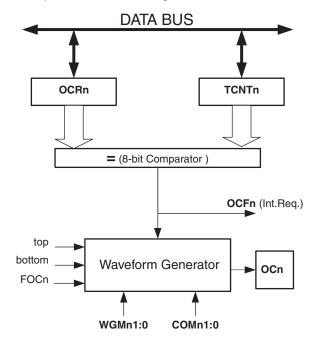

**Output Compare Unit** The 8-bit comparator continuously compares TCNT0 with the Output Compare Register (OCR0). Whenever TCNT0 equals OCR0, the comparator signals a match. A match will set the Output Compare Flag (OCF0) at the next timer clock cycle. If enabled (OCIE0 = 1 and Global Interrupt Flag in SREG is set), the Output Compare Flag generates an output compare interrupt. The OCF0 Flag is automatically cleared when the interrupt is executed. Alternatively, the OCF0 Flag can be cleared by software by writing a logical one to its I/O bit location. The Waveform Generator uses the match signal to generate an output according to operating mode set by the WGM01:0 bits and Compare Output mode (COM01:0) bits. The max and bottom signals are used by the Waveform Generator for handling the special cases of the extreme values in some modes of operation (See "Modes of Operation" on page 76.).

Figure 29 shows a block diagram of the output compare unit.

Figure 29. Output Compare Unit, Block Diagram

|                                       | The OCR0 Register is double buffered when using any of the Pulse Width Modulation (PWM) modes. For the normal and Clear Timer on Compare (CTC) modes of operation, the double buffering is disabled. The double buffering synchronizes the update of the OCR0 Compare Register to either top or bottom of the counting sequence. The synchronization prevents the occurrence of odd-length, non-symmetrical PWM pulses, thereby making the output glitch-free.                         |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                       | The OCR0 Register access may seem complex, but this is not the case. When the dou-<br>ble buffering is enabled, the CPU has access to the OCR0 Buffer Register, and if double<br>buffering is disabled the CPU will access the OCR0 directly.                                                                                                                                                                                                                                          |

| Force Output Compare                  | In non-PWM waveform generation modes, the match output of the comparator can be forced by writing a one to the Force Output Compare (FOC0) bit. Forcing Compare Match will not set the OCF0 Flag or reload/clear the timer, but the OC0 pin will be updated as if a real Compare Match had occurred (the COM01:0 bits settings define whether the OC0 pin is set, cleared or toggled).                                                                                                 |

| Compare Match Blocking by TCNT0 Write | All CPU write operations to the TCNT0 Register will block any Compare Match that occur in the next timer clock cycle, even when the timer is stopped. This feature allows OCR0 to be initialized to the same value as TCNT0 without triggering an interrupt when the Timer/Counter clock is enabled.                                                                                                                                                                                   |

| Using the Output Compare<br>Unit      | Since writing TCNT0 in any mode of operation will block all compare matches for one timer clock cycle, there are risks involved when changing TCNT0 when using the output compare channel, independently of whether the Timer/Counter is running or not. If the value written to TCNT0 equals the OCR0 value, the Compare Match will be missed, resulting in incorrect waveform generation. Similarly, do not write the TCNT0 value equal to BOTTOM when the counter is down-counting. |

|                                       | The setup of the OC0 should be performed before setting the Data Direction Register for the port pin to output. The easiest way of setting the OC0 value is to use the force output compare (FOC0) strobe bits in normal mode. The OC0 Register keeps its value even when changing between Waveform Generation modes.                                                                                                                                                                  |

|                                       | Be aware that the COM01:0 bits are not double buffered together with the compare value. Changing the COM01:0 bits will take effect immediately.                                                                                                                                                                                                                                                                                                                                        |

AMEL

when the counter is running with none or a low prescaler value must be done with care since the CTC mode does not have the double buffering feature. If the new value written to OCR0 is lower than the current value of TCNT0, the counter will miss the Compare Match. The counter will then have to count to its maximum value (0xFF) and wrap around starting at 0x00 before the Compare Match can occur.

For generating a waveform output in CTC mode, the OC0 output can be set to toggle its logical level on each Compare Match by setting the Compare Output mode bits to toggle mode (COM01:0 = 1). The OC0 value will not be visible on the port pin unless the data direction for the pin is set to output. The waveform generated will have a maximum frequency of  $f_{OC0} = f_{clk_l/O}/2$  when OCR0 is set to zero (0x00). The waveform frequency is defined by the following equation:

$$f_{OCn} = \frac{f_{clk\_l/O}}{2 \cdot N \cdot (1 + OCRn)}$$

The "N" variable represents the prescale factor (1, 8, 64, 256, or 1024).

As for the normal mode of operation, the TOV0 Flag is set in the same timer clock cycle that the counter counts from MAX to 0x00.

Fast PWM ModeThe fast Pulse Width Modulation or fast PWM mode (WGM01:0 = 3) provides a high frequency PWM waveform generation option. The fast PWM differs from the other PWM option by its single-slope operation. The counter counts from BOTTOM to MAX then restarts from BOTTOM. In non-inverting Compare Output mode, the Output Compare (OC0) is cleared on the Compare Match between TCNT0 and OCR0, and set at BOTTOM. In inverting Compare Output mode, the output is set on Compare Match and cleared at BOTTOM. Due to the single-slope operation, the operating frequency of the fast PWM mode can be twice as high as the phase correct PWM mode that use dual-slope operation. This high frequency makes the fast PWM mode well suited for power regulation, rectification, and DAC applications. High frequency allows physically small sized external components (coils, capacitors), and therefore reduces total system cost.

In fast PWM mode, the counter is incremented until the counter value matches the MAX value. The counter is then cleared at the following timer clock cycle. The timing diagram for the fast PWM mode is shown in Figure 32. The TCNT0 value is in the timing diagram shown as a histogram for illustrating the single-slope operation. The diagram includes non-inverted and inverted PWM outputs. The small horizontal line marks on the TCNT0 slopes represent compare matches between OCR0 and TCNT0.

measuring frequency only, the clearing of the ICF1 Flag is not required (if an interrupt handler is used).

# **Output Compare Units**

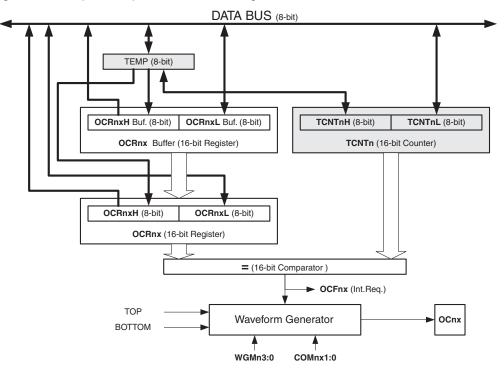

The 16-bit comparator continuously compares TCNT1 with the *Output Compare Register* (OCR1x). If TCNT equals OCR1x the comparator signals a match. A match will set the *Output Compare Flag* (OCF1x) at the next timer clock cycle. If enabled (OCIE1x = 1), the Output Compare Flag generates an output compare interrupt. The OCF1x Flag is automatically cleared when the interrupt is executed. Alternatively the OCF1x Flag can be cleared by software by writing a logical one to its I/O bit location. The Waveform Generator uses the match signal to generate an output according to operating mode set by the *Waveform Generation mode* (WGM13:0) bits and *Compare Output mode* (COM1x1:0) bits. The TOP and BOTTOM signals are used by the Waveform Generator for handling the special cases of the extreme values in some modes of operation. (See "Modes of Operation" on page 101.)

A special feature of output compare unit A allows it to define the Timer/Counter TOP value (i.e., counter resolution). In addition to the counter resolution, the TOP value defines the period time for waveforms generated by the Waveform Generator.

Figure 43 shows a block diagram of the output compare unit. The small "n" in the register and bit names indicates the device number (n = 1 for Timer/Counter1), and the "x" indicates output compare unit (A/B). The elements of the block diagram that are not directly a part of the output compare unit are gray shaded.

Figure 43. Output Compare Unit, Block Diagram

The OCR1x Register is double buffered when using any of the twelve *Pulse Width Modulation* (PWM) modes. For the Normal and *Clear Timer on Compare* (CTC) modes of operation, the double buffering is disabled. The double buffering synchronizes the update of the OCR1x Compare Register to either TOP or BOTTOM of the counting

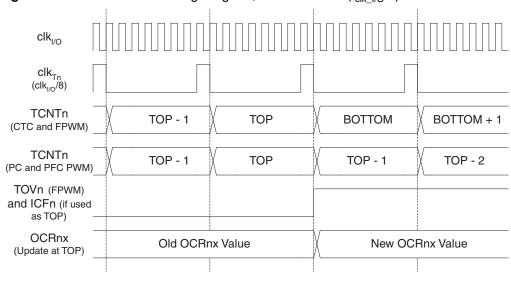

Figure 52. Timer/Counter Timing Diagram, with Prescaler (f<sub>clk I/O</sub>/8)

# 16-bit Timer/Counter Register Description

Timer/Counter1 Control Register A – TCCR1A

| Bit           | 7      | 6      | 5      | 4      | 3     | 2     | 1     | 0     |        |

|---------------|--------|--------|--------|--------|-------|-------|-------|-------|--------|

|               | COM1A1 | COM1A0 | COM1B1 | COM1B0 | FOC1A | FOC1B | WGM11 | WGM10 | TCCR1A |

| Read/Write    | R/W    | R/W    | R/W    | R/W    | W     | W     | R/W   | R/W   |        |

| Initial Value | 0      | 0      | 0      | 0      | 0     | 0     | 0     | 0     |        |

• Bit 7:6 – COM1A1:0: Compare Output Mode for Channel A

## • Bit 5:4 – COM1B1:0: Compare Output Mode for Channel B

The COM1A1:0 and COM1B1:0 control the Output Compare pins (OC1A and OC1B respectively) behavior. If one or both of the COM1A1:0 bits are written to one, the OC1A output overrides the normal port functionality of the I/O pin it is connected to. If one or both of the COM1B1:0 bit are written to one, the OC1B output overrides the normal port functionality of the I/O pin it is connected to. However, note that the *Data Direction Register* (DDR) bit corresponding to the OC1A or OC1B pin must be set in order to enable the output driver.

When the OC1A or OC1B is connected to the pin, the function of the COM1x1:0 bits is dependent of the WGM13:0 bits setting. Table 45 shows the COM1x1:0 bit functionality when the WGM13:0 bits are set to a normal or a CTC mode (non-PWM).

| COM1A1/<br>COM1B1 | COM1A0/<br>COM1B0 | Description                                                 |

|-------------------|-------------------|-------------------------------------------------------------|

| 0                 | 0                 | Normal port operation, OC1A/OC1B disconnected.              |

| 0                 | 1                 | Toggle OC1A/OC1B on Compare Match.                          |

| 1                 | 0                 | Clear OC1A/OC1B on Compare Match (set output to low level). |

| 1                 | 1                 | Set OC1A/OC1B on Compare Match (set output to high level).  |

Table 45. Compare Output Mode, non-PWM

A change of the COM21:0 bits state will take effect at the first Compare Match after the bits are written. For non-PWM modes, the action can be forced to have an immediate effect by using the FOC2 strobe bits.

**Modes of Operation** The mode of operation (i.e., the behavior of the Timer/Counter and the Output Compare pins) is defined by the combination of the Waveform Generation mode (WGM21:0) and Compare Output mode (COM21:0) bits. The Compare Output mode bits do not affect the counting sequence, while the Waveform Generation mode bits do. The COM21:0 bits control whether the PWM output generated should be inverted or not (inverted or non-inverted PWM). For non-PWM modes the COM21:0 bits control whether the output should be set, cleared, or toggled at a Compare Match (See "Compare Match Output Unit" on page 121.).

For detailed timing information refer to "Timer/Counter Timing Diagrams" on page 126.

Normal Mode The simplest mode of operation is the Normal mode (WGM21:0 = 0). In this mode the counting direction is always up (incrementing), and no counter clear is performed. The counter simply overruns when it passes its maximum 8-bit value (TOP = 0xFF) and then restarts from the bottom (0x00). In normal operation the Timer/Counter Overflow Flag (TOV2) will be set in the same timer clock cycle as the TCNT2 becomes zero. The TOV2 Flag in this case behaves like a ninth bit, except that it is only set, not cleared. However, combined with the timer overflow interrupt that automatically clears the TOV2 Flag, the timer resolution can be increased by software. There are no special cases to consider in the normal mode, a new counter value can be written anytime.

The output compare unit can be used to generate interrupts at some given time. Using the output compare to generate waveforms in Normal mode is not recommended, since this will occupy too much of the CPU time.

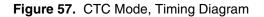

# Clear Timer on Compare Match (CTC) Mode

In Clear Timer on Compare or CTC mode (WGM21:0 = 2), the OCR2 Register is used to manipulate the counter resolution. In CTC mode, the counter is cleared to zero when the counter value (TCNT2) matches the OCR2. The OCR2 defines the top value for the counter, hence also its resolution. This mode allows greater control of the Compare Match output frequency. It also simplifies the operation of counting external events.

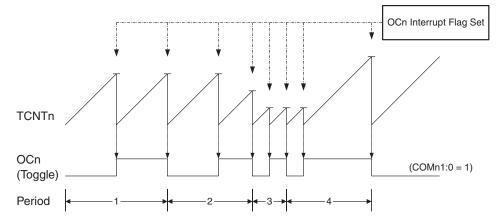

The timing diagram for the CTC mode is shown in Figure 57. The counter value (TCNT2) increases until a Compare Match occurs between TCNT2 and OCR2, and then counter (TCNT2) is cleared.

#### Timer/Counter Interrupt Flag Register – TIFR

| Bit           | 7    | 6    | 5    | 4     | 3     | 2    | 1    | 0    | _    |

|---------------|------|------|------|-------|-------|------|------|------|------|

|               | OCF2 | TOV2 | ICF1 | OCF1A | OCF1B | TOV1 | OCF0 | TOV0 | TIFR |

| Read/Write    | R/W  | R/W  | R/W  | R/W   | R/W   | R/W  | R/W  | R/W  | •    |

| Initial Value | 0    | 0    | 0    | 0     | 0     | 0    | 0    | 0    |      |

## Bit 7 – OCF2: Output Compare Flag 2

The OCF2 bit is set (one) when a Compare Match occurs between the Timer/Counter2 and the data in OCR2 – Output Compare Register 2. OCF2 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, OCF2 is cleared by writing a logic one to the flag. When the I-bit in SREG, OCIE2 (Timer/Counter2 Compare Match interrupt enable), and OCF2 are set (one), the Timer/Counter2 Compare Match Interrupt is executed.

## • Bit 6 – TOV2: Timer/Counter2 Overflow Flag

The TOV2 bit is set (one) when an overflow occurs in Timer/Counter2. TOV2 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, TOV2 is cleared by writing a logic one to the flag. When the SREG I-bit, TOIE2 (Timer/Counter2 Overflow Interrupt Enable), and TOV2 are set (one), the Timer/Counter2 Overflow interrupt is executed. In PWM mode, this bit is set when Timer/Counter2 changes counting direction at 0x00.

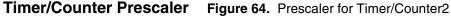

The clock source for Timer/Counter2 is named  $clk_{T2S}$ .  $clk_{T2S}$  is, by default, connected to the main system I/O clock  $clk_{IO}$ . By setting the AS2 bit in ASSR, Timer/Counter2 is asynchronously clocked from the TOSC1 pin. This enables use of Timer/Counter2 as a Real Time Counter (RTC). When AS2 is set, pins TOSC1 and TOSC2 are disconnected from Port C. A crystal can then be connected between the TOSC1 and TOSC2 pins to serve as an independent clock source for Timer/Counter2. The Oscillator is optimized for use with a 32.768 kHz crystal. Applying an external clock source to TOSC1 is not recommended.

For Timer/Counter2, the possible prescaled selections are:  $clk_{T2S}/8$ ,  $clk_{T2S}/32$ ,  $clk_{T2S}/64$ ,  $clk_{T2S}/128$ ,  $clk_{T2S}/256$ , and  $clk_{T2S}/1024$ . Additionally,  $clk_{T2S}$  as well as 0 (stop) may be selected. Setting the PSR2 bit in SFIOR resets the prescaler. This allows the user to operate with a predictable prescaler.

# 134 ATmega8535(L)

Note: 1. See "About Code Examples" on page 7.

The receive function example reads all the I/O Registers into the Register File before any computation is done. This gives an optimal receive buffer utilization since the buffer location read will be free to accept new data as early as possible.

**Receive Compete Flag and** The USART Receiver has one flag that indicates the receiver state.

The Receive Complete (RXC) Flag indicates if there are unread data present in the receive buffer. This flag is one when unread data exist in the receive buffer and zero when the receive buffer is empty (i.e., does not contain any unread data). If the Receiver is disabled (RXEN = 0), the receive buffer will be flushed and consequently the RXC bit will become zero.

When the Receive Complete Interrupt Enable (RXCIE) in UCSRB is set, the USART Receive Complete Interrupt will be executed as long as the RXC Flag is set (provided that global interrupts are enabled). When interrupt-driven data reception is used, the receive complete routine must read the received data from UDR in order to clear the RXC Flag, otherwise a new interrupt will occur once the interrupt routine terminates.

**Receiver Error Flags** The USART Receiver has three Error Flags: Frame Error (FE), Data OverRun (DOR) and Parity Error (PE). All can be accessed by reading UCSRA. Common for the error flags is that they are located in the receive buffer together with the frame for which they indicate the error status. Due to the buffering of the error flags, the UCSRA must be read before the receive buffer (UDR), since reading the UDR I/O location changes the buffer read location. Another equality for the error flags is that they can not be altered by software doing a write to the flag location. However, all flags must be set to zero when the UCSRA is written for upward compatibility of future USART implementations. None of the error flags can generate interrupts.

The Frame Error (FE) Flag indicates the state of the first stop bit of the next readable frame stored in the receive buffer. The FE Flag is zero when the stop bit was correctly read (as one), and the FE Flag will be one when the stop bit was incorrect (zero). This flag can be used for detecting out-of-sync conditions, detecting break conditions and protocol handling. The FE Flag is not affected by the setting of the USBS bit in UCSRC since the Receiver ignores all, except for the first, stop bits. For compatibility with future devices, always set this bit to zero when writing to UCSRA.

The Data OverRun (DOR) Flag indicates data loss due to a Receiver Buffer full condition. A Data OverRun occurs when the receive buffer is full (two characters), it is a new character waiting in the receive Shift Register, and a new start bit is detected. If the DOR Flag is set there was one or more serial frame lost between the frame last read from UDR, and the next frame read from UDR. For compatibility with future devices, always write this bit to zero when writing to UCSRA. The DOR Flag is cleared when the frame received was successfully moved from the Shift Register to the receive buffer.

The Parity Error (PE) Flag indicates that the next frame in the receive buffer had a Parity Error when received. If parity check is not enabled the PE bit will always be read zero. For compatibility with future devices, always set this bit to zero when writing to UCSRA. For more details see "Parity Bit Calculation" on page 150 and "Parity Checker" on page 157.

Parity CheckerThe Parity Checker is active when the high USART Parity mode (UPM1) bit is set. The<br/>type of Parity Check to be performed (odd or even) is selected by the UPM0 bit. When<br/>enabled, the Parity Checker calculates the parity of the data bits in incoming frames and<br/>compares the result with the parity bit from the serial frame. The result of the check is

Interrupt

| Table 62. | Recomme | ended Ma | ximum | Receive | er Baud | Rate E | Error for | Normal | Speed N | lode |

|-----------|---------|----------|-------|---------|---------|--------|-----------|--------|---------|------|

| (U2X = 0) |         |          |       |         |         |        |           |        |         |      |

|           |         |          |       |         |         |        |           |        |         |      |

| D<br># (Data+Parity Bit) | R <sub>slow</sub> (%) | R <sub>fast</sub> (%) | Max Total<br>Error (%) | Recommended Max<br>Receiver Error (%) |

|--------------------------|-----------------------|-----------------------|------------------------|---------------------------------------|

| 5                        | 93.20                 | 106.67                | +6.67/-6.8             | ± 3.0                                 |

| 6                        | 94.12                 | 105.79                | +5.79/-5.88            | ± 2.5                                 |

| 7                        | 94.81                 | 105.11                | +5.11 -5.19            | ± 2.0                                 |

| 8                        | 95.36                 | 104.58                | +4.58/-4.54            | ± 2.0                                 |

| 9                        | 95.81                 | 104.14                | +4.14/-4.19            | ± 1.5                                 |

| 10                       | 96.17                 | 103.78                | +3.78/-3.83            | ± 1.5                                 |

**Table 63.** Recommended Maximum Receiver Baud Rate Error for Double Speed Mode (U2X = 1)

| D<br># (Data+Parity Bit) | R <sub>slow</sub> (%) | R <sub>fast</sub> (%) | Max Total<br>Error (%) | Recommended Max<br>Receiver Error (%) |

|--------------------------|-----------------------|-----------------------|------------------------|---------------------------------------|

| 5                        | 94.12                 | 105.66                | +5.66/-5.88            | ± 2.5                                 |

| 6                        | 94.92                 | 104.92                | +4.92/-5.08            | ± 2.0                                 |

| 7                        | 95.52                 | 104.35                | +4.35/-4.48            | ± 1.5                                 |

| 8                        | 96.00                 | 103.90                | +3.90/-4.00            | ± 1.5                                 |

| 9                        | 96.39                 | 103.53                | +3.53/-3.61            | ± 1.5                                 |

| 10                       | 96.70                 | 103.23                | +3.23/-3.30            | ± 1.0                                 |

The recommendations of the maximum receiver baud rate error was made under the assumption that the Receiver and Transmitter equally divides the maximum total error.

There are two possible sources for the receivers baud rate error. The receiver's system clock (XTAL) will always have some minor instability over the supply voltage range and the temperature range. When using a crystal to generate the system clock, this is rarely a problem, but for a resonator the system clock may differ more than 2% depending of the resonators tolerance. The second source for the error is more controllable. The baud rate generator can not always do an exact division of the system frequency to get the baud rate wanted. In this case an UBRR value that gives an acceptable low error can be used if possible.

# ATmega8535(L)

# Accessing UBRRH/UCSRC Registers

Write Access

The UBRRH Register shares the same I/O location as the UCSRC Register. Therefore some special consideration must be taken when accessing this I/O location.

When doing a write access of this I/O location, the high bit of the value written, the USART Register Select (URSEL) bit, controls which one of the two registers that will be written. If URSEL is zero during a write operation, the UBRRH value will be updated. If URSEL is one, the UCSRC setting will be updated.

The following code examples show how to access the two registers.

Assembly Code Examples<sup>(1)</sup>

```

...

; Set UBRRH to 2

ldi r16,0x02

out UBRRH,r16

...

; Set the USBS and the UCSZ1 bit to one, and

; the remaining bits to zero.

Idi r16,(1<<URSEL)|(1<<USBS)|(1<<UCSZ1)

out UCSRC,r16

...

C Code Examples<sup>(1)</sup>

/* Set UBRRH to 2 */

UBRRH = 0x02;

...

/* Set the USBS and the UCSZ1 bit to one, and */

/* the remaining bits to zero. */

UCSRC = (1<<URSEL)|(1<<USBS)|(1<<UCSZ1);

...

```

Note: 1. See "About Code Examples" on page 7.

As the code examples illustrate, write accesses of the two registers are relatively unaffected of the sharing of I/O location.

|                    |      | f <sub>osc</sub> = 16. | 0000 MHz |              |       | f <sub>osc</sub> = 18. | 4320 MHz |       |      | f <sub>osc</sub> = 20. | 0000 MHz |              |

|--------------------|------|------------------------|----------|--------------|-------|------------------------|----------|-------|------|------------------------|----------|--------------|

| Baud<br>Rate       | U2)  | ζ = 0                  | U2)      | <b>(</b> = 1 | U2)   | <b>κ</b> = 0           | U2>      | ( = 1 | U2>  | ζ = 0                  | U2)      | <b>(</b> = 1 |

| (bps)              | UBRR | Error                  | UBRR     | Error        | UBRR  | Error                  | UBRR     | Error | UBRR | Error                  | UBRR     | Error        |

| 2400               | 416  | -0.1%                  | 832      | 0.0%         | 479   | 0.0%                   | 959      | 0.0%  | 520  | 0.0%                   | 1041     | 0.0%         |

| 4800               | 207  | 0.2%                   | 416      | -0.1%        | 239   | 0.0%                   | 479      | 0.0%  | 259  | 0.2%                   | 520      | 0.0%         |

| 9600               | 103  | 0.2%                   | 207      | 0.2%         | 119   | 0.0%                   | 239      | 0.0%  | 129  | 0.2%                   | 259      | 0.2%         |

| 14.4k              | 68   | 0.6%                   | 138      | -0.1%        | 79    | 0.0%                   | 159      | 0.0%  | 86   | -0.2%                  | 173      | -0.2%        |

| 19.2k              | 51   | 0.2%                   | 103      | 0.2%         | 59    | 0.0%                   | 119      | 0.0%  | 64   | 0.2%                   | 129      | 0.2%         |

| 28.8k              | 34   | -0.8%                  | 68       | 0.6%         | 39    | 0.0%                   | 79       | 0.0%  | 42   | 0.9%                   | 86       | -0.2%        |

| 38.4k              | 25   | 0.2%                   | 51       | 0.2%         | 29    | 0.0%                   | 59       | 0.0%  | 32   | -1.4%                  | 64       | 0.2%         |

| 57.6k              | 16   | 2.1%                   | 34       | -0.8%        | 19    | 0.0%                   | 39       | 0.0%  | 21   | -1.4%                  | 42       | 0.9%         |

| 76.8k              | 12   | 0.2%                   | 25       | 0.2%         | 14    | 0.0%                   | 29       | 0.0%  | 15   | 1.7%                   | 32       | -1.4%        |

| 115.2k             | 8    | -3.5%                  | 16       | 2.1%         | 9     | 0.0%                   | 19       | 0.0%  | 10   | -1.4%                  | 21       | -1.4%        |

| 230.4k             | 3    | 8.5%                   | 8        | -3.5%        | 4     | 0.0%                   | 9        | 0.0%  | 4    | 8.5%                   | 10       | -1.4%        |

| 250k               | 3    | 0.0%                   | 7        | 0.0%         | 4     | -7.8%                  | 8        | 2.4%  | 4    | 0.0%                   | 9        | 0.0%         |

| 0.5M               | 1    | 0.0%                   | 3        | 0.0%         | _     | _                      | 4        | -7.8% | _    | _                      | 4        | 0.0%         |

| 1M                 | 0    | 0.0%                   | 1        | 0.0%         | _     | _                      | _        | _     | _    | -                      | _        | -            |

| Max <sup>(1)</sup> | 1 N  | lbps                   | 2 N      | lbps         | 1.152 | Mbps                   | 2.304    | Mbps  | 1.25 | Mbps                   | 2.5      | Mbps         |

| Table 72. Examples of UBRR Settings for Commonly Used Oscillator Frequer | ncies (Continued) |

|--------------------------------------------------------------------------|-------------------|

|                                                                          |                   |

1. UBRR = 0, Error = 0.0%

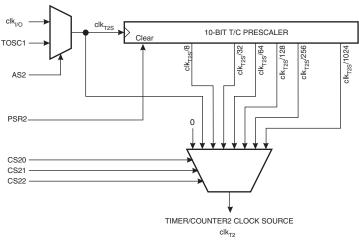

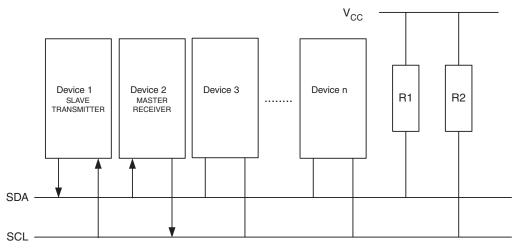

## **Slave Transmitter Mode**

In the Slave Transmitter mode, a number of data bytes are transmitted to a Master Receiver (see Figure 92). All the status codes mentioned in this section assume that the prescaler bits are zero or are masked to zero.

To initiate the Slave Transmitter mode, TWAR and TWCR must be initialized as follows:

| TWAR  | TWA6 | TWA5 | TWA4     | TWA3        | TWA2    | TWA1 | TWA0 | TWGCE |

|-------|------|------|----------|-------------|---------|------|------|-------|

| Value |      |      | Device's | s Own Slave | Address |      |      |       |

The upper seven bits are the address to which the Two-wire Serial Interface will respond when addressed by a Master. If the LSB is set, the TWI will respond to the general call address (0x00), otherwise it will ignore the general call address.

| TWCR  | TWINT | TWEA | TWSTA | TWSTO | TWWC | TWEN | - | TWIE |

|-------|-------|------|-------|-------|------|------|---|------|

| Value | 0     | 1    | 0     | 0     | 0    | 1    | 0 | Х    |

TWEN must be written to one to enable the TWI. The TWEA bit must be written to one to enable the acknowledgement of the device's own slave address or the general call address. TWSTA and TWSTO must be written to zero.

When TWAR and TWCR have been initialized, the TWI waits until it is addressed by its own slave address (or the general call address if enabled) followed by the data direction bit. If the direction bit is "1" (read), the TWI will operate in ST mode, otherwise SR mode is entered. After its own slave address and the write bit have been received, the TWINT Flag is set and a valid status code can be read from TWSR. The status code is used to determine the appropriate software action. The appropriate action to be taken for each status code is detailed in Table 78. The Slave Transmitter mode may also be entered if arbitration is lost while the TWI is in the Master mode (see state 0xB0).

If the TWEA bit is written to zero during a transfer, the TWI will transmit the last byte of the transfer. State 0xC0 or state 0xC8 will be entered, depending on whether the Master Receiver transmits a NACK or ACK after the final byte. The TWI is switched to the not addressed Slave mode, and will ignore the Master if it continues the transfer. Thus the Master Receiver receives all "1" as serial data. State 0xC8 is entered if the Master demands additional data bytes (by transmitting ACK), even though the Slave has transmitted the last byte (TWEA zero and expecting NACK from the Master).

While TWEA is zero, the TWI does not respond to its own slave address. However, the Two-wire Serial Bus is still monitored and address recognition may resume at any time

# <sup>198</sup> ATmega8535(L)

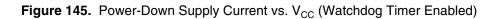

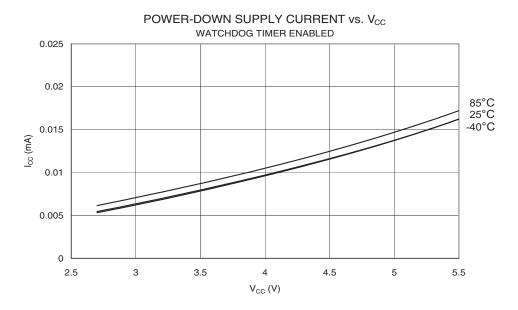

**Power-Save Supply Current**

Figure 146. Power-Save Supply Current vs.  $V_{CC}$  (Watchdog Timer Disabled)

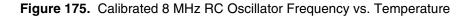

CALIBRATED 8 MHz RC OSCILLATOR FREQUENCY vs. TEMPERATURE

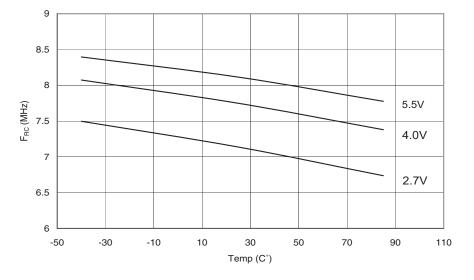

CALIBRATED 8 MHz RC OSCILLATOR FREQUENCY vs.  $V_{\rm CC}$

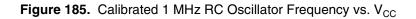

CALIBRATED 1 MHz RC OSCILLATOR FREQUENCY vs.  $V_{\text{CC}}$

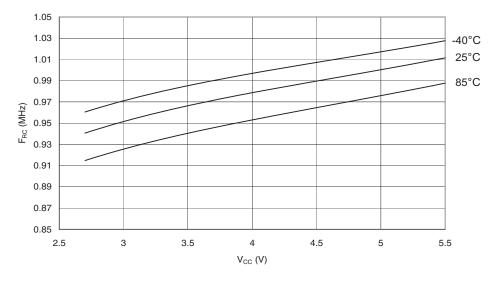

CALIBRATED 1 MHz RC OSCILLATOR FREQUENCY vs. OSCCAL VALUE

# ATmega8535(L)

| Features                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Configurations                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                          |

| Disclaimer                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                          |

| Overview                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                          |

| Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                          |

| AT90S8535 Compatibility                                                                                                                                                                                                                                                                                                                                                                                                       | 4                                                                                                                                                        |

| Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                              | 5                                                                                                                                                        |

| Resources                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                          |

| About Code Examples                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                          |

| AVR CPU Core                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                          |

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                          |

| Architectural Overview                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                          |

| ALU – Arithmetic Logic Unit                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                          |

| Status Register                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                          |

| General Purpose Register File                                                                                                                                                                                                                                                                                                                                                                                                 | 11                                                                                                                                                       |

| Stack Pointer                                                                                                                                                                                                                                                                                                                                                                                                                 | 12                                                                                                                                                       |

| Instruction Execution Timing                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                          |

| Reset and Interrupt Handling                                                                                                                                                                                                                                                                                                                                                                                                  | 13                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                          |

| AVR ATmega8535 Memories                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                          |

| AVR ATmega8535 Memories<br>In-System Reprogrammable Flash Program Memory                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                          |

| AVR ATmega8535 Memories<br>In-System Reprogrammable Flash Program Memory<br>SRAM Data Memory                                                                                                                                                                                                                                                                                                                                  | 16                                                                                                                                                       |

| In-System Reprogrammable Flash Program Memory                                                                                                                                                                                                                                                                                                                                                                                 | 16<br>17                                                                                                                                                 |

| In-System Reprogrammable Flash Program Memory<br>SRAM Data Memory                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                          |

| In-System Reprogrammable Flash Program Memory<br>SRAM Data Memory<br>EEPROM Data Memory<br>I/O Memory                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                          |

| In-System Reprogrammable Flash Program Memory<br>SRAM Data Memory<br>EEPROM Data Memory<br>I/O Memory                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                          |

| In-System Reprogrammable Flash Program Memory<br>SRAM Data Memory<br>EEPROM Data Memory<br>I/O Memory<br>System Clock and Clock Options<br>Clock Systems and their Distribution                                                                                                                                                                                                                                               | 16<br>17<br>18<br>23<br>                                                                                                                                 |

| In-System Reprogrammable Flash Program Memory<br>SRAM Data Memory<br>EEPROM Data Memory<br>I/O Memory<br>System Clock and Clock Options<br>Clock Systems and their Distribution<br>Clock Sources                                                                                                                                                                                                                              | 16<br>17<br>18<br>23<br>                                                                                                                                 |

| In-System Reprogrammable Flash Program Memory<br>SRAM Data Memory<br>EEPROM Data Memory<br>I/O Memory<br>Clock And Clock Options<br>Clock Systems and their Distribution<br>Clock Sources<br>Default Clock Source                                                                                                                                                                                                             | 16<br>17<br>18<br>23<br><b>24</b><br>24<br>25<br>25                                                                                                      |

| In-System Reprogrammable Flash Program Memory<br>SRAM Data Memory<br>EEPROM Data Memory<br>I/O Memory<br>Code Memory And Clock Options<br>Clock Systems and their Distribution<br>Clock Sources<br>Default Clock Source<br>Crystal Oscillator                                                                                                                                                                                 | 16<br>17<br>18<br>23<br>                                                                                                                                 |

| In-System Reprogrammable Flash Program Memory<br>SRAM Data Memory<br>EEPROM Data Memory<br>I/O Memory<br>Clock Systems and their Distribution<br>Clock Sources<br>Default Clock Source<br>Crystal Oscillator<br>Low-frequency Crystal Oscillator                                                                                                                                                                              | 16<br>17<br>18<br>23<br>23<br>24<br>24<br>25<br>25<br>25<br>25<br>25<br>28                                                                               |

| In-System Reprogrammable Flash Program Memory<br>SRAM Data Memory<br>EEPROM Data Memory<br>I/O Memory<br>Code Memory And Clock Options<br>Clock Systems and their Distribution<br>Clock Sources<br>Default Clock Source<br>Crystal Oscillator                                                                                                                                                                                 | 16<br>17<br>18<br>23<br>24<br>24<br>25<br>25<br>25<br>25<br>25<br>28<br>28                                                                               |

| In-System Reprogrammable Flash Program Memory<br>SRAM Data Memory<br>EEPROM Data Memory<br>I/O Memory<br>Code Memory<br>Clock Systems and their Distribution<br>Clock Sources<br>Default Clock Source<br>Crystal Oscillator<br>Low-frequency Crystal Oscillator<br>External RC Oscillator                                                                                                                                     | 16<br>17<br>18<br>23<br>24<br>24<br>25<br>25<br>25<br>25<br>25<br>25<br>25<br>25<br>25<br>25<br>25<br>25<br>25                                           |

| In-System Reprogrammable Flash Program Memory<br>SRAM Data Memory<br>EEPROM Data Memory<br>I/O Memory<br>Code Systems and their Distribution<br>Clock Systems and their Distribution<br>Clock Sources<br>Default Clock Source<br>Crystal Oscillator<br>Low-frequency Crystal Oscillator<br>External RC Oscillator<br>Calibrated Internal RC Oscillator                                                                        | 16<br>17<br>18<br>23<br>24<br>24<br>25<br>25<br>25<br>25<br>25<br>25<br>25<br>28<br>28<br>28<br>28<br>28<br>29<br>31                                     |

| In-System Reprogrammable Flash Program Memory<br>SRAM Data Memory<br>EEPROM Data Memory<br>I/O Memory<br>Codek Systems and their Distribution<br>Clock Systems and their Distribution<br>Clock Sources<br>Default Clock Source<br>Crystal Oscillator<br>Low-frequency Crystal Oscillator<br>External RC Oscillator<br>Calibrated Internal RC Oscillator<br>External Clock<br>Timer/Counter Oscillator                         | 16<br>17<br>18<br>23<br>24<br>24<br>25<br>25<br>25<br>25<br>25<br>25<br>25<br>25<br>25<br>25<br>25<br>25<br>25                                           |

| In-System Reprogrammable Flash Program Memory<br>SRAM Data Memory<br>EEPROM Data Memory<br>I/O Memory<br>Clock And Clock Options<br>Clock Systems and their Distribution<br>Clock Sources<br>Default Clock Source<br>Crystal Oscillator<br>Low-frequency Crystal Oscillator<br>External RC Oscillator<br>External RC Oscillator<br>External Clock<br>Timer/Counter Oscillator<br><b>Power Management and Sleep Modes</b>      | 16<br>17<br>18<br>23<br>24<br>24<br>25<br>25<br>25<br>25<br>25<br>25<br>28<br>28<br>28<br>28<br>28<br>29<br>31<br>31<br>31                               |

| In-System Reprogrammable Flash Program Memory<br>SRAM Data Memory<br>EEPROM Data Memory<br>I/O Memory<br>Codek Systems and their Distribution<br>Clock Systems and their Distribution<br>Clock Sources<br>Default Clock Source<br>Crystal Oscillator<br>Low-frequency Crystal Oscillator<br>External RC Oscillator<br>Calibrated Internal RC Oscillator<br>External Clock<br>Timer/Counter Oscillator                         | 16<br>17<br>18<br>23<br>24<br>24<br>25<br>25<br>25<br>25<br>25<br>25<br>28<br>28<br>28<br>29<br>31<br>31<br>31<br>31<br>31<br>33                         |

| In-System Reprogrammable Flash Program Memory<br>SRAM Data Memory<br>EEPROM Data Memory<br>I/O Memory<br>System Clock and Clock Options<br>Clock Systems and their Distribution<br>Clock Sources<br>Default Clock Source<br>Crystal Oscillator<br>Low-frequency Crystal Oscillator<br>External RC Oscillator<br>External RC Oscillator<br>External Clock<br>Timer/Counter Oscillator<br>Idle Mode                             | 16<br>17<br>18<br>23<br>24<br>24<br>25<br>25<br>25<br>25<br>25<br>25<br>28<br>28<br>28<br>28<br>29<br>31<br>31<br>31<br>31<br>31<br>31                   |

| In-System Reprogrammable Flash Program Memory<br>SRAM Data Memory<br>EEPROM Data Memory<br>I/O Memory<br>System Clock and Clock Options<br>Clock Systems and their Distribution<br>Clock Sources<br>Default Clock Source<br>Crystal Oscillator<br>Low-frequency Crystal Oscillator<br>External RC Oscillator<br>External RC Oscillator<br>External Clock<br>Timer/Counter Oscillator<br>Idle Mode<br>ADC Noise Reduction Mode | 16<br>17<br>18<br>23<br>24<br>24<br>25<br>25<br>25<br>25<br>25<br>25<br>28<br>28<br>28<br>29<br>31<br>31<br>31<br>31<br>31<br>31<br>31<br>33<br>33<br>33 |

**Table of Contents**