Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                             |

|----------------------------|-------------------------------------------------------------|

| Product Status             | Active                                                      |

| Core Processor             | AVR                                                         |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 16MHz                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                       |

| Number of I/O              | 32                                                          |

| Program Memory Size        | 8KB (4K x 16)                                               |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | 512 x 8                                                     |

| RAM Size                   | 512 x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                 |

| Data Converters            | A/D 8x10b                                                   |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 44-LCC (J-Lead)                                             |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/atmel/atmega8535-16jur |

Asynchronous Timer Clock – clk<sub>ASY</sub>

The Asynchronous Timer clock allows the Asynchronous Timer/Counter to be clocked directly from an external 32 kHz clock crystal. The dedicated clock domain allows using this Timer/Counter as a real-time counter even when the device is in sleep mode.

ADC Clock - clk<sub>ADC</sub>

The ADC is provided with a dedicated clock domain. This allows halting the CPU and I/O clocks in order to reduce noise generated by digital circuitry. This gives more accurate ADC conversion results.

#### **Clock Sources**

The device has the following clock source options, selectable by Flash Fuse bits as shown below. The clock from the selected source is input to the AVR clock generator, and routed to the appropriate modules.

**Table 2.** Device Clocking Options Select<sup>(1)</sup>

| Device Clocking Option             | CKSEL30     |

|------------------------------------|-------------|

| External Crystal/Ceramic Resonator | 1111 - 1010 |

| External Low-frequency Crystal     | 1001        |

| External RC Oscillator             | 1000 - 0101 |

| Calibrated Internal RC Oscillator  | 0100 - 0001 |

| External Clock                     | 0000        |

Note: 1. For all fuses "1" means unprogrammed while "0" means programmed.

The various choices for each clocking option is given in the following sections. When the CPU wakes up from Power-down or Power-save, the selected clock source is used to time the start-up, ensuring stable Oscillator operation before instruction execution starts. When the CPU starts from Reset, there is as an additional delay allowing the power to reach a stable level before commencing normal operation. The Watchdog Oscillator is used for timing this real-time part of the start-up time. The number of WDT Oscillator cycles used for each time-out is shown in Table 3. The frequency of the Watchdog Oscillator is voltage dependent as shown in "ATmega8535 Typical Characteristics" on page 266.

Table 3. Number of Watchdog Oscillator Cycles

| Typ Time-out (V <sub>CC</sub> = 5.0V) |  | p Time-out (V <sub>CC</sub> = 3.0V) | Number of Cycles |  |  |

|---------------------------------------|--|-------------------------------------|------------------|--|--|

| 4.1 ms                                |  | 4.3 ms                              | 4K (4,096)       |  |  |

| 65 ms                                 |  | 69 ms                               | 64K (65,536)     |  |  |

## **Default Clock Source**

The device is shipped with CKSEL = "0001" and SUT = "10". The default clock source setting is therefore the Internal RC Oscillator with longest startup time. This default setting ensures that all users can make their desired clock source setting using an In-System or Parallel Programmer.

## **Crystal Oscillator**

XTAL1 and XTAL2 are input and output, respectively, of an inverting amplifier which can be configured for use as an On-chip Oscillator, as shown in Figure 12. Either a quartz crystal or a ceramic resonator may be used. The CKOPT Fuse selects between two different oscillator amplifier modes. When CKOPT is programmed, the Oscillator output will oscillate will a full rail-to-rail swing on the output. This mode is suitable when operating in a very noisy environment or when the output from XTAL2 drives a second clock buffer. This mode has a wide frequency range. When CKOPT is unprogrammed, the Oscillator has a smaller output swing. This reduces power consumption considerably.

if the WDCE bit has logic level one. To disable an enabled Watchdog Timer, the following procedure must be followed:

- 1. In the same operation, write a logic one to WDCE and WDE. A logic one must be written to WDE even though it is set to one before the disable operation starts.

- 2. Within the next four clock cycles, write a logic 0 to WDE. This disables the watchdog.

In safety level 2, it is not possible to disable the Watchdog Timer, even with the algorithm described above. See "Timed Sequences for Changing the Configuration of the Watchdog Timer" on page 45.

### • Bits 2..0 - WDP2, WDP1, WDP0: Watchdog Timer Prescaler 2, 1, and 0

The WDP2, WDP1, and WDP0 bits determine the Watchdog Timer prescaling when the Watchdog Timer is enabled. The different prescaling values and their corresponding Timeout Periods are shown in Table 18.

**Table 18.** Watchdog Timer Prescale Select<sup>(1)</sup>

| WDP2 | WDP1 | WDP0 | Number of WDT<br>Oscillator Cycles | Typical Time-out at V <sub>CC</sub> = 3.0V | Typical Time-out at V <sub>CC</sub> = 5.0V |

|------|------|------|------------------------------------|--------------------------------------------|--------------------------------------------|

| 0    | 0    | 0    | 16K (16,384)                       | 17.1 ms                                    | 16.3 ms                                    |

| 0    | 0    | 1    | 32K (32,768)                       | 34.3 ms                                    | 32.5 ms                                    |

| 0    | 1    | 0    | 64K (65,536)                       | 68.5 ms                                    | 65 ms                                      |

| 0    | 1    | 1    | 128K (131,072)                     | 0.14 s                                     | 0.13 s                                     |

| 1    | 0    | 0    | 256K (262,144)                     | 0.27 s                                     | 0.26 s                                     |

| 1    | 0    | 1    | 512K (524,288)                     | 0.55 s                                     | 0.52 s                                     |

| 1    | 1    | 0    | 1,024K (1,048,576)                 | 1.1 s                                      | 1.0 s                                      |

| 1    | 1    | 1    | 2,048K (2,097,152)                 | 2.2 s                                      | 2.1 s                                      |

Note: 1. Values are guidelines only.

A change of the COM1x1:0 bits state will have effect at the first Compare Match after the bits are written. For non-PWM modes, the action can be forced to have immediate effect by using the FOC1x strobe bits.

## **Modes of Operation**

The mode of operation, i.e., the behavior of the Timer/Counter and the output compare pins, is defined by the combination of the *Waveform Generation mode* (WGM13:0) and *Compare Output mode* (COM1x1:0) bits. The Compare Output mode bits do not affect the counting sequence, while the Waveform Generation mode bits do. The COM1x1:0 bits control whether the PWM output generated should be inverted or not (inverted or non-inverted PWM). For non-PWM modes the COM1x1:0 bits control whether the output should be set, cleared or toggle at a Compare Match (See "Compare Match Output Unit" on page 100.)

For detailed timing information refer to "Timer/Counter Timing Diagrams" on page 108.

#### **Normal Mode**

The simplest mode of operation is the *Normal* mode (WGM13:0 = 0). In this mode the counting direction is always up (incrementing), and no counter clear is performed. The counter simply overruns when it passes its maximum 16-bit value (MAX = 0xFFFF) and then restarts from the BOTTOM (0x0000). In normal operation the *Timer/Counter Over-flow Flag* (TOV1) will be set in the same timer clock cycle as the TCNT1 becomes zero. The TOV1 Flag in this case behaves like a 17th bit, except that it is only set, not cleared. However, combined with the timer overflow interrupt that automatically clears the TOV1 Flag, the timer resolution can be increased by software. There are no special cases to consider in the Normal mode, a new counter value can be written anytime.

The Input Capture unit is easy to use in Normal mode. However, observe that the maximum interval between the external events must not exceed the resolution of the counter. If the interval between events are too long, the timer overflow interrupt or the prescaler must be used to extend the resolution for the capture unit.

The output compare units can be used to generate interrupts at some given time. Using the output compare to generate waveforms in normal mode is not recommended, since this will occupy too much of the CPU time.

# Clear Timer on Compare Match (CTC) Mode

In Clear Timer on Compare or CTC mode (WGM13:0 = 4 or 12), the OCR1A or ICR1 Register is used to manipulate the counter resolution. In CTC mode the counter is cleared to zero when the counter value (TCNT1) matches either the OCR1A (WGM13:0 = 4) or the ICR1 (WGM13:0 = 12). The OCR1A or ICR1 define the top value for the counter, hence also its resolution. This mode allows greater control of the Compare Match output frequency. It also simplifies the operation of counting external events.

The timing diagram for the CTC mode is shown in Figure 45. The counter value (TCNT1) increases until a Compare Match occurs with either OCR1A or ICR1, and then counter (TCNT1) is cleared.

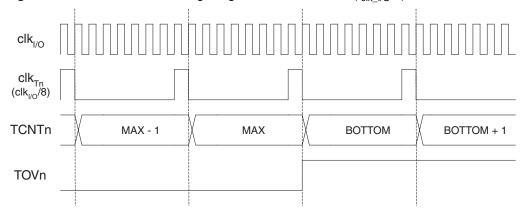

Figure 61. Timer/Counter Timing Diagram, with Prescaler ( $f_{\text{clk\_I/O}}/8$ )

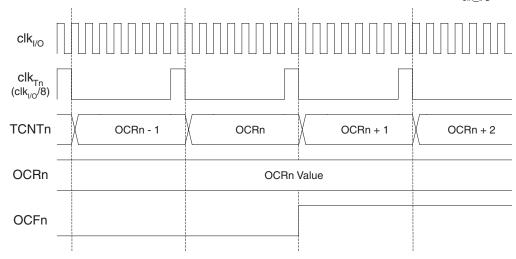

Figure 62 shows the setting of OCF2 in all modes except CTC mode.

**Figure 62.** Timer/Counter Timing Diagram, Setting of OCF2, with Prescaler ( $f_{clk}$   $_{l/O}$ /8)

Figure 63 shows the setting of OCF2 and the clearing of TCNT2 in CTC mode.

The dashed boxes in the block diagram separate the three main parts of the USART (listed from the top): Clock Generator, Transmitter and Receiver. Control registers are shared by all units. The clock generation logic consists of synchronization logic for external clock input used by synchronous slave operation, and the baud rate generator. The XCK (Transfer Clock) pin is only used by Synchronous Transfer mode. The Transmitter consists of a single write buffer, a serial Shift Register, Parity Generator and control logic for handling different serial frame formats. The write buffer allows a continuous transfer of data without any delay between frames. The Receiver is the most complex part of the USART module due to its clock and data recovery units. The recovery units are used for asynchronous data reception. In addition to the recovery units, the Receiver includes a Parity Checker, control logic, a Shift Register and a two level receive buffer (UDR). The Receiver supports the same frame formats as the Transmitter, and can detect frame error, data overrun and parity errors.

# AVR USART vs. AVR UART – Compatibility

The USART is fully compatible with the AVR UART regarding:

- Bit locations inside all USART Registers

- Baud Rate Generation

- Transmitter Operation

- Transmit Buffer Functionality

- Receiver Operation

However, the receive buffering has two improvements that will affect the compatibility in some special cases:

- A second buffer register has been added. The two buffer registers operate as a

circular FIFO buffer. Therefore the UDR must only be read once for each incoming

data! More important is the fact that the Error Flags (FE and DOR) and the ninth

data bit (RXB8) are buffered with the data in the receive buffer. Therefore the status

bits must always be read before the UDR Register is read. Otherwise the error

status will be lost since the buffer state is lost.

- The Receiver Shift Register can now act as a third buffer level. This is done by allowing the received data to remain in the serial Shift Register (see Figure 69) if the buffer registers are full, until a new start bit is detected. The USART is therefore more resistant to Data OverRun (DOR) error conditions.

The following control bits have changed name, but have same functionality and register location:

- CHR9 is changed to UCSZ2

- OR is changed to DOR

## **Clock Generation**

The clock generation logic generates the base clock for the Transmitter and Receiver. The USART supports four modes of clock operation: Normal asynchronous, Double Speed asynchronous, Master synchronous and Slave synchronous mode. The UMSEL bit in USART Control and Status Register C (UCSRC) selects between asynchronous and synchronous operation. Double Speed (asynchronous mode only) is controlled by the U2X found in the UCSRA Register. When using Synchronous mode (UMSEL = 1), the Data Direction Register for the XCK pin (DDR\_XCK) controls whether the clock source is internal (Master mode) or external (Slave mode). The XCK pin is only active when using synchronous mode.

Figure 70 shows a block diagram of the clock generation logic.

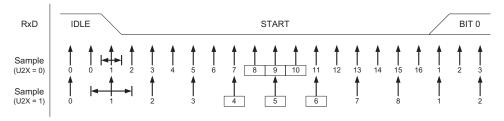

Figure 73. Start Bit Sampling

When the clock recovery logic detects a high (idle) to low (start) transition on the RxD line, the start bit detection sequence is initiated. Let sample 1 denote the first zero-sample as shown in the figure. The clock recovery logic then uses samples 8, 9, and 10 for normal mode, and samples 4, 5, and 6 for Double Speed mode (indicated with sample numbers inside boxes on the figure), to decide if a valid start bit is received. If two or more of these three samples have logical high levels (the majority wins), the start bit is rejected as a noise spike and the Receiver starts looking for the next high to low-transition. If however, a valid start bit is detected, the clock recovery logic is synchronized and the data recovery can begin. The synchronization process is repeated for each start bit.

#### **Asynchronous Data Recovery**

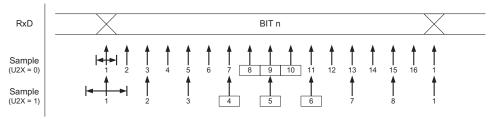

When the receiver clock is synchronized to the start bit, the data recovery can begin. The data recovery unit uses a state machine that has 16 states for each bit in normal mode and eight states for each bit in Double Speed mode. Figure 74 shows the sampling of the data bits and the parity bit. Each of the samples is given a number that is equal to the state of the recovery unit.

Figure 74. Sampling of Data and Parity Bit

The decision of the logic level of the received bit is taken by doing a majority voting of the logic value to the three samples in the center of the received bit. The center samples are emphasized on the figure by having the sample number inside boxes. The majority voting process is done as follows: If two or all three samples have high levels, the received bit is registered to be a logic 1. If two or all three samples have low levels, the received bit is registered to be a logic 0. This majority voting process acts as a low pass filter for the incoming signal on the RxD pin. The recovery process is then repeated until a complete frame is received. Including the first stop bit. Note that the Receiver only uses the first stop bit of a frame.

Figure 75 shows the sampling of the stop bit and the earliest possible beginning of the start bit of the next frame.

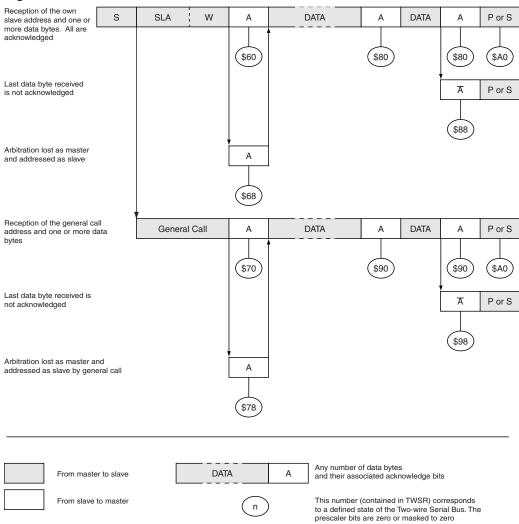

Figure 91. Formats and States in the Slave Receiver Mode

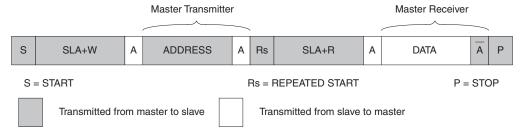

## Combining Several TWI Modes

In some cases, several TWI modes must be combined in order to complete the desired action. Consider for example reading data from a serial EEPROM. Typically, such a transfer involves the following steps:

- 1. The transfer must be initiated.

- 2. The EEPROM must be instructed what location should be read.

- 3. The reading must be performed.

- 4. The transfer must be finished.

Note that data is transmitted both from Master to Slave and vice versa. The Master must instruct the Slave what location it wants to read, requiring the use of the MT mode. Subsequently, data must be read from the Slave, implying the use of the MR mode. Thus, the transfer direction must be changed. The Master must keep control of the bus during all these steps, and the steps should be carried out as an atomical operation. If this principle is violated in a multimaster system, another Master can alter the data pointer in the EEPROM between steps 2 and 3, and the Master will read the wrong data location. Such a change in transfer direction is accomplished by transmitting a REPEATED START between the transmission of the address byte and reception of the data. After a REPEATED START, the Master keeps ownership of the bus. The following figure shows the flow in this transfer.

Figure 94. Combining Several TWI Modes to Access a Serial EEPROM

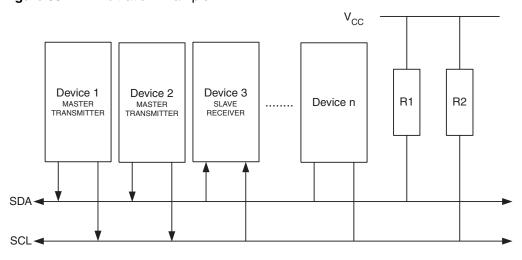

# Multi-master Systems and Arbitration

If Multiple Masters are connected to the same bus, transmissions may be initiated simultaneously by one or more of them. The TWI standard ensures that such situations are handled in such a way that one of the masters will be allowed to proceed with the transfer, and that no data will be lost in the process. An example of an arbitration situation is depicted below, where two masters are trying to transmit data to a Slave Receiver.

Figure 95. An Arbitration Example

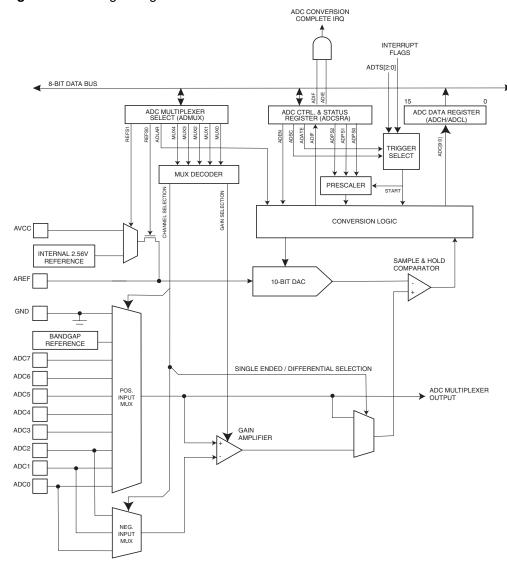

Figure 98. Analog-to-Digital Converter Block Schematic

## **Operation**

The ADC converts an analog input voltage to a 10-bit digital value through successive approximation. The minimum value represents GND and the maximum value represents the voltage on the AREF pin minus 1 LSB. Optionally, AVCC or an internal 2.56V reference voltage may be connected to the AREF pin by writing to the REFSn bits in the ADMUX Register. The internal voltage reference may thus be decoupled by an external capacitor at the AREF pin to improve noise immunity.

The analog input channel and differential gain are selected by writing to the MUX bits in ADMUX. Any of the ADC input pins, as well as GND and a fixed bandgap voltage reference, can be selected as single ended inputs to the ADC. A selection of ADC input pins can be selected as positive and negative inputs to the differential gain amplifier.

If differential channels are selected, the differential gain stage amplifies the voltage difference between the selected input channel pair by the selected gain factor. This amplified value then becomes the analog input to the ADC. If single ended channels are used, the gain amplifier is bypassed altogether.

## • Bits 4:0 - MUX4:0: Analog Channel and Gain Selection Bits

The value of these bits selects which combination of analog inputs are connected to the ADC. These bits also select the gain for the differential channels. See Table 85 for details. If these bits are changed during a conversion, the change will not go in effect until this conversion is complete (ADIF in ADCSRA is set).

Table 85. Input Channel and Gain Selections

| MUX40 | Single Ended Input | Pos Differential Input | Neg Differential Input | Gain |

|-------|--------------------|------------------------|------------------------|------|

| 00000 | ADC0               |                        |                        |      |

| 00001 | ADC1               |                        |                        |      |

| 00010 | ADC2               |                        |                        |      |

| 00011 | ADC3               | N/A                    |                        |      |

| 00100 | ADC4               |                        |                        |      |

| 00101 | ADC5               |                        |                        |      |

| 00110 | ADC6               |                        |                        |      |

| 00111 | ADC7               |                        |                        |      |

| 01000 |                    | ADC0                   | ADC0                   | 10x  |

| 01001 |                    | ADC1                   | ADC0                   | 10x  |

| 01010 |                    | ADC0                   | ADC0                   | 200x |

| 01011 |                    | ADC1                   | ADC0                   | 200x |

| 01100 |                    | ADC2                   | ADC2                   | 10x  |

| 01101 |                    | ADC3                   | ADC2                   | 10x  |

| 01110 |                    | ADC2                   | ADC2                   | 200x |

| 01111 |                    | ADC3                   | ADC2                   | 200x |

| 10000 |                    | ADC0                   | ADC1                   | 1x   |

| 10001 |                    | ADC1                   | ADC1                   | 1x   |

| 10010 | N/A                | ADC2                   | ADC1                   | 1x   |

| 10011 |                    | ADC3                   | ADC1                   | 1x   |

| 10100 |                    | ADC4                   | ADC1                   | 1x   |

| 10101 |                    | ADC5                   | ADC1                   | 1x   |

| 10110 |                    | ADC6                   | ADC1                   | 1x   |

| 10111 |                    | ADC7                   | ADC1                   | 1x   |

| 11000 |                    | ADC0                   | ADC2                   | 1x   |

| 11001 |                    | ADC1                   | ADC2                   | 1x   |

| 11010 |                    | ADC2                   | ADC2                   | 1x   |

| 11011 |                    | ADC3                   | ADC2                   | 1x   |

| 11100 |                    | ADC4                   | ADC2                   | 1x   |

Table 86. ADC Prescaler Selections

| ADPS2 | ADPS1 | ADPS0 | Division Factor |

|-------|-------|-------|-----------------|

| 0     | 0     | 0     | 2               |

| 0     | 0     | 1     | 2               |

| 0     | 1     | 0     | 4               |

| 0     | 1     | 1     | 8               |

| 1     | 0     | 0     | 16              |

| 1     | 0     | 1     | 32              |

| 1     | 1     | 0     | 64              |

| 1     | 1     | 1     | 128             |

## The ADC Data Register – ADCL and ADCH

ADLAR = 0

| Bit           | 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    | _    |

|---------------|------|------|------|------|------|------|------|------|------|

|               | -    | -    | -    | -    | -    | -    | ADC9 | ADC8 | ADCH |

|               | ADC7 | ADC6 | ADC5 | ADC4 | ADC3 | ADC2 | ADC1 | ADC0 | ADCL |

|               | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    | •    |

| Read/Write    | R    | R    | R    | R    | R    | R    | R    | R    |      |

|               | R    | R    | R    | R    | R    | R    | R    | R    |      |

| Initial Value | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |      |

|               | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |      |

ADLAR = 1

| Bit           | 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    | _    |

|---------------|------|------|------|------|------|------|------|------|------|

|               | ADC9 | ADC8 | ADC7 | ADC6 | ADC5 | ADC4 | ADC3 | ADC2 | ADCH |

|               | ADC1 | ADC0 | -    | -    | -    | -    | -    | -    | ADCL |

|               | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    | •    |

| Read/Write    | R    | R    | R    | R    | R    | R    | R    | R    |      |

|               | R    | R    | R    | R    | R    | R    | R    | R    |      |

| Initial Value | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |      |

|               | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |      |

When an ADC conversion is complete, the result is found in these two registers. If differential channels are used, the result is presented in two's complement form.

When ADCL is read, the ADC Data Register is not updated until ADCH is read. Consequently, if the result is left adjusted and no more than 8-bit precision is required, it is sufficient to read ADCH. Otherwise, ADCL must be read first, then ADCH.

The ADLAR bit in ADMUX, and the MUXn bits in ADMUX affect the way the result is read from the registers. If ADLAR is set, the result is left adjusted. If ADLAR is cleared (default), the result is right adjusted.

### • ADC9:0: ADC Conversion Result

These bits represent the result from the conversion, as detailed in "ADC Conversion Result" on page 218.

## Special Function IO Register – SFIOR

| Bit           | 7     | 6     | 5     | 4 | 3    | 2   | 1    | 0     |       |

|---------------|-------|-------|-------|---|------|-----|------|-------|-------|

|               | ADTS2 | ADTS1 | ADTS0 | - | ACME | PUD | PSR2 | PSR10 | SFIOR |

| Read/Write    | R/W   | R/W   | R/W   | R | R/W  | R/W | R/W  | R/W   | l     |

| Initial Value | 0     | 0     | 0     | 0 | 0    | 0   | 0    | 0     |       |

## • Bit 7:5 - ADTS2:0: ADC Auto Trigger Source

If ADATE in ADCSRA is written to one, the value of these bits selects which source will trigger an ADC conversion. If ADATE is cleared, the ADTS2:0 settings will have no effect. A conversion will be triggered by the rising edge of the selected interrupt flag. Note that switching from a trigger source that is cleared to a trigger source that is set, will generate a positive edge on the trigger signal. If ADEN in ADCSRA is set, this will start a conversion. Switching to Free Running mode (ADTS[2:0]=0) will not cause a trigger event, even if the ADC Interrupt Flag is set.

Table 87. ADC Auto Trigger Source Selections

| ADTS2 | ADTS1 | ADTS0 | Trigger Source                 |  |  |  |

|-------|-------|-------|--------------------------------|--|--|--|

| 0     | 0     | 0     | Free Running mode              |  |  |  |

| 0     | 0     | 1     | Analog Comparator              |  |  |  |

| 0     | 1     | 0     | External Interrupt Request 0   |  |  |  |

| 0     | 1     | 1     | Timer/Counter0 Compare Match   |  |  |  |

| 1     | 0     | 0     | Timer/Counter0 Overflow        |  |  |  |

| 1     | 0     | 1     | Timer/Counter1 Compare Match B |  |  |  |

| 1     | 1     | 0     | Timer/Counter1 Overflow        |  |  |  |

| 1     | 1     | 1     | Timer/Counter1 Capture Event   |  |  |  |

### • Bit 4 - RES: Reserved Bit

This bit is reserved bit in the ATmega8535, and will always read as zero.

## **Parallel Programming**

#### **Enter Programming Mode**

The following algorithm puts the device in Parallel Programming mode:

- 1. Apply 4.5 5.5V between  $V_{CC}$  and GND, and wait at least 100  $\mu$ s.

- 2. Set RESET to "0" and toggle XTAL1 at least six times.

- 3. Set the Prog\_enable pins listed in Table 101 on page 241 to "0000" and wait at least 100 ns.

- 4. Apply 11.5 12.5V to RESET. Any activity on Prog\_enable pins within 100 ns after +12V has been applied to RESET, will cause the device to fail entering Programming mode.

Note, if External Crystal or External RC configuration is selected, it may not be possible to apply qualified XTAL1 pulses. In such cases, the following algorithm should be followed:

- 1. Set Prog\_enable pins listed in Table 101 on page 241 to "0000".

- 2. Apply 4.5 5.5V between  $V_{CC}$  and GND simultaneously as 11.5 12.5V is applied to  $\overline{\text{RESET}}$ .

- Wait 100 ns.

- 4. Re-program the fuses to ensure that External Clock is selected as clock source (CKSEL3:0 = 0b0000) If Lock bits are programmed, a Chip Erase command must be executed before changing the fuses.

- 5. Exit Programming mode by power the device down or by bringing RESET pin to 0b0.

- Entering Programming mode with the original algorithm, as described above.

# Considerations for Efficient Programming

The loaded command and address are retained in the device during programming. For efficient programming, the following should be considered.

- The command needs only be loaded once when writing or reading multiple memory locations.

- Skip writing the data value 0xFF, that is the contents of the entire EEPROM (unless the EESAVE fuse is programmed) and Flash after a Chip Erase.

- Address high byte needs only be loaded before programming or reading a new 256 word window in Flash or 256 byte EEPROM. This consideration also applies to Signature bytes reading.

#### **Chip Erase**

The Chip Erase will erase the Flash and EEPROM<sup>(1)</sup> memories plus Lock bits. The Lock bits are not reset until the program memory has been completely erased. The Fuse bits are not changed. A Chip Erase must be performed before the Flash and/or the EEPROM is reprogrammed.

Note: 1. The EEPRPOM memory is preserved during Chip Erase if the EESAVE Fuse is programmed.

Load Command "Chip Erase"

- 1. Set XA1, XA0 to "10". This enables command loading.

- 2. Set BS1 to "0".

- 3. Set DATA to "1000 0000". This is the command for Chip Erase.

- 4. Give XTAL1 a positive pulse. This loads the command.

- 5. Give WR a negative pulse. This starts the Chip Erase. RDY/BSY goes low.

- 6. Wait until RDY/BSY goes high before loading a new command.

## **Programming the Flash**

The Flash is organized in pages, see Table 104 on page 241. When programming the Flash, the program data is latched into a page buffer. This allows one page of program data to be programmed simultaneously. The following procedure describes how to program the entire Flash memory:

- A. Load Command "Write Flash"

- 1. Set XA1, XA0 to "10". This enables command loading.

- 2. Set BS1 to "0".

- 3. Set DATA to "0001 0000". This is the command for Write Flash.

- 4. Give XTAL1 a positive pulse. This loads the command.

- B. Load Address Low byte

- 1. Set XA1, XA0 to "00". This enables address loading.

- 2. Set BS1 to "0". This selects low address.

- 3. Set DATA = Address low byte (0x00 0xFF).

- 4. Give XTAL1 a positive pulse. This loads the address low byte.

- C. Load Data Low Byte

- 1. Set XA1, XA0 to "01". This enables data loading.

- 2. Set DATA = Data low byte (0x00 0xFF).

- 3. Give XTAL1 a positive pulse. This loads the data byte.

- D. Load Data High Byte

- 1. Set BS1 to "1". This selects high data byte.

- 2. Set XA1, XA0 to "01". This enables data loading.

- 3. Set DATA = Data high byte (0x00 0xFF).

- 4. Give XTAL1 a positive pulse. This loads the data byte.

- E. Latch Data

- 1. Set BS1 to "1". This selects high data byte.

- 2. Give PAGEL a positive pulse. This latches the data bytes. (See Figure 117 for signal waveforms.)

- F. Repeat B through E until the entire buffer is filled or until all data within the page is loaded.

While the lower bits in the address are mapped to words within the page, the higher bits address the pages within the FLASH. This is illustrated in Figure 116 on page 244. Note that if less than eight bits are required to address words in the page (pagesize < 256), the most significant bit(s) in the address low byte are used to address the page when performing a page write.

- G. Load Address High byte

- 1. Set XA1, XA0 to "00". This enables address loading.

- 2. Set BS1 to "1". This selects high address.

- 3. Set DATA = Address high byte (0x00 0xFF).

- 4. Give XTAL1 a positive pulse. This loads the address high byte.

- H. Program Page

- 1. Set BS1 to "0".

- 2. Give WR a negative pulse. This starts programming of the entire page of data. RDY/BSY goes low.

## **Data Polling EEPROM**

When a new byte has been written and is being programmed into EEPROM, reading the address location being programmed will give the value 0xFF. At the time the device is ready for a new byte, the programmed value will read correctly. This is used to determine when the next byte can be written. This will not work for the value 0xFF, but the user should have the following in mind: As a chip erased device contains 0xFF in all locations, programming of addresses that are meant to contain 0xFF, can be skipped. This does not apply if the EEPROM is reprogrammed without chip erasing the device. In this case, data polling cannot be used for the value 0xFF, and the user will have to wait at least  $t_{\rm WD\_EEPROM}$  before programming the next byte. See Table 108 for  $t_{\rm WD\_EEPROM}$  value.

Table 108. Minimum Wait Delay Before Writing the Next Flash or EEPROM Location

| Symbol                 | Minimum Wait Delay |

|------------------------|--------------------|

| t <sub>WD_FLASH</sub>  | 4.5 ms             |

| t <sub>WD_EEPROM</sub> | 9.0 ms             |

| t <sub>WD_ERASE</sub>  | 9.0 ms             |

| t <sub>WD_FUSE</sub>   | 4.5 ms             |

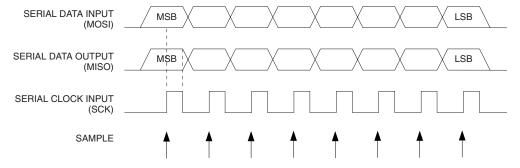

Figure 125. Serial Programming Waveforms

$T_A = -40$ °C to 85°C,  $V_{CC} = 2.7$ V to 5.5V (unless otherwise noted) (Continued)

| Symbol            | Parameter                                  | Condition                                                    | Min | Тур        | Max | Units |

|-------------------|--------------------------------------------|--------------------------------------------------------------|-----|------------|-----|-------|

|                   |                                            | Active 4 MHz, V <sub>CC</sub> = 3V (ATmega8535L)             |     | 4          |     | mA    |

|                   |                                            | Active 8 MHz, V <sub>CC</sub> = 5V (ATmega8535)              |     | 14         |     | mA    |

| I <sub>CC</sub>   | Power Supply Current                       | Idle 4 MHz, V <sub>CC</sub> = 3V<br>(ATmega8535L)            |     | 3          |     | mA    |

|                   |                                            | Idle 8 MHz, V <sub>CC</sub> = 5V<br>(ATmega8535)             |     | 10         |     | mA    |

|                   | Power-down mode <sup>(5)</sup>             | WDT enabled, V <sub>CC</sub> = 3V                            |     | < 10       |     | μA    |

|                   | Power-down mode(*)                         | WDT disabled, V <sub>CC</sub> = 3V                           |     | < 3        |     | μA    |

| V <sub>ACIO</sub> | Analog Comparator<br>Input Offset Voltage  | $V_{CC} = 5V$ $V_{in} = V_{CC}/2$                            |     |            | 40  | mV    |

| I <sub>ACLK</sub> | Analog Comparator<br>Input Leakage Current | V <sub>CC</sub> = 5V<br>V <sub>in</sub> = V <sub>CC</sub> /2 | -50 |            | 50  | nA    |

| t <sub>ACPD</sub> | Analog Comparator<br>Propagation Delay     | V <sub>CC</sub> = 2.7V<br>V <sub>CC</sub> = 4.0V             |     | 750<br>500 |     | ns    |

- Notes: 1. "Max" means the highest value where the pin is guaranteed to be read as low.

- 2. "Min" means the lowest value where the pin is guaranteed to be read as high.

- 3. Although each I/O port can sink more than the test conditions (20mA at  $V_{CC} = 5V$ , 10mA at  $V_{CC} = 3V$ ) under steady state conditions (non-transient), the following must be observed: PDIP Package:

- 1] The sum of all IOL, for all ports, should not exceed 200 mA.

- 2] The sum of all IOL, for port A0 A7, should not exceed 100 mA.

- 3] The sum of all IOL, for ports B0 B7,C0 C7, D0 D7 and XTAL2, should not exceed 100 mA.

#### PLCC/MLF/TQFP Package:

- 1] The sum of all IOL, for all ports, should not exceed 400 mA.

- 2] The sum of all IOL, for ports A0 A7, should not exceed 100 mA.

- 3] The sum of all IOL, for ports B0 B3, should not exceed 100 mA.

- 4] The sum of all IOL, for ports B4 B7, should not exceed 100 mA.

- 5] The sum of all IOL, for ports C0 C3, should not exceed 100 mA.

- 6] The sum of all IOL, for ports C4 C7, should not exceed 100 mA.

- 7] The sum of all IOL, for ports D0 D3 and XTAL2, should not exceed 100 mA.

- 8] The sum of all IOL, for ports D4 D7, should not exceed 100 mA.

- If IOL exceeds the test condition, VOL may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test condition.

- 4. Although each I/O port can source more than the test conditions (20mA at V<sub>CC</sub> = 5V, 10mA at V<sub>CC</sub> = 3V) under steady state conditions (non-transient), the following must be observed:

- 1] The sum of all IOH, for all ports, should not exceed 200 mA.

- 2] The sum of all IOH, for port A0 A7, should not exceed 100 mA.

- 3] The sum of all IOH, for ports B0 B7,C0 C7, D0 D7 and XTAL2, should not exceed 100 mA.

#### PLCC/MLF/TQFP Package:

- 1] The sum of all IOH, for all ports, should not exceed 400 mA.

- 2] The sum of all IOH, for ports A0 A7, should not exceed 100 mA.

- 3] The sum of all IOH, for ports B0 B3, should not exceed 100 mA.

- 4] The sum of all IOH, for ports B4 B7, should not exceed 100 mA.

- 5] The sum of all IOH, for ports C0 C3, should not exceed 100 mA.

- 6] The sum of all IOH, for ports C4 C7, should not exceed 100 mA.

- 7] The sum of all IOH, for ports D0 D3 and XTAL2, should not exceed 100 mA.

- 8] The sum of all IOH, for ports D4 D7, should not exceed 100 mA

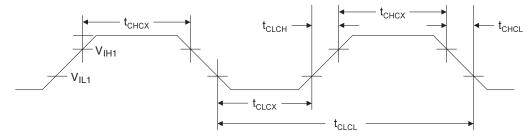

## **External Clock Drive Waveforms**

Figure 126. External Clock Drive Waveforms

## **External Clock Drive**

Table 110. External Clock Drive

|                         |                                                   | V <sub>CC</sub> = 2.7 | 7V to 5.5V | V <sub>CC</sub> = 4.5 | 5V to 5.5V |       |

|-------------------------|---------------------------------------------------|-----------------------|------------|-----------------------|------------|-------|

| Symbol                  | Parameter                                         | Min                   | Max        | Min                   | Max        | Units |

| 1/t <sub>CLCL</sub>     | Oscillator Frequency                              | 0                     | 8          | 0                     | 16         | MHz   |

| t <sub>CLCL</sub>       | Clock Period                                      | 125                   |            | 62.5                  |            | ns    |

| t <sub>CHCX</sub>       | High Time                                         | 50                    |            | 25                    |            | ns    |

| t <sub>CLCX</sub>       | Low Time                                          | 50                    |            | 25                    |            | ns    |

| t <sub>CLCH</sub>       | Rise Time                                         |                       | 1.6        |                       | 0.5        | μS    |

| t <sub>CHCL</sub>       | Fall Time                                         |                       | 1.6        |                       | 0.5        | μS    |

| $\Delta t_{	ext{CLCL}}$ | Change in period from one clock cycle to the next |                       | 2          |                       | 2          | %     |

Table 111. External RC Oscillator, Typical Frequencies

| R [ $\mathbf{k}\Omega$ ] <sup>(1)</sup> | C [pF] | <b>f</b> <sup>(2)</sup> |

|-----------------------------------------|--------|-------------------------|

| 33                                      | 22     | 650 kHz                 |

| 10                                      | 22     | 2.0 MHz                 |

- Notes: 1. R should be in the range 3 k $\Omega$  100 k $\Omega$ , and C should be at least 20 pF. The C values given in the table includes pin capacitance. This will vary with package type.

2. The frequency will vary with package type and board layout.

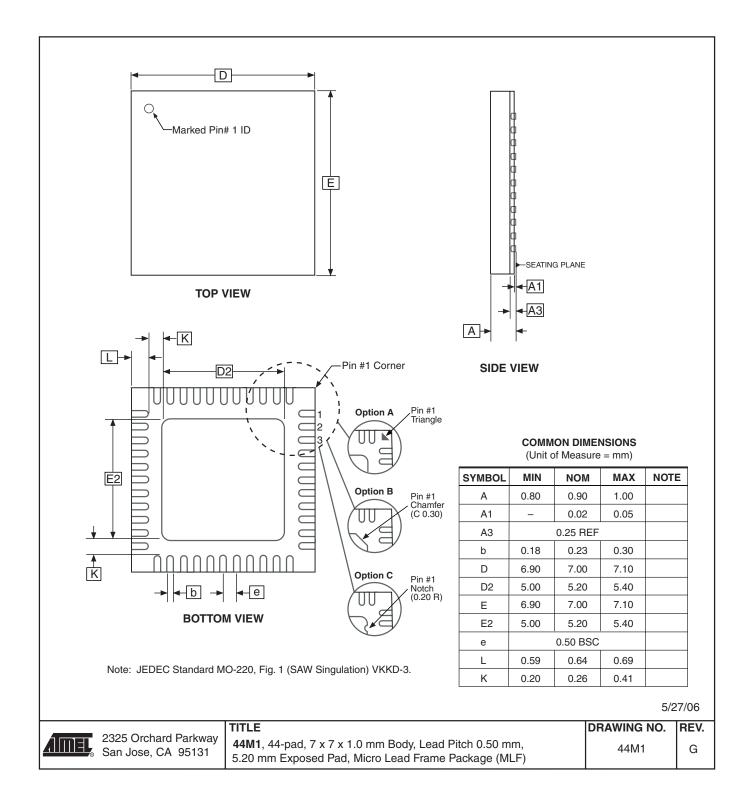

## 44M1-A

## **Errata**

The revision letter refer to the device revision.

## ATmega8535 Rev. A and B

- First Analog Comparator conversion may be delayed

- Asynchronous Oscillator does not stop in Power-down

#### 1. First Analog Comparator conversion may be delayed

If the device is powered by a slow rising  $V_{\text{CC}}$ , the first Analog Comparator conversion will take longer than expected on some devices.

#### **Problem Fix/Workaround**

When the device has been powered or reset, disable then enable the Analog Comparator before the first conversion.

## 2. Asynchronous Oscillator does not stop in Power-down

The asynchronous oscillator does not stop when entering Power-down mode. This leads to higher power consumption than expected.

### Problem Fix/Workaround

Manually disable the asynchronous timer before entering Power-down.

| Prescaling and Conversion Timing                                                                                                                                                                                                                                                                                                | 209               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Changing Channel or Reference Selection                                                                                                                                                                                                                                                                                         | 212               |

| ADC Noise Canceler                                                                                                                                                                                                                                                                                                              | 214               |

| ADC Conversion Result                                                                                                                                                                                                                                                                                                           | 218               |

| Boot Loader Support – Read-While-Write Self-Programmii                                                                                                                                                                                                                                                                          | ng 224            |

| Boot Loader Features                                                                                                                                                                                                                                                                                                            | _                 |

| Application and Boot Loader Flash Sections                                                                                                                                                                                                                                                                                      | 224               |

| Read-While-Write and No Read-While-Write Flash Sections                                                                                                                                                                                                                                                                         | 224               |

| Boot Loader Lock Bits                                                                                                                                                                                                                                                                                                           | 226               |

| Entering the Boot Loader Program                                                                                                                                                                                                                                                                                                | 227               |

| Addressing the Flash during Self-Programming                                                                                                                                                                                                                                                                                    | 229               |

| Self-Programming the Flash                                                                                                                                                                                                                                                                                                      | 230               |

| Memory Programming                                                                                                                                                                                                                                                                                                              | 237               |

| Program And Data Memory Lock Bits                                                                                                                                                                                                                                                                                               | 237               |

| Fuse Bits                                                                                                                                                                                                                                                                                                                       | 238               |

| Signature Bytes                                                                                                                                                                                                                                                                                                                 | 239               |

| Calibration Byte                                                                                                                                                                                                                                                                                                                | 239               |

| Parallel Programming Parameters, Pin Mapping, and Commands                                                                                                                                                                                                                                                                      | 240               |

| Parallel Programming                                                                                                                                                                                                                                                                                                            | 242               |

| Serial Downloading                                                                                                                                                                                                                                                                                                              | 251               |

| Electrical Characteristics                                                                                                                                                                                                                                                                                                      | 255               |

|                                                                                                                                                                                                                                                                                                                                 |                   |

| Absolute Maximum Ratings*                                                                                                                                                                                                                                                                                                       |                   |

|                                                                                                                                                                                                                                                                                                                                 | 255               |

| Absolute Maximum Ratings*                                                                                                                                                                                                                                                                                                       | 255<br>255        |

| Absolute Maximum Ratings*  DC Characteristics                                                                                                                                                                                                                                                                                   | 255<br>255<br>258 |

| Absolute Maximum Ratings*  DC Characteristics  External Clock Drive Waveforms                                                                                                                                                                                                                                                   |                   |

| Absolute Maximum Ratings*  DC Characteristics  External Clock Drive Waveforms  External Clock Drive                                                                                                                                                                                                                             |                   |

| Absolute Maximum Ratings*  DC Characteristics  External Clock Drive Waveforms  External Clock Drive  Two-wire Serial Interface Characteristics                                                                                                                                                                                  |                   |

| Absolute Maximum Ratings*  DC Characteristics  External Clock Drive Waveforms  External Clock Drive  Two-wire Serial Interface Characteristics  SPI Timing Characteristics                                                                                                                                                      |                   |

| Absolute Maximum Ratings*                                                                                                                                                                                                                                                                                                       |                   |

| Absolute Maximum Ratings*  DC Characteristics  External Clock Drive Waveforms  External Clock Drive  Two-wire Serial Interface Characteristics  SPI Timing Characteristics  ADC Characteristics  ATmega8535 Typical Characteristics  Register Summary                                                                           |                   |

| Absolute Maximum Ratings*  DC Characteristics  External Clock Drive Waveforms  External Clock Drive  Two-wire Serial Interface Characteristics  SPI Timing Characteristics  ADC Characteristics  ATmega8535 Typical Characteristics                                                                                             |                   |

| Absolute Maximum Ratings*  DC Characteristics  External Clock Drive Waveforms  External Clock Drive  Two-wire Serial Interface Characteristics  SPI Timing Characteristics  ADC Characteristics  ATmega8535 Typical Characteristics  Register Summary                                                                           |                   |

| Absolute Maximum Ratings*  DC Characteristics  External Clock Drive Waveforms  External Clock Drive  Two-wire Serial Interface Characteristics  SPI Timing Characteristics  ADC Characteristics  ATmega8535 Typical Characteristics  Register Summary  Instruction Set Summary  Ordering Information  Packaging Information     | 255<br>           |

| Absolute Maximum Ratings*  DC Characteristics  External Clock Drive Waveforms  External Clock Drive  Two-wire Serial Interface Characteristics  SPI Timing Characteristics  ADC Characteristics  ATmega8535 Typical Characteristics  Register Summary  Instruction Set Summary  Ordering Information                            | 255<br>           |

| Absolute Maximum Ratings* DC Characteristics External Clock Drive Waveforms External Clock Drive Two-wire Serial Interface Characteristics SPI Timing Characteristics ADC Characteristics  ATmega8535 Typical Characteristics  Register Summary  Instruction Set Summary  Ordering Information  Packaging Information  44A 40P6 |                   |

| Absolute Maximum Ratings* DC Characteristics External Clock Drive Waveforms External Clock Drive Two-wire Serial Interface Characteristics SPI Timing Characteristics ADC Characteristics  ATmega8535 Typical Characteristics  Register Summary  Instruction Set Summary  Ordering Information  Packaging Information  44A      |                   |