Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | AVR                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 8MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 32                                                                        |

| Program Memory Size        | 8KB (4K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 512 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-LCC (J-Lead)                                                           |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega8535I-8ju |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Pin Descriptions**

| V <sub>cc</sub> | Digital supply voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND             | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Port A (PA7PA0) | Port A serves as the analog inputs to the A/D Converter.<br>Port A also serves as an 8-bit bi-directional I/O port, if the A/D Converter is not used.<br>Port pins can provide internal pull-up resistors (selected for each bit). The Port A output<br>buffers have symmetrical drive characteristics with both high sink and source capability.<br>When pins PA0 to PA7 are used as inputs and are externally pulled low, they will source<br>current if the internal pull-up resistors are activated. The Port A pins are tri-stated when |

| Port B (PB7PB0) | a reset condition becomes active, even if the clock is not running.<br>Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running.                             |

|                 | Port B also serves the functions of various special features of the ATmega8535 as listed on page 60.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Port C (PC7PC0) | Port C is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port C output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tri-stated when a reset condition becomes active, even if the clock is not running.                                                                                                    |

| Port D (PD7PD0) | Port D is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not running.                                                                                                    |

|                 | Port D also serves the functions of various special features of the ATmega8535 as listed on page 64.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RESET           | Reset input. A low level on this pin for longer than the minimum pulse length will gener-<br>ate a reset, even if the clock is not running. The minimum pulse length is given in Table<br>15 on page 37. Shorter pulses are not guaranteed to generate a reset.                                                                                                                                                                                                                                                                              |

| XTAL1           | Input to the inverting Oscillator amplifier and input to the internal clock operating circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| XTAL2           | Output from the inverting Oscillator amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| AVCC            | AVCC is the supply voltage pin for Port A and the A/D Converter. It should be externally connected to $V_{CC}$ , even if the ADC is not used. If the ADC is used, it should be connected to $V_{CC}$ through a low-pass filter.                                                                                                                                                                                                                                                                                                              |

| AREF            | AREF is the analog reference pin for the A/D Converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Moving Interrupts Between Application and Boot Space The General Interrupt Control Register controls the placement of the Interrupt Vector table.

General Interrupt Control Register – GICR

| Bit           | 7    | 6    | 5    | 4 | 3 | 2 | 1     | 0    | _    |

|---------------|------|------|------|---|---|---|-------|------|------|

|               | INT1 | INT0 | INT2 | - | - | - | IVSEL | IVCE | GICR |

| Read/Write    | R/W  | R/W  | R/W  | R | R | R | R/W   | R/W  |      |

| Initial Value | 0    | 0    | 0    | 0 | 0 | 0 | 0     | 0    |      |

#### • Bit 1 – IVSEL: Interrupt Vector Select

When the IVSEL bit is cleared (zero), the Interrupt Vectors are placed at the start of the Flash memory. When this bit is set (one), the Interrupt Vectors are moved to the beginning of the Boot Loader section of the Flash. The actual address of the start of the Boot Flash section is determined by the BOOTSZ Fuses. Refer to the section "Boot Loader Support – Read-While-Write Self-Programming" on page 224 for details. To avoid unintentional changes of Interrupt Vector tables, a special write procedure must be followed to change the IVSEL bit:

- 1. Write the Interrupt Vector Change Enable (IVCE) bit to one.

- 2. Within four cycles, write the desired value to IVSEL while writing a zero to IVCE.

Interrupts will automatically be disabled while this sequence is executed. Interrupts are disabled in the cycle IVCE is set, and they remain disabled until after the instruction following the write to IVSEL. If IVSEL is not written, interrupts remain disabled for four cycles. The I-bit in the Status Register is unaffected by the automatic disabling.

Note: If Interrupt Vectors are placed in the Boot Loader section and Boot Lock bit BLB02 is programmed, interrupts are disabled while executing from the Application section. If Interrupt Vectors are placed in the Application section and Boot Lock bit BLB12 is programed, interrupts are disabled while executing from the Boot Loader section. Refer to the section "Boot Loader Support – Read-While-Write Self-Programming" on page 224 for details on Boot Lock bits.

#### Bit 0 – IVCE: Interrupt Vector Change Enable

The IVCE bit must be written to logic one to enable change of the IVSEL bit. IVCE is cleared by hardware four cycles after it is written or when IVSEL is written. Setting the IVCE bit will disable interrupts, as explained in the IVSEL description above. See Code Example below.

| Signal Name | PA3/ADC3   | PA2/ADC2   | PA1/ADC1   | PA0/ADC0   |

|-------------|------------|------------|------------|------------|

| PUOE        | 0          | 0          | 0          | 0          |

| PUOV        | 0          | 0          | 0          | 0          |

| DDOE        | 0          | 0          | 0          | 0          |

| DDOV        | 0          | 0          | 0          | 0          |

| PVOE        | 0          | 0          | 0          | 0          |

| PVOV        | 0          | 0          | 0          | 0          |

| DIEOE       | 0          | 0          | 0          | 0          |

| DIEOV       | 0          | 0          | 0          | 0          |

| DI          | -          | -          | -          | -          |

| AIO         | ADC3 INPUT | ADC2 INPUT | ADC1 INPUT | ADC0 INPUT |

**Table 25.** Overriding Signals for Alternate Functions in PA3..PA0

Alternate Functions Of Port B The Port B pins with alternate functions are shown in Table 26.

Table 26. Port B Pins Alternate Functions

| Port Pin | Alternate Functions                                                                         |  |  |  |

|----------|---------------------------------------------------------------------------------------------|--|--|--|

| PB7      | SCK (SPI Bus Serial Clock)                                                                  |  |  |  |

| PB6      | MISO (SPI Bus Master Input/Slave Output)                                                    |  |  |  |

| PB5      | MOSI (SPI Bus Master Output/Slave Input)                                                    |  |  |  |

| PB4      | SS (SPI Slave Select Input)                                                                 |  |  |  |

| PB3      | AIN1 (Analog Comparator Negative Input)<br>OC0 (Timer/Counter0 Output Compare Match Output) |  |  |  |

| PB2      | AIN0 (Analog Comparator Positive Input)<br>INT2 (External Interrupt 2 Input)                |  |  |  |

| PB1      | T1 (Timer/Counter1 External Counter Input)                                                  |  |  |  |

| PB0      | T0 (Timer/Counter0 External Counter Input)<br>XCK (USART External Clock Input/Output)       |  |  |  |

The alternate pin configuration is as follows:

## • SCK - Port B, Bit 7

SCK: Master Clock output, Slave Clock input pin for SPI channel. When the SPI is enabled as a Slave, this pin is configured as an input regardless of the setting of DDB7. When the SPI is enabled as a Master, the data direction of this pin is controlled by DDB7. When the pin is forced by the SPI to be an input, the pull-up can still be controlled by the PORTB7 bit.

### • MISO - Port B, Bit 6

MISO: Master Data input, Slave Data output pin for SPI channel. When the SPI is enabled as a Master, this pin is configured as an input regardless of the setting of DDB6. When the SPI is enabled as a Slave, the data direction of this pin is controlled by DDB6. When the pin is forced by the SPI to be an input, the pull-up can still be controlled by the PORTB6 bit.

### • Bit 0 – TOIE0: Timer/Counter0 Overflow Interrupt Enable

When the TOIE0 bit is written to one, and the I-bit in the Status Register is set (one), the Timer/Counter0 Overflow interrupt is enabled. The corresponding interrupt is executed if an overflow in Timer/Counter0 occurs (i.e., when the TOV0 bit is set in the Timer/Counter Interrupt Flag Register – TIFR).

## Timer/Counter Interrupt Flag Register – TIFR

| Bit           | 7    | 6    | 5    | 4     | 3     | 2    | 1    | 0    | _    |

|---------------|------|------|------|-------|-------|------|------|------|------|

|               | OCF2 | TOV2 | ICF1 | OCF1A | OCF1B | TOV1 | OCF0 | TOV0 | TIFR |

| Read/Write    | R/W  | R/W  | R/W  | R/W   | R/W   | R/W  | R/W  | R/W  | -    |

| Initial Value | 0    | 0    | 0    | 0     | 0     | 0    | 0    | 0    |      |

## Bit 1 – OCF0: Output Compare Flag 0

The OCF0 bit is set (one) when a Compare Match occurs between the Timer/Counter0 and the data in OCR0 – Output Compare Register0. OCF0 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, OCF0 is cleared by writing a logic one to the flag. When the I-bit in SREG, OCIE0 (Timer/Counter0 Compare Match Interrupt Enable), and OCF0 are set (one), the Timer/Counter0 Compare Match Interrupt is executed.

## • Bit 0 – TOV0: Timer/Counter0 Overflow Flag

The bit TOV0 is set (one) when an overflow occurs in Timer/Counter0. TOV0 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, TOV0 is cleared by writing a logic one to the flag. When the SREG I-bit, TOIE0 (Timer/Counter0 Overflow Interrupt Enable), and TOV0 are set (one), the Timer/Counter0 Overflow Interrupt is executed. In phase correct PWM mode, this bit is set when Timer/Counter0 changes counting direction at 0x00.

measuring frequency only, the clearing of the ICF1 Flag is not required (if an interrupt handler is used).

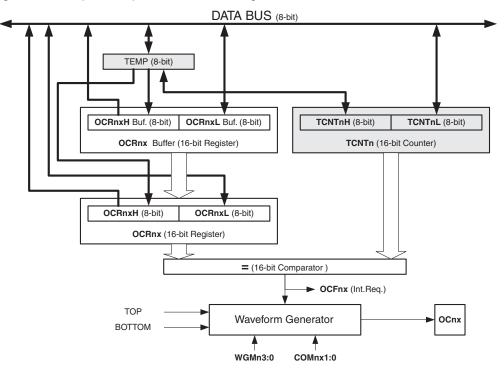

## **Output Compare Units**

The 16-bit comparator continuously compares TCNT1 with the *Output Compare Register* (OCR1x). If TCNT equals OCR1x the comparator signals a match. A match will set the *Output Compare Flag* (OCF1x) at the next timer clock cycle. If enabled (OCIE1x = 1), the Output Compare Flag generates an output compare interrupt. The OCF1x Flag is automatically cleared when the interrupt is executed. Alternatively the OCF1x Flag can be cleared by software by writing a logical one to its I/O bit location. The Waveform Generator uses the match signal to generate an output according to operating mode set by the *Waveform Generation mode* (WGM13:0) bits and *Compare Output mode* (COM1x1:0) bits. The TOP and BOTTOM signals are used by the Waveform Generator for handling the special cases of the extreme values in some modes of operation. (See "Modes of Operation" on page 101.)

A special feature of output compare unit A allows it to define the Timer/Counter TOP value (i.e., counter resolution). In addition to the counter resolution, the TOP value defines the period time for waveforms generated by the Waveform Generator.

Figure 43 shows a block diagram of the output compare unit. The small "n" in the register and bit names indicates the device number (n = 1 for Timer/Counter1), and the "x" indicates output compare unit (A/B). The elements of the block diagram that are not directly a part of the output compare unit are gray shaded.

Figure 43. Output Compare Unit, Block Diagram

The OCR1x Register is double buffered when using any of the twelve *Pulse Width Modulation* (PWM) modes. For the Normal and *Clear Timer on Compare* (CTC) modes of operation, the double buffering is disabled. The double buffering synchronizes the update of the OCR1x Compare Register to either TOP or BOTTOM of the counting High frequency allows physically small sized external components (coils, capacitors), hence reducing total system cost.

The PWM resolution for fast PWM can be fixed to 8-, 9-, or 10-bit, or defined by either ICR1 or OCR1A. The minimum resolution allowed is 2-bit (ICR1 or OCR1A set to 0x0003), and the maximum resolution is 16-bit (ICR1 or OCR1A set to MAX). The PWM resolution can be calculated in bits by using the following equation:

$$R_{FPWM} = \frac{\log(TOP + 1)}{\log(2)}$$

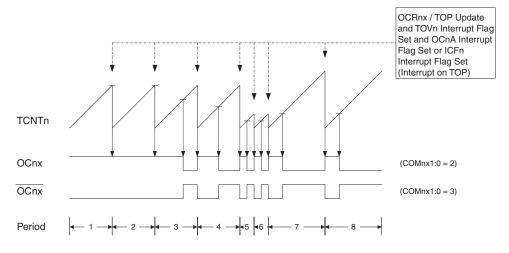

In fast PWM mode the counter is incremented until the counter value matches either one of the fixed values 0x00FF, 0x01FF, or 0x03FF (WGM13:0 = 5, 6, or 7), the value in ICR1 (WGM13:0 = 14), or the value in OCR1A (WGM13:0 = 15). The counter is then cleared at the following timer clock cycle. The timing diagram for the fast PWM mode is shown in Figure 46. The figure shows fast PWM mode when OCR1A or ICR1 is used to define TOP. The TCNT1 value is in the timing diagram shown as a histogram for illustrating the single-slope operation. The diagram includes non-inverted and inverted PWM outputs. The small horizontal line marks on the TCNT1 slopes represent compare matches between OCR1x and TCNT1. The OC1x Interrupt Flag will be set when a Compare Match occurs.

#### Figure 46. Fast PWM Mode, Timing Diagram

The Timer/Counter Overflow Flag (TOV1) is set each time the counter reaches TOP. In addition the OC1A or ICF1 Flag is set at the same timer clock cycle as TOV1 is set when either OCR1A or ICR1 is used for defining the TOP value. If one of the interrupts are enabled, the interrupt handler routine can be used for updating the TOP and compare values.

When changing the TOP value the program must ensure that the new TOP value is higher or equal to the value of all of the compare registers. If the TOP value is lower than any of the compare registers, a Compare Match will never occur between the TCNT1 and the OCR1x. Note that when using fixed TOP values the unused bits are masked to zero when any of the OCR1x Registers are written.

The procedure for updating ICR1 differs from updating OCR1A when used for defining the TOP value. The ICR1 Register is not double buffered. This means that if ICR1 is changed to a low value when the counter is running with a low or none prescaler value, there is a risk that the new ICR1 value written is lower than the current value of TCNT1. The result will then be that the counter will miss the Compare Match at the TOP value.

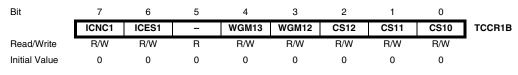

## Timer/Counter1 Control Register B – TCCR1B

## • Bit 7 – ICNC1: Input Capture Noise Canceler

Setting this bit (to one) activates the Input Capture Noise Canceler. When the Noise Canceler is activated, the input from the Input Capture Pin (ICP1) is filtered. The filter function requires four successive equal valued samples of the ICP1 pin for changing its output. The Input Capture is therefore delayed by four oscillator cycles when the noise canceler is enabled.

## • Bit 6 – ICES1: Input Capture Edge Select

This bit selects which edge on the Input Capture Pin (ICP1) is used to trigger a capture event. When the ICES1 bit is written to zero, a falling (negative) edge is used as trigger, and when the ICES1 bit is written to one, a rising (positive) edge will trigger the capture.

When a capture is triggered according to the ICES1 setting, the counter value is copied into the Input Capture Register (ICR1). The event will also set the Input Capture Flag (ICF1), and this can be used to cause an Input Capture Interrupt, if this interrupt is enabled.

When the ICR1 is used as TOP value (see description of the WGM13:0 bits located in the TCCR1A and the TCCR1B Register), the ICP1 is disconnected, and consequently, the Input Capture function is disabled.

## • Bit 5 - Reserved Bit

This bit is reserved for future use. For ensuring compatibility with future devices, this bit must be written to zero when TCCR1B is written.

• Bit 4:3 – WGM13:2: Waveform Generation Mode

See TCCR1A Register description.

Bit 2:0 – CS12:0: Clock Select

The three Clock Select bits select the clock source to be used by the Timer/Counter, see Figure 49 and Figure 50.

| CS12 | CS11 | CS10 | Description                                             |  |  |

|------|------|------|---------------------------------------------------------|--|--|

| 0    | 0    | 0    | No clock source (Timer/Counter stopped).                |  |  |

| 0    | 0    | 1    | clk <sub>I/O</sub> /1 (No prescaling)                   |  |  |

| 0    | 1    | 0    | clk <sub>I/O</sub> /8 (From prescaler)                  |  |  |

| 0    | 1    | 1    | clk <sub>I/O</sub> /64 (From prescaler)                 |  |  |

| 1    | 0    | 0    | clk <sub>I/O</sub> /256 (From prescaler)                |  |  |

| 1    | 0    | 1    | clk <sub>I/O</sub> /1024 (From prescaler)               |  |  |

| 1    | 1    | 0    | External clock source on T1 pin. Clock on falling edge. |  |  |

| 1    | 1    | 1    | External clock source on T1 pin. Clock on rising edge.  |  |  |

Table 49.

Clock Select Bit Description

If external pin modes are used for the Timer/Counter1, transitions on the T1 pin will clock the counter even if the pin is configured as an output. This feature allows software control of the counting.

down or Standby mode due to unstable clock signal upon start-up, no matter whether the Oscillator is in use or a clock signal is applied to the TOSC1 pin.

- Description of wake-up from Power-save or Extended Standby mode when the timer is clocked asynchronously: When the interrupt condition is met, the wake up process is started on the following cycle of the timer clock, that is, the timer is always advanced by at least one before the processor can read the counter value. After wake-up, the MCU is halted for four cycles, it executes the interrupt routine, and resumes execution from the instruction following SLEEP.

- Reading of the TCNT2 Register shortly after wake-up from Power-save may give an incorrect result. Since TCNT2 is clocked on the asynchronous TOSC clock, reading TCNT2 must be done through a register synchronized to the internal I/O clock domain. Synchronization takes place for every rising TOSC1 edge. When waking up from Power-save mode, and the I/O clock (clk<sub>I/O</sub>) again becomes active, TCNT2 will read as the previous value (before entering sleep) until the next rising TOSC1 edge. The phase of the TOSC clock after waking up from Power-save mode is essentially unpredictable, as it depends on the wake-up time. The recommended procedure for reading TCNT2 is thus as follows:

- 1. Write any value to either of the registers OCR2 or TCCR2.

- 2. Wait for the corresponding Update Busy Flag to be cleared.

- 3. Read TCNT2.

- During asynchronous operation, the synchronization of the interrupt flags for the asynchronous timer takes three processor cycles plus one timer cycle. The timer is therefore advanced by at least one before the processor can read the timer value causing the setting of the Interrupt Flag. The output compare pin is changed on the timer clock and is not synchronized to the processor clock.

| Timer/Counter Interrupt Mask |     |  |

|------------------------------|-----|--|

| Register – TIMSK             | Bit |  |

| Bit           | 7     | 6     | 5      | 4      | 3      | 2     | 1     | 0     | _     |

|---------------|-------|-------|--------|--------|--------|-------|-------|-------|-------|

|               | OCIE2 | TOIE2 | TICIE1 | OCIE1A | OCIE1B | TOIE1 | OCIE0 | TOIE0 | TIMSK |

| Read/Write    | R/W   | R/W   | R/W    | R/W    | R/W    | R/W   | R/W   | R/W   | 1     |

| Initial Value | 0     | 0     | 0      | 0      | 0      | 0     | 0     | 0     |       |

• Bit 7 – OCIE2: Timer/Counter2 Output Compare Match Interrupt Enable

When the OCIE2 bit is written to one and the I-bit in the Status Register is set (one), the Timer/Counter2 Compare Match interrupt is enabled. The corresponding interrupt is executed if a Compare Match in Timer/Counter2 occurs (i.e., when the OCF2 bit is set in the Timer/Counter Interrupt Flag Register – TIFR).

#### Bit 6 – TOIE2: Timer/Counter2 Overflow Interrupt Enable

When the TOIE2 bit is written to one and the I-bit in the Status Register is set (one), the Timer/Counter2 Overflow interrupt is enabled. The corresponding interrupt is executed if an overflow in Timer/Counter2 occurs (i.e., when the TOV2 bit is set in the Timer/Counter Interrupt Flag Register – TIFR).

Note: 1. See "About Code Examples" on page 7.

The receive function example reads all the I/O Registers into the Register File before any computation is done. This gives an optimal receive buffer utilization since the buffer location read will be free to accept new data as early as possible.

**Receive Compete Flag and** The USART Receiver has one flag that indicates the receiver state.

The Receive Complete (RXC) Flag indicates if there are unread data present in the receive buffer. This flag is one when unread data exist in the receive buffer and zero when the receive buffer is empty (i.e., does not contain any unread data). If the Receiver is disabled (RXEN = 0), the receive buffer will be flushed and consequently the RXC bit will become zero.

When the Receive Complete Interrupt Enable (RXCIE) in UCSRB is set, the USART Receive Complete Interrupt will be executed as long as the RXC Flag is set (provided that global interrupts are enabled). When interrupt-driven data reception is used, the receive complete routine must read the received data from UDR in order to clear the RXC Flag, otherwise a new interrupt will occur once the interrupt routine terminates.

**Receiver Error Flags** The USART Receiver has three Error Flags: Frame Error (FE), Data OverRun (DOR) and Parity Error (PE). All can be accessed by reading UCSRA. Common for the error flags is that they are located in the receive buffer together with the frame for which they indicate the error status. Due to the buffering of the error flags, the UCSRA must be read before the receive buffer (UDR), since reading the UDR I/O location changes the buffer read location. Another equality for the error flags is that they can not be altered by software doing a write to the flag location. However, all flags must be set to zero when the UCSRA is written for upward compatibility of future USART implementations. None of the error flags can generate interrupts.

The Frame Error (FE) Flag indicates the state of the first stop bit of the next readable frame stored in the receive buffer. The FE Flag is zero when the stop bit was correctly read (as one), and the FE Flag will be one when the stop bit was incorrect (zero). This flag can be used for detecting out-of-sync conditions, detecting break conditions and protocol handling. The FE Flag is not affected by the setting of the USBS bit in UCSRC since the Receiver ignores all, except for the first, stop bits. For compatibility with future devices, always set this bit to zero when writing to UCSRA.

The Data OverRun (DOR) Flag indicates data loss due to a Receiver Buffer full condition. A Data OverRun occurs when the receive buffer is full (two characters), it is a new character waiting in the receive Shift Register, and a new start bit is detected. If the DOR Flag is set there was one or more serial frame lost between the frame last read from UDR, and the next frame read from UDR. For compatibility with future devices, always write this bit to zero when writing to UCSRA. The DOR Flag is cleared when the frame received was successfully moved from the Shift Register to the receive buffer.

The Parity Error (PE) Flag indicates that the next frame in the receive buffer had a Parity Error when received. If parity check is not enabled the PE bit will always be read zero. For compatibility with future devices, always set this bit to zero when writing to UCSRA. For more details see "Parity Bit Calculation" on page 150 and "Parity Checker" on page 157.

Parity CheckerThe Parity Checker is active when the high USART Parity mode (UPM1) bit is set. The<br/>type of Parity Check to be performed (odd or even) is selected by the UPM0 bit. When<br/>enabled, the Parity Checker calculates the parity of the data bits in incoming frames and<br/>compares the result with the parity bit from the serial frame. The result of the check is

Interrupt

| Z I |  |            |

|-----|--|------------|

|     |  | <b>T</b> ® |

| Multi-processor<br>Communication Mode | Setting the Multi-processor Communication Mode (MPCM) bit in UCSRA enables a fil-<br>tering function of incoming frames received by the USART Receiver. Frames that do not<br>contain address information will be ignored and not put into the receive buffer. This<br>effectively reduces the number of incoming frames that has to be handled by the CPU,<br>in a system with multiple MCUs that communicate via the same serial bus. The Trans-<br>mitter is unaffected by the MPCM setting, but has to be used differently when it is a part<br>of a system utilizing the Multi-processor Communication Mode. |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                       | If the Receiver is set up to receive frames that contain five to eight data bits, then the first stop bit indicates if the frame contains data or address information. If the Receiver is set up for frames with nine data bits, then the ninth bit (RXB8) is used for identifying address and data frames. When the frame type bit (the first stop or the ninth bit) is one, the frame contains an address. When the frame type bit is zero the frame is a data frame.                                                                                                                                           |

|                                       | The Multi-processor Communication Mode enables several slave MCUs to receive data from a Master MCU. This is done by first decoding an address frame to find out which MCU has been addressed. If a particular Slave MCU has been addressed, it will receive the following data frames as normal, while the other Slave MCUs will ignore the received frames until another address frame is received.                                                                                                                                                                                                             |

| Using MPCM                            | For an MCU to act as a Master MCU, it can use a 9-bit character frame format $(UCSZ = 7)$ . The ninth bit (TXB8) must be set when an address frame $(TXB8 = 1)$ or cleared when a data frame $(TXB = 0)$ is being transmitted. The Slave MCUs must, in this case, be set to use a 9-bit character frame format.                                                                                                                                                                                                                                                                                                   |

|                                       | The following procedure should be used to exchange data in Multi-processor Communi-<br>cation Mode:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                       | 1. All Slave MCUs are in Multi-processor Communication Mode (MPCM in UCSRA is set).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                       | <ol> <li>The Master MCU sends an address frame, and all slaves receive and read this<br/>frame. In the Slave MCUs, the RXC Flag in UCSRA will be set as normal.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                       | 3. Each Slave MCU reads the UDR Register and determines if it has been selected. If so, it clears the MPCM bit in UCSRA, otherwise it waits for the next address byte and keeps the MPCM setting.                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                       | 4. The addressed MCU will receive all data frames until a new address frame is received. The other Slave MCUs, which still have the MPCM bit set, will ignore the data frames.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                       | 5. When the last data frame is received by the addressed MCU, the addressed MCU sets the MPCM bit and waits for a new address frame from Master. The process then repeats from 2.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                       | Using any of the 5- to 8-bit character frame formats is possible, but impractical since the Receiver must change between using n and n+1 character frame formats. This makes full-duplex operation difficult since the Transmitter and Receiver uses the same character size setting. If 5- to 8-bit character frames are used, the Transmitter must be set to use two stop bit (USBS = 1) since the first stop bit is used for indicating the frame type.                                                                                                                                                        |

|                                       | Do not use Read-Modify-Write instructions (SBI and CBI) to set or clear the MPCM bit. The MPCM bit shares the same I/O location as the TXC Flag and this might accidentally be cleared when using SBI or CBI instructions.                                                                                                                                                                                                                                                                                                                                                                                        |

|                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

This bit is used for Synchronous mode only. Write this bit to zero when asynchronous mode is used. The UCPOL bit sets the relationship between data output change and data input sample, and the synchronous clock (XCK).

Table 68. UCPOL Bit Settings

| UCPOL | Transmitted Data Changed<br>(Output of TxD Pin) | Received Data Sampled<br>(Input on RxD Pin) |

|-------|-------------------------------------------------|---------------------------------------------|

| 0     | Rising XCK Edge                                 | Falling XCK Edge                            |

| 1     | Falling XCK Edge                                | Rising XCK Edge                             |

## USART Baud Rate Registers – UBRRL and UBRRH<sup>(1)</sup>

| Bit           | 15    | 14  | 13  | 12  | 11     | 10   | 9      | 8   | _     |

|---------------|-------|-----|-----|-----|--------|------|--------|-----|-------|

|               | URSEL | -   | -   | -   |        | UBRR | [11:8] |     | UBRRH |

|               |       |     |     | UBR | R[7:0] |      |        |     | UBRRL |

|               | 7     | 6   | 5   | 4   | 3      | 2    | 1      | 0   | •     |

| Read/Write    | R/W   | R   | R   | R   | R/W    | R/W  | R/W    | R/W |       |

|               | R/W   | R/W | R/W | R/W | R/W    | R/W  | R/W    | R/W |       |

| Initial Value | 0     | 0   | 0   | 0   | 0      | 0    | 0      | 0   |       |

|               | 0     | 0   | 0   | 0   | 0      | 0    | 0      | 0   |       |

|               |       |     |     |     |        |      |        |     |       |

Note: 1. The UBRRH Register shares the same I/O location as the UCSRC Register. See the "Accessing UBRRH/UCSRC Registers" on page 163 section which describes how to access this register.

### • Bit 15 – URSEL: Register Select

This bit selects between accessing the UBRRH or the UCSRC Register. It is read as zero when reading UBRRH. The URSEL must be zero when writing the UBRRH.

#### • Bit 14:12 - Reserved Bits

These bits are reserved for future use. For compatibility with future devices, these bit must be written to zero when UBRRH is written.

### • Bit 11:0 – UBRR11:0: USART Baud Rate Register

This is a 12-bit register which contains the USART Baud Rate. The UBRRH contains the four most significant bits, and the UBRRL contains the eight least significant bits of the USART baud rate. Ongoing transmissions by the Transmitter and Receiver will be corrupted if the baud rate is changed. Writing UBRRL will trigger an immediate update of the baud rate prescaler.

## Analog-to-Digital Converter

## Features

- 10-bit Resolution

- 0.5 LSB Integral Non-linearity

- ±2 LSB Absolute Accuracy

- 65 260 µs Conversion Time

- Up to 15 kSPS at Maximum Resolution

- 8 Multiplexed Single Ended Input Channels

- 7 Differential Input Channels

- 2 Differential Input Channels with Optional Gain of 10x and 200x<sup>(1)</sup>

- Optional Left Adjustment for ADC Result Readout

- 0 V<sub>CC</sub> ADC Input Voltage Range

- Selectable 2.56V ADC Reference Voltage

- Free Running or Single Conversion Mode

- ADC Start Conversion by Auto Triggering on Interrupt Sources

- Interrupt on ADC Conversion Complete

- Sleep Mode Noise Canceler

- Note: 1. The differential input channel are not tested for devices in PDIP and PLCC Package. This feature is only guaranteed to work for devices in TQFP and QFN/MLF Packages.

The ATmega8535 features a 10-bit successive approximation ADC. The ADC is connected to an 8-channel Analog Multiplexer which allows eight single-ended voltage inputs constructed from the pins of Port A. The single-ended voltage inputs refer to 0V (GND).

The device also supports 16 differential voltage input combinations. Two of the differential inputs (ADC1, ADC0 and ADC3, ADC2) are equipped with a programmable gain stage, providing amplification steps of 0 dB (1x), 20 dB (10x), or 46 dB (200x) on the differential input voltage before the A/D conversion. Seven differential analog input channels share a common negative terminal (ADC1), while any other ADC input can be selected as the positive input terminal. If 1x or 10x gain is used, 8-bit resolution can be expected. If 200x gain is used, 7-bit resolution can be expected.

The ADC contains a Sample and Hold circuit which ensures that the input voltage to the ADC is held at a constant level during conversion. A block diagram of the ADC is shown in Figure 98.

The ADC has a separate analog supply voltage pin, AVCC. AVCC must not differ more than  $\pm 0.3V$  from V<sub>CC</sub>. See the paragraph "ADC Noise Canceler" on page 214 on how to connect this pin.

Internal reference voltages of nominally 2.56V or AVCC are provided On-chip. The voltage reference may be externally decoupled at the AREF pin by a capacitor for better noise performance.

|                       | If both ADATE and ADEN is written to one, an interrupt event can occur at any time. If the ADMUX Register is changed in this period, the user cannot tell if the next conversion is based on the old or the new settings. ADMUX can be safely updated in the following ways:<br>1. When ADATE or ADEN is cleared.                                                                                                                                                                                                                                                        |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | <ol> <li>During conversion, minimum one ADC clock cycle after the trigger event.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                       | <ol> <li>After a conversion, before the interrupt flag used as trigger source is cleared.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                       | When updating ADMUX in one of these conditions, the new settings will affect the next ADC conversion.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                       | Special care should be taken when changing differential channels. Once a differential channel has been selected, the gain stage may take as much as 125 $\mu$ s to stabilize to the new value. Thus conversions should not be started within the first 125 $\mu$ s after selecting a new differential channel. Alternatively, conversion results obtained within this period should be discarded.                                                                                                                                                                        |

|                       | The same settling time should be observed for the first differential conversion after changing ADC reference (by changing the REFS1:0 bits in ADMUX).                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ADC Input Channels    | When changing channel selections, the user should observe the following guidelines to ensure that the correct channel is selected:                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                       | In Single Conversion mode, always select the channel before starting the conversion.<br>The channel selection may be changed one ADC clock cycle after writing one to ADSC.<br>However, the simplest method is to wait for the conversion to complete before changing<br>the channel selection.                                                                                                                                                                                                                                                                          |

|                       | In Free Running mode, always select the channel before starting the first conversion. The channel selection may be changed one ADC clock cycle after writing one to ADSC. However, the simplest method is to wait for the first conversion to complete, and then change the channel selection. Since the next conversion has already started automatically, the next result will reflect the previous channel selection. Subsequent conversions will reflect the new channel selection.                                                                                  |

|                       | When switching to a differential gain channel, the first conversion result may have a poor accuracy due to the required settling time for the automatic offset cancellation circuitry. The user should preferably disregard the first conversion result.                                                                                                                                                                                                                                                                                                                 |

| ADC Voltage Reference | The reference voltage for the ADC (V <sub>REF</sub> ) indicates the conversion range for the ADC. Single ended channels that exceed V <sub>REF</sub> will result in codes close to 0x3FF. V <sub>REF</sub> can be selected as either AVCC, internal 2.56V reference, or external AREF pin.                                                                                                                                                                                                                                                                               |

|                       | AVCC is connected to the ADC through a passive switch. The internal 2.56V reference is generated from the internal bandgap reference ( $V_{BG}$ ) through an internal amplifier. In either case, the external AREF pin is directly connected to the ADC, and the reference voltage can be made more immune to noise by connecting a capacitor between the AREF pin and ground. $V_{REF}$ can also be measured at the AREF pin with a high impedant voltmeter. Note that $V_{REF}$ is a high impedant source, and only a capacitive load should be connected in a system. |

|                       | If the user has a fixed voltage source connected to the AREF pin, the user may not use<br>the other reference voltage options in the application, as they will be shorted to the<br>external voltage. If no external voltage is applied to the AREF pin, the user may switch<br>between AVCC and 2.56V as reference selection. The first ADC conversion result after<br>switching reference voltage source may be inaccurate, and the user is advised to dis-<br>card this result.                                                                                       |

| Performing Page Erase by<br>SPM                               | <ul> <li>To execute Page Erase, set up the address in the Z-pointer, write "X0000011" to SPMCR and execute SPM within four clock cycles after writing SPMCR. The data in R1 and R0 is ignored. The page address must be written to PCPAGE in the Z-register. Other bits in the Z-pointer will be ignored during this operation.</li> <li>Page Erase to the RWW section: The NRWW section can be read during the Page Erase.</li> <li>Page Erase to the NRWW section: The CPU is halted during the operation.</li> </ul>                                                                                                                                                                             |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Filling the Temporary Buffer<br>(Page Loading)                | To write an instruction word, set up the address in the Z-pointer and data in R1:R0, write<br>"00000001" to SPMCR and execute SPM within four clock cycles after writing SPMCR.<br>The content of PCWORD in the Z-register is used to address the data in the temporary<br>buffer. The temporary buffer will auto-erase after a Page Write operation or by writing<br>the RWWSRE bit in SPMCR. It is also erased after a System Reset. Note that it is not<br>possible to write more than one time to each address without erasing the temporary<br>buffer.<br>Note: If the EEPROM is written in the middle of an SPM Page Load operation, all data loaded<br>will be lost.                         |

| Performing a Page Write                                       | <ul> <li>To execute Page Write, set up the address in the Z-pointer, write "X0000101" to SPMCR and execute SPM within four clock cycles after writing SPMCR. The data in R1 and R0 is ignored. The page address must be written to PCPAGE. Other bits in the Z-pointer must be written to zero during this operation.</li> <li>Page Write to the RWW section: The NRWW section can be read during the Page Write.</li> <li>Page Write to the NRWW section: The CPU is halted during the operation.</li> </ul>                                                                                                                                                                                       |

| Using the SPM Interrupt                                       | If the SPM interrupt is enabled, the SPM interrupt will generate a constant interrupt when the SPMEN bit in SPMCR is cleared. This means that the interrupt can be used instead of polling the SPMCR Register in software. When using the SPM interrupt, the Interrupt Vectors should be moved to the BLS section to avoid that an interrupt is accessing the RWW section when it is blocked for reading. How to move the interrupts is described in "Interrupts" on page 46.                                                                                                                                                                                                                       |

| Consideration While Updating<br>BLS                           | Special care must be taken if the user allows the Boot Loader section to be updated by leaving Boot Lock bit 11 unprogrammed. An accidental write to the Boot Loader itself can corrupt the entire Boot Loader, and further software updates might be impossible. If it is not necessary to change the Boot Loader software itself, it is recommended to program the Boot Lock bit 11 to protect the Boot Loader software from any internal software changes.                                                                                                                                                                                                                                       |

| Prevent Reading the RWW<br>Section During<br>Self-Programming | During Self-Programming (either Page Erase or Page Write), the RWW section is<br>always blocked for reading. The user software itself must prevent that this section is<br>addressed during the Self-Programming operation. The RWWSB in the SPMCR will be<br>set as long as the RWW section is busy. During Self-Programming the Interrupt Vector<br>table should be moved to the BLS as described in "Interrupts" on page 46, or the inter-<br>rupts must be disabled. Before addressing the RWW section after the programming is<br>completed, the user software must clear the RWWSB by writing the RWWSRE. See<br>"Simple Assembly Code Example for a Boot Loader" on page 233 for an example. |

**Table 95.** Explanation of Different Variables used in Figure 114 and the Mapping to the Z-pointer<sup>(1)</sup>

| Variable |          | Corresponding<br>Z-value | Description                                                                                                                     |

|----------|----------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| PCMSB    | 11       |                          | Most significant bit in the Program Counter.<br>(The Program Counter is 12 bits PC[11:0])                                       |

| PAGEMSB  | 4        |                          | Most significant bit which is used to address<br>the words within one page (64 words in a page<br>requires five bits PC [4:0]). |

| ZPCMSB   |          | Z12                      | Bit in Z-register that is mapped to PCMSB.<br>Because Z0 is not used, the ZPCMSB equals<br>PCMSB + 1.                           |

| ZPAGEMSB |          | Z5                       | Bit in Z-register that is mapped to PCMSB.<br>Because Z0 is not used, the ZPAGEMSB<br>equals PAGEMSB + 1.                       |

| PCPAGE   | PC[11:5] | Z12:Z6                   | Program Counter page address: Page select, for Page Erase and Page Write                                                        |

| PCWORD   | PC[4:0]  | Z5:Z1                    | Program Counter word address: Word select,<br>for filling temporary buffer (must be zero during<br>page write operation)        |

Note: 1. Z15:Z13: always ignored

Z0: should be zero for all SPM commands, byte select for the LPM instruction. See "Addressing the Flash during Self-Programming" on page 229 for details about the use of Z-pointer during Self-Programming.

## Table 109. Serial Programming Instruction Set

a = address high bits, b = address low bits, H = 0 - Low byte, 1 - High Byte, o = data out, i = data in, x = don't care

|                              |                   | Instructio        |                   |                   |                                                                                                                                                                                                 |  |  |

|------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Instruction                  | Byte 1            | Byte 2            | Byte 2 Byte 3     |                   | Operation                                                                                                                                                                                       |  |  |

| Programming Enable           | 1010 1100         | 0101 0011         | XXXX XXXX         | XXXX XXXX         | Enable Serial Programming after RESET goes low.                                                                                                                                                 |  |  |

| Chip Erase                   | 1010 1100         | 100x xxxx         | xxxx xxxx         | XXXX XXXX         | Chip Erase EEPROM and Flash.                                                                                                                                                                    |  |  |

| Read Program Memory          | 0010 <b>H</b> 000 | 0000 <b>aaaa</b>  | bbbb bbbb         | 0000 0000         | Read <b>H</b> (high or low) data <b>o</b> from<br>Program memory at word address<br><b>a</b> : <b>b</b> .                                                                                       |  |  |

| Load Program Memory<br>Page  | 0100 <b>H</b> 000 | 0000 xxxx         | xxxb bbbb         | 1111 1111         | Write <b>H</b> (high or low) data <b>i</b> to<br>Program Memory page at word<br>address <b>b</b> . Data low byte must be<br>loaded before Data high byte is<br>applied within the same address. |  |  |

| Write Program Memory<br>Page | 0100 1100         | 0000 <b>aaaa</b>  | bbbx xxxx         | XXXX XXXX         | Write Program Memory Page at address <b>a</b> : <b>b</b> .                                                                                                                                      |  |  |

| Read EEPROM Memory           | 1010 0000         | 00xx xxx <b>a</b> | bbbb bbbb         | 0000 0000         | Read data <b>o</b> from EEPROM memory at address <b>a:b</b> .                                                                                                                                   |  |  |

| Write EEPROM Memory          | 1100 0000         | 00xx xxx <b>a</b> | bbbb bbbb         | 1111 1111         | Write data <b>i</b> to EEPROM memory at address <b>a</b> : <b>b</b> .                                                                                                                           |  |  |

| Read Lock Bits               | 0101 1000         | 0000 0000         | XXXX XXXX         | xx <b>oo oooo</b> | Read Lock bits. "0" = programmed<br>"1" = unprogrammed. See Table<br>96 on page 237 for details.                                                                                                |  |  |

| Write Lock Bits              | 1010 1100         | 111x xxxx         | XXXX XXXX         | 1111 1111         | Write Lock bits. Set bits = "0" to<br>program Lock bits. See Table 96<br>on page 237 for details.                                                                                               |  |  |

| Read Signature Byte          | 0011 0000         | 00xx xxxx         | xxxx xxbb         | 0000 0000         | Read Signature Byte <b>o</b> at address <b>b</b> .                                                                                                                                              |  |  |

| Write Fuse Bits              | 1010 1100         | 1010 0000         | XXXX XXXX         | 1111 1111         | Set bits = "0" to program, "1" to<br>unprogram. See Table 99 on<br>page 239 for details.                                                                                                        |  |  |

| Write Fuse High Bits         | 1010 1100         | 1010 1000         | XXXX XXXX         | 1111 1111         | Set bits = "0" to program, "1" to<br>unprogram. See Table 98 on<br>page 238 for details.                                                                                                        |  |  |

| Read Fuse Bits               | 0101 0000         | 0000 0000         | XXXX XXXX         | 0000 0000         | Read Fuse bits. "0" = programmed<br>"1" = unprogrammed. See Table<br>99 on page 239 for details.                                                                                                |  |  |

| Read Fuse High Bits          | 0101 1000         | 0000 1000         | XXXX XXXX         | 0000 0000         | Read Fuse high bits. "0" = pro-<br>grammed, "1" = unprogrammed.<br>See Table 98 on page 238 for<br>details.                                                                                     |  |  |

| Read Calibration Byte        | 0011 1000         | 00xx xxxx         | 0000 00 <b>bb</b> | 0000 0000         | Read Calibration Byte                                                                                                                                                                           |  |  |

SPI Serial Programming Characteristics For characteristics of the SPI module, see "SPI Timing Characteristics" on page 261.

## **Two-wire Serial Interface Characteristics**

Table 112 describes the requirements for devices connected to the Two-wire Serial Bus. The ATmega8535 Two-wire Serial Interface meets or exceeds these requirements under the noted conditions.

Timing symbols refer to Figure 127.

|  | Table 112. | Two-wire Serial | Bus Rec | uirements |

|--|------------|-----------------|---------|-----------|

|--|------------|-----------------|---------|-----------|

| Symbol                        | Parameter                                                      | Condition                                      | Min                                 | Max                          | Units |

|-------------------------------|----------------------------------------------------------------|------------------------------------------------|-------------------------------------|------------------------------|-------|

| VIL                           | Input Low Voltage                                              |                                                | -0.5                                | $0.3 V_{CC}$                 | V     |

| VIH                           | Input High Voltage                                             |                                                | 0.7 V <sub>CC</sub>                 | V <sub>CC</sub> + 0.5        | V     |

| (1)<br>Vhys                   | Hysteresis of Schmitt Trigger Inputs                           |                                                | 0.05 V <sub>CC</sub> <sup>(2)</sup> | _                            | V     |

| VOL <sup>(1)</sup>            | Output Low Voltage                                             | 3 mA sink current                              | 0                                   | 0.4                          | V     |

| (1)<br>tr                     | Rise Time for both SDA and SCL                                 |                                                | $20 + 0.1C_{b}^{(3)(2)}$            | 300                          | ns    |

| (1)<br>tof                    | Output Fall Time from V <sub>IHmin</sub> to V <sub>ILmax</sub> | 10 pF < C <sub>b</sub> < 400 pF <sup>(3)</sup> | $20 + 0.1C_{b}^{(3)(2)}$            | 250                          | ns    |

| tSP <sup>(1)</sup>            | Spikes Suppressed by Input Filter                              |                                                | 0                                   | 50 <sup>(2)</sup>            | ns    |

| l <sub>i</sub>                | Input Current each I/O Pin                                     | $0.1V_{\rm CC} < V_{\rm i} < 0.9V_{\rm CC}$    | -10                                 | 10                           | μA    |

| C <sub>i</sub> <sup>(1)</sup> | Capacitance for each I/O Pin                                   |                                                | _                                   | 10                           | pF    |

| f <sub>SCL</sub>              | SCL Clock Frequency                                            | $f_{CK}^{(4)} > max(16f_{SCL}, 250kHz)^{(5)}$  | 0                                   | 400                          | kHz   |

| _                             |                                                                | $f_{SCL} \le 100 \text{ kHz}$                  | $\frac{V_{CC} - 0.4V}{3mA}$         | $\frac{1000 \text{ns}}{C_b}$ | Ω     |

| Rp                            | Value of Pull-up resistor                                      | f <sub>SCL</sub> > 100 kHz                     | $\frac{V_{CC} - 0.4V}{3mA}$         | $\frac{300 \text{ns}}{C_b}$  | Ω     |

|                               |                                                                | $f_{SCL} \le 100 \text{ kHz}$                  | 4.0                                 | _                            | μs    |

| t <sub>HD;STA</sub>           | Hold Time (Repeated) START Condition                           | f <sub>SCL</sub> > 100 kHz                     | 0.6                                 | _                            | μs    |

|                               | Law Daviad of the COL Clash                                    | $f_{SCL} \le 100 \text{ kHz}^{(6)}$            | 4.7                                 | _                            | μs    |

| t <sub>LOW</sub>              | Low Period of the SCL Clock                                    | f <sub>SCL</sub> > 100 kHz <sup>(7)</sup>      | 1.3                                 | _                            | μs    |

|                               |                                                                | f <sub>SCL</sub> ≤ 100 kHz                     | 4.0                                 | _                            | μs    |

| t <sub>HIGH</sub>             | High Period of the SCL clock                                   | f <sub>SCL</sub> > 100 kHz                     | 0.6                                 | _                            | μs    |

|                               | Set-up Time for a Repeated START                               | f <sub>SCL</sub> ≤ 100 kHz                     | 4.7                                 | _                            | μs    |

| t <sub>SU;STA</sub>           | Condition                                                      | f <sub>SCL</sub> > 100 kHz                     | 0.6                                 | _                            | μs    |

|                               | Data hal d Tima                                                | $f_{SCL} \le 100 \text{ kHz}$                  | 0                                   | 3.45                         | μs    |

| t <sub>HD;DAT</sub>           | Data hoLd Time                                                 | f <sub>SCL</sub> > 100 kHz                     | 0                                   | 0.9                          | μs    |

|                               | Data Catura Tima                                               | $f_{SCL} \le 100 \text{ kHz}$                  | 250                                 | _                            | ns    |

| t <sub>SU;DAT</sub>           | Data Setup Time                                                | f <sub>SCL</sub> > 100 kHz                     | 100                                 | _                            | ns    |

| •                             | Setup Time for STOP Condition                                  | f <sub>SCL</sub> ≤ 100 kHz                     | 4.0                                 | _                            | μs    |

| t <sub>SU;STO</sub>           | Setup Time for STOP Condition                                  | f <sub>SCL</sub> > 100 kHz                     | 0.6                                 | _                            | μs    |

|                               | Bus Free Time between a STOP and START                         | $f_{SCL} \le 100 \text{ kHz}$                  | 4.7                                 | _                            | μs    |

| t <sub>BUF</sub>              | Condition                                                      | f <sub>SCL</sub> > 100 kHz                     | 1.3                                 | _                            | μs    |

Notes: 1. In ATmega8535, this parameter is characterized and not 100% tested.

2. Required only for  $f_{SCL} > 100$  kHz. 3.  $C_b$  = capacitance of one bus line in pF.

## **Register Summary**

| -                                                        |                        | _               |                 |                 |                 |                    |                 |                 |               | -                 |

|----------------------------------------------------------|------------------------|-----------------|-----------------|-----------------|-----------------|--------------------|-----------------|-----------------|---------------|-------------------|

| Address                                                  | Name                   | Bit 7           | Bit 6           | Bit 5           | Bit 4           | Bit 3              | Bit 2           | Bit 1           | Bit 0         | Page              |

| 0x3F (0x5F)                                              | SREG                   | 1               | Т               | Н               | S               | V                  | N               | Z               | С             | 10                |

| 0x3E (0x5E)                                              | SPH                    | -               | -               | -               | -               | -                  | -               | SP9             | SP8           | 12                |

| 0x3D (0x5D)                                              | SPL                    | SP7             | SP6             | SP5             | SP4             | SP3                | SP2             | SP1             | SP0           | 12                |

| 0x3C (0x5C)                                              | OCR0                   |                 |                 | Ti              | mer/Counter0 Ou | tput Compare Re    | gister          |                 |               | 85                |

| 0x3B (0x5B)                                              | GICR                   | INT1            | INT0            | INT2            | -               | -                  | -               | IVSEL           | IVCE          | 49, 69            |

| 0x3A (0x5A)                                              | GIFR                   | INTF1           | INTF0           | INTF2           | -               | -                  | -               | -               | -             | 70                |

| 0x39 (0x59)                                              | TIMSK                  | OCIE2           | TOIE2           | TICIE1          | OCIE1A          | OCIE1B             | TOIE1           | OCIE0           | TOIE0         | 85, 115, 133      |

| 0x38 (0x58)                                              | TIFR                   | OCF2            | TOV2            | ICF1            | OCF1A           | OCF1B              | TOV1            | OCF0            | TOV0          | 86, 116, 134      |

| 0x37 (0x57)                                              | SPMCR                  | SPMIE           | RWWSB           | -               | RWWSRE          | BLBSET             | PGWRT           | PGERS           | SPMEN         | 228               |