### Intel - HC1S40F780NAD Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Obsolete                                                 |

|--------------------------------|----------------------------------------------------------|

| Number of LABs/CLBs            | 4125                                                     |

| Number of Logic Elements/Cells | 41250                                                    |

| Total RAM Bits                 | 2244096                                                  |

| Number of I/O                  | 613                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.425V ~ 1.575V                                          |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | -                                                        |

| Package / Case                 | 780-BBGA, FCBGA                                          |

| Supplier Device Package        | 780-FBGA (29x29)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/hc1s40f780nad |

|                                |                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 2–1 illustrates the differences between HardCopy Stratix and Stratix devices.

ć

| Table 2–1. HardCopy Stratix and Stratix Device Comparison (Part 1 of 2)                                                                                     |                                                                                                                                                             |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| HardCopy Stratix                                                                                                                                            | Stratix                                                                                                                                                     |  |  |  |  |  |

| Customized device. All reprogrammability support is removed and no configuration is required.                                                               | Re-programmable with configuration is required upon power-up.                                                                                               |  |  |  |  |  |

| Average of 50% performance<br>improvement over corresponding<br>FPGA (1).                                                                                   | High-performance FPGA.                                                                                                                                      |  |  |  |  |  |

| Average of 40% less power<br>consumption compared to<br>corresponding FPGA (1).                                                                             | Standard FPGA power consumption.                                                                                                                            |  |  |  |  |  |

| Contact Altera for information regarding specific IP support.                                                                                               | IP support for all devices is available.                                                                                                                    |  |  |  |  |  |

| Double data rate (DDR) SDRAM<br>maximum operating frequency is<br>pending characterization.                                                                 | DDR SDRAM can operate at 200 MHz for -5 speed grade devices.                                                                                                |  |  |  |  |  |

| All routing connections are direct and all unused routing is removed.                                                                                       | MultiTrack™ routing stitches together routing resources to provide a path.                                                                                  |  |  |  |  |  |

| HC1S30 and HC1S40 devices have<br>two M-RAM blocks. HC1S80 devices<br>have six M-RAM blocks.                                                                | EP1S30 and EP1S40 devices have four<br>M-RAM blocks. EP1S80 devices have<br>nine M-RAM blocks.                                                              |  |  |  |  |  |

| It is not possible to initialize M512 and M4K RAM contents during power-up.                                                                                 | The contents of M512 and M4K RAM<br>blocks can be preloaded during<br>configuration with data specified in a<br>memory initialization file ( <b>.mif</b> ). |  |  |  |  |  |

| The contents of memory output registers are unknown after power-on reset (POR).                                                                             | The contents of memory output registers are initialized to '0' after POR.                                                                                   |  |  |  |  |  |

| HC1S30 and HC1S40 devices have six PLLs.                                                                                                                    | HC1S30 devices have 10 PLLs.<br>HC1S40 devices have 12 PLLs.                                                                                                |  |  |  |  |  |

| PLL dynamic reconfiguration uses<br>ROM for information. This<br>reconfiguration is performed in the<br>back-end and does not affect the<br>migration flow. | PLL dynamic reconfiguration uses a MIF to initialize a RAM resource with information.                                                                       |  |  |  |  |  |

| The I/O elements (IOEs) are equivalent<br>but not identical to FPGA IOEs due to<br>slight design optimizations for<br>HardCopy devices.                     | The IOEs are optimized for the FPGA architecture.                                                                                                           |  |  |  |  |  |

Although memory resource implementation is equivalent, the number of specific M-RAM blocks are not necessarily the same between corresponding Stratix and HardCopy Stratix devices. Table 2–3 shows the number of M-RAM blocks available in each device.

| Table 2–3. HardCopy Stratix and Stratix M-RAM Block Comparison |              |         |              |  |  |

|----------------------------------------------------------------|--------------|---------|--------------|--|--|

| HardCopy Stratix                                               |              | Stratix |              |  |  |

| Device                                                         | M-RAM Blocks | Device  | M-RAM Blocks |  |  |

| HC1S25                                                         | 2            | EP1S25  | 2            |  |  |

| HC1S30                                                         | 2            | EP1S30  | 4            |  |  |

| HC1S40                                                         | 2            | EP1S40  | 4            |  |  |

| HC1S60                                                         | 6            | EP1S60  | 6            |  |  |

| HC1S830                                                        | 6            | EP1S830 | 9            |  |  |

In HardCopy Stratix devices, it is not possible to preload RAM contents using a MIF after powering up; the output registers of memory blocks will have unknown values. This occurs because there is no configuration process that is executed.

Violating the setup or hold time requirements on address registers could corrupt the memory contents. This requirement applies to both read and write operations.

Table 2–4 illustrates the differences between HardCopy Stratix and Stratix memory.

| Table 2–4. HardCopy Stratix and Stratix Memory Comparison                                    |                                                                                                                      |  |  |  |  |

|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| HardCopy Stratix                                                                             | Stratix                                                                                                              |  |  |  |  |

| HC1S30 and HC1S40 devices have<br>two M-RAM blocks. HC1S80 devices<br>have six M-RAM blocks. | EP1S30 and EP1S40 devices have four<br>M-RAM blocks. EP1S80 devices have<br>nine M-RAM blocks.                       |  |  |  |  |

| It is not possible to initialize M512 and M4k RAM contents during power-up.                  | The contents of M512 and M4K RAM<br>blocks can be preloaded during<br>configuration with data specified in a<br>MIF. |  |  |  |  |

| The contents of memory output registers are unknown after POR.                               | The contents of memory output registers are initialized to '0' after POR.                                            |  |  |  |  |

- In instant on mode, the HardCopy Stratix device is available for use shortly after the device receives power. The on-chip POR circuit resets all registers. The CONF\_DONE output is tri-stated once the POR has elapsed. No configuration device or configuration data is necessary.

- In instant on after 50 ms mode, the HardCopy Stratix device performs in a fashion similar to the instant on mode, except that there is an additional delay of 50 ms, during which time the device is held in reset stage. The CONF\_DONE output is pulled low during this time, and then tri-stated after the 50 ms have elapsed. No configuration device or configuration data is necessary for this option.

- In configuration emulation mode, the HardCopy series device emulates the behavior of an APEX or Stratix FPGA during its configuration phase. When this mode is used, the HardCopy device uses a configuration emulation circuit to receive configuration bit streams. When all the configuration data is received, the HardCopy series device transitions into an initialization phase and releases the CONF\_DONE pin to be pulled high. Pulling the CONF\_DONE pin high signals that the HardCopy series device is ready for normal operation. If the optional open-drain INIT\_DONE output is used, the normal operation is delayed until this signal is released by the HardCopy series device.

- HardCopy II and some HardCopy Stratix devices do not support configuration emulation mode.

Instant on and instant on after 50 ms modes are the recommended power-up modes because these modes are similar to an ASIC's functionality upon power-up. No changes to the existing board design or the configuration software are required.

All three modes provide significant benefits to system designers. They enable seamless migration of the design from the FPGA device to the HardCopy device with no changes to the existing board design or the configuration software. The pull-up resistors on *n*CONFIG, *n*STATUS, and CONF DONE should be left on the printed circuit board.

For more information, refer to the *HardCopy Series Configuration Emulation* chapter in the *HardCopy Series Handbook*.

### **Hot Socketing**

HardCopy Stratix devices support hot socketing without any external components. In a hot socketing situation, a device's output buffers are turned off during system power up or power down. To simplify board design, HardCopy Stratix devices support any power-up or power-down sequence ( $V_{CCIO}$  and  $V_{CCINT}$ ). For mixed-voltage environments, you can

| Table 4-          | Table 4–3. HardCopy Stratix Device DC Operating Conditions       Note (7)                         |                                                         |         |         |         |      |  |  |

|-------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------|---------|---------|---------|------|--|--|

| Symbol            | Parameter                                                                                         | Conditions                                              | Minimum | Typical | Maximum | Unit |  |  |

| I <sub>I</sub>    | Input pin leakage current                                                                         | $V_I = V_{CCIOmax}$ to 0 V (8)                          | -10     |         | 10      | μA   |  |  |

| I <sub>OZ</sub>   | Tri-stated I/O pin leakage current                                                                | $V_{O} = V_{CCIOmax}$ to 0 V<br>(8)                     | -10     |         | 10      | μA   |  |  |

| I <sub>CC0</sub>  | V <sub>CC</sub> supply current<br>(standby) (All memory<br>blocks in power-down<br>mode)          | V <sub>I</sub> = ground, no load,<br>no toggling inputs |         |         |         | mA   |  |  |

| R <sub>CONF</sub> | Value of I/O pin pull-up                                                                          | Vi=0; V <sub>CCIO</sub> = 3.3 V <i>(9)</i>              | 15      | 25      | 50      | kΩ   |  |  |

|                   | resistor before and<br>during configuration                                                       | Vi=0; V <sub>CCIO</sub> = 2.5 V <i>(9)</i>              | 20      | 45      | 70      | kΩ   |  |  |

|                   | gg                                                                                                | Vi=0; V <sub>CCIO</sub> = 1.8 V (9)                     | 30      | 65      | 100     | kΩ   |  |  |

|                   |                                                                                                   | Vi=0; V <sub>CCIO</sub> = 1.5 V (9)                     | 50      | 100     | 150     | kΩ   |  |  |

|                   | Recommended value of<br>I/O pin external<br>pull-down resistor before<br>and during configuration |                                                         |         | 1       | 2       | kΩ   |  |  |

#### Notes to Tables 4–1 through 4–3:

- (1) Refer to the Operating Requirements for Altera Devices Data Sheet.

- (2) Conditions beyond those listed in Table 4–1 may cause permanent damage to a device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse affects on the device.

- (3) Minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2 V or overshoot to 4.6 V for input currents less than 100 mA and periods shorter than 20 ns.

- (4) Maximum  $V_{CC}$  rise time is 100 ms, and  $V_{CC}$  must rise monotonically.

- (5) V<sub>CCIO</sub> maximum and minimum conditions for LVPECL, LVDS, and 3.3-V PCML are shown in parentheses.

- (6) All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before V<sub>CCINT</sub> and V<sub>CCIO</sub> are powered.

- (7) Typical values are for  $T_A = 25 \text{ °C}$ ,  $V_{CCINT} = 1.5 \text{ V}$ , and  $V_{CCIO} = 1.5 \text{ V}$ , 1.8 V, 2.5 V, and 3.3 V.

- (8) This value is specified for normal device operation. The value may vary during power up. This applies for all V<sub>CCIO</sub> settings (3.3, 2.5, 1.8, and 1.5 V).

- (9) Pin pull-up resistance values will be lower if an external source drives the pin higher than V<sub>CCIO</sub>.

| Table 4-                | Table 4–10. 3.3-V PCML Specifications             |            |         |                   |         |      |  |  |

|-------------------------|---------------------------------------------------|------------|---------|-------------------|---------|------|--|--|

| Symbol                  | Parameter                                         | Conditions | Minimum | Typical           | Maximum | Unit |  |  |

| V <sub>CCIO</sub>       | I/O supply voltage                                |            | 3.135   | 3.3               | 3.465   | V    |  |  |

| V <sub>ID</sub>         | Input differential voltage swing                  |            | 300     |                   | 600     | mV   |  |  |

| V <sub>ICM</sub>        | Input common mode voltage                         |            | 1.5     |                   | 3.465   | V    |  |  |

| V <sub>OD</sub>         | Output differential voltage                       |            | 300     | 370               | 500     | mV   |  |  |

| $\Delta V_{OD}$         | Change in V <sub>OD</sub> between<br>high and low |            |         |                   | 50      | mV   |  |  |

| V <sub>OCM</sub>        | Output common mode voltage                        |            | 2.5     | 2.85              | 3.3     | V    |  |  |

| $\Delta V_{\text{OCM}}$ | Change in V <sub>OCM</sub> between high and low   |            |         |                   | 50      | mV   |  |  |

| V <sub>T</sub>          | Output termination voltage                        |            |         | V <sub>CCIO</sub> |         | V    |  |  |

| R <sub>1</sub>          | Output external pull-up resistors                 |            | 45      | 50                | 55      | Ω    |  |  |

| R <sub>2</sub>          | Output external pull-up resistors                 |            | 45      | 50                | 55      | Ω    |  |  |

| Table 4–11. LVPECL Specifications |                                      |                        |         |         |         |      |  |

|-----------------------------------|--------------------------------------|------------------------|---------|---------|---------|------|--|

| Symbol                            | Parameter                            | Conditions             | Minimum | Typical | Maximum | Unit |  |

| V <sub>CCIO</sub>                 | I/O supply voltage                   |                        | 3.135   | 3.3     | 3.465   | V    |  |

| V <sub>ID</sub>                   | Input differential voltage swing     |                        | 300     |         | 1,000   | mV   |  |

| V <sub>ICM</sub>                  | Input common mode<br>voltage         |                        | 1       |         | 2       | V    |  |

| V <sub>OD</sub>                   | Output differential voltage          | R <sub>L</sub> = 100 Ω | 525     | 700     | 970     | mV   |  |

| V <sub>OCM</sub>                  | Output common mode voltage           | R <sub>L</sub> = 100 Ω | 1.5     | 1.7     | 1.9     | V    |  |

| RL                                | Receiver differential input resistor |                        | 90      | 100     | 110     | Ω    |  |

| Table 4–22. SSTL-3 Class II Specifications (Part 2 of 2) |                             |                                     |                        |         |                        |      |  |

|----------------------------------------------------------|-----------------------------|-------------------------------------|------------------------|---------|------------------------|------|--|

| Symbol                                                   | Parameter                   | Conditions                          | Minimum                | Typical | Maximum                | Unit |  |

| V <sub>IH(DC)</sub>                                      | High-level DC input voltage |                                     | V <sub>REF</sub> + 0.2 |         | $V_{\rm CCIO}$ + 0.3   | V    |  |

| V <sub>IL(DC)</sub>                                      | Low-level DC input voltage  |                                     | -0.3                   |         | V <sub>REF</sub> - 0.2 | V    |  |

| V <sub>IH(AC)</sub>                                      | High-level AC input voltage |                                     | V <sub>REF</sub> + 0.4 |         |                        | V    |  |

| V <sub>IL(AC)</sub>                                      | Low-level AC input voltage  |                                     |                        |         | V <sub>REF</sub> - 0.4 | V    |  |

| V <sub>OH</sub>                                          | High-level output voltage   | I <sub>OH</sub> = -16 mA <i>(1)</i> | V <sub>TT</sub> + 0.8  |         |                        | V    |  |

| V <sub>OL</sub>                                          | Low-level output voltage    | I <sub>OL</sub> = 16 mA <i>(1)</i>  |                        |         | V <sub>TT</sub> - 0.8  | V    |  |

| Table 4–23. 3.3-V AGP 2× Specifications |                              |                            |                       |         |                               |      |  |

|-----------------------------------------|------------------------------|----------------------------|-----------------------|---------|-------------------------------|------|--|

| Symbol                                  | Parameter                    | Conditions                 | Minimum               | Typical | Maximum                       | Unit |  |

| V <sub>CCIO</sub>                       | Output supply voltage        |                            | 3.15                  | 3.3     | 3.45                          | V    |  |

| V <sub>REF</sub>                        | Reference voltage            |                            | $0.39 	imes V_{CCIO}$ |         | $0.41 \times V_{\text{CCIO}}$ | V    |  |

| V <sub>IH</sub>                         | High-level input voltage (4) |                            | $0.5 	imes V_{CCIO}$  |         | V <sub>CCIO</sub> + 0.5       | V    |  |

| V <sub>IL</sub>                         | Low-level input voltage      |                            |                       |         | $0.3 \times V_{CCIO}$         | V    |  |

| V <sub>OH</sub>                         | High-level output voltage    | I <sub>OUT</sub> = -0.5 mA | $0.9 	imes V_{CCIO}$  |         | 3.6                           | V    |  |

| V <sub>OL</sub>                         | Low-level output voltage     | I <sub>OUT</sub> = 1.5 mA  |                       |         | $0.1\times V_{\text{CCIO}}$   | V    |  |

| Table 4–24. 3.3-V AGP 1× Specifications |                              |                            |                      |         |                         |      |  |

|-----------------------------------------|------------------------------|----------------------------|----------------------|---------|-------------------------|------|--|

| Symbol                                  | Parameter                    | Conditions                 | Minimum              | Typical | Maximum                 | Unit |  |

| V <sub>CCIO</sub>                       | Output supply voltage        |                            | 3.15                 | 3.3     | 3.45                    | V    |  |

| V <sub>IH</sub>                         | High-level input voltage (4) |                            | $0.5 	imes V_{CCIO}$ |         | V <sub>CCIO</sub> + 0.5 | V    |  |

| V <sub>IL</sub>                         | Low-level input voltage (4)  |                            |                      |         | $0.3 	imes V_{CCIO}$    | V    |  |

| V <sub>OH</sub>                         | High-level output voltage    | I <sub>OUT</sub> = -0.5 mA | $0.9 	imes V_{CCIO}$ |         | 3.6                     | V    |  |

| V <sub>OL</sub>                         | Low-level output voltage     | I <sub>OUT</sub> = 1.5 mA  |                      |         | $0.1 	imes V_{CCIO}$    | V    |  |

| Table 4–25. 1.5-V HSTL Class I Specifications |                             |                             |                         |         |                        |      |  |

|-----------------------------------------------|-----------------------------|-----------------------------|-------------------------|---------|------------------------|------|--|

| Symbol                                        | Parameter                   | Conditions                  | Minimum                 | Typical | Maximum                | Unit |  |

| V <sub>CCIO</sub>                             | Output supply voltage       |                             | 1.4                     | 1.5     | 1.6                    | V    |  |

| $V_{REF}$                                     | Input reference voltage     |                             | 0.68                    | 0.75    | 0.9                    | V    |  |

| V <sub>TT</sub>                               | Termination voltage         |                             | 0.7                     | 0.75    | 0.8                    | V    |  |

| V <sub>IH</sub> (DC)                          | DC high-level input voltage |                             | V <sub>REF</sub> + 0.1  |         |                        | V    |  |

| V <sub>IL</sub> (DC)                          | DC low-level input voltage  |                             | -0.3                    |         | V <sub>REF</sub> - 0.1 | V    |  |

| V <sub>IH</sub> (AC)                          | AC high-level input voltage |                             | V <sub>REF</sub> + 0.2  |         |                        | V    |  |

| V <sub>IL</sub> (AC)                          | AC low-level input voltage  |                             |                         |         | V <sub>REF</sub> - 0.2 | V    |  |

| V <sub>OH</sub>                               | High-level output voltage   | I <sub>OH</sub> = 8 mA (1)  | V <sub>CCIO</sub> - 0.4 |         |                        | V    |  |

| V <sub>OL</sub>                               | Low-level output voltage    | I <sub>OH</sub> = -8 mA (1) |                         |         | 0.4                    | V    |  |

| Table 4-             | Table 4–26. 1.5-V HSTL Class II Specifications |                                     |                         |         |                        |      |  |  |

|----------------------|------------------------------------------------|-------------------------------------|-------------------------|---------|------------------------|------|--|--|

| Symbol               | Parameter                                      | Conditions                          | Minimum                 | Typical | Maximum                | Unit |  |  |

| V <sub>CCIO</sub>    | Output supply voltage                          |                                     | 1.4                     | 1.5     | 1.6                    | V    |  |  |

| $V_{REF}$            | Input reference voltage                        |                                     | 0.68                    | 0.75    | 0.9                    | V    |  |  |

| V <sub>TT</sub>      | Termination voltage                            |                                     | 0.7                     | 0.75    | 0.8                    | V    |  |  |

| V <sub>IH</sub> (DC) | DC high-level input<br>voltage                 |                                     | V <sub>REF</sub> + 0.1  |         |                        | V    |  |  |

| V <sub>IL</sub> (DC) | DC low-level input voltage                     |                                     | -0.3                    |         | V <sub>REF</sub> - 0.1 | V    |  |  |

| V <sub>IH</sub> (AC) | AC high-level input voltage                    |                                     | V <sub>REF</sub> + 0.2  |         |                        | V    |  |  |

| V <sub>IL</sub> (AC) | AC low-level input voltage                     |                                     |                         |         | V <sub>REF</sub> - 0.2 | V    |  |  |

| V <sub>OH</sub>      | High-level output voltage                      | I <sub>OH</sub> = 16 mA <i>(1)</i>  | V <sub>CCIO</sub> - 0.4 |         |                        | V    |  |  |

| V <sub>OL</sub>      | Low-level output voltage                       | I <sub>OH</sub> = -16 mA <i>(1)</i> |                         |         | 0.4                    | V    |  |  |

| Table 4-,            | Table 4–27. 1.8-V HSTL Class I Specifications |                             |                         |                             |                        |      |

|----------------------|-----------------------------------------------|-----------------------------|-------------------------|-----------------------------|------------------------|------|

| Symbol               | Parameter                                     | Conditions                  | Minimum                 | Typical                     | Maximum                | Unit |

| V <sub>CCIO</sub>    | Output supply voltage                         |                             | 1.65                    | 1.80                        | 1.95                   | V    |

| $V_{REF}$            | Input reference voltage                       |                             | 0.70                    | 0.90                        | 0.95                   | V    |

| V <sub>TT</sub>      | Termination voltage                           |                             |                         | $V_{\text{CCIO}} 	imes 0.5$ |                        | V    |

| V <sub>IH</sub> (DC) | DC high-level input voltage                   |                             | V <sub>REF</sub> + 0.1  |                             |                        | V    |

| V <sub>IL</sub> (DC) | DC low-level input voltage                    |                             | -0.5                    |                             | V <sub>REF</sub> – 0.1 | V    |

| V <sub>IH</sub> (AC) | AC high-level input voltage                   |                             | V <sub>REF</sub> + 0.2  |                             |                        | V    |

| V <sub>IL</sub> (AC) | AC low-level input voltage                    |                             |                         |                             | V <sub>REF</sub> – 0.2 | V    |

| V <sub>OH</sub>      | High-level output voltage                     | I <sub>OH</sub> = 8 mA (1)  | V <sub>CCIO</sub> - 0.4 |                             |                        | V    |

| V <sub>OL</sub>      | Low-level output voltage                      | I <sub>OH</sub> = -8 mA (1) |                         |                             | 0.4                    | V    |

| Table 4-             | Table 4–28. 1.8-V HSTL Class II Specifications |                                     |                         |                      |                        |      |

|----------------------|------------------------------------------------|-------------------------------------|-------------------------|----------------------|------------------------|------|

| Symbol               | Parameter                                      | Conditions                          | Minimum                 | Typical              | Maximum                | Unit |

| V <sub>CCIO</sub>    | Output supply voltage                          |                                     | 1.65                    | 1.80                 | 1.95                   | V    |

| V <sub>REF</sub>     | Input reference voltage                        |                                     | 0.70                    | 0.90                 | 0.95                   | V    |

| V <sub>TT</sub>      | Termination voltage                            |                                     |                         | $V_{CCIO} 	imes 0.5$ |                        | V    |

| V <sub>IH</sub> (DC) | DC high-level input<br>voltage                 |                                     | V <sub>REF</sub> + 0.1  |                      |                        | V    |

| V <sub>IL</sub> (DC) | DC low-level input<br>voltage                  |                                     | -0.5                    |                      | V <sub>REF</sub> – 0.1 | V    |

| V <sub>IH</sub> (AC) | AC high-level input voltage                    |                                     | V <sub>REF</sub> + 0.2  |                      |                        | V    |

| V <sub>IL</sub> (AC) | AC low-level input voltage                     |                                     |                         |                      | V <sub>REF</sub> - 0.2 | V    |

| V <sub>OH</sub>      | High-level output voltage                      | I <sub>OH</sub> = 16 mA <i>(1)</i>  | V <sub>CCIO</sub> - 0.4 |                      |                        | V    |

| V <sub>OL</sub>      | Low-level output voltage                       | I <sub>OH</sub> = -16 mA <i>(1)</i> |                         |                      | 0.4                    | V    |

Tables 4–40 through 4–41 show the external timing parameters on column and row pins for HC1S60 devices.

|                      | Perfor | mance |        |

|----------------------|--------|-------|--------|

| Parameter —          | Min    | Max   | – Unit |

| t <sub>INSU</sub>    | 2.000  |       | ns     |

| t <sub>INH</sub>     | 0.000  |       | ns     |

| t <sub>оитсо</sub>   | 3.051  | 6.977 | ns     |

| t <sub>xz</sub>      | 2.991  | 6.853 | ns     |

| t <sub>zx</sub>      | 2.991  | 6.853 | ns     |

| t <sub>INSUPLL</sub> | 1.315  |       | ns     |

| t <sub>INHPLL</sub>  | 0.000  |       | ns     |

| toutcopll            | 1.029  | 2.323 | ns     |

| t <sub>XZPLL</sub>   | 0.969  | 2.199 | ns     |

| t <sub>ZXPLL</sub>   | 0.969  | 2.199 | ns     |

| Table 4–40. HC1S60 External I/O Timing on Column Pins Using Global | Clock |

|--------------------------------------------------------------------|-------|

| Networks                                                           |       |

Table 4–41. HC1S60 External I/O Timing on Row Pins Using Global Clock Networks

| Deveryotev           | Perfor | 11    |      |

|----------------------|--------|-------|------|

| Parameter –          | Min    | Max   | Unit |

| t <sub>INSU</sub>    | 2.232  |       | ns   |

| t <sub>INH</sub>     | 0.000  |       | ns   |

| t <sub>оитсо</sub>   | 3.182  | 7.286 | ns   |

| t <sub>xz</sub>      | 3.209  | 7.354 | ns   |

| t <sub>ZX</sub>      | 3.209  | 7.354 | ns   |

| t <sub>INSUPLL</sub> | 1.651  |       | ns   |

| t <sub>INHPLL</sub>  | 0.000  |       | ns   |

| toutcopll            | 1.154  | 2.622 | ns   |

| t <sub>XZPLL</sub>   | 1.181  | 2.690 | ns   |

| t <sub>ZXPLL</sub>   | 1.181  | 2.690 | ns   |

Table 4–50 shows the high-speed I/O timing for HardCopy Stratix devices.

| Ourse had                                  | 0 - m diki - m -                                                   | Performance |         |     | 11   |  |

|--------------------------------------------|--------------------------------------------------------------------|-------------|---------|-----|------|--|

| Symbol                                     | Conditions                                                         | Min         | Typ Max |     | Unit |  |

| f <sub>HSCLK</sub> (Clock frequency)       | W = 4 to 30 (Serdes used)                                          | 10          |         | 210 | MHz  |  |

| (LVDS, LVPECL, HyperTransport technology)  | W = 2 (Serdes bypass)                                              | 50          |         | 231 | MHz  |  |

| $f_{HSCLK} = f_{HSDR} / W$                 | W = 2 (Serdes used)                                                | 150         |         | 420 | MHz  |  |

|                                            | W = 1 (Serdes bypass)                                              | 100         |         | 462 | MHz  |  |

|                                            | W = 1 (Serdes used)                                                | 300         |         | 717 | MHz  |  |

| HSDR Device operation                      | <i>J</i> = 10                                                      | 300         |         | 840 | Mbps |  |

| (LVDS, LVPECL, HyperTransport              | <i>J</i> = 8                                                       | 300         |         | 840 | Mbps |  |

| echnology)                                 | J = 7                                                              | 300         |         | 840 | Mbps |  |

|                                            | <i>J</i> = 4                                                       | 300         |         | 840 | Mbps |  |

|                                            | J = 2                                                              | 100         |         | 462 | Mbps |  |

|                                            | J = 1 (LVDS and LVPECL only)                                       | 100         |         | 462 | Mbps |  |

| HSCLK (Clock frequency)                    | W = 4 to 30 (Serdes used)                                          | 10          |         | 100 | MHz  |  |

| (PCML)                                     | W = 2 (Serdes bypass)                                              | 50          |         | 200 | MHz  |  |

| f <sub>HSCLK</sub> = f <sub>HSDR</sub> / W | W = 2 (Serdes used)                                                | 150         |         | 200 | MHz  |  |

|                                            | W = 1 (Serdes bypass)                                              | 100         |         | 250 | MHz  |  |

|                                            | W = 1 (Serdes used)                                                | 300         |         | 400 | MHz  |  |

| HSDR Device operation (PCML)               | <i>J</i> = 10                                                      | 300         |         | 400 | Mbps |  |

|                                            | <i>J</i> = 8                                                       | 300         |         | 400 | Mbps |  |

|                                            | J = 7                                                              | 300         |         | 400 | Mbps |  |

|                                            | <i>J</i> = 4                                                       | 300         |         | 400 | Mbps |  |

|                                            | J = 2                                                              | 100         |         | 400 | Mbps |  |

|                                            | <i>J</i> = 1                                                       | 100         |         | 250 | Mbps |  |

| TCCS                                       | All                                                                |             |         | 200 | ps   |  |

| SW                                         | PCML ( <i>J</i> = 4, 7, 8, 10)                                     | 750         |         |     | ps   |  |

|                                            | PCML ( <i>J</i> = 2)                                               | 900         |         |     | ps   |  |

|                                            | PCML ( <i>J</i> = 1)                                               | 1,500       |         |     | ps   |  |

|                                            | LVDS and LVPECL $(J = 1)$                                          | 500         |         |     | ps   |  |

|                                            | LVDS, LVPECL,<br>HyperTransport technology<br>(J = 2  through  10) | 440         |         |     | ps   |  |

| Table 4–50. High-Speed I/O Specifications (Part 2 of 2) Notes (1), (2) |                                                              |      |             |      |      |

|------------------------------------------------------------------------|--------------------------------------------------------------|------|-------------|------|------|

| Querra la                                                              | Oanditions                                                   |      | Performance |      |      |

| Symbol                                                                 | Conditions                                                   | Min  | Тур         | Max  | Unit |

| Input jitter tolerance<br>(peak-to-peak)                               | All                                                          |      |             | 250  | ps   |

| Output jitter (peak-to-peak)                                           | All                                                          |      |             | 160  | ps   |

| Output t <sub>RISE</sub>                                               | LVDS                                                         | 80   | 110         | 120  | ps   |

|                                                                        | HyperTransport technology                                    | 110  | 170         | 200  | ps   |

|                                                                        | LVPECL                                                       | 90   | 130         | 150  | ps   |

|                                                                        | PCML                                                         | 80   | 110         | 135  | ps   |

| Output t <sub>FALL</sub>                                               | LVDS                                                         | 80   | 110         | 120  | ps   |

|                                                                        | HyperTransport technology                                    | 110  | 170         | 200  | ps   |

|                                                                        | LVPECL                                                       | 90   | 130         | 160  | ps   |

|                                                                        | PCML                                                         | 105  | 140         | 175  | ps   |

| t <sub>DUTY</sub>                                                      | LVDS ( $J = 2$ through 10)                                   | 47.5 | 50          | 52.5 | %    |

|                                                                        | LVDS (J=1) and LVPECL,<br>PCML, HyperTransport<br>technology | 45   | 50          | 55   | %    |

| t <sub>LOCK</sub>                                                      | All                                                          |      |             | 100  | μs   |

#### Notes to Table 4–50:

(1) When J = 4, 7, 8, and 10, the SERDES block is used.

(2) When J = 2 or J = 1, the SERDES is bypassed.

## PLL **Specifications**

Table 4-51 describes the HardCopy Stratix device enhanced PLL specifications.

| Table 4–51. Enhanced PLL Specifications (Part 1 of 3) |                                               |       |     |          |      |

|-------------------------------------------------------|-----------------------------------------------|-------|-----|----------|------|

| Symbol                                                | Parameter                                     | Min   | Тур | Мах      | Unit |

| f <sub>IN</sub>                                       | Input clock frequency                         | 3 (1) |     | 684      | MHz  |

| f <sub>INDUTY</sub>                                   | Input clock duty cycle                        | 40    |     | 60       | %    |

| f <sub>EINDUTY</sub>                                  | External feedback clock input duty cycle      | 40    |     | 60       | %    |

| t <sub>INJITTER</sub>                                 | Input clock period jitter                     |       |     | ±200 (2) | ps   |

| t <sub>EINJITTER</sub>                                | External feedback clock period jitter         |       |     | ±200 (2) | ps   |

| t <sub>FCOMP</sub>                                    | External feedback clock compensation time (3) |       |     | 6        | ns   |

| Symbol                   | Parameter                                                                                                    | Min | Тур | Max                                                        | Unit         |

|--------------------------|--------------------------------------------------------------------------------------------------------------|-----|-----|------------------------------------------------------------|--------------|

| f <sub>оит</sub>         | Output frequency for internal global or regional clock                                                       | 0.3 |     | 500                                                        | MHz          |

| f <sub>OUT_EXT</sub>     | Output frequency for external clock (2)                                                                      | 0.3 |     | 526                                                        | MHz          |

| toutduty                 | Duty cycle for external clock output (when set to 50%)                                                       | 45  |     | 55                                                         | %            |

| t <sub>JITTER</sub>      | Period jitter for external clock output (5)                                                                  |     |     | ±100 ps for >200 MHz outclk<br>±20 mUI for <200 MHz outclk | ps or<br>mUI |

| t <sub>CONFIG5,6</sub>   | Time required to reconfigure the scan chains for PLLs 5 and 6                                                |     |     | 289/f <sub>SCANCLK</sub>                                   |              |

| t <sub>CONFIG11,12</sub> | Time required to reconfigure the scan chains for PLLs 11 and 12                                              |     |     | 193/f <sub>SCANCLK</sub>                                   |              |

| t <sub>SCANCLK</sub>     | scanclk frequency (4)                                                                                        |     |     | 22                                                         | MHz          |

| t <sub>DLOCK</sub>       | Time required to lock dynamically (after switchover or reconfiguring any non-post-scale counters/delays) (6) | (8) |     | 100                                                        | μs           |

| t <sub>LOCK</sub>        | Time required to lock from end of device configuration                                                       | 10  |     | 400                                                        | μs           |

| f <sub>VCO</sub>         | PLL internal VCO operating range                                                                             | 300 |     | 800 (7)                                                    | MHz          |

| t <sub>LSKEW</sub>       | Clock skew between two external clock outputs driven by the same counter                                     |     | ±50 |                                                            | ps           |

| t <sub>skew</sub>        | Clock skew between two external clock<br>outputs driven by the different counters<br>with the same settings  |     | ±75 |                                                            | ps           |

| f <sub>SS</sub>          | Spread spectrum modulation frequency                                                                         | 30  |     | 150                                                        | kHz          |

| % spread                 | Percentage spread for spread spectrum frequency (9)                                                          | 0.4 | 0.5 | 0.6                                                        | %            |

| Table 4–53. Document Revision History (Part 2 of 2) |                                                                                                                                                                                                                                                                                                                                                                                                                                            |                    |  |  |  |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--|--|--|

| Date and Document<br>Version                        | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                               | Summary of Changes |  |  |  |

| December 2006<br>v3.2                               | Updated chapter number and metadata.                                                                                                                                                                                                                                                                                                                                                                                                       | _                  |  |  |  |

| March 2006                                          | Formerly chapter 8; no content change.                                                                                                                                                                                                                                                                                                                                                                                                     | _                  |  |  |  |

| October 2005 v3.1                                   | <ul><li>Minor edits</li><li>Graphic updates</li></ul>                                                                                                                                                                                                                                                                                                                                                                                      |                    |  |  |  |

| May 2005<br>v3.0                                    | <ul> <li>Updated SSTL-2 and SSTL-3 specifications in<br/>Tables 8–19 through 8–22</li> <li>Updated CTT I/O specifications in Table 8–30</li> <li>Updated bus hold parameters in Table 8–31.</li> <li>Added the External Timing Parameters, HardCopy<br/>Stratix External I/O Timing, and Maximum Input and<br/>Output Clock Rates sections</li> <li>Added the High-Speed I/O Specification, and PLL<br/>Specifications sections</li> </ul> |                    |  |  |  |

| January 2005<br>v2.0                                | Removed recommended maximum rise and fall times (t <sub>R</sub> — and t <sub>F</sub> ) for input signals                                                                                                                                                                                                                                                                                                                                   |                    |  |  |  |

| June 2003<br>v1.0                                   | Initial release of Chapter 8, Operating Conditions, in the<br>HardCopy Device Handbook                                                                                                                                                                                                                                                                                                                                                     |                    |  |  |  |

## 5. Quartus II Support for HardCopy Stratix Devices

#### H51014-3.4

### Introduction

Altera<sup>®</sup> HardCopy devices provide a comprehensive alternative to ASICs. HardCopy structured ASICs offer a complete solution from prototype to high-volume production, and maintain the powerful features and high-performance architecture of their equivalent FPGAs with the programmability removed. You can use the Quartus II design software to design HardCopy devices in a manner similar to the traditional ASIC design flow and you can prototype with Altera's high density Stratix, APEX 20KC, and APEX 20KE FPGAs before seamlessly migrating to the corresponding HardCopy device for high-volume production.

HardCopy structured ASICs provide the following key benefits:

- Improves performance, on the average, by 40% over the corresponding -6 speed grade FPGA device

- Lowers power consumption, on the average, by 40% over the corresponding FPGA

- Preserves the FPGA architecture and features and minimizes risk

- Guarantees first-silicon success through a proven, seamless migration process from the FPGA to the equivalent HardCopy device

- Offers a quick turnaround of the FPGA design to a structured ASIC device—samples are available in about eight weeks

Altera's Quartus II software has built-in support for HardCopy Stratix devices. The HardCopy design flow in Quartus II software offers the following advantages:

- Unified design flow from prototype to production

- Performance estimation of the HardCopy Stratix device allows you to design systems for maximum throughput

- Easy-to-use and inexpensive design tools from a single vendor

- An integrated design methodology that enables system-on-a-chip designs

This section discusses the following areas:

- How to design HardCopy Stratix and HardCopy APEX structured ASICs using the Quartus II software

- An explanation of what the HARDCOPY\_FPGA\_PROTOTYPE devices are and how to target designs to these devices

- Performance and power estimation of HardCopy Stratix devices

- How to generate the HardCopy design database for submitting HardCopy Stratix and HardCopy APEX designs to the HardCopy Design Center

# **Features** Beginning with version 4.2, the Quartus II software contains several powerful features that facilitate design of HardCopy Stratix and HardCopy APEX devices:

#### HARDCOPY\_FPGA\_PROTOTYPE Devices These are virtual Stratix FPGA devices with features identical to

HardCopy Stratix devices. You must use these FPGA devices to prototype your designs and verify the functionality in silicon.

## HardCopy Timing Optimization Wizard Using this feature, you can target your design to HardCopy Stratix devices, providing an estimate of the design's performance in a

HardCopy Stratix Floorplans and Timing Models The Quartus II software supports post-migration HardCopy Stratix device floorplans and timing models and facilitates design optimization for design performance.

#### Placement Constraints

Location and LogicLock constraints are supported at the HardCopy Stratix floorplan level to improve overall performance.

#### Improved Timing Estimation

HardCopy Stratix device.

Beginning with version 4.2, the Quartus II software determines routing and associated buffer insertion for HardCopy Stratix designs, and provides the Timing Analyzer with more accurate information about the delays than was possible in previous versions of the Quartus II software. The Quartus II Archive File automatically receives buffer insertion information, which greatly enhances the timing closure process in the back-end migration of your HardCopy Stratix device.

Figure 5–2. Selecting a HARDCOPY\_FPGA\_PROTOTYPE Device

| General                                                             | Device                                                                                     |

|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| Files<br>User Libraries (Current Project)<br>Device                 | Select the family and device you want to target for compilation.                           |

| — Timing Requirements & Options                                     | Eamily: Stratix                                                                            |

| EDA Tool Settings                                                   | Package: Any                                                                               |

| ±- Compilation Process Settings<br>±- Analysis & Synthesis Settings | Device & Pin Options Bouting Options                                                       |

| Analysis & Synthesis Settings     Fitter Settings                   | Pin count: Any                                                                             |

| Assembler                                                           | C Auto device selected by the Fitter Speed grade: Any                                      |

| - Timing Analyzer                                                   | Specific device selected in 'Available devices' list     Core voltage: 1.5V                |

| Design Assistant<br>SignalTap II Logic Analyzer                     | C Dther: n/a V Show advanced devices                                                       |

| - Logic Analyzer Interface                                          | Available devices:                                                                         |

| SignalProbe Settings                                                | Name LEs Memor DSP PLL                                                                     |

| PowerPlay Power Analyzer Settings                                   | EP1540B956i6 41250 3423744 14 12                                                           |

| + Software Build Settings                                           | EP1S40F780C5 41250 3423744 14 6                                                            |

| HardCopy Settings                                                   | EP1S40F780C5_HARDCOPY_FPGA_PROTOTYPE 41250 2244096 14 6                                    |

|                                                                     | EP1S40F780C6 41250 3423744 14 6<br>EP1S40F780C6 HARDCOPY FPGA PROTOTYPE 41250 2244096 14 6 |

|                                                                     | EP1540F780C6_HARDCOF1_FPGA_FROTOTTFE_41230_2244036_146                                     |

|                                                                     | EP1S40F780C7_HARDC0PY_FPGA_PROTOTYPE 41250 2244096 14 6                                    |

|                                                                     | EP1S40F780C8 41250 3423744 14 6                                                            |

|                                                                     | EP1S40F780I6 41250 3423744 14 6                                                            |

|                                                                     |                                                                                            |

|                                                                     | Migration compatibility Companion device                                                   |

|                                                                     | Migration Devices HardCopy II                                                              |

|                                                                     | 0 migration devices selected                                                               |

|                                                                     |                                                                                            |

By choosing the HARDCOPY\_FPGA\_PROTOTYPE device, all the design information, available resources, package option, and pin assignments are constrained to guarantee a seamless migration of your project to the HardCopy Stratix device. The netlist resulting from the HARDCOPY\_FPGA\_PROTOTYPE device compilation contains information about the electrical connectivity, resources used, I/O placements, and the unused resources in the FPGA device.

- 4. On the Assignments menu, click **Settings**. In the **Category** list, select **HardCopy Settings** and specify the input transition timing to be modeled for both clock and data input pins. These transition times are used in static timing analysis during back-end timing closure of the HardCopy device.

- Add constraints to your HARDCOPY\_FPGA\_PROTOTYPE device, and on the Processing menu, click Start Compilation to compile the design.

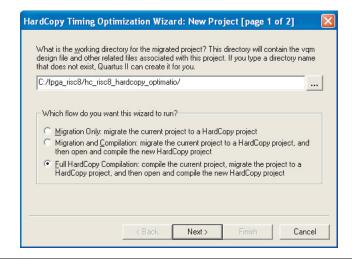

Figure 5–3. HardCopy Timing Optimization Wizard Options

The main benefit of the HardCopy Timing Wizard's three options is flexibility of the conversion process automation. The first time you migrate your HARDCOPY\_FPGA\_PROTOTYPE project to a HardCopy Stratix device, you may want to use Migration Only, and then work on the HardCopy Stratix project in the Quartus II software. As your prototype FPGA project and HardCopy Stratix project constraints stabilize and you have fewer changes, the Full HardCopy Compilation is ideal for one-click compiling of your HARDCOPY\_FPGA\_PROTOTYPE and HardCopy Stratix projects.

| Related   | For more information, refer to the following documentation:                                                                                                                                                              |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Documents | <ul> <li>The HardCopy Series Design Guidelines chapter in volume 1 of the HardCopy Series Handbook.</li> <li>The HardCopy Series Back-End Timing Closure chapter in volume 1 of the HardCopy Series Handbook.</li> </ul> |

## Document Revision History

Table 5–6 shows the revision history for this chapter.

| Table 5–6. Document Revision History |                                                                                                                                                                                       |                    |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Date and Document<br>Version         | Changes Made                                                                                                                                                                          | Summary of Changes |

| September 2008<br>v3.4               | Updated chapter number and metadata.                                                                                                                                                  | _                  |

| June 2007 v3.3                       | Updated with the current Quartus II software version 7.1 information.                                                                                                                 | _                  |

| December 2006<br>v3.2                | Updated revision history.                                                                                                                                                             | _                  |

| March 2006                           | Formerly chapter 20; no content change.                                                                                                                                               | _                  |

| October 2005 v3.1                    | <ul> <li>Updated for technical contents for Quartus II 5.1 release</li> <li>Minor edits</li> </ul>                                                                                    | Minor edits.       |

| May 2005<br>v3.0                     | Added PowerPlay early Power estimator information.                                                                                                                                    | _                  |

| January 2005<br>v2.0                 | This revision was previously the <i>Quartus<sup>®</sup> II Support for</i><br><i>HardCopy Devices</i> chapter in the <i>Quartus II Development</i><br><i>Software Handbook, v4.1.</i> | _                  |

| August 2003<br>v1.1                  | Overall edit; added Tcl script appendix.                                                                                                                                              | _                  |

| June 2003<br>v1.0                    | Initial release of Chapter 20, Quartus II Support for<br>HardCopy Stratix Devices.                                                                                                    | _                  |

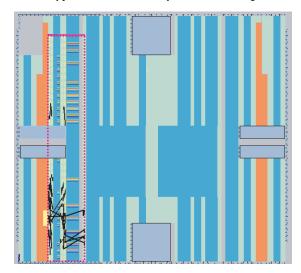

Figure 6–4. HardCopy Stratix Device Floorplan with Soft Region Off

## Using Analysis and Synthesis Settings for Performance Improvement

After establishing the baseline for improvement for this design of 65.30 MHz FPGA/88.14 MHz HardCopy, you can gain additional performance improvement in the Stratix FPGA and HardCopy Stratix devices using the available features in the Quartus II software.

Changing the **Analysis & Synthesis Effort** from **Balanced** to **Speed** yields additional benefit in performance, but at the cost of additional LE resources. The Tcl command for this assignment is as follows:

set\_global\_assignment -name

STRATIX\_OPTIMIZATION\_TECHNIQUE SPEED