Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Obsolete                                                 |

| Number of LABs/CLBs            | 5712                                                     |

| Number of Logic Elements/Cells | 57120                                                    |

| Total RAM Bits                 | 5215104                                                  |

| Number of I/O                  | 782                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.425V ~ 1.575V                                          |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | -                                                        |

| Package / Case                 | 1020-BBGA                                                |

| Supplier Device Package        | 1020-FBGA (33x33)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/hc1s60f1020by |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1. Introduction to HardCopy Stratix Devices

H51001-2.4

### Introduction

HardCopy® Stratix® structured ASICs, Altera's second-generation HardCopy structured ASICs, are low-cost, high-performance devices with the same architecture as the high-density Stratix FPGAs. The combination of Stratix FPGAs for prototyping and design verification, HardCopy Stratix devices for high-volume production, and the Quartus® II design software beginning with version 3.0, provide a complete and powerful alternative to ASIC design and development.

HardCopy Stratix devices are architecturally equivalent and have the same features as the corresponding Stratix FPGA. They offer pin-to-pin compatibility using the same package as the corresponding Stratix FPGA prototype. Designers can prototype their design to verify functionality with Stratix FPGAs before seamlessly migrating the proven design to a HardCopy Stratix structured ASIC.

The Quartus II software provides a complete set of inexpensive and easy-to-use tools for designing HardCopy Stratix devices. Using the successful and proven methodology from HardCopy APEX™ devices, Stratix FPGA designs can be seamlessly and quickly migrated to a low-cost ASIC alternative. Designers can use the Quartus II software to design HardCopy Stratix devices to obtain an average of 50% higher performance and up to 40% lower power consumption than can be achieved in the corresponding Stratix FPGAs. The migration process is fully automated, requires minimal customer involvement, and takes approximately eight weeks to deliver fully tested HardCopy Stratix prototypes.

The HardCopy Stratix devices use the same base arrays across multiple designs for a given device density and are customized using the top two metal layers. The HardCopy Stratix family consists of the HC1S25, HC1S30, HC1S40, HC1S60, and HC1S80 devices. Table 1–1 provides the details of the HardCopy Stratix devices.

| Table 1–1. HardCopy Stratix Devices and Features |         |             |            |                 |                |          |

|--------------------------------------------------|---------|-------------|------------|-----------------|----------------|----------|

| Device                                           | LEs (1) | M512 Blocks | M4K Blocks | M-RAM<br>Blocks | DSP Blocks (2) | PLLs (3) |

| HC1S25                                           | 25,660  | 224         | 138        | 2               | 10             | 6        |

| HC1S30                                           | 32,470  | 295         | 171        | 2 (4)           | 12             | 6        |

| HC1S40                                           | 41,250  | 384         | 183        | 2 (4)           | 14             | 6        |

| HC1S60                                           | 57,120  | 574         | 292        | 6               | 18             | 12       |

| HC1S80                                           | 79,040  | 767         | 364        | 6 (4)           | 22             | 12       |

#### *Notes to Table 1–1:*

- (1) LE: logic elements.

- (2) DSP: digital signal processing.

- (3) PLLs: phase-locked loops.

- (4) In HC1S30, HC1S40, and HC1S80 devices, there are fewer M-RAM blocks than in the equivalent Stratix FPGA. All other resources are identical to the Stratix counterpart.

### **Features**

HardCopy Stratix devices are manufactured on the same 1.5-V, 0.13  $\mu m$  all-layer-copper metal fabrication process (up to eight layers of metal) as the Stratix FPGAs.

- Preserves the functionality of a configured Stratix device

- Pin-compatible with the Stratix counterparts

- On average, 50% faster than their Stratix equivalents

- On average, 40% less power consumption than their Stratix equivalents

- 25,660 to 79,040 LEs

- Up to 5,658,408 RAM bits available

- TriMatrix memory architecture consisting of three RAM block sizes to implement true dual-port memory and first-in-first-out (FIFO) buffers

- Embedded high-speed DSP blocks provide dedicated implementation of multipliers, multiply-accumulate functions, and finite impulse response (FIR) filters

- Up to 12 PLLs (four enhanced PLLs and eight fast PLLs) per device which provide identical features as the FPGA counterparts, including spread spectrum, programmable bandwidth, clock switchover, real-time PLL reconfiguration, advanced multiplication, and phase shifting

- Supports numerous single-ended and differential I/O standards

- Supports high-speed networking and communications bus standards including RapidIO<sup>TM</sup>, UTOPIA IV, CSIX, HyperTransport technology, 10G Ethernet XSBI, SPI-4 Phase 2 (POS-PHY Level 4), and SFI-4

- Differential on-chip termination support for LVDS

| Table 2–1. HardCopy Stratix and Stratix Device Comparison (Part 2 of 2)                                                     |                                                                                                                |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|--|--|

| HardCopy Stratix                                                                                                            | Stratix                                                                                                        |  |  |  |

| The I/O drive strength for single-ended I/O pins are slightly different and is modeled in the HardCopy Stratix IBIS models. | The I/O drive strength for single-ended I/O pins are found in Stratix IBIS models.                             |  |  |  |

| In the HC1S40 780-pin FineLine BGA® device, the I/O pins U12 and U18 must be connected to ground.                           | In the HC1S40 780-pin FineLine BGA device, the I/O pins U12 and U18 are available as general-purpose I/O pins. |  |  |  |

| The BSDL file describes re-ordered Joint Test Action Group (JTAG) boundary-scan chains.                                     | The JTAG boundary-scan chain is defined in the BSDL file.                                                      |  |  |  |

#### Note to Table 2-1:

(1) Performance and power consumption are design dependant.

## **Logic Elements**

Logic is implemented in HardCopy Stratix devices using the same architectural units as the Stratix device family. The basic unit is the logic element (LE) with logic array blocks (LAB) consisting of 10 LEs. The implementation of LEs and LABs is identical to the Stratix device family.

In the HardCopy Stratix device family, all extraneous routing resources not essential to the specific design are removed for performance and die size efficiency. Therefore, the MultiTrack interconnect for routing implementation between LABs and other device resources in the Stratix device family is no longer necessary in the HardCopy Stratix device family.

Table 2–2 illustrates the differences between HardCopy Stratix and Stratix logic.

| Table 2–2. HardCopy Stratix and Stratix Logic Comparison              |                                                                           |  |  |  |

|-----------------------------------------------------------------------|---------------------------------------------------------------------------|--|--|--|

| HardCopy Stratix Stratix                                              |                                                                           |  |  |  |

| All routing connections are direct and all unused routing is removed. | MultiTrack routing stitches routing resources together to provide a path. |  |  |  |

## Embedded Memory

TriMatrix™ memory blocks from Stratix devices, including M512, M4K, and M-RAM memory blocks, are available in HardCopy Stratix devices. Embedded memory is seamlessly implemented in the equivalent resource.

When designing with very tight timing constraints (for example, DDR or quad data rate [QDR]), or if using the programmable drive strength option, Altera recommends verifying final drive strength using updated IBIS models located on the Altera website at www.altera.com. Differential I/O standards are unaffected.

I/O pin placement and VREF pin placement rules are identical between HardCopy Stratix and Stratix devices. Unused pin settings will carry over from Stratix device settings and are implemented as tri-stated outputs driving ground or outputs driving  $V_{CC}$ .

In Stratix EP1S40 780-pin FineLine BGA FPGAs, the I/O pins U12 and U18 are available as general-purpose I/O pins. In the FPGA prototype, EP1S40F780\_HARDCOPY\_FPGA\_PROTOTYPE, and in the Hardcopy Stratix HC1S40 780-pin FineLine BGA device, the I/O pins U12 and U18 must be connected to ground. HC1S40 780-pin FineLine BGA and EP1S40F780\_HARDCOPY\_FPGA\_PROTOTYPE pin-outs are identical.

Table 2–7 illustrates the differences between HardCopy Stratix and Stratix I/O pins.

| Table 2–7. HardCopy Stratix and Stratix I/O Pin Comparison                                                                 |                                                                                                                |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|--|--|--|

| HardCopy Stratix                                                                                                           | Stratix                                                                                                        |  |  |  |  |

| The IOEs are equivalent, but not identical to, the FPGA IOEs due to slight design optimizations for HardCopy devices.      | IOEs are optimized for the FPGA architecture.                                                                  |  |  |  |  |

| The I/O drive strength for single-ended I/O pins are slightly different and are found in the HardCopy Stratix IBIS models. | The I/O drive strength for single-ended I/O pins are found in Stratix IBIS models.                             |  |  |  |  |

| In the HC1S40 780-pin FineLine BGA device, the I/O pins U12 and U18 must be connected to ground.                           | In the EP1S40 780-pin FineLine BGA device, the I/O pins U12 and U18 are available as general-purpose I/O pins. |  |  |  |  |

## Power-Up Modes in HardCopy Stratix Devices

Designers do not need to configure HardCopy Stratix devices, unlike their FPGA counterparts. However, to facilitate seamless migration, configuration can be emulated in HardCopy Stratix devices.

The modes in which a HardCopy Stratix device can be made ready for operation after power-up are: instant on, instant on after 50 ms, and configuration emulation. These modes are briefly described below.

- In instant on mode, the HardCopy Stratix device is available for use shortly after the device receives power. The on-chip POR circuit resets all registers. The CONF\_DONE output is tri-stated once the POR has elapsed. No configuration device or configuration data is necessary.

- In instant on after 50 ms mode, the HardCopy Stratix device performs in a fashion similar to the instant on mode, except that there is an additional delay of 50 ms, during which time the device is held in reset stage. The CONF\_DONE output is pulled low during this time, and then tri-stated after the 50 ms have elapsed. No configuration device or configuration data is necessary for this option.

- In configuration emulation mode, the HardCopy series device emulates the behavior of an APEX or Stratix FPGA during its configuration phase. When this mode is used, the HardCopy device uses a configuration emulation circuit to receive configuration bit streams. When all the configuration data is received, the HardCopy series device transitions into an initialization phase and releases the CONF\_DONE pin to be pulled high. Pulling the CONF\_DONE pin high signals that the HardCopy series device is ready for normal operation. If the optional open-drain INIT\_DONE output is used, the normal operation is delayed until this signal is released by the HardCopy series device.

HardCopy II and some HardCopy Stratix devices do not support configuration emulation mode.

Instant on and instant on after 50 ms modes are the recommended power-up modes because these modes are similar to an ASIC's functionality upon power-up. No changes to the existing board design or the configuration software are required.

All three modes provide significant benefits to system designers. They enable seamless migration of the design from the FPGA device to the HardCopy device with no changes to the existing board design or the configuration software. The pull-up resistors on <code>nCONFIG</code>, <code>nSTATUS</code>, and <code>CONF DONE</code> should be left on the printed circuit board.

For more information, refer to the *HardCopy Series Configuration Emulation* chapter in the *HardCopy Series Handbook*.

### **Hot Socketing**

HardCopy Stratix devices support hot socketing without any external components. In a hot socketing situation, a device's output buffers are turned off during system power up or power down. To simplify board design, HardCopy Stratix devices support any power-up or power-down sequence ( $V_{\text{CCIO}}$  and  $V_{\text{CCINT}}$ ). For mixed-voltage environments, you can

| Table 4-          | Table 4–3. HardCopy Stratix Device DC Operating Conditions         Note (7)              |                                                      |         |         |         |      |  |  |

|-------------------|------------------------------------------------------------------------------------------|------------------------------------------------------|---------|---------|---------|------|--|--|

| Symbol            | Parameter                                                                                | Conditions                                           | Minimum | Typical | Maximum | Unit |  |  |

| l <sub>l</sub>    | Input pin leakage current                                                                | $V_I = V_{CCIOmax}$ to 0 V (8)                       | -10     |         | 10      | μΑ   |  |  |

| l <sub>oz</sub>   | Tri-stated I/O pin leakage current                                                       | $V_O = V_{CCIOmax}$ to 0 V (8)                       | -10     |         | 10      | μА   |  |  |

| I <sub>CC0</sub>  | V <sub>CC</sub> supply current<br>(standby) (All memory<br>blocks in power-down<br>mode) | V <sub>I</sub> = ground, no load, no toggling inputs |         |         |         | mA   |  |  |

| R <sub>CONF</sub> | Value of I/O pin pull-up                                                                 | Vi=0; V <sub>CCIO</sub> = 3.3 V (9)                  | 15      | 25      | 50      | kΩ   |  |  |

|                   | resistor before and during configuration                                                 | Vi=0; V <sub>CCIO</sub> = 2.5 V (9)                  | 20      | 45      | 70      | kΩ   |  |  |

|                   | aumig comigui anon                                                                       | Vi=0; V <sub>CCIO</sub> = 1.8 V (9)                  | 30      | 65      | 100     | kΩ   |  |  |

|                   |                                                                                          | Vi=0; V <sub>CCIO</sub> = 1.5 V (9)                  | 50      | 100     | 150     | kΩ   |  |  |

|                   | Recommended value of I/O pin external pull-down resistor before and during configuration |                                                      |         | 1       | 2       | kΩ   |  |  |

### *Notes to Tables 4–1 through 4–3:*

- (1) Refer to the Operating Requirements for Altera Devices Data Sheet.

- (2) Conditions beyond those listed in Table 4–1 may cause permanent damage to a device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse affects on the device.

- (3) Minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2 V or overshoot to 4.6 V for input currents less than 100 mA and periods shorter than 20 ns.

- (4) Maximum  $V_{CC}$  rise time is 100 ms, and  $V_{CC}$  must rise monotonically.

- (5)  $V_{CCIO}$  maximum and minimum conditions for LVPECL, LVDS, and 3.3-V PCML are shown in parentheses.

- (6) All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before V<sub>CCINT</sub> and V<sub>CCIO</sub> are powered.

- (7) Typical values are for  $T_A = 25$  °C,  $V_{CCINT} = 1.5$  V, and  $V_{CCIO} = 1.5$  V, 1.8 V, 2.5 V, and 3.3 V.

- (8) This value is specified for normal device operation. The value may vary during power up. This applies for all  $V_{CCIO}$  settings (3.3, 2.5, 1.8, and 1.5 V).

- (9) Pin pull-up resistance values will be lower if an external source drives the pin higher than V<sub>CCIO</sub>.

| Table 4-             | Table 4–27. 1.8-V HSTL Class I Specifications |                               |                         |                       |                        |      |  |

|----------------------|-----------------------------------------------|-------------------------------|-------------------------|-----------------------|------------------------|------|--|

| Symbol               | Parameter                                     | Conditions                    | Minimum                 | Typical               | Maximum                | Unit |  |

| V <sub>CCIO</sub>    | Output supply voltage                         |                               | 1.65                    | 1.80                  | 1.95                   | ٧    |  |

| $V_{REF}$            | Input reference voltage                       |                               | 0.70                    | 0.90                  | 0.95                   | V    |  |

| V <sub>TT</sub>      | Termination voltage                           |                               |                         | $V_{CCIO} \times 0.5$ |                        | V    |  |

| V <sub>IH</sub> (DC) | DC high-level input voltage                   |                               | V <sub>REF</sub> + 0.1  |                       |                        | V    |  |

| V <sub>IL</sub> (DC) | DC low-level input voltage                    |                               | -0.5                    |                       | V <sub>REF</sub> - 0.1 | V    |  |

| V <sub>IH</sub> (AC) | AC high-level input voltage                   |                               | V <sub>REF</sub> + 0.2  |                       |                        | V    |  |

| V <sub>IL</sub> (AC) | AC low-level input voltage                    |                               |                         |                       | V <sub>REF</sub> - 0.2 | V    |  |

| V <sub>OH</sub>      | High-level output voltage                     | I <sub>OH</sub> = 8 mA (1)    | V <sub>CCIO</sub> - 0.4 |                       |                        | ٧    |  |

| V <sub>OL</sub>      | Low-level output voltage                      | $I_{OH} = -8 \text{ mA } (1)$ |                         |                       | 0.4                    | V    |  |

| Table 4-2            | Table 4–28. 1.8-V HSTL Class II Specifications |                                |                         |                              |                        |      |  |

|----------------------|------------------------------------------------|--------------------------------|-------------------------|------------------------------|------------------------|------|--|

| Symbol               | Parameter                                      | Conditions                     | Minimum                 | Typical                      | Maximum                | Unit |  |

| V <sub>CCIO</sub>    | Output supply voltage                          |                                | 1.65                    | 1.80                         | 1.95                   | V    |  |

| V <sub>REF</sub>     | Input reference voltage                        |                                | 0.70                    | 0.90                         | 0.95                   | V    |  |

| V <sub>TT</sub>      | Termination voltage                            |                                |                         | $V_{\text{CCIO}} \times 0.5$ |                        | V    |  |

| V <sub>IH</sub> (DC) | DC high-level input voltage                    |                                | V <sub>REF</sub> + 0.1  |                              |                        | ٧    |  |

| V <sub>IL</sub> (DC) | DC low-level input voltage                     |                                | -0.5                    |                              | V <sub>REF</sub> - 0.1 | ٧    |  |

| V <sub>IH</sub> (AC) | AC high-level input voltage                    |                                | V <sub>REF</sub> + 0.2  |                              |                        | ٧    |  |

| V <sub>IL</sub> (AC) | AC low-level input voltage                     |                                |                         |                              | V <sub>REF</sub> - 0.2 | ٧    |  |

| V <sub>OH</sub>      | High-level output voltage                      | I <sub>OH</sub> = 16 mA (1)    | V <sub>CCIO</sub> - 0.4 |                              |                        | V    |  |

| V <sub>OL</sub>      | Low-level output voltage                       | $I_{OH} = -16 \text{ mA } (1)$ |                         |                              | 0.4                    | ٧    |  |

Tables 4–34 through 4–35 show the external timing parameters on column and row pins for HC1S25 devices.

Table 4–34. HC1S25 External I/O Timing on Column Pins Using Global Clock Networks

| Davamatav             | Perfo | 11-:4 |      |  |

|-----------------------|-------|-------|------|--|

| Parameter -           | Min   | Max   | Unit |  |

| t <sub>INSU</sub>     | 1.371 |       | ns   |  |

| t <sub>INH</sub>      | 0.000 |       | ns   |  |

| t <sub>оитсо</sub>    | 2.809 | 7.155 | ns   |  |

| t <sub>XZ</sub>       | 2.749 | 7.040 | ns   |  |

| t <sub>ZX</sub>       | 2.749 | 7.040 | ns   |  |

| t <sub>INSUPLL</sub>  | 1.271 |       | ns   |  |

| t <sub>INHPLL</sub>   | 0.000 |       | ns   |  |

| t <sub>OUTCOPLL</sub> | 1.124 | 2.602 | ns   |  |

| t <sub>XZPLL</sub>    | 1.064 | 2.487 | ns   |  |

| t <sub>ZXPLL</sub>    | 1.064 | 2.487 | ns   |  |

Table 4–35. HC1S25 External I/O Timing on Row Pins Using Global Clock Networks

| Doromotor             | Perfo | Unit  |       |

|-----------------------|-------|-------|-------|

| Parameter             | Min   | Max   | Ullit |

| t <sub>INSU</sub>     | 1.665 |       | ns    |

| t <sub>INH</sub>      | 0.000 |       | ns    |

| t <sub>outco</sub>    | 2.834 | 7.194 | ns    |

| t <sub>XZ</sub>       | 2.861 | 7.276 | ns    |

| t <sub>ZX</sub>       | 2.861 | 7.276 | ns    |

| t <sub>INSUPLL</sub>  | 1.538 |       | ns    |

| t <sub>INHPLL</sub>   | 0.000 |       | ns    |

| t <sub>OUTCOPLL</sub> | 1.164 | 2.653 | ns    |

| t <sub>XZPLL</sub>    | 1.191 | 2.735 | ns    |

| t <sub>ZXPLL</sub>    | 1.191 | 2.735 | ns    |

Tables 4–40 through 4–41 show the external timing parameters on column and row pins for HC1S60 devices.

Table 4–40. HC1S60 External I/O Timing on Column Pins Using Global Clock Networks

| Davamatav             | Perfo   | Heit  |      |  |

|-----------------------|---------|-------|------|--|

| Parameter             | Min Max |       | Unit |  |

| t <sub>INSU</sub>     | 2.000   |       | ns   |  |

| t <sub>INH</sub>      | 0.000   |       | ns   |  |

| t <sub>outco</sub>    | 3.051   | 6.977 | ns   |  |

| t <sub>XZ</sub>       | 2.991   | 6.853 | ns   |  |

| t <sub>ZX</sub>       | 2.991   | 6.853 | ns   |  |

| t <sub>INSUPLL</sub>  | 1.315   |       | ns   |  |

| t <sub>INHPLL</sub>   | 0.000   |       | ns   |  |

| t <sub>OUTCOPLL</sub> | 1.029   | 2.323 | ns   |  |

| t <sub>XZPLL</sub>    | 0.969   | 2.199 | ns   |  |

| t <sub>ZXPLL</sub>    | 0.969   | 2.199 | ns   |  |

Table 4–41. HC1S60 External I/O Timing on Row Pins Using Global Clock Networks

| Donomoton            | Perfor | 11-:4 |      |

|----------------------|--------|-------|------|

| Parameter            | Min    | Max   | Unit |

| t <sub>INSU</sub>    | 2.232  |       | ns   |

| t <sub>INH</sub>     | 0.000  |       | ns   |

| t <sub>оитсо</sub>   | 3.182  | 7.286 | ns   |

| t <sub>XZ</sub>      | 3.209  | 7.354 | ns   |

| t <sub>ZX</sub>      | 3.209  | 7.354 | ns   |

| t <sub>INSUPLL</sub> | 1.651  |       | ns   |

| t <sub>INHPLL</sub>  | 0.000  |       | ns   |

| toutcopll            | 1.154  | 2.622 | ns   |

| t <sub>XZPLL</sub>   | 1.181  | 2.690 | ns   |

| t <sub>ZXPLL</sub>   | 1.181  | 2.690 | ns   |

Table 4–45. HardCopy Stratix Maximum Input Clock Rate for CLK[0,2,9,11] Pins and FPLL[10..7]CLK Pins

| I/O Standard                  | Performance | Unit |

|-------------------------------|-------------|------|

| LVTTL                         | 422         | MHz  |

| 2.5 V                         | 422         | MHz  |

| 1.8 V                         | 422         | MHz  |

| 1.5 V                         | 422         | MHz  |

| LVCMOS                        | 422         | MHz  |

| GTL                           | 300         | MHz  |

| GTL+                          | 300         | MHz  |

| SSTL-3 class I                | 400         | MHz  |

| SSTL-3 class II               | 400         | MHz  |

| SSTL-2 class I                | 400         | MHz  |

| SSTL-2 class II               | 400         | MHz  |

| SSTL-18 class I               | 400         | MHz  |

| SSTL-18 class II              | 400         | MHz  |

| 1.5-V HSTL class I            | 400         | MHz  |

| 1.5-V HSTL class II           | 400         | MHz  |

| 1.8-V HSTL class I            | 400         | MHz  |

| 1.8-V HSTL class II           | 400         | MHz  |

| 3.3-V PCI                     | 422         | MHz  |

| 3.3-V PCI-X 1.0               | 422         | MHz  |

| Compact PCI                   | 422         | MHz  |

| AGP 1×                        | 422         | MHz  |

| AGP 2×                        | 422         | MHz  |

| CTT                           | 300         | MHz  |

| Differential HSTL             | 400         | MHz  |

| LVPECL (1)                    | 717         | MHz  |

| PCML (1)                      | 400         | MHz  |

| LVDS (1)                      | 717         | MHz  |

| HyperTransport technology (1) | 717         | MHz  |

Table 4–52 describes the HardCopy Stratix device fast PLL specifications.

| Symbol                             | Parameter                                                  | Min       | Max                                                        | Unit         |

|------------------------------------|------------------------------------------------------------|-----------|------------------------------------------------------------|--------------|

| f <sub>IN</sub>                    | CLKIN frequency (for $m = 1$ ) (1), (2)                    | 300       | 717                                                        | MHz          |

|                                    | CLKIN frequency (for $m = 2$ to 19)                        | 300/<br>m | 1,000/ <i>m</i>                                            | MHz          |

|                                    | CLKIN frequency (for $m = 20$ to 32)                       | 10        | 1,000/ <i>m</i>                                            | MHz          |

| f <sub>OUT</sub>                   | Output frequency for internal global or regional clock (3) | 9.4       | 420                                                        | MHz          |

| f <sub>OUT_EXT</sub>               | Output frequency for external clock (2)                    | 9.375     | 717                                                        | MHz          |

| f <sub>VCO</sub>                   | VCO operating frequency                                    | 300       | 1,000                                                      | MHz          |

| t <sub>INDUTY</sub>                | CLKIN duty cycle                                           | 40        | 60                                                         | %            |

| t <sub>INJITTER</sub>              | Period jitter for CLKIN pin                                |           | ±200                                                       | ps           |

| t <sub>DUTY</sub>                  | Duty cycle for DFFIO 1× CLKOUT pin (4)                     | 45        | 55                                                         | %            |

| t <sub>JITTER</sub>                | Period jitter for DFFIO clock out (4)                      |           | ±80                                                        | ps           |

|                                    | Period jitter for internal global or regional clock        |           | ±100 ps for >200-MHz outclk<br>±20 mUl for <200-MHz outclk | ps or<br>mUI |

| t <sub>LOCK</sub>                  | Time required for PLL to acquire lock                      | 10        | 100                                                        | μs           |

| m                                  | Multiplication factors for <i>m</i> counter (4)            | 1         | 32                                                         | Integer      |

| <i>l</i> 0, <i>l</i> 1, <i>g</i> 0 | Multiplication factors for I0, I1, and g0 counter (5), (6) | 1         | 32                                                         | Integer      |

| t <sub>ARESET</sub>                | Minimum pulse width on areset signal                       | 10        |                                                            | ns           |

### Notes to Table 4-52:

- (1) Refer to "Maximum Input and Output Clock Rates" on page 4–23 for more information.

- (2) PLLs 7, 8, 9, and 10 in the HC1S80 device support up to 717-MHz input and output.

- (3) When using the SERDES, high-speed differential I/O mode supports a maximum output frequency of 210 MHz to the global or regional clocks (for example, the maximum data rate 840 Mbps divided by the smallest SERDES J factor of 4).

- (4) This parameter is for high-speed differential I/O mode only.

- (5) These counters have a maximum of 32 if programmed for 50/50 duty cycle. Otherwise, they have a maximum of 16.

- (6) High-speed differential I/O mode supports W = 1 to 16 and J = 4, 7, 8, or 10.

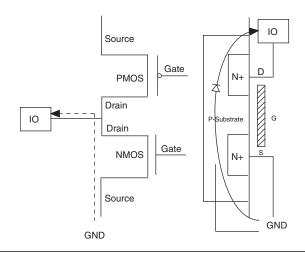

# Electrostatic Discharge

Electrostatic discharge (ESD) protection is a design practice that is integrated in Altera FPGAs and Structured ASIC devices. HardCopy Stratix devices are no exception, and they are designed with ESD protection on all I/O and power pins.

The dashed line (Figure 4–4) shows the ESD current discharge path during a negative voltage zap.

Figure 4-4. ESD Protection During Negative Voltage Zap

Details of ESD protection are also outlined in the *Hot-Socketing and Power-Sequencing Feature and Testing for Altera Devices* white paper located on the Altera website at www.altera.com.

For information on ESD results of Altera products, see the Reliability Report on the Altera website at www.altera.com.

# Document Revision History

Table 4–53 shows the revision history for this chapter.

| Table 4–53. Document Revision History (Part 1 of 2) |                                                                                              |   |  |  |

|-----------------------------------------------------|----------------------------------------------------------------------------------------------|---|--|--|

| Date and Document<br>Version                        | Changes Made Summary of Change                                                               |   |  |  |

| September 2008<br>v3.4                              | Updated the revision history.                                                                | _ |  |  |

| June 2007 v3.3                                      | Updated R <sub>CONF</sub> section of Table 4–3. Added the "Electrostatic Discharge" section. | _ |  |  |

### Migrate the Compiled Project

This step generates the Quartus II Project File (.qpf) and the other files required for HardCopy implementation. The Quartus II software also assigns the appropriate HardCopy Stratix device for the design migration.

### Close the Quartus FPGA Project

Because you must compile the project for a HardCopy Stratix device, you must close the existing project which you have targeted your design to a HARDCOPY\_FPGA\_PROTOTYPE device.

### Open the Quartus HardCopy Project

Open the Quartus II project that you created in the "Migrate the Compiled Project" step. The selected device is one of the devices from the HardCopy Stratix family that was assigned during that step.

### Compile for HardCopy Stratix Device

Compile the design for a HardCopy Stratix device. After successful compilation, the Timing Analysis section of the compilation report shows the performance of the design implemented in the HardCopy device.

## How to Design HardCopy Stratix Devices

This section describes the process for designing for a HardCopy Stratix device using the HARDCOPY\_FPGA\_PROTOTYPE as your initial selected device. In order to use the HardCopy Timing Optimization Wizard, you must first design with the HARDCOPY\_FPGA\_PROTOTYPE in order for the design to migrate to a HardCopy Stratix device.

To target a design to a HardCopy Stratix device in the Quartus II software, follow these steps:

- 1. If you have not yet done so, create a new project or open an existing project.

- On the Assignments menu, click Settings. In the Category list, select Device.

- 3. On the **Device** page, in the **Family** list, select **Stratix**. Select the desired HARDCOPY\_FPGA\_PROTOTYPE device in the **Available Devices** list (Figure 5–2).

Performance estimation is not supported for HardCopy APEX devices in the Quartus II software. Your design can be optimized by modifying the RTL code or the FPGA design and the constraints. You should contact Altera to discuss any desired performance improvements with HardCopy APEX devices.

### **Buffer Insertion**

Beginning with version 4.2, the Quartus II software provides improved HardCopy Stratix device timing closure and estimation, to more accurately reflect the results expected after back-end migration. The Quartus II software performs the necessary buffer insertion in your HardCopy Stratix device during the Fitter process, and stores the location of these buffers and necessary routing information in the Quartus II Archive File. This buffer insertion improves the estimation of the Quartus II Timing Analyzer for the HardCopy Stratix device.

### **Placement Constraints**

Beginning with version 4.2, the Quartus II software supports placement constraints and LogicLock regions for HardCopy Stratix devices. Figure 5–6 shows an iterative process to modify the placement constraints until the best placement for the HardCopy Stratix device is achieved.

turned on by default in the HardCopy Stratix design. While this does allow the Fitter to place all logic in your design with fewer restrictions, it is not optimal for performance improvement in the HardCopy Stratix design.

### Recommended LogicLock Settings for HardCopy Stratix Designs

Altera recommends the following LogicLock region settings for the HARDCOPY FPGA PROTOTYPE:

- Turn on Reserve Unused Logic

- Turn off Soft Region

- Select either **Auto** or **Fixed** as the **Size** (design-dependent)

- Select either Floating or Locked as the Location (design-dependent)

When using the **Reserve Unused Logic** setting in a design with high resource utilization (> 95% LE utilization), and a large number of LogicLock regions, the design may not fit in the device. Turning off **Reserve Unused Logic** in less critical LogicLock regions can help Fitter placement. The LEs allowed to float in placement and be packed into unused LEs of LogicLock regions may not be placed optimally after migration to the HardCopy Stratix device since they are merged with other LogicLock regions.

After running the HardCopy Timing Optimization Wizard, the LogicLock region properties are reset to their default conditions. This allows a successful and immediate placement of your design in the Quartus II software. You can further refine the LogicLock region properties for additional benefits.

Altera recommends using the following properties for LogicLock regions in the HardCopy design project:

- Turn off Soft Region

- Select either Auto or Fixed as the Size after you are satisfied with the placement and timing result of a LogicLock region in a successful HardCopy Stratix compilation

- Select either Floating or Locked as the Location after you are satisfied with the placement and timing results

- Reserve Unused Logic is not applicable in the HardCopy Stratix device placement because logic array block (LAB) contents can not be changed after the HardCopy Timing Optimization Wizard is run

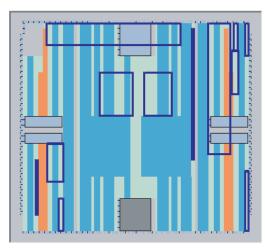

An example of a well partitioned design using LogicLock regions effectively for some portions of the design is shown in Figure 6–1. Only the most critical logic functions required are placed in LogicLock regions in order to achieve the desired performance in the HardCopy Stratix

device. The dark blue rectangles shown in Figure 6–1 are the user-assigned LogicLock regions that have fixed locations. In this example, the design needed to be constrained by LogicLock regions first inside the HARDCOPY\_FPGA\_PROTOTYPE with **Reserve Unused Logic** turned off in **Properties** in LogicLock regions. This selection allows the Quartus II software to isolate and compact the logic of these blocks in the HARDCOPY\_FPGA\_PROTOTYPE such that the placement is tightly controlled in the HardCopy Stratix device.

Figure 6-1. A Well Partitioned Design

In the example shown in Figure 6–1, once suitable locations were identified for LogicLock regions, the LogicLock region properties were changed from floating to locked. The Quartus II software can then reproduce their placement in subsequent compilations, while focusing attention on fixing other portions of the design.

Using Design Space Explorer for HardCopy Stratix Designs The DSE feature in the Quartus II software allows you to evaluate various compilation settings to achieve the best results for your FPGA designs. DSE can also be used in the HardCopy Stratix project after running the HardCopy Timing Optimization wizard.

Only some of the DSE settings affect HardCopy Stratix designs because HDL synthesis and physical optimization have been completed on the FPGA. No logic restructuring can occur after using the HardCopy Timing Optimization wizard. When you compile your design, the placement of LABs is optimized in the HardCopy Stratix device. To access the DSE GUI

Making these settings in the FPGA while leaving **Analysis & Synthesis Effort** set to **Speed** yielded some additional improvement in the FPGA as shown in Table 6–3.

| Table 6–3. Results of Analysis & Synthesis Effort Set to Speed |                    |  |

|----------------------------------------------------------------|--------------------|--|

| Result Type                                                    | Results            |  |

| f <sub>MAX</sub>                                               | 70.28 MHz          |  |

| Total logic elements                                           | 5,515/32,470 (16%) |  |

| Total LABs                                                     | 597/3,247 (18%)    |  |

The WYSIWYG resynthesis added a minimal increase in LEs over the speed setting, and the design performance improved by 2 MHz in the FPGA. Using the HardCopy Timing Optimization wizard to migrate the design to HardCopy and subsequently compiling the HardCopy Stratix design, we find that performance is not improved beyond previous compiles, with an  $f_{\rm MAX}$  of 86.58 MHz.

The Quartus II software automatically optimizes state machines and restructures multiplexers when these settings are set to **Auto** in the **Analysis & Synthesis** settings. Changing these options from **Auto** usually does not yield performance improvement.

For example, changing the multiplexer restructuring and state machine processing settings from both set to **Auto**, to **On** and **One-Hot**, respectively, actually hurt performance, not allowing the Quartus II software to determine the optimization on a case-by-case basis. With these settings, the FPGA compiled to an  $f_{MAX}$  of 65.99 MHz, and the HardCopy Stratix design only performed at 83.77 MHz. For this design example, it is better to leave these settings to **Auto** as seen in the Tcl assignments in the "Using Fitter Assignments and Physical Synthesis Optimizations for Performance Improvement" section, and allow the Quartus II software to determine when to use these features.

## Using Fitter Assignments and Physical Synthesis Optimizations for Performance Improvement

After exploring the Analysis & Synthesis optimization settings in the Quartus II software, you can use the Fitter Settings and Physical Synthesis Optimization features to gain further performance improvement in your Stratix FPGA and HardCopy Stratix devices. In this design example, multiplexer and state machine restructuring settings have been set to **Auto**, and the **Synthesis Optimization Technique** is set

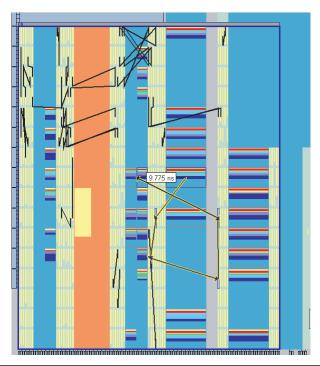

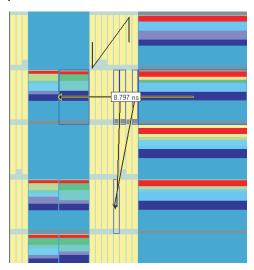

Figure 6-8. New Critical Path

Examining this new critical path placement, you can see that there is room for further performance improvement through additional location assignments. The current slowest path is 9.775 ns of delay. Manually moving the LABs in this critical path and placing them between the M4K and M512 endpoints, and subsequently recompiling, shows improved results not only for this path, but for several other paths, as this path contained a major timing bottleneck. The critical path between this start and endpoint was reduced to 8.797 ns (Figure 6–9). However, the entire design only improved to 100.30 MHz because other paths are now the slowest paths in the design. This illustrates that fixing one major bottleneck path can raise the entire design performance since one high fanout node can affect multiple timing paths, as was the case in this example.

Figure 6-9. Improved Results

In summary, this design example started with 65.30 MHz in the Stratix FPGA device, and was improved to 74.34 MHz. It was then taken from the Stratix FPGA device compile and improved to 100.30 MHz in the HardCopy Stratix design, for a performance improvement of 35%.

### **Conclusion**

Using performance-optimization techniques specifically for HardCopy Stratix devices can achieve significant performance improvement over the Stratix FPGA prototype device. Many of these changes must be incorporated up-front in the HARDCOPY\_FPGA\_PROTOTYPE so that your design is properly prepared for performance improvement after running the HardCopy Timing Optimization wizard.

The example discussed in this chapter demonstrates the process for performance improvement and various features in the Quartus II software available for use when optimizing your Stratix FPGA prototype and HardCopy Stratix device. It also demonstrates the importance of planning ahead for the HardCopy Stratix design implementation while continuing to work in the HARDCOPY\_FPGA\_PROTOTYPE design if you are going to seek performance improvement in the HardCopy Stratix device.