Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

### Details

| Product Status          | Obsolete                                                                       |

|-------------------------|--------------------------------------------------------------------------------|

| Туре                    | SC3850 Dual Core                                                               |

| Interface               | Ethernet, I <sup>2</sup> C, PCI, RGMII, Serial RapidIO, SGMII, SPI, UART/USART |

| Clock Rate              | 1GHz                                                                           |

| Non-Volatile Memory     | ROM (96kB)                                                                     |

| On-Chip RAM             | 576kB                                                                          |

| Voltage - I/O           | 2.50V                                                                          |

| Voltage - Core          | 1.00V                                                                          |

| Operating Temperature   | -40°C ~ 105°C (TJ)                                                             |

| Mounting Type           | Surface Mount                                                                  |

| Package / Case          | 783-BBGA, FCBGA                                                                |

| Supplier Device Package | 783-FCPBGA (29x29)                                                             |

| Purchase URL            | https://www.e-xfl.com/product-detail/nxp-semiconductors/msc8252tag1000b        |

|                         |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

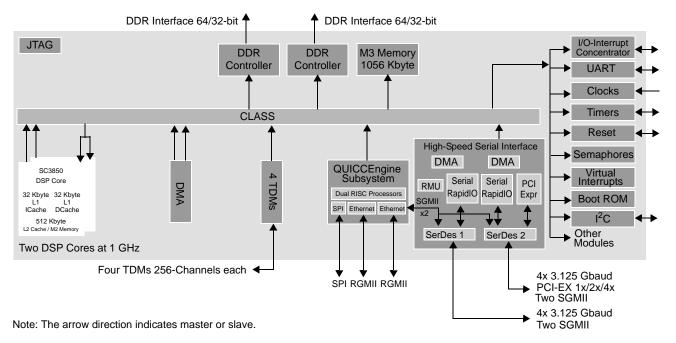

Figure 1. MSC8252 Block Diagram

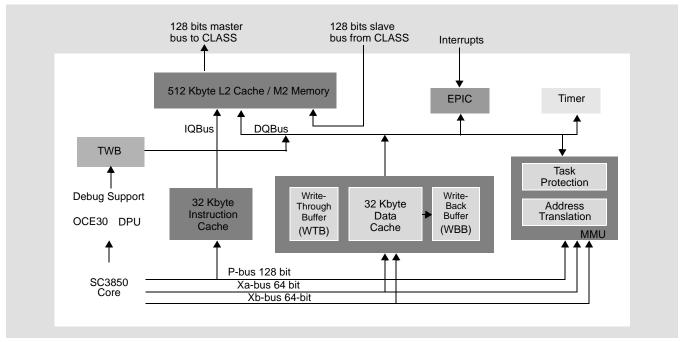

Figure 2. StarCore SC3850 DSP Subsystem Block Diagram

# **1.2 Signal List By Ball Location**

Table 1 presents the signal list sorted by ball number. When designing a board, make sure that the power rail for each signal is appropriately considered. The specified power rail must be tied to the voltage level specified in this document if any of the related signal functions are used (active)

**Note:** The information in Table 1 and Table 2 distinguishes among three concepts. First, the power pins are the balls of the device package used to supply specific power levels for different device subsystems (as opposed to signals). Second, the power rails are the electrical lines on the board that transfer power from the voltage regulators to the device. They are indicated here as the reference power rails for signal lines; therefore, the actual power inputs are listed as N/A with regard to the power rails. Third, symbols used in these tables are the names for the voltage levels (absolute, recommended, and so on) and not the power supplies themselves.

| Ball Number | Signal Name <sup>1,2</sup> | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|----------------------------|------------------------|--------------------|

| A2          | M2DQS3                     | I/O                    | GVDD2              |

| A3          | M2DQS3                     | I/O                    | GVDD2              |

| A4          | M2ECC0                     | I/O                    | GVDD2              |

| A5          | M2DQS8                     | I/O                    | GVDD2              |

| A6          | M2DQS8                     | I/O                    | GVDD2              |

| A7          | M2A5                       | 0                      | GVDD2              |

| A8          | M2CK1                      | 0                      | GVDD2              |

| A9          | M2CK1                      | 0                      | GVDD2              |

| A10         | M2CS0                      | 0                      | GVDD2              |

| A11         | M2BA0                      | 0                      | GVDD2              |

| A12         | M2CAS                      | 0                      | GVDD2              |

| A13         | M2DQ34                     | I/O                    | GVDD2              |

| A14         | M2DQS4                     | I/O                    | GVDD2              |

| A15         | M2DQS4                     | I/O                    | GVDD2              |

| A16         | M2DQ50                     | I/O                    | GVDD2              |

| A17         | M2DQS6                     | I/O                    | GVDD2              |

| A18         | M2DQS6                     | I/O                    | GVDD2              |

| A19         | M2DQ48                     | I/O                    | GVDD2              |

| A20         | M2DQ49                     | I/O                    | GVDD2              |

| A21         | VSS                        | Ground                 | N/A                |

| A22         | Reserved                   | NC                     | _                  |

| A23         | SXPVDD1                    | Power                  | N/A                |

| A24         | SXPVSS1                    | Ground                 | N/A                |

| A25         | Reserved                   | NC                     | _                  |

| A26         | Reserved                   | NC                     | _                  |

| A27         | SXCVDD1                    | Power                  | N/A                |

| A28         | SXCVSS1                    | Ground                 | N/A                |

| B1          | M2DQ24                     | I/O                    | GVDD2              |

| B2          | GVDD2                      | Power                  | N/A                |

| B3          | M2DQ25                     | I/O                    | GVDD2              |

| B4          | VSS                        | Ground                 | N/A                |

| B5          | GVDD2                      | Power                  | N/A                |

| B6          | M2ECC1                     | I/O                    | GVDD2              |

| B7          | VSS                        | Ground                 | N/A                |

| B8          | GVDD2                      | Power                  | N/A                |

### Table 1. Signal List by Ball Number

| Ball Number | Signal Name <sup>1,2</sup> | Pin Type <sup>10</sup> | Power Rail<br>Name |  |

|-------------|----------------------------|------------------------|--------------------|--|

| B9          | M2A13                      | 0                      | GVDD2              |  |

| B10         | VSS                        | Ground                 | N/A                |  |

| B11         | GVDD2                      | Power                  | N/A                |  |

| B12         | M2CS1                      | 0                      | GVDD2              |  |

| B13         | VSS                        | Ground                 | N/A                |  |

| B14         | GVDD2                      | Power                  | N/A                |  |

| B15         | M2DQ35                     | I/O                    | GVDD2              |  |

| B16         | VSS                        | Ground                 | N/A                |  |

| B17         | GVDD2                      | Power                  | N/A                |  |

| B18         | M2DQ51                     | I/O                    | GVDD2              |  |

| B19         | VSS                        | Ground                 | N/A                |  |

| B20         | GVDD2                      | Power                  | N/A                |  |

| B21         | Reserved                   | NC                     | _                  |  |

| B22         | Reserved                   | NC                     | _                  |  |

| B23         | SR1_TXD0                   | 0                      | SXPVDD1            |  |

| B24         | SR1_TXD0                   | 0                      | SXPVDD1            |  |

| B25         | SXCVDD1                    | Power                  | N/A                |  |

| B26         | SXCVSS1                    | Ground                 | N/A                |  |

| B27         | SR1_RXD0                   | I                      | SXCVDD1            |  |

| B28         | SR1_RXD0                   | I                      | SXCVDD1            |  |

| C1          | M2DQ28                     | I/O                    | GVDD2              |  |

| C2          | M2DM3                      | 0                      | GVDD2              |  |

| C3          | M2DQ26                     | I/O                    | GVDD2              |  |

| C4          | M2ECC4                     | I/O                    | GVDD2              |  |

| C5          | M2DM8                      | 0                      | GVDD2              |  |

| C6          | M2ECC2                     | I/O                    | GVDD2              |  |

| C7          | M2CKE1                     | 0                      | GVDD2              |  |

| C8          | M2CK0                      | 0                      | GVDD2              |  |

| C9          | M2CK0                      | 0                      | GVDD2              |  |

| C10         | M2BA1                      | 0                      | GVDD2              |  |

| C11         | M2A1                       | 0                      | GVDD2              |  |

| C12         | M2WE                       | 0                      | GVDD2              |  |

| C13         | M2DQ37                     | I/O                    | GVDD2              |  |

| C14         | M2DM4                      | 0                      | GVDD2              |  |

| C15         | M2DQ36                     | I/O                    | GVDD2              |  |

| C16         | M2DQ32                     | I/O                    | GVDD2              |  |

| C17         | M2DQ55                     | I/O                    | GVDD2              |  |

| C18         | M2DM6                      | 0                      | GVDD2              |  |

| C19         | M2DQ53                     | I/O                    | GVDD2              |  |

| C20         | M2DQ52                     | I/O                    | GVDD2              |  |

| C21         | Reserved                   | NC                     | —                  |  |

| C22         | SR1_IMP_CAL_RX             | I                      | SXCVDD1            |  |

| C23         | SXPVSS1                    | Ground                 | N/A                |  |

| C24         | SXPVDD1                    | Power                  | N/A                |  |

| C25         | SR1_REF_CLK                | l                      | SXCVDD1            |  |

| C26         | SR1_REF_CLK                | 1                      | SXCVDD1            |  |

| Ball Number Signal Name <sup>1,2</sup> |                              | Pin Type <sup>10</sup> | Power Rail<br>Name |  |

|----------------------------------------|------------------------------|------------------------|--------------------|--|

| E17                                    | M2DQ56                       | I/O                    | GVDD2              |  |

| E18                                    | M2DQ57                       | I/O                    | GVDD2              |  |

| E19                                    | M2DQS7                       | I/O                    | GVDD2              |  |

| E20                                    | Reserved                     | NC                     | —                  |  |

| E21                                    | Reserved                     | NC                     | —                  |  |

| E22                                    | Reserved                     | NC                     | —                  |  |

| E23                                    | SXPVDD1                      | Power                  | N/A                |  |

| E24                                    | SXPVSS1                      | Ground                 | N/A                |  |

| E25                                    | SR1_PLL_AGND <sup>9</sup>    | Ground                 | SXCVSS1            |  |

| E26                                    | SR1_PLL_AVDD <sup>9</sup>    | Power                  | SXCVDD1            |  |

| E27                                    | SXCVSS1                      | Ground                 | N/A                |  |

| E28                                    | SXCVDD1                      | Power                  | N/A                |  |

| F1                                     | VSS                          | Ground                 | N/A                |  |

| F2                                     | GVDD2                        | Power                  | N/A                |  |

| F3                                     | M2DQ16                       | I/O                    | GVDD2              |  |

| F4                                     | VSS                          | Ground                 | N/A                |  |

| F5                                     | GVDD2                        | Power                  | N/A                |  |

| F6                                     | M2DQ17                       | I/O                    | GVDD2              |  |

| F7                                     | VSS                          | Ground                 | N/A                |  |

| F8                                     | GVDD2                        | Power                  | N/A                |  |

| F9                                     | M2BA2                        | 0                      | GVDD2              |  |

| F10                                    | VSS                          | Ground                 | N/A                |  |

| F11                                    | GVDD2                        | Power                  | N/A                |  |

| F12                                    | M2A4                         | 0                      | GVDD2              |  |

| F13                                    | VSS                          | Ground                 | N/A                |  |

| F14                                    | GVDD2                        | Power                  | N/A                |  |

| F15                                    | M2DQ42                       | I/O                    | GVDD2              |  |

| F16                                    | VSS                          | Ground                 | N/A                |  |

| F17                                    | GVDD2                        | Power                  | N/A                |  |

| F18                                    | M2DQ58                       | I/O                    | GVDD2              |  |

| F19                                    | M2DQS7                       | I/O                    | GVDD2              |  |

| F20                                    | GVDD2                        | Power                  | N/A                |  |

| F21                                    | SXPVDD1                      | Power                  | N/A                |  |

| F22                                    | SXPVSS1                      | Ground                 | N/A                |  |

| F23                                    | SR1_TXD2/SG1_TX <sup>4</sup> | 0                      | SXPVDD1            |  |

| F24                                    | SR1_TXD2/SG1_TX <sup>4</sup> | 0                      | SXPVDD1            |  |

| F25                                    | SXCVDD1                      | Power                  | N/A                |  |

| F26                                    | SXCVSS1                      | Ground                 | N/A                |  |

| F27                                    | SR1_RXD2/SG1_RX <sup>4</sup> |                        | SXCVDD1            |  |

| F28                                    | SR1_RXD2/SG1_RX <sup>4</sup> |                        | SXCVDD1            |  |

| G1                                     | M2DQS2                       | I/O                    | GVDD2              |  |

| G2                                     | M2DQS2                       | I/O                    | GVDD2<br>GVDD2     |  |

| G3                                     | M2DQ19                       | I/O                    | GVDD2<br>GVDD2     |  |

| G4                                     | M2DM2                        | 0                      | GVDD2<br>GVDD2     |  |

| G5                                     | M2DQ21                       | I/O                    | GVDD2<br>GVDD2     |  |

| G6                                     | M2DQ22                       | I/O                    | GVDD2<br>GVDD2     |  |

| Ball Number | Signal Name <sup>1,2</sup>           | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|--------------------------------------|------------------------|--------------------|

| N23         | SR2_TXD2/PE_TXD2/SG1_TX <sup>4</sup> | 0                      | SXPVDD2            |

| N24         | SR2_TXD2/PE_TXD2/SG1_TX <sup>4</sup> | 0                      | SXPVDD2            |

| N25         | SXCVDD2                              | Power                  | N/A                |

| N26         | SXCVSS2                              | Ground                 | N/A                |

| N27         | SR2_RXD2/PE_RXD2/SG1_RX <sup>4</sup> | I                      | SXCVDD2            |

| N28         | SR2_RXD2/PE_RXD2/SG1_RX <sup>4</sup> | I                      | SXCVDD2            |

| P1          | CLKIN                                | I                      | QVDD               |

| P2          | EE0                                  | I                      | QVDD               |

| P3          | QVDD                                 | Power                  | N/A                |

| P4          | VSS                                  | Ground                 | N/A                |

| P5          | STOP_BS                              | 1                      | QVDD               |

| P6          | QVDD                                 | Power                  | N/A                |

| P7          | VSS                                  | Ground                 | N/A                |

| P8          | PLL0_AVDD <sup>9</sup>               | Power                  | VDD                |

| P9          | PLL2_AVDD <sup>9</sup>               | Power                  | VDD                |

| P10         | VSS                                  | Ground                 | N/A                |

| P11         | VDD                                  | Power                  | N/A                |

| P12         | VSS                                  | Ground                 | N/A                |

| P13         | VDD                                  | Power                  | N/A                |

| P14         | VSS                                  | Ground                 | N/A                |

| P15         | VSS                                  | Ground                 | N/A                |

| P16         | VSS                                  | Ground                 | N/A                |

| P17         | VSS                                  | Ground                 | N/A                |

| P18         | VSS                                  | Ground                 | N/A                |

| P19         | VDD                                  | Power                  | N/A                |

| P20         | Reserved                             | NC                     | _                  |

| P21         | Reserved                             | NC                     | _                  |

| P22         | Reserved                             | NC                     | _                  |

| P23         | SXPVDD2                              | Power                  | N/A                |

| P24         | SXPVSS2                              | Ground                 | N/A                |

| P25         | SR2_PLL_AGND <sup>9</sup>            | Ground                 | SXCVSS2            |

| P26         | SR2_PLL_AVDD <sup>9</sup>            | Power                  | SXCVDD2            |

| P27         | SXCVSS2                              | Ground                 | N/A                |

| P28         | SXCVDD2                              | Power                  | N/A                |

| R1          | VSS                                  | Ground                 | N/A                |

| R2          | NMI                                  |                        | QVDD               |

| R3          | NMI_OUT <sup>6</sup>                 | 0                      | QVDD               |

| R4          | HRESET <sup>6,7</sup>                | I/O                    | QVDD               |

| R5          | INT_OUT <sup>6</sup>                 | 0                      | QVDD               |

| R6          | EE1                                  | 0                      | QVDD               |

| R7          | VSS                                  | Ground                 | N/A                |

| R8          | PLL1_AVDD <sup>9</sup>               | Power                  | VDD                |

| R9          | VSS                                  | Ground                 | N/A                |

| R10         | VDD                                  | Power                  | N/A                |

| R11         | VSS                                  | Non-user               | N/A                |

| R12         | VDD                                  | Power                  | N/A                |

| Ball Number | Signal Name <sup>1,2</sup>         | Pin Type <sup>10</sup> | Power Rail<br>Name |  |

|-------------|------------------------------------|------------------------|--------------------|--|

| V21         | RCW_LSEL_3/RC20                    | I/O                    | NVDD               |  |

| V22         | RCW_LSEL_2/RC19                    | I/O                    | NVDD               |  |

| V23         | SXPVDD2                            | Power                  | N/A                |  |

| V24         | SXPVSS2                            | Ground                 | N/A                |  |

| V25         | RCW_LSEL_1/RC18                    | I/O                    | NVDD               |  |

| V26         | RC21                               | I                      | NVDD               |  |

| V27         | SXCVDD2                            | Power                  | N/A                |  |

| V28         | SXCVSS2                            | Ground                 | N/A                |  |

| W1          | VSS                                | Ground                 | N/A                |  |

| W2          | GVDD1                              | Power                  | N/A                |  |

| W3          | M1DM1                              | 0                      | GVDD1              |  |

| W4          | VSS                                | Ground                 | N/A                |  |

| W5          | GVDD1                              | Power                  | N/A                |  |

| W6          | M1DQ0                              | I/O                    | GVDD1              |  |

| W7          | VSS                                | Ground                 | N/A                |  |

| W8          | GVDD1                              | Power                  | N/A                |  |

| W9          | M1DQ5                              | I/O                    | GVDD1              |  |

| W10         | VDD                                | Power                  | N/A                |  |

| W11         | VSS                                | Ground                 | N/A                |  |

| W12         | VDD                                | Power                  | N/A                |  |

| W13         | VSS                                | Ground                 | N/A                |  |

| W14         | VDD                                | Power                  | N/A                |  |

| W15         | VSS                                | Ground                 | N/A                |  |

| W16         | VDD                                | Power                  | N/A                |  |

| W17         | VSS                                | Ground                 | N/A                |  |

| W18         | VDD                                | Power                  | N/A                |  |

| W19         | VSS                                | Ground                 | N/A                |  |

| W20         | VSS                                | Ground                 | N/A                |  |

| W21         | RCW_LSEL0/RC17                     | I/O                    | NVDD               |  |

| W22         | GPIO19/SPI_MISO <sup>5,8</sup>     | I/O                    | NVDD               |  |

| W23         | VSS                                | Ground                 | N/A                |  |

| W24         | NVDD                               | Power                  | N/A                |  |

| W25         | GPI011/IRQ11/RC11 <sup>5,8</sup>   | I/O                    | NVDD               |  |

| W26         | GPIO3/DRQ1/IRQ3/RC3 <sup>5,8</sup> | I/O                    | NVDD               |  |

| W27         | GPIO7/IRQ7/RC7 <sup>5,8</sup>      | I/O                    | NVDD               |  |

| W28         | GPIO2/IRQ2/RC2 <sup>5,8</sup>      | I/O                    | NVDD               |  |

| Y1          | M1DQS1                             | I/O                    | GVDD1              |  |

| Y2          | M1DQS1                             | I/O                    | GVDD1              |  |

| Y3          | M1DQ10                             | I/O                    | GVDD1              |  |

| Y4          | M1DQ11                             | I/O                    | GVDD1              |  |

| Y5          | M1DQ14                             | I/O                    | GVDD1              |  |

| Y6          | M1DQ23                             | I/O                    | GVDD1              |  |

| Y7          | M1ODT0                             | 0                      | GVDD1              |  |

| Y8          | M1A12                              | 0                      | GVDD1              |  |

| Y9          | M1A14                              | 0                      | GVDD1              |  |

| Y10         | VSS                                | Ground                 | N/A                |  |

| Ball Number | Signal Name <sup>1,2</sup>          | Pin Type <sup>10</sup> | Power Rail<br>Name |  |

|-------------|-------------------------------------|------------------------|--------------------|--|

| AB1         | M1DQS2                              | I/O                    | GVDD1              |  |

| AB2         | M1DQS2                              | I/O                    | GVDD1              |  |

| AB3         | M1DQ19                              | I/O                    | GVDD1              |  |

| AB4         | M1DM2                               | 0                      | GVDD1              |  |

| AB5         | M1DQ21                              | I/O                    | GVDD1              |  |

| AB6         | M1DQ22                              | I/O                    | GVDD1              |  |

| AB7         | M1CKE0                              | 0                      | GVDD1              |  |

| AB8         | M1A11                               | 0                      | GVDD1              |  |

| AB9         | M1A7                                | 0                      | GVDD1              |  |

| AB10        | M1CK2                               | 0                      | GVDD1              |  |

| AB11        | M1APAR_OUT                          | 0                      | GVDD1              |  |

| AB12        | M1ODT1                              | 0                      | GVDD1              |  |

| AB13        | M1APAR_IN                           | I                      | GVDD1              |  |

| AB14        | M1DQ43                              | I/O                    | GVDD1              |  |

| AB15        | M1DM5                               | 0                      | GVDD1              |  |

| AB16        | M1DQ44                              | I/O                    | GVDD1              |  |

| AB17        | M1DQ40                              | I/O                    | GVDD1              |  |

| AB18        | M1DQ59                              | I/O                    | GVDD1              |  |

| AB19        | M1DM7                               | 0                      | GVDD1              |  |

| AB20        | M1DQ60                              | I/O                    | GVDD1              |  |

| AB21        | VSS                                 | Ground                 | N/A                |  |

| AB22        | GPIO31/I2C_SDA <sup>5,8</sup>       | I/O                    | NVDD               |  |

| AB23        | GPIO27/TMR4/RCW_SRC0 <sup>5,8</sup> | I/O                    | NVDD               |  |

| AB24        | GPIO25/TMR2/RCW_SRC1 <sup>5,8</sup> | I/O                    | NVDD               |  |

| AB25        | GPIO24/TMR1/RCW_SRC2 <sup>5,8</sup> | I/O                    | NVDD               |  |

| AB26        | GPIO10/IRQ10/RC10 <sup>5,8</sup>    | I/O                    | NVDD               |  |

| AB27        | GPIO5/IRQ5/RC5 <sup>5,8</sup>       | I/O                    | NVDD               |  |

| AB28        | GPIO0/IRQ0/RC0 <sup>5,8</sup>       | I/O                    | NVDD               |  |

| AC1         | VSS                                 | Ground                 | N/A                |  |

| AC2         | GVDD1                               | Power                  | N/A                |  |

| AC3         | M1DQ16                              | I/O                    | GVDD1              |  |

| AC4         | VSS                                 | Ground                 | N/A                |  |

| AC5         | GVDD1                               | Power                  | N/A                |  |

| AC6         | M1DQ17                              | I/O                    | GVDD1              |  |

| AC7         | VSS                                 | Ground                 | N/A                |  |

| AC8         | GVDD1                               | Power                  | N/A                |  |

| AC9         | M1BA2                               | 0                      | GVDD1              |  |

| AC10        | VSS                                 | Ground                 | N/A                |  |

| AC11        | GVDD1                               | Power                  | N/A                |  |

| AC12        | M1A4                                | 0                      | GVDD1              |  |

| AC13        | VSS                                 | Ground                 | N/A                |  |

| AC14        | GVDD1                               | Power                  | N/A                |  |

| AC15        | M1DQ42                              | I/O                    | GVDD1              |  |

| AC16        | VSS                                 | Ground                 | N/A                |  |

| AC17        | GVDD1                               | Power                  | N/A                |  |

| AC18        | M1DQ58                              | I/O                    | GVDD1              |  |

#### **Electrical Characteristics** 2

This document contains detailed information on power considerations, DC/AC electrical characteristics, and AC timing specifications. For additional information, see the MSC8252 Reference Manual.

#### **Maximum Ratings** 2.1

In calculating timing requirements, adding a maximum value of one specification to a minimum value of another specification does not yield a reasonable sum. A maximum specification is calculated using a worst case variation of process parameter values in one direction. The minimum specification is calculated using the worst case for the same parameters in the opposite direction. Therefore, a "maximum" value for a specification never occurs in the same device with a "minimum" value for another specification; adding a maximum to a minimum represents a condition that can never exist.

Table 2 describes the maximum electrical ratings for the MSC8252.

| Rating                                                  | Power Rail Name     | Symbol                                                            | Value                                     | Unit        |

|---------------------------------------------------------|---------------------|-------------------------------------------------------------------|-------------------------------------------|-------------|

| Core supply voltage Cores 0–3                           | VDD                 | V <sub>DD</sub>                                                   | -0.3 to 1.1                               | V           |

| PLL supply voltage <sup>3</sup>                         |                     | V <sub>DDPLL0</sub><br>V <sub>DDPLL1</sub><br>V <sub>DDPLL2</sub> | -0.3 to 1.1<br>-0.3 to 1.1<br>-0.3 to 1.1 | V<br>V<br>V |

| M3 memory supply voltage                                | M3VDD               | V <sub>DDM3</sub>                                                 | -0.3 to 1.1                               | V           |

| DDR memory supply voltage<br>• DDR2 mode<br>• DDR3 mode | GVDD1, GVDD2        | V <sub>DDDDR</sub>                                                | -0.3 to 1.98<br>-0.3 to 1.65              | V<br>V      |

| DDR reference voltage                                   | MVREF               | $MV_{REF}$                                                        | –0.3 to 0.51 $\times$ $V_{DDDDR}$         | V           |

| Input DDR voltage                                       |                     | VINDDR                                                            | -0.3 to V <sub>DDDDR</sub> + 0.3          | V           |

| I/O voltage excluding DDR and RapidIO lines             | NVDD, QVDD          | V <sub>DDIO</sub>                                                 | -0.3 to 2.625                             | V           |

| Input I/O voltage                                       |                     | V <sub>INIO</sub>                                                 | –0.3 to V <sub>DDIO</sub> + 0.3           | V           |

| RapidIO pad voltage                                     | SXPVDD1,<br>SXPVDD2 | V <sub>DDSXP</sub>                                                | -0.3 to 1.26                              | V           |

| Rapid I/O core voltage                                  | SXCVDD1,<br>SXCVDD2 | V <sub>DDSXC</sub>                                                | -0.3 to 1.21                              | V           |

| Rapid I/O PLL voltage <sup>3</sup>                      |                     | V <sub>DDRIOPLL</sub>                                             | -0.3 to 1.21                              | V           |

| Input RapidIO I/O voltage                               |                     | V <sub>INRIO</sub>                                                | -0.3 to V <sub>DDSXC</sub> + 0.3          | V           |

| Operating temperature                                   |                     | TJ                                                                | -40 to 105                                | °C          |

| Storage temperature range                               |                     | T <sub>STG</sub>                                                  | -55 to +150                               | °C          |

### Table 2. Absolute Maximum Ratings

2. Absolute maximum ratings are stress ratings only, and functional operation at the maximum is not guaranteed. Stress beyond the listed limits may affect device reliability or cause permanent damage.

3. PLL supply voltage is specified at input of the filter and not at pin of the MSC8252 (see Figure 37 and Figure 38)

rical Characteristics

# 2.2 Recommended Operating Conditions

Table 3 lists recommended operating conditions. Proper device operation outside of these conditions is not guaranteed.

| Rating                                                                                                    | Symbol                                  | Min                                                                                                               | Nominal                                         | Мах                                       | Unit           |

|-----------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-------------------------------------------|----------------|

| Core supply voltage                                                                                       | V <sub>DD</sub>                         | 0.97                                                                                                              | 1.0                                             | 1.05                                      | V              |

| M3 memory supply voltage                                                                                  | V <sub>DDM3</sub>                       | 0.97                                                                                                              | 1.0                                             | 1.05                                      | V              |

| DDR memory supply voltage <ul> <li>DDR2 mode</li> <li>DDR3 mode</li> <li>DDR reference voltage</li> </ul> | V <sub>DDDDR</sub><br>MV <sub>REF</sub> | 1.7<br>1.425<br>0.49 × V <sub>DDDDR</sub>                                                                         | 1.8<br>1.5<br>0.5 × V <sub>DDDDR</sub>          | 1.9<br>1.575<br>0.51 × V <sub>DDDDR</sub> | V<br>V<br>V    |

| I/O voltage excluding DDR and<br>RapidIO lines                                                            | V <sub>DDIO</sub>                       | 2.375                                                                                                             | 2.5                                             | 2.625                                     | V              |

| Rapid I/O pad voltage                                                                                     | V <sub>DDSXP</sub>                      | 0.97                                                                                                              | 1.0                                             | 1.05                                      | V              |

| Rapid I/O core voltage                                                                                    | V <sub>DDSXC</sub>                      | 0.97                                                                                                              | 1.0                                             | 1.05                                      | V              |

| Operating temperature range:<br>• Standard<br>• Higher<br>• Extended                                      | TJ<br>TJ<br>TA<br>TJ                    | 0<br>0<br>40<br>                                                                                                  |                                                 | 90<br>105<br>—<br>105                     | 0°<br>0°<br>0° |

| Typical power: 1 GHz at 1.0 V <sup>1</sup>                                                                | Р                                       | —                                                                                                                 | 3.54                                            | —                                         | W              |

| <ul><li>Two cores run</li><li>A single 64 bit</li></ul>                                                   | ning at 1 GHz, Cor<br>DDR3 running at 8 | or a device running under<br>e voltage at 1V, 75% utili<br>300 MHz, 50% utilization<br>press controller disabled, | zation (50% control/50% (50% reads/50% writes). | DSP).                                     | oller          |

| Table 3. Recommended Operating Conditions |

|-------------------------------------------|

|-------------------------------------------|

# 2.3 Thermal Characteristics

A junction temperature of 60°C.

Table 4 describes thermal characteristics of the MSC8252 for the FC-PBGA packages.

disabled, 1 RGMII at 1 Gbps 50% loading.

| Characteristic                |                                                                                                                                                                                                                                                                                                          | Sumbol                     | FC-PBGA<br>29 × 29 mm <sup>2</sup> |                                                      |                    |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------------|------------------------------------------------------|--------------------|

|                               |                                                                                                                                                                                                                                                                                                          | Symbol                     | Natural<br>Convection              | 200 ft/min<br>(1 m/s) airflow                        | Unit               |

| Junction-to                   | o-ambient <sup>1, 2</sup>                                                                                                                                                                                                                                                                                | R <sub>0JA</sub>           | 18                                 | 12                                                   | °C/W               |

| Junction-to                   | o-ambient, four-layer board <sup>1, 2</sup>                                                                                                                                                                                                                                                              | $R_{	ext{	heta}JA}$        | 13                                 | 9                                                    | °C/W               |

| Junction-to                   | o-board (bottom) <sup>3</sup>                                                                                                                                                                                                                                                                            | R <sub>0JB</sub>           | 5                                  |                                                      | °C/W               |

| Junction-to-case <sup>4</sup> |                                                                                                                                                                                                                                                                                                          | R <sub>θJC</sub>           | 0.6                                |                                                      | °C/W               |

|                               | <ol> <li>Junction temperature is a function of die<br/>temperature, ambient temperature, air flo<br/>resistance.</li> <li>Junction-to-ambient thermal resistance of<br/>specification for the specified package.</li> <li>Junction-to-board thermal resistance det<br/>the specified package.</li> </ol> | ow, power dissipation of c | other components on th             | e board, and board therr<br>-6. Thermal test board m | nal<br>ieets JEDEC |

|                               | 4. Junction-to-case at the top of the package                                                                                                                                                                                                                                                            | e determined using MIL-    | STD-883 Method 1012                | .1. The cold plate temper                            | ature is used      |

for the case temperature. Reported value includes the thermal resistance of the interface layer

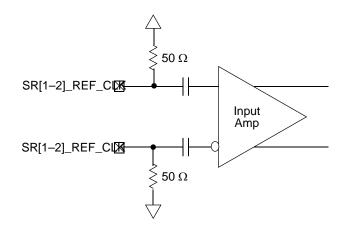

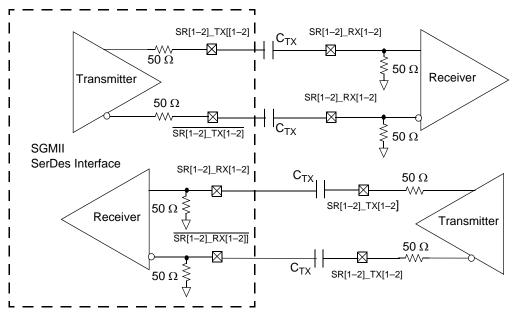

### 2.5.2.2 SerDes Reference Clock Receiver Characteristics

The SerDes reference clock inputs are applied to an internal PLL whose output creates the clock used by the corresponding SerDes lanes. The SerDes reference clock inputs are SR1\_REF\_CLK/SR1\_REF\_CLK or SR2\_REF\_CLK/SR2\_REF\_CLK. Figure 5 shows a receiver reference diagram of the SerDes reference clocks.

### Figure 5. Receiver of SerDes Reference Clocks

The characteristics of the clock signals are as follows:

- The supply voltage requirements for V<sub>DDSXC</sub> are as specified in **Table 3**.

- The SerDes reference clock receiver reference circuit structure is as follows:

- The SR[1–2]\_REF\_CLK and SR[1–2]\_REF\_CLK are internally AC-coupled differential inputs as shown in Figure 5. Each differential clock input (SR[1–2]\_REF\_CLK or SR[1–2]\_REF\_CLK) has on-chip 50-Ω termination to GND<sub>SXC</sub> followed by on-chip AC-coupling.

- The external reference clock driver must be able to drive this termination.

- The SerDes reference clock input can be either differential or single-ended. Refer to the differential mode and single-ended mode descriptions below for detailed requirements.

- The maximum average current requirement also determines the common mode voltage range.

- When the SerDes reference clock differential inputs are DC coupled externally with the clock driver chip, the maximum average current allowed for each input pin is 8 mA. In this case, the exact common mode input voltage is not critical as long as it is within the range allowed by the maximum average current of 8 mA because the input is AC-coupled on-chip.

- This current limitation sets the maximum common mode input voltage to be less than 0.4 V (0.4 V / 50 = 8 mA) while the minimum common mode input level is 0.1 V above GND<sub>SXC</sub>. For example, a clock with a 50/50 duty cycle can be produced by a clock driver with output driven by its current source from 0 mA to 16 mA (0–0.8 V), such that each phase of the differential input has a single-ended swing from 0 V to 800 mV with the common mode voltage at 400 mV.

- If the device driving the SR[1–2]\_REF\_CLK and  $\overline{SR[1-2]}_REF_CLK$  inputs cannot drive 50  $\Omega$  to GND<sub>SXC</sub> DC or the drive strength of the clock driver chip exceeds the maximum input current limitations, it must be AC-coupled externally.

- The input amplitude requirement is described in detail in the following sections.

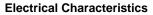

Figure 13 shows the DDR SDRAM output timing diagram.

Figure 13. DDR SDRAM Output Timing

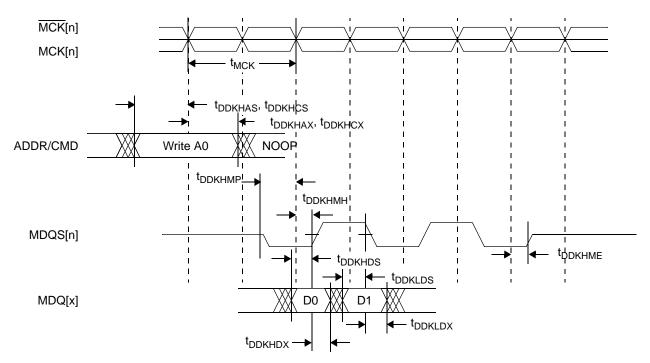

Figure 14 provides the AC test load for the DDR2 and DDR3 controller bus.

Figure 14. DDR2 and DDR3 Controller Bus AC Test Load

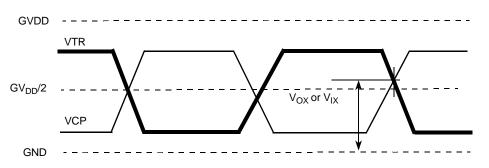

# 2.6.1.3 DDR2 and DDR3 SDRAM Differential Timing Specifications

This section describes the DC and AC differential timing specifications for the DDR2 and DDR3 SDRAM controller interface. Figure 15 shows the differential timing specification.

Figure 15. DDR2 and DDR3 SDRAM Differential Timing Specifications

Note: VTR specifies the true input signal (such as MCK or MDQS) and VCP is the complementary input signal (such as  $\overline{MCK}$  or  $\overline{MDQS}$ ).

### MSC8252 Dual-Core Digital Signal Processor Data Sheet, Rev. 8

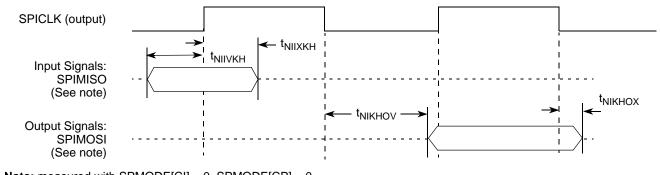

**Note:** measured with SPMODE[CI] = 0, SPMODE[CP] = 0

Figure 28. SPI AC Timing in Master Mode (Internal Clock)

# 3 Hardware Design Considerations

The following sections discuss areas to consider when the MSC8252 device is designed into a system.

# 3.1 Power Supply Ramp-Up Sequence

The following subsections describe the required device initialization sequence.

# 3.1.1 Clock, Reset, and Supply Coordination

Starting the device requires coordination between several inputs including: clock, reset, and power supplies. Follow this guidelines when starting up an MSC8252 device:

- <u>PORESET</u> and <u>TRST</u> must be asserted externally for the duration of the supply ramp-up, using the V<sub>DDIO</sub> supply. <u>TRST</u> deassertion does not have to be synchronized with <u>PORESET</u> deassertion. However, <u>TRST</u> must be deasserted before normal operation begins to ensure correct functionality of the device.

- CLKIN should toggle at least 32 cycles before PORESET deassertion to guarantee correct device operation. The 32 cycles should only be counted from the time after V<sub>DDIO</sub> reaches its nominal value (see timing 1 in Figure 33).

- CLKIN should either be stable low during ramp-up of V<sub>DDIO</sub> supply (and start its swings after ramp-up) or should swing within V<sub>DDIO</sub> range during V<sub>DDIO</sub> ramp-up, so its amplitude grows as V<sub>DDIO</sub> grows during ramp-up.

Figure 33 shows a sequence in which  $V_{DDIO}$  ramps-up after  $V_{DD}$  and CLKIN begins to toggle with the raise of  $V_{DDIO}$  supply.

### Figure 33. Supply Ramp-Up Sequence with V<sub>DD</sub> Ramping Before V<sub>DDIO</sub> and CLKIN Starting With V<sub>DDIO</sub>

Note: For details on power-on reset flow and duration, see the *Reset* chapter in the *MSC8252 Reference Manual*.

# 3.3 Clock and Timing Signal Board Layout Considerations

When laying out the system board, use the following guidelines:

- Keep clock and timing signal paths as short as possible and route with 50  $\Omega$  impedance.

- Use a serial termination resistor placed close to the clock buffer to minimize signal reflection. Use the following equation to compute the resistor value:

Rterm = Rim - Rbuf

where Rim = trace characteristic impedance

Rbuf = clock buffer internal impedance.

# 3.4 SGMII AC-Coupled Serial Link Connection Example

Figure 39 shows an example of a 4-wire AC-coupled serial link connection. For additional layout suggestions, see *AN3556 MSC815x High Speed Serial Interface Hardware Design Considerations*, available on the Freescale website or from your local sales office or representative.

Figure 39. 4-Wire AC-Coupled SGMII Serial Link Connection Example

#### 3.5.1 **DDR Memory Related Pins**

This section discusses the various scenarios that can be used with either of the MSC8252 DDR ports.

The signal names in Table 40, Table 41 and Table 42 are generic names for a DDR SDRAM interface. For actual pin Note: names refer to Table 1.

#### 3.5.1.1 **DDR Interface Is Not Used**

| Signal Name              | Pin Connection |  |

|--------------------------|----------------|--|

| MDQ[0-63]                | NC             |  |

| MDQS[7-0]                | NC             |  |

| MDQS[7-0]                | NC             |  |

| MA[15–0]                 | NC             |  |

| MCK[0-2]                 | NC             |  |

| MCK[0-2]                 | NC             |  |

| MCS[1-0]                 | NC             |  |

| MDM[7-0]                 | NC             |  |

| MBA[2-0]                 | NC             |  |

| MCAS                     | NC             |  |

| MCKE[1-0]                | NC             |  |

| MODT[1-0]                | NC             |  |

| MMDIC[1-0]               | NC             |  |

| MRAS                     | NC             |  |

| MWE                      | NC             |  |

| MECC[7-0]                | NC             |  |

| MDM8                     | NC             |  |

| MDQS8                    | NC             |  |

| MDQS8                    | NC             |  |

| MAPAR_OUT                | NC             |  |

| MAPAR_IN                 | NC             |  |

| MVREF <sup>3</sup>       | NC             |  |

| GVDD1/GVDD2 <sup>3</sup> | NC             |  |

### Table 40. Connectivity of DDR Related Pins When the DDR Interface Is Not Used

Clocks and General Configuration Registers chapters in the MSC8252 Reference Manual for details.

For MSC8252 Revision 1 silicon, these pins were connected to GND. For newer revisions of the MSC8252, connecting these 3. pins to GND increases device power consumption.

ware Design Considerations

## 3.5.1.2 DDR Interface Is Used With 32-Bit DDR Memory Only

Table 41 lists unused pin connection when using 32-bit DDR memory. The 32 most significant data lines are not used.

### Table 41. Connectivity of DDR Related Pins When Using 32-bit DDR Memory Only

| Signal Name | Pin Connection |  |

|-------------|----------------|--|

| MDQ[31-0]   | in use         |  |

| MDQ[63-32]  | NC             |  |

| MDQS[3-0]   | in use         |  |

| MDQS[7-4]   | NC             |  |

| MDQS[3-0]   | in use         |  |

| MDQS[7-4]   | NC             |  |

| MA[15–0]    | in use         |  |

| MCK[2-0]    | in use         |  |

| MCK[2-0]    | in use         |  |

| MCS[1-0]    | in use         |  |

| MDM[3-0]    | in use         |  |

| MDM[7-4]    | NC             |  |

| MBA[2-0]    | in use         |  |

| MCAS        | in use         |  |

| MCKE[1-0]   | in use         |  |

| MODT[1-0]   | in use         |  |

| MMDIC[1–0]  | in use         |  |

| MRAS        | in use         |  |

| MWE         | in use         |  |

| MVREF       | in use         |  |

| GVDD1/GVDD2 | in use         |  |

For MSC8252 Revision 1 silicon, these pins were connected to GND (or VDD). For newer revisions of the MSC8252, connecting these pins to GND increases device power consumption.

### 3.5.1.3 ECC Unused Pin Connections

When the error code correction mechanism is not used in any 32- or 64-bit DDR configuration, refer to Table 42 to determine the correct pin connections.

| Signal Name |                                                                                                                                                                                                                                                                                                                                     | Signal Name | Pin connection |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------|--|

| MECC[7-0]   |                                                                                                                                                                                                                                                                                                                                     |             | NC             |  |

| MDM8 NC     |                                                                                                                                                                                                                                                                                                                                     | NC          |                |  |

| MDQS8 NC    |                                                                                                                                                                                                                                                                                                                                     | NC          |                |  |

| MDQS8       | IS8 NC                                                                                                                                                                                                                                                                                                                              |             | NC             |  |

| Notes:      | <ol> <li>For the signals listed in this table, the initial M stands for M1 or M2 depending on which DDR controller is not used.</li> <li>For MSC8252 Revision 1 silicon, these pins were connected to GND (or VDD). For newer revisions of the MSC8252, connecting these pins to GND increases device power consumption.</li> </ol> |             |                |  |

#### MSC8252 Dual-Core Digital Signal Processor Data Sheet, Rev. 8

### 3.5.1.4 DDR2 Unused MAPAR Pin Connections

When the MAPAR signals are not used, refer to Table 43 to determine the correct pin connections.

| Table 43. | Connectivity | of MAPAR | Pins for DDR2 |

|-----------|--------------|----------|---------------|

|-----------|--------------|----------|---------------|

| Signal Name  |                                                                                                                                                                                                                                                                                                                                 | Signal Name | Pin connection |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------|

| MAPAR_OUT NC |                                                                                                                                                                                                                                                                                                                                 | NC          |                |

| MAPAR_IN NC  |                                                                                                                                                                                                                                                                                                                                 | NC          |                |

| Notes:       | <ol> <li>For the signals listed in this table, the initial M stands for M1 or M2 depending on which DDR controller is used for DDR2.</li> <li>For MSC8252 Revision 1 silicon, these pins were connected to GND. For newer revisions of the MSC8252, connecting these pins to GND increases device power consumption.</li> </ol> |             |                |

# 3.5.2 HSSI-Related Pins

### 3.5.2.1 HSSI Port Is Not Used

The signal names in Table 44 and Table 45 are generic names for a RapidIO interface. For actual pin names refer to Table 1.

| NC     |

|--------|

| NC     |

| SXCVSS |

| SXCVSS |

| SXCVSS |

| SXCVSS |

| NC     |

| NC     |

| In use |

|        |

### 3.5.2.2 HSSI Specific Lane Is Not Used

### Table 45. Connectivity of HSSI Related Pins When Specific Lane Is Not Used

| Signal Name     | Pin Connection |

|-----------------|----------------|

| SR_IMP_CAL_RX   | In use         |

| SR_IMP_CAL_TX   | In use         |

| SR[1-2]_REF_CLK | In use         |

| SR[1–2]_REF_CLK | In use         |

#### MSC8252 Dual-Core Digital Signal Processor Data Sheet, Rev. 8

uct Documentation

# 6 **Product Documentation**

Following is a general list of supporting documentation:

- *MSC8252 Technical Data Sheet* (MSC8252). Details the signals, AC/DC characteristics, clock signal characteristics, package and pinout, and electrical design considerations of the MSC8252 device.

- *MSC8252 Reference Manual* (MSC8252RM). Includes functional descriptions of the extended cores and all the internal subsystems including configuration and programming information.

- Application Notes. Cover various programming topics related to the StarCore DSP core and the MSC8252 device.

- *QUICC Engine Block Reference Manual with Protocol Interworking* (QEIWRM). Provides detailed information regarding the QUICC Engine technology including functional description, registers, and programming information.

- *SC3850 DSP Core Reference Manual*. Covers the SC3850 core architecture, control registers, clock registers, program control, and instruction set.

- *MSC8156SC3850 DSP Core Subsystem Reference Manual*. Covers core subsystem architecture, functionality, and registers.

# 7 Revision History

Table 50 provides a revision history for this data sheet.

| Rev. | Date      | Description                                                                                                                                                                                                                         |

|------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | Apr. 2010 | Initial public release.                                                                                                                                                                                                             |

| 1    | May 2010  | <ul> <li>Changed connection for pins K17, L14, L16, M15, M17, and N14 from VDD to VSS in Table 1.</li> <li>Updated Section 3.1.2, <i>Power-On Ramp Time</i>.</li> </ul>                                                             |

| 2    | Jun 2010  | <ul> <li>Changed the number of cores in the first bullet on the first page from four to two.</li> <li>The correction to the L16 connection was not made in Rev. 1. Fixed the entry to change from VDD to VSS in Table 1.</li> </ul> |

| 3    | Dec 2010  | <ul> <li>Updated Table 16.</li> <li>Updated Section 3.1.2, Power-On Ramp Time.</li> <li>Updated Section 4, Ordering Information.</li> </ul>                                                                                         |

| 4    | Mar 2011  | <ul> <li>Updated Table 8.</li> <li>Updated Table 15.</li> <li>Updated Table 17.</li> <li>Updated Table 33.</li> <li>Updated Table 35.</li> <li>Updated Table 39.</li> </ul>                                                         |

| 5    | May 2011  | <ul> <li>Updated Table 1. Changed the pin types for the following:</li> <li>F25 from ground to power.</li> <li>F26 from power to ground.</li> <li>T6 from power to O.</li> </ul>                                                    |

| 6    | Oct 2011  | • Updated Table 34 and Table 35 to reflect 1 Gbps and 100 Mbps data rate instead of 1 GHz and 100 MHz.                                                                                                                              |

| 7    | Dec 2011  | Added note 4 to Table 39.                                                                                                                                                                                                           |

| 8    | Aug 2013  | Updated Section 4, "Ordering Information".                                                                                                                                                                                          |

### Table 50. Document Revision History

#### How to Reach Us:

Home Page: freescale.com

Web Support: freescale.com/support Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document.

Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: freescale.com/SalesTermsandConditions.

Freescale, the Freescale logo, CodeWarrior, ColdFire, ColdFire+, StarCore are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. QUICC Engine is a trademark of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2010–2013 Freescale Semiconductor, Inc.

> Document Number: MSC8252 Rev. 8 08/2013