Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Decails                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                 |

| Core Processor             | 8051                                                                     |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 18MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                               |

| Number of I/O              | 14                                                                       |

| Program Memory Size        | 2KB (2K x 8)                                                             |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 3.6V                                                              |

| Data Converters            | A/D 4x8b; D/A 1x8b                                                       |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 16-TSSOP (0.173", 4.40mm Width)                                          |

| Supplier Device Package    | 16-TSSOP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/p89lpc916fdh-118 |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Serial Flash In-Circuit Programming (ICP) allows simple production coding with commercial EPROM programmers. Flash security bits prevent reading of sensitive application programs.

- Watchdog timer with separate on-chip oscillator, requiring no external components. The Watchdog prescaler is selectable from 8 values.

- Low voltage brownout detect allows a graceful system shutdown when power fails. May optionally be configured as an interrupt.

- Idle and two different power-down reduced power modes. Improved wake-up from Power-down mode (a LOW interrupt input starts execution). Typical power-down current is 1 µA (total power-down with voltage comparators disabled).

- Active-LOW reset. On-chip power-on reset allows operation without external reset components. A reset counter and reset glitch suppression circuitry prevent spurious and incomplete resets. A software reset function is also available.

- Programmable port output configuration options: quasi-bidirectional, open drain, push-pull, input-only.

- Port 'input pattern match' detect. Port 0 may generate an interrupt when the value of the pins match or do not match a programmable pattern.

- LED drive capability (20 mA) on all port pins. A maximum limit is specified for the entire chip.

- Controlled slew rate port outputs to reduce EMI. Outputs have approximately 10 ns minimum ramp times.

- Only power and ground connections are required to operate the P89LPC915/916/917 when internal reset option is selected.

- Four interrupt priority levels.

- Five (P89LPC916), six (P89LPC915), or seven (P89LPC917) keypad interrupt inputs.

- Second data pointer.

- Schmitt trigger port inputs.

- Emulation support.

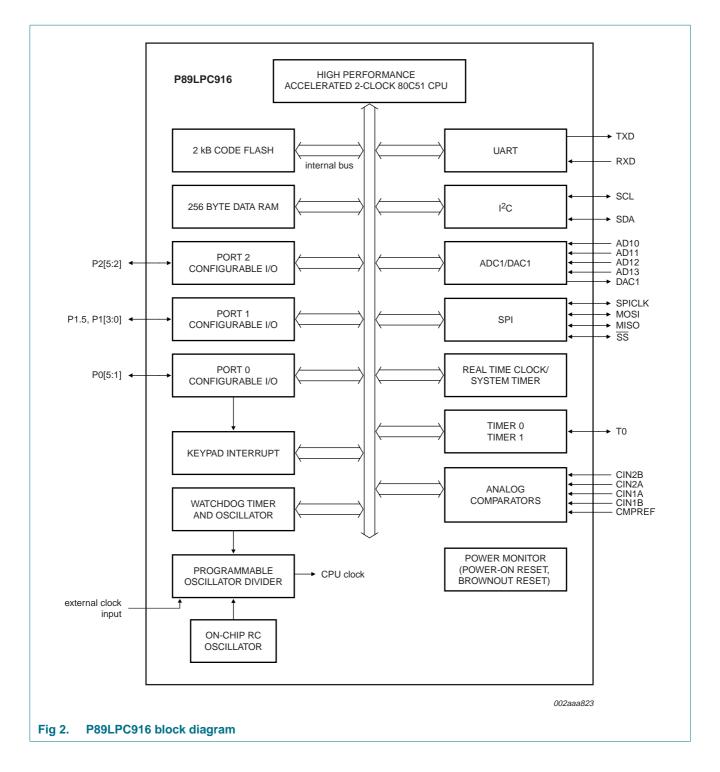

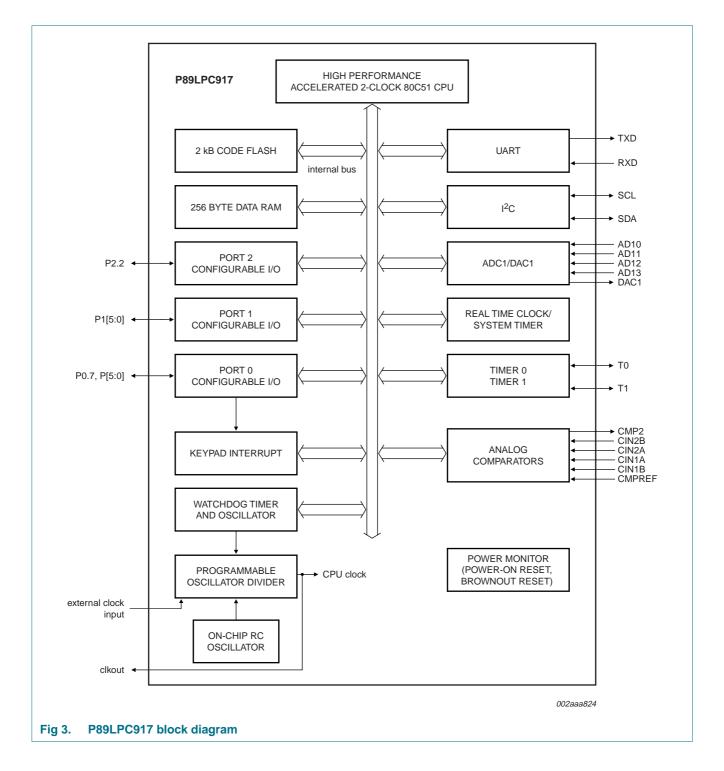

# 3. Product comparison overview

<u>Table 1</u> highlights the differences between these three devices. For a complete list of device features, please see <u>Section 2 "Features"</u>.

#### Table 1. Product comparison overview

| Type number | Comparator 2<br>output | SPI | T1 toggle/PWM | CLKOUT | INT1 | KBI |

|-------------|------------------------|-----|---------------|--------|------|-----|

| P89LPC915   | Х                      | -   | -             | -      | Х    | 6   |

| P89LPC916   | -                      | Х   | -             | -      | -    | 5   |

| P89LPC917   | Х                      | -   | Х             | Х      | Х    | 7   |

# **NXP Semiconductors**

# P89LPC915/916/917

#### 8-bit microcontrollers with accelerated two-clock 80C51 core

P89LPC915\_916\_917\_5

# **NXP Semiconductors**

# P89LPC915/916/917

#### 8-bit microcontrollers with accelerated two-clock 80C51 core

P89LPC915\_916\_917\_5

8-bit microcontrollers with accelerated two-clock 80C51 core

# Table 7. P89LPC915 special function registers ... continued \* indicates SFRs that are bit addressable. P89LPC9

| Name   | Description                                       | SFR         | Bit function | ons and ad  | Idresses    |              |             |             |              |             | Reset value   |           |

|--------|---------------------------------------------------|-------------|--------------|-------------|-------------|--------------|-------------|-------------|--------------|-------------|---------------|-----------|

|        |                                                   | addr.       | MSB          |             |             |              |             |             |              | LSB         | Hex           | Binary    |

| FMCON  | Program flash control (F                          | Read) E4H   | BUSY         | -           | -           | -            | HVA         | HVE         | SV           | OI          | 70            | 0111 0000 |

|        | Program flash control (V                          | Vrite) E4H  | FMCMD.<br>7  | FMCMD.<br>6 | FMCMD.<br>5 | FMCMD.<br>4  | FMCMD.<br>3 | FMCMD.<br>2 | FMCMD.<br>1  | FMCMD.<br>0 |               |           |

| FMDATA | Program flash data                                | E5H         |              |             |             |              |             |             |              |             | 00            | 0000 0000 |

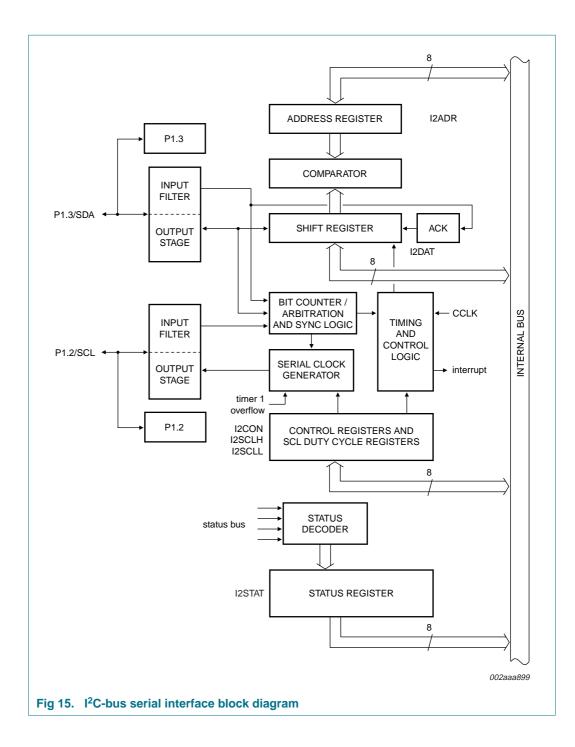

| I2ADR  | I <sup>2</sup> C slave address regist             | er DBH      | I2ADR.6      | I2ADR.5     | I2ADR.4     | I2ADR.3      | I2ADR.2     | I2ADR.1     | I2ADR.0      | GC          | 00            | 0000 0000 |

|        |                                                   | Bit address | DF           | DE          | DD          | DC           | DB          | DA          | D9           | <b>D8</b>   |               |           |

| I2CON* | I <sup>2</sup> C control register                 | D8H         | -            | I2EN        | STA         | STO          | SI          | AA          | -            | CRSEL       | 00            | x000 00x0 |

| I2DAT  | I <sup>2</sup> C data register                    | DAH         |              |             |             |              |             |             |              |             |               |           |

| I2SCLH | Serial clock generator/S duty cycle register high | CL DDH      |              |             |             |              |             |             |              |             | 00            | 0000 000  |

| I2SCLL | Serial clock generator/S duty cycle register low  | CL DCH      |              |             |             |              |             |             |              |             | 00            | 0000 000  |

| I2STAT | I <sup>2</sup> C status register                  | D9H         | STA.4        | STA.3       | STA.2       | STA.1        | STA.0       | 0           | 0            | 0           | F8            | 1111 100  |

|        |                                                   | Bit address | AF           | AE          | AD          | AC           | AB          | AA          | A9           | <b>A8</b>   |               |           |

| IEN0*  | Interrupt enable 0                                | A8H         | EA           | EWDRT       | EBO         | ES/ESR       | ET1         | EX1         | ET0          | EX0         | 00            | 0000 000  |

|        |                                                   | Bit address | EF           | EE          | ED          | EC           | EB          | EA          | E9           | <b>E8</b>   |               |           |

| IEN1*  | Interrupt enable 1                                | E8H         | EAD          | EST         | -           | -            | -           | EC          | EKBI         | EI2C        | 00[1]         | 00x0 000  |

|        |                                                   | Bit address | BF           | BE          | BD          | BC           | BB          | BA          | <b>B9</b>    | <b>B</b> 8  |               |           |

| IP0*   | Interrupt priority 0                              | B8H         | -            | PWDRT       | PBO         | PS/PSR       | PT1         | PX1         | PT0          | PX0         | 00[1]         | x000 000  |

| IP0H   | Interrupt priority 0 high                         | B7H         | -            | PWDRT<br>H  | PBOH        | PSH/<br>PSRH | PT1H        | PX1H        | PT0H         | PX0H        | 00 <u>[1]</u> | x000 0000 |

|        |                                                   | Bit address | FF           | FE          | FD          | FC           | FB          | FA          | F9           | F8          |               |           |

| IP1*   | Interrupt priority 1                              | F8H         | PAD          | PST         | -           | -            | -           | PC          | PKBI         | PI2C        | 00 <u>[1]</u> | 00x0 000  |

| IP1H   | Interrupt priority 1 high                         | F7H         | PADH         | PSTH        | -           | -            | -           | PCH         | PKBIH        | PI2CH       | 00 <u>[1]</u> | 00x0 000  |

| KBCON  | Keypad control register                           | 94H         | -            | -           | -           | -            | -           | -           | PATN<br>_SEL | KBIF        | 00 <u>[1]</u> | XXXX XXOC |

| KBMASK | Keypad interrupt mask register                    | 86H         |              |             |             |              |             |             |              |             | 00            | 0000 000  |

| KBPATN | Keypad pattern register                           |             |              |             |             |              |             |             |              |             | FF            | 1111 111  |

20 of 75

Product data sheet

#### Table 8. P89LPC916 special function registers ... continued \* indicates SFRs that are bit addressable. P89LPC

| Name          | )  | Description                                       | SFR         |             | ons and ac  | Idresses    |              |             |             |              |             | Rese          | t value   |

|---------------|----|---------------------------------------------------|-------------|-------------|-------------|-------------|--------------|-------------|-------------|--------------|-------------|---------------|-----------|

| Name          |    |                                                   | addr.       | MSB         |             |             |              |             |             |              | LSB         | Hex           | Binary    |

| FMCO          | N  | Program flash control (F                          | Read) E4H   | BUSY        | -           | -           | -            | HVA         | HVE         | SV           | OI          | 70            | 0111 0000 |

|               |    | Program flash control (V                          | Vrite) E4H  | FMCMD.<br>7 | FMCMD.<br>6 | FMCMD.<br>5 | FMCMD.<br>4  | FMCMD.<br>3 | FMCMD.<br>2 | FMCMD.<br>1  | FMCMD.<br>0 |               |           |

| FMDA          | TA | Program flash data                                | E5H         |             |             |             |              |             |             |              |             | 00            | 0000 0000 |

| I2ADR         | र  | I <sup>2</sup> C slave address regist             | er DBH      | I2ADR.6     | I2ADR.5     | I2ADR.4     | I2ADR.3      | I2ADR.2     | I2ADR.1     | I2ADR.0      | GC          | 00            | 0000 0000 |

|               |    |                                                   | Bit address | DF          | DE          | DD          | DC           | DB          | DA          | D9           | <b>D8</b>   |               |           |

| 12CON         | ۷* | I <sup>2</sup> C control register                 | D8H         | -           | I2EN        | STA         | STO          | SI          | AA          | -            | CRSEL       | 00            | x000 00x0 |

| I2DAT         | •  | I <sup>2</sup> C data register                    | DAH         |             |             |             |              |             |             |              |             |               |           |

| I2SCL         | .H | Serial clock generator/S duty cycle register high | CL DDH      |             |             |             |              |             |             |              |             | 00            | 0000 0000 |

| I2SCL         | L  | Serial clock generator/S duty cycle register low  | CL DCH      |             |             |             |              |             |             |              |             | 00            | 0000 0000 |

| I2STAT        | Т  | I <sup>2</sup> C status register                  | D9H         | STA.4       | STA.3       | STA.2       | STA.1        | STA.0       | 0           | 0            | 0           | F8            | 1111 100  |

|               |    |                                                   | Bit address | AF          | AE          | AD          | AC           | AB          | AA          | A9           | <b>A8</b>   |               |           |

| IEN0*         |    | Interrupt enable 0                                | A8H         | EA          | EWDRT       | EBO         | ES/ESR       | ET1         | -           | ET0          | EX0         | 00            | 0000 0000 |

|               |    |                                                   | Bit address | EF          | EE          | ED          | EC           | EB          | EA          | E9           | <b>E8</b>   |               |           |

| IEN1*         |    | Interrupt enable 1                                | E8H         | EAD         | EST         | -           | -            | ESPI        | EC          | EKBI         | EI2C        | 00[1]         | 00x0 0000 |

|               |    |                                                   | Bit address | BF          | BE          | BD          | BC           | BB          | BA          | <b>B9</b>    | <b>B8</b>   |               |           |

| IP0*          |    | Interrupt priority 0                              | B8H         | -           | PWDRT       | PBO         | PS/PSR       | PT1         | -           | PT0          | PX0         | 00[1]         | x000 0000 |

| IP0H          |    | Interrupt priority 0 high                         | B7H         | -           | PWDRT<br>H  | PBOH        | PSH/<br>PSRH | PT1H        | -           | PT0H         | PX0H        | 00[1]         | x000 0000 |

|               |    |                                                   | Bit address | FF          | FE          | FD          | FC           | FB          | FA          | F9           | F8          |               |           |

| IP1*          |    | Interrupt priority 1                              | F8H         | PAD         | PST         | -           | -            | PSPI        | PC          | PKBI         | PI2C        | 00[1]         | 00x0 0000 |

| IP1H          |    | Interrupt priority 1 high                         | F7H         | PADH        | PSTH        | -           | -            | PSPIH       | PCH         | PKBIH        | PI2CH       | 00[1]         | 00x0 0000 |

| KBCO          | N  | Keypad control register                           | 94H         | -           | -           | -           | -            | -           | -           | PATN<br>_SEL | KBIF        | 00 <u>[1]</u> | xxxx xx00 |

| kbma<br>Kbpat | SK | Keypad interrupt mask register                    | 86H         |             |             |             |              |             |             |              |             | 00            | 0000 0000 |

| KBPAT         | TN | Keypad pattern register                           |             |             |             |             |              |             |             |              |             | FF            | 1111 111  |

# **NXP Semiconductors**

8-bit microcontrollers with accelerated two-clock 80C51 core P89LPC915/916/917

ights reserved. 24 of 75

Product data sheet

# Table 8. P89LPC916 special function registers ... continued \* indicates SFRs that are bit addressable.

| Name   | Description                    | SFR     | Bit function | ons and ad | dresses        |               |               |               |               |           | Rese                        | t value  |

|--------|--------------------------------|---------|--------------|------------|----------------|---------------|---------------|---------------|---------------|-----------|-----------------------------|----------|

|        |                                | addr.   | MSB          |            |                |               |               |               |               | LSB       | Hex                         | Binary   |

|        | Bit                            | address | 87           | 86         | 85             | 84            | 83            | 82            | 81            | 80        |                             |          |

| P0*    | Port 0                         | 80H     | -            | -          | CMPREF<br>/KB5 | CIN1A<br>/KB4 | CIN1B<br>/KB3 | CIN2A<br>/KB2 | CIN2B<br>/KB1 | -         | <u>[1]</u>                  |          |

|        | Bit                            | address | 97           | 96         | 95             | 94            | 93            | 92            | 91            | 90        |                             |          |

| P1*    | Port 1                         | 90H     | -            | -          | RST            | -             | INT0/<br>SDA  | T0/SCL        | RXD           | TXD       | <u>[1]</u>                  |          |

|        | Bit                            | address | A7           | <b>A6</b>  | A5             | A4            | A3            | A2            | A1            | <b>A0</b> |                             |          |

| P2*    | Port 2                         | A0H     | -            | -          | SPICLK         | SS            | MISO          | MOSI          | -             | -         | <u>[1]</u>                  |          |

| P0M1   | Port 0 output mode 1           | 84H     | (P0M1.7)     | (P0M1.6)   | (P0M1.5)       | (P0M1.4)      | (P0M1.3)      | (P0M1.2)      | (P0M1.1)      | (P0M1.0)  | FF <u>[1]</u>               | 1111 11  |

| P0M2   | Port 0 output mode 2           | 85H     | (P0M2.7)     | (P0M2.6)   | (P0M2.5)       | (P0M2.4)      | (P0M2.3)      | (P0M2.2)      | (P0M2.1)      | (P0M2.0)  | 00 <mark>[1]</mark>         | 0000 000 |

| P1M1   | Port 1 output mode 1           | 91H     | (P1M1.7)     | (P1M1.6)   | -              | (P1M1.4)      | (P1M1.3)      | (P1M1.2)      | (P1M1.1)      | (P1M1.0)  | D3[1]                       | 11x1 xx1 |

| P1M2   | Port 1 output mode 2           | 92H     | (P1M2.7)     | (P1M2.6)   | -              | (P1M2.4)      | (P1M2.3)      | (P1M2.2)      | (P1M2.1)      | (P1M2.0)  | 00 <mark>[1]</mark>         | 00x0 xx0 |

| P2M1   | Port 2 output mode 1           | A4H     | -            | -          | (P2M1.5)       | (P2M1.4)      | (P2M1.3)      | (P2M1.2)      | -             | -         | FF[1]                       | 11x1 xx1 |

| P2M2   | Port 2 output mode 2           | A5H     | -            | -          | (P2M2.5)       | (P2M2.4)      | (P2M2.3)      | (P2M2.2)      | -             | -         | 00 <mark>[1]</mark>         | 00x0 xx0 |

| PCON   | Power control register         | 87H     | SMOD1        | SMOD0      | BOPD           | BOI           | GF1           | GF0           | PMOD1         | PMOD0     | 00                          | 0000 000 |

| PCONA  | Power control register A       | B5H     | RTCPD        | -          | VCPD           | ADPD          | I2PD          | SPPD          | SPD           | -         | 00 <mark>[1]</mark>         | 0000 000 |

|        | Bit                            | address | D7           | D6         | D5             | D4            | D3            | D2            | D1            | D0        |                             |          |

| PSW*   | Program status word            | D0H     | CY           | AC         | F0             | RS1           | RS0           | OV            | F1            | Р         | 00                          | 0000 000 |

| PT0AD  | Port 0 digital input disable   | F6H     | -            | -          | PT0AD.5        | PT0AD.4       | PT0AD.3       | PT0AD.2       | PT0AD.1       | -         | 00                          | xx00 000 |

| RSTSRC | Reset source register          | DFH     | -            | -          | BOF            | POF           | R_BK          | R_WD          | R_SF          | R_EX      | <u>[3]</u>                  |          |

| RTCCON | RTC control                    | D1H     | RTCF         | RTCS1      | RTCS0          | -             | -             | -             | ERTC          | RTCEN     | 60 <u>[1][</u><br><u>6]</u> | 011x xx0 |

| RTCH   | RTC register high              | D2H     |              |            |                |               |               |               |               |           | 00 <mark>[6]</mark>         | 0000 000 |

| RTCL   | RTC register low               | D3H     |              |            |                |               |               |               |               |           | 00[6]                       | 0000 000 |

| SADDR  | Serial port address register   | A9H     |              |            |                |               |               |               |               |           | 00                          | 0000 000 |

| SADEN  | Serial port address enable     | B9H     |              |            |                |               |               |               |               |           | 00                          | 0000 000 |

| SBUF   | Serial Port data buffer regist | er 99H  |              |            |                |               |               |               |               |           | xx                          | xxxx xxx |

|        | Bit                            | address | 9F           | 9E         | 9D             | 9C            | 9B            | <b>9A</b>     | 99            | 98        |                             |          |

| SCON*  | Serial port control            | 98H     | SM0/FE       | SM1        | SM2            | REN           | TB8           | RB8           | TI            | RI        | 00                          | 0000 000 |

8-bit microcontrollers with accelerated two-clock 80C51 core P89LPC915/916/917

25 of 75

P89LPC9 Product data sheet

Rev. 05 15 December 2009

# Table 9. P89LPC917 special function registers ... continued \* indicates SFRs that are bit addressable. P89LPC9

| Ν                 | lame   | Description                         | SFR         | Bit function      | ons and ac | Idresses       |               |               |               |               |              | Rese                        | t value  |

|-------------------|--------|-------------------------------------|-------------|-------------------|------------|----------------|---------------|---------------|---------------|---------------|--------------|-----------------------------|----------|

| Ta<br>* i<br>N    |        |                                     | addr.       | MSB               |            |                |               |               |               |               | LSB          | Hex                         | Binary   |

|                   |        |                                     | Bit address | 87                | 86         | 85             | 84            | 83            | 82            | 81            | 80           |                             |          |

| Ρ                 | 90*    | Port 0                              | 80H         | T1/KB7/<br>CLKOUT | -          | CMPREF<br>/KB5 | CIN1A<br>/KB4 | CIN1B<br>/KB3 | CIN2A<br>/KB2 | CIN2B<br>/KB1 | CMP2<br>/KB0 | <u>[1]</u>                  |          |

|                   |        |                                     | Bit address | 97                | 96         | 95             | 94            | 93            | 92            | 91            | 90           |                             |          |

| Ρ                 | 91*    | Port 1                              | 90H         | -                 | -          | RST            | INT1          | INT0/<br>SDA  | T0/SCL        | RXD           | TXD          | <u>[1]</u>                  |          |

|                   |        | I                                   | Bit address | B7                | <b>B6</b>  | <b>B5</b>      | <b>B</b> 4    | <b>B</b> 3    | <b>B2</b>     | B1            | <b>B0</b>    |                             |          |

| Ρ                 | 20M1   | Port 0 output mode 1                | 84H         | (P0M1.7)          | -          | (P0M1.5)       | (P0M1.4)      | (P0M1.3)      | (P0M1.2)      | (P0M1.1)      | (P0M1.0)     | FF[1]                       | 1111 11  |

| Ρ                 | 20M2   | Port 0 output mode 2                | 85H         | (P0M2.7)          | -          | (P0M2.5)       | (P0M2.4)      | (P0M2.3)      | (P0M2.2)      | (P0M2.1)      | (P0M2.0)     | 00[1]                       | 0000 00  |

| Ρ                 | P1M1   | Port 1 output mode 1                | 91H         | -                 | -          | -              | (P1M1.4)      | (P1M1.3)      | (P1M1.2)      | (P1M1.1)      | (P1M1.0)     | D3[1]                       | 11x1 xx  |

| Ρ                 | 21M2   | Port 1 output mode 2                | 92H         | -                 | -          | -              | (P1M2.4)      | (P1M2.3)      | (P1M2.2)      | (P1M2.1)      | (P1M2.0)     | 00[1]                       | 00x0 xx( |

| Ρ                 | CON    | Power control register              | 87H         | SMOD1             | SMOD0      | BOPD           | BOI           | GF1           | GF0           | PMOD1         | PMOD0        | 00                          | 0000 00  |

| Ρ                 | CONA   | Power control register A            | B5H         | RTCPD             | -          | VCPD           | ADPD          | I2PD          | -             | SPD           | -            | 00[1]                       | 0000 00  |

|                   |        | I                                   | Bit address | D7                | <b>D6</b>  | D5             | D4            | D3            | D2            | D1            | <b>D0</b>    |                             |          |

| Ρ                 | PSW*   | Program status word                 | D0H         | CY                | AC         | F0             | RS1           | RS0           | OV            | F1            | Р            | 00                          | 0000 00  |

| Ρ                 | T0AD   | Port 0 digital input disable        | e F6H       | -                 | -          | PT0AD.5        | PT0AD.4       | PT0AD.3       | PT0AD.2       | PT0AD.1       | -            | 00                          | xx00 000 |

| R                 | RSTSRC | Reset source register               | DFH         | -                 | -          | BOF            | POF           | R_BK          | R_WD          | R_SF          | R_EX         | <u>[3]</u>                  |          |

| R                 | RTCCON | RTC control                         | D1H         | RTCF              | RTCS1      | RTCS0          | -             | -             | -             | ERTC          | RTCEN        | 60 <u>[1][</u><br><u>6]</u> | 011x xx( |

| R                 | ТСН    | RTC register high                   | D2H         |                   |            |                |               |               |               |               |              | 00 <mark>[6]</mark>         | 0000 00  |

| R                 | RTCL   | RTC register low                    | D3H         |                   |            |                |               |               |               |               |              | 00 <mark>[6]</mark>         | 0000 00  |

| S                 | SADDR  | Serial port address regist          | er A9H      |                   |            |                |               |               |               |               |              | 00                          | 0000 00  |

| S                 | SADEN  | Serial port address enabl           | e B9H       |                   |            |                |               |               |               |               |              | 00                          | 0000 00  |

| S                 | BUF    | Serial Port data buffer reg         | gister 99H  |                   |            |                |               |               |               |               |              | хх                          | XXXX XXX |

|                   |        |                                     | Bit address | 9F                | 9E         | 9D             | 9C            | 9B            | 9A            | 99            | 98           |                             |          |

| S                 | SCON*  | Serial port control                 | 98H         | SM0/FE            | SM1        | SM2            | REN           | TB8           | RB8           | TI            | RI           | 00                          | 0000 00  |

| S<br>S<br>S<br>T/ | STAT   | Serial port extended state register | us BAH      | DBMOD             | INTLO      | CIDIS          | DBISEL        | FE            | BR            | OE            | STINT        | 00                          | 0000 00  |

| S                 | SP .   | Stack pointer                       | 81H         |                   |            |                |               |               |               |               |              | 07                          | 0000 01  |

|                   | AMOD   | Timer 0 and 1 auxiliary m           | ode 8FH     |                   |            |                | T1M2          |               |               |               | T0M2         | 00                          | xxx0 xxx |

NXP Semiconductors

29 of 75

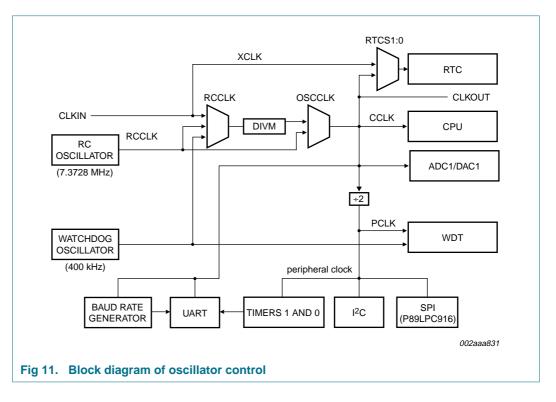

# 8.6 External clock input option

In this configuration, the processor clock is derived from an external source driving the CLKIN pin. The rate may be from 0 Hz up to 18 MHz.

When using an external clock input frequency above 12 MHz, the reset input function of P1.5 must be enabled. An external circuit is required to hold the device in reset at power-up until  $V_{DD}$  has reached its specified level. When system power is removed  $V_{DD}$  will fall below the minimum specified operating voltage. When using an external clock input frequency above 12 MHz, in some applications, an external brownout detect circuit may be required to hold the device in reset when  $V_{DD}$  falls below the minimum specified operating voltage.

# 8.7 CCLK wake-up delay

The P89LPC915/916/917 has an internal wake-up timer that delays the clock until it stabilizes. The delay is 224 OSCCLK cycles plus 60  $\mu$ s to 100  $\mu$ s.

# 8.8 CCLK modification: DIVM register

The OSCCLK frequency can be divided down up to 510 times by configuring a dividing register, DIVM, to generate CCLK. This feature makes it possible to temporarily run the CPU at a lower rate, reducing power consumption. By dividing the clock, the CPU can retain the ability to respond to events that would not exit Idle mode by executing its normal program at a lower rate. This can also allow bypassing the oscillator start-up time in cases where Power-down mode would otherwise be used. The value of DIVM may be changed by the program at any time without interrupting code execution.

#### 8.9 Low power select

The P89LPC915/916/917 is designed to run at 18 MHz (CCLK) maximum. However, if CCLK is 8 MHz or slower, the CLKLP SFR bit (AUXR1.7) can be set to '1' to lower the power consumption further. On any reset, CLKLP is '0' allowing highest performance access. This bit can then be set in software if CCLK is running at 8 MHz or slower.

## 8.10 Memory organization

The various P89LPC915/916/917 memory spaces are as follows:

• DATA

128 bytes of internal data memory space (00H:7FH) accessed via direct or indirect addressing, using instructions other than MOVX and MOVC. All or part of the Stack may be in this area.

• IDATA

Indirect Data. 256 bytes of internal data memory space (00H:FFH) accessed via indirect addressing using instructions other than MOVX and MOVC. All or part of the Stack may be in this area. This area includes the DATA area and the 128 bytes immediately above it.

SFR

Special Function Registers. Selected CPU registers and peripheral control and status registers, accessible only via direct addressing.

• CODE

64 kB of Code memory space, accessed as part of program execution and via the MOVC instruction. The P89LPC915/916/917 devices have 2 kB of on-chip Code memory.

# 8.11 Data RAM arrangement

The 256 bytes of on-chip RAM are organized as shown in Table 10.

| Туре  | Data RAM                                             | Size (bytes) |

|-------|------------------------------------------------------|--------------|

| DATA  | Memory that can be addressed directly and indirectly | 128          |

| IDATA | Memory that can be addressed indirectly              | 256          |

#### 8.12 Interrupts

The P89LPC915/916/917 uses a four priority level interrupt structure. This allows great flexibility in controlling the handling of the many interrupt sources.

The P89LPC915 and P89LPC917 support 13 interrupt sources: external interrupts 0 and 1, timers 0 and 1, serial port TX, serial port RX, combined serial port RX/TX, brownout detect, watchdog/RTC, I<sup>2</sup>C-bus, keyboard, comparators 1 and 2, and ADC completion.

The P89LPC916 supports 14 interrupt sources: external interrupts 0 and 1, timers 0 and 1, serial port TX, serial port RX, combined serial port RX/TX, brownout detect, watchdog/RTC, I<sup>2</sup>C-bus, keyboard, comparators 1 and 2, SPI, and ADC completion.

In the 'Timer' function, the register is incremented every machine cycle.

In the 'Counter' function, the register is incremented in response to a 1-to-0 transition at its corresponding external input pin, T0 or T1. In this function, the external input is sampled once during every machine cycle.

Timer 0 has five operating modes (Modes 0, 1, 2, 3 and 6).

Timer 1 has four operating modes (Modes 0, 1, 2, and 3), except on the P89LPC917 where Timer 1 also has Mode 6. Modes 0, 1, 2 and 6 are the same for both Timers/Counters. Mode 3 is different.

#### 8.17.1 Mode 0

Putting either Timer into Mode 0 makes it look like an 8048 Timer, which is an 8-bit Counter with a divide-by-32 prescaler. In this mode, the Timer register is configured as a 13-bit register. Mode 0 operation is the same for Timer 0 and Timer 1.

#### 8.17.2 Mode 1

Mode 1 is the same as Mode 0, except that all 16 bits of the timer register are used.

## 8.17.3 Mode 2

Mode 2 configures the Timer register as an 8-bit Counter with automatic reload. Mode 2 operation is the same for Timer 0 and Timer 1.

#### 8.17.4 Mode 3

When Timer 1 is in Mode 3 it is stopped. Timer 0 in Mode 3 forms two separate 8-bit counters and is provided for applications that require an extra 8-bit timer. When Timer 1 is in Mode 3 it can still be used by the serial port as a baud rate generator.

#### 8.17.5 Mode 6

In this mode, the corresponding timer can be changed to a PWM with a full period of 256 timer clocks.

#### 8.17.6 Timer overflow toggle output

Timer 0 (and Timer 1 on the P89LPC917) can be configured to automatically toggle a port output whenever a timer overflow occurs. The same device pins that are used for the T0 and T1 count inputs are also used for the timer toggle outputs. The port outputs will be a logic 1 prior to the first timer overflow when this mode is turned on.

#### 8.18 RTC/system timer

The P89LPC915/916/917 have a simple RTC that allows a user to continue running an accurate timer while the rest of the device is powered down. The RTC can be a wake-up or an interrupt source. The RTC is a 23-bit down-counter comprised of a 7-bit prescaler and a 16-bit loadable down-counter. When it reaches all '0's, the counter will be reloaded again and the RTCF flag will be set.

The clock source for this counter can be either the CPU clock (CCLK) or the external clock input, provided that the external clock input is not being used as the CPU clock. If the external clock input is used as the CPU clock, then the RTC will use CCLK as its clock source. Only power-on reset will reset the RTC and its associated SFRs to the default state.

# 8.19 UART

The P89LPC915/916/917 has an enhanced UART that is compatible with the conventional 80C51 UART except that Timer 2 overflow cannot be used as a baud rate source. The P89LPC915/916/917 does include an independent Baud Rate Generator. The baud rate can be selected from the oscillator (divided by a constant), Timer 1 overflow, or the independent Baud Rate Generator. In addition to the baud rate generation, enhancements over the standard 80C51 UART include Framing Error detection, automatic address recognition, selectable double buffering and several interrupt options. The UART can be operated in 4 modes: shift register, 8-bit UART, 9-bit UART, and CPU clock/32 or CPU clock/16.

#### 8.19.1 Mode 0

Serial data enters and exits through RXD. TXD outputs the shift clock. 8 bits are transmitted or received, LSB first. The baud rate is fixed at  $\frac{1}{16}$  of the CPU clock frequency.

#### 8.19.2 Mode 1

10 bits are transmitted (through TXD) or received (through RXD): a start bit (logic 0), 8 data bits (LSB first), and a stop bit (logic 1). When data is received, the stop bit is stored in RB8\_n in Special Function Register SnCON. The baud rate is variable and is determined by the Timer 1 overflow rate or the Baud Rate Generator (described in <u>Section</u> <u>8.19.5 "Baud rate generator and selection"</u>).

#### 8.19.3 Mode 2

11 bits are transmitted (through TXD) or received (through RXD): start bit (logic 0), 8 data bits (LSB first), a programmable 9<sup>th</sup> data bit, and a stop bit (logic 1). When data is transmitted, the 9<sup>th</sup> data bit (TB8 in SCON) can be assigned the value of '0' or '1'. Or, for example, the parity bit (P, in the PSW) could be moved into TB8. When data is received, the 9<sup>th</sup> data bit goes into RB8 in Special Function Register SCON, while the stop bit is not saved. The baud rate is programmable to either  $1/_{16}$  or  $1/_{32}$  of the CPU clock frequency, as determined by the SMOD1 bit in PCON. The SMOD1 bit controls the Timer 1 output rate available to the UART.

#### 8.19.4 Mode 3

11 bits are transmitted (through TXD) or received (through RXD): a start bit (logic 0), 8 data bits (LSB first), a programmable 9<sup>th</sup> data bit, and a stop bit (logic 1). In fact, Mode 3 is the same as Mode 2 in all respects except baud rate. The baud rate in Mode 3 is variable and is determined by the Timer 1 overflow rate or the Baud Rate Generator (described in Section 8.19.5 "Baud rate generator and selection").

#### 8-bit microcontrollers with accelerated two-clock 80C51 core

#### 8-bit microcontrollers with accelerated two-clock 80C51 core

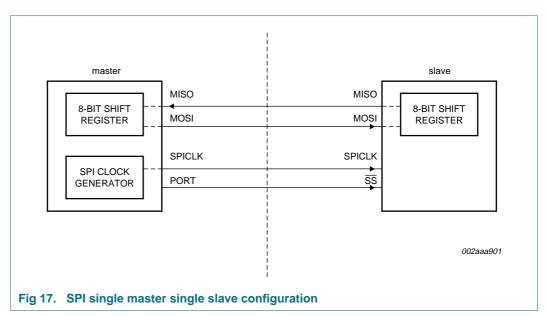

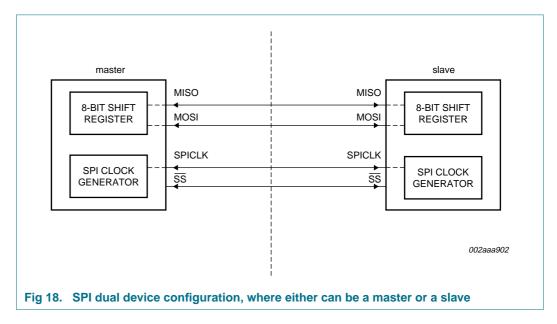

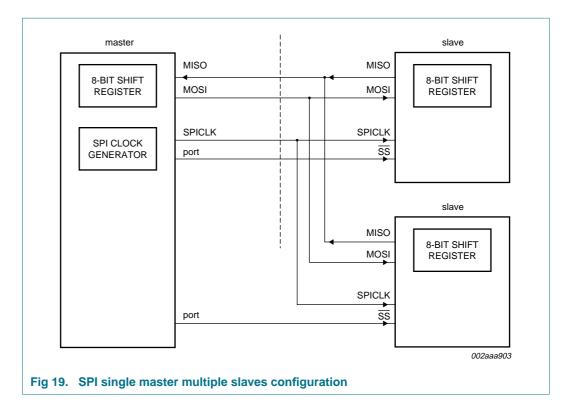

# 8.21.1 Typical SPI configurations

#### 8-bit microcontrollers with accelerated two-clock 80C51 core

#### 8.28 User sector security bytes

There are eight User Sector Security Bytes on the P89LPC915/916/917. Each byte corresponds to one sector. Please see the P89LPC915/916/917 *User's Manual* for additional details.

# 9. A/D converter

#### 9.1 General description

The P89LPC915/916/917 devices have a single 8-bit, 4-channel multiplexed analog-to-digital converter with a DAC module. A block diagram of the A/D converter is shown in <u>Figure 22</u>. The A/D consists of a 4-input multiplexer which feeds a sample-and-hold circuit providing an input signal to one of two comparator inputs. The control logic in combination with the SAR drives a digital-to-analog converter which provides the other input to the comparator. The output of the comparator is fed to the SAR.

#### 9.2 Features

- Single 8-bit, 4-channel multiplexed input, successive approximation A/D converter.

- Four A/D result registers.

- Six operating modes:

- Fixed channel, single conversion mode.

- Fixed channel, continuous conversion mode.

- Auto scan, single conversion mode.

- Auto scan, continuous conversion mode.

- Dual channel, continuous conversion mode.

- Single step mode.

- Three conversion start modes:

- Timer triggered start.

- Start immediately.

- Edge triggered.

- **8**-bit conversion time of  $\geq$ 3.9 µs at an A/D clock of 3.3 MHz.

- Interrupt or polled operation.

- Boundary limits interrupt.

- DAC output to a port pin with high output impedance.

- Clock divider.

- Power-down mode.

#### 9.4.4 Auto scan, continuous conversion mode

Any combination of the four input channels can be selected for conversion. A conversion of each selected input will be performed and the result placed in the result register which corresponds to the selected input channel. An interrupt, if enabled, will be generated after all selected channels have been converted. The process will repeat starting with the first selected channel. Additional conversion results will again cycle through the four result registers, overwriting the previous results.Continous conversions continue until terminated by the user.

#### 9.4.5 Dual channel, continuous conversion mode

This is a variation of the auto scan continuous conversion mode where conversion occurs on two user-selectable inputs. The result of the conversion of the first channel is placed in result register, AD1DAT0. The result of the conversion of the second channel is placed in result register, AD1DAT1. The first channel is again converted and its result stored in AD1DAT2. The second channel is again converted and its result placed in AD1DAT3. An interrupt is generated, if enabled, after every set of four conversions (two conversions per channel).

#### 9.4.6 Single step mode

This special mode allows 'single-stepping' in an auto scan conversion mode. Any combination of the four input channels can be selected for conversion. After each channel is converted, an interrupt is generated, if enabled, and the A/D waits for the next start condition. May be used with any of the start modes.

# 9.5 Conversion start modes

# 9.5.1 Timer triggered start

An A/D conversion is started by the overflow of Timer 0. Once a conversion has started, additional Timer 0 triggers are ignored until the conversion has completed. The Timer triggered start mode is available in all A/D operating modes.

#### 9.5.2 Start immediately

Programming this mode immediately starts a conversion. This start mode is available in all A/D operating modes.

# 9.5.3 Edge triggered

An A/D conversion is started by rising or falling edge of P1.4. Once a conversion has started, additional edge triggers are ignored until the conversion has completed. The edge triggered start mode is available in all A/D operating modes.

# 9.6 Boundary limits interrupt

The A/D converter has both a high and low boundary limit register. After the four MSBs have been converted, these four bits are compared with the four MSBs of the boundary high and low registers. If the four MSBs of the conversion are outside the limit an interrupt will be generated, if enabled. If the conversion result is within the limits, the boundary limits will again be compared after all 8 bits have been converted. An interrupt will be generated, if enabled, if the result is outside the boundary limits. The boundary limit may be disabled by clearing the boundary limit interrupt enable.

# **10. Limiting values**

#### Table 14. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).[1]

| Parameter                             | Conditions                                                                                                                                                                                                                    | Min                                                                                                                                                                                                                                                                                                                             | Max                                                                                                                                                                                                                                                                                                                                      | Unit                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| operating bias ambient temperature    |                                                                                                                                                                                                                               | -55                                                                                                                                                                                                                                                                                                                             | +125                                                                                                                                                                                                                                                                                                                                     | °C                                                                                                                                                                                                                                                                                                                                                          |

| storage temperature range             |                                                                                                                                                                                                                               | -65                                                                                                                                                                                                                                                                                                                             | +150                                                                                                                                                                                                                                                                                                                                     | °C                                                                                                                                                                                                                                                                                                                                                          |

| HIGH-level output current per I/O pin |                                                                                                                                                                                                                               | -                                                                                                                                                                                                                                                                                                                               | 8                                                                                                                                                                                                                                                                                                                                        | mA                                                                                                                                                                                                                                                                                                                                                          |

| LOW-level output current per I/O pin  |                                                                                                                                                                                                                               | -                                                                                                                                                                                                                                                                                                                               | 20                                                                                                                                                                                                                                                                                                                                       | mA                                                                                                                                                                                                                                                                                                                                                          |

| maximum total I/O current             |                                                                                                                                                                                                                               | -                                                                                                                                                                                                                                                                                                                               | 120                                                                                                                                                                                                                                                                                                                                      | mA                                                                                                                                                                                                                                                                                                                                                          |

| voltage on any pin (except $V_{SS}$ ) | with respect to V <sub>DD</sub>                                                                                                                                                                                               | -                                                                                                                                                                                                                                                                                                                               | 3.5                                                                                                                                                                                                                                                                                                                                      | V                                                                                                                                                                                                                                                                                                                                                           |

| total power dissipation per package   | based on package heat<br>transfer, not device power<br>consumption                                                                                                                                                            | -                                                                                                                                                                                                                                                                                                                               | 1.5                                                                                                                                                                                                                                                                                                                                      | W                                                                                                                                                                                                                                                                                                                                                           |

|                                       | operating bias ambient temperature<br>storage temperature range<br>HIGH-level output current per I/O pin<br>LOW-level output current per I/O pin<br>maximum total I/O current<br>voltage on any pin (except V <sub>SS</sub> ) | operating bias ambient temperaturestorage temperature rangeHIGH-level output current per I/O pinLOW-level output current per I/O pinmaximum total I/O currentvoltage on any pin (except V <sub>SS</sub> )with respect to V <sub>DD</sub> total power dissipation per packagebased on package heat<br>transfer, not device power | operating bias ambient temperature-55storage temperature range-65HIGH-level output current per I/O pin-LOW-level output current per I/O pin-maximum total I/O current-voltage on any pin (except V <sub>SS</sub> )with respect to V <sub>DD</sub> total power dissipation per packagebased on package heat<br>transfer, not device power | operating bias ambient temperature-55+125storage temperature range-65+150HIGH-level output current per I/O pin-8LOW-level output current per I/O pin-20maximum total I/O current-120voltage on any pin (except V <sub>SS</sub> )with respect to V <sub>DD</sub> -total power dissipation per packagebased on package heat<br>transfer, not device power-1.5 |

[1] The following applies to <u>Table 14</u>:

a) This product includes circuitry specifically designed for the protection of its internal devices from the damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying greater than the rated maximum.

b) Parameters are valid over ambient temperature range unless otherwise specified. All voltages are with respect to V<sub>SS</sub> unless otherwise noted.

#### 8-bit microcontrollers with accelerated two-clock 80C51 core

#### Table 17. Dynamic characteristics (18 MHz)

$V_{DD}$  = 3.0 V to 3.6 V unless otherwise specified.

$T_{amb} = -40 \degree C$  to +85 °C, or -40 °C to +125 °C (see <u>Table 3 on page 3</u>), unless otherwise specified.[1][2]

| Symbol               | Parameter                                     | Conditions                       | Varia                  | able clock               | f <sub>osc</sub> = 1 | Unit  |     |

|----------------------|-----------------------------------------------|----------------------------------|------------------------|--------------------------|----------------------|-------|-----|

|                      |                                               |                                  | Min                    | Max                      | Min                  | Max   | 1   |

| osc(RC)              | internal RC oscillator frequency              | industrial                       | 7.189                  | 7.557                    | 7.189                | 7.557 | MHz |

| ( -/                 |                                               | extended                         | 7.004                  | 7.741                    | 7.004                | 7.741 | MHz |

| <sup>f</sup> osc(WD) | internal watchdog oscillator<br>frequency     |                                  | 320                    | 520                      | 320                  | 520   | kHz |

| fclklp               | low power select clock<br>frequency           |                                  | 0                      | 8                        | -                    | -     | MHz |

| Glitch filte         | r                                             |                                  |                        |                          |                      |       |     |

| t <sub>gr</sub>      | glitch rejection time                         | P1.5/RST pin                     | -                      | 50                       | -                    | 50    | ns  |

|                      |                                               | any pin except<br>P1.5/RST       | -                      | 15                       | -                    | 15    | ns  |

| t <sub>sa</sub>      | signal acceptance time                        | P1.5/RST pin                     | 125                    | -                        | 125                  | -     | ns  |

|                      |                                               | any pin except<br>P1.5/RST       | 50                     | -                        | 50                   | -     | ns  |

| External c           | lock                                          |                                  |                        |                          |                      |       |     |

| f <sub>osc</sub>     | oscillator frequency                          |                                  | 0                      | 18                       | -                    | -     | MHz |

| T <sub>cy(clk)</sub> | clock cycle time                              | see Figure 28                    | 55                     | -                        | -                    | -     | ns  |

| снсх                 | clock HIGH time                               | see Figure 28                    | 22                     | $T_{cy(CLK)} - t_{CLCX}$ | 22                   | -     | ns  |

| CLCX                 | clock LOW time                                | see Figure 28                    | 22                     | $T_{cy(CLK)} - t_{CHCX}$ | 22                   | -     | ns  |

| <sup>t</sup> сlсн    | clock rise time                               | see Figure 28                    | -                      | 5                        | -                    | 5     | ns  |

| <sup>t</sup> CHCL    | clock fall time                               | see Figure 28                    | -                      | 5                        | -                    | 5     | ns  |

| Shift regis          | ter (UART mode 0)                             |                                  |                        |                          |                      |       |     |

| T <sub>XLXL</sub>    | serial port clock cycle time                  | see Figure 27                    | 16T <sub>cy(CLK)</sub> | -                        | 888                  | -     | ns  |

| QVXH                 | output data set-up to clock rising edge time  | see Figure 27                    | 13T <sub>cy(CLK)</sub> | -                        | 722                  | -     | ns  |

| <sup>t</sup> xhqx    | output data hold after clock rising edge time | see Figure 27                    | -                      | $T_{cy(CLK)}$ + 20       | -                    | 75    | ns  |

| t <sub>XHDX</sub>    | input data hold after clock rising edge time  | see Figure 27                    | -                      | 0                        | -                    | 0     | ns  |

| t <sub>XHDV</sub>    | input data valid to clock rising edge time    | see Figure 27                    | 150                    | -                        | 150                  | -     | ns  |

| SPI interfa          | ice                                           |                                  |                        |                          |                      |       |     |

| f <sub>SPI</sub>     | SPI operating frequency                       |                                  |                        |                          |                      |       |     |

|                      | slave                                         |                                  | 0                      | CCLK <sub>/6</sub>       | 0                    | 3.0   | MH: |

|                      | master                                        |                                  | -                      | CCLK/4                   | -                    | 4.5   | MH: |

| T <sub>SPICYC</sub>  | SPI cycle time                                | see Figure 23, 24,               |                        |                          |                      |       |     |

|                      | slave                                         | <u>25, 26</u>                    | <sup>6</sup> /CCLK     | -                        | 333                  | -     | ns  |

|                      | master                                        |                                  | 4/CCLK                 | -                        | 222                  | -     | ns  |

| SPILEAD              | SPI enable lead time                          | see Figure 25, 26                |                        |                          |                      |       |     |

|                      | slave                                         |                                  | 250                    | -                        | 250                  | -     | ns  |

| t <sub>SPILAG</sub>  | SPI enable lag time                           | see <u>Figure 25</u> , <u>26</u> | 250                    | -                        | 250                  | -     | ns  |

|                      |                                               |                                  |                        |                          |                      |       |     |

#### 8-bit microcontrollers with accelerated two-clock 80C51 core

#### Table 17. Dynamic characteristics (18 MHz) ...continued

$V_{DD}$  = 3.0 V to 3.6 V unless otherwise specified.

$T_{amb} = -40 \degree C$  to +85 °C, or -40 °C to +125 °C (see <u>Table 3 on page 3</u>), unless otherwise specified.<sup>[1][2]</sup>

| Symbol               | Parameter                                         | Conditions                                 | Varial             | ole clock | f <sub>osc</sub> = 1 | Unit                                             |    |

|----------------------|---------------------------------------------------|--------------------------------------------|--------------------|-----------|----------------------|--------------------------------------------------|----|

|                      |                                                   |                                            | Min                | Max       | Min                  | Max                                              |    |

| t <sub>SPICLKH</sub> | SPICLK HIGH time                                  | see <u>Figure 23</u> , <u>24</u> ,         |                    |           |                      |                                                  |    |

|                      | master                                            | <u>25, 26</u>                              | <sup>2</sup> /CCLK | -         | 111                  | -                                                | ns |

|                      | slave                                             |                                            | <sup>3</sup> ⁄CCLK | -         | 167                  | -                                                | ns |

| t <sub>SPICLKL</sub> | SPICLK LOW time                                   | see Figure 23, 24,                         |                    |           |                      |                                                  |    |

|                      | master                                            | <u>25, 26</u>                              | <sup>2</sup> /CCLK | -         | 111                  | -<br>-<br>-<br>-<br>80<br>160<br>111<br>-<br>111 | ns |

|                      | slave                                             |                                            | <sup>3</sup> ⁄CCLK | -         | 167                  | -                                                | ns |

| t <sub>SPIDSU</sub>  | SPI data set-up time                              | see Figure 23, 24,                         |                    |           |                      |                                                  |    |

|                      | master or slave                                   | <u>25, 26</u>                              | 100                | -         | 100                  | Max 80 160 111 100 2000 100                      | ns |

| t <sub>SPIDH</sub>   | SPI data hold time                                | see <u>Figure 23, 24,</u>                  |                    |           |                      |                                                  |    |

|                      | master or slave                                   | <u>25, 26</u>                              | 100                | -         | 100                  | -                                                | ns |

| t <sub>SPIA</sub>    | SPI access time                                   | see Figure 25, 26                          |                    |           |                      |                                                  |    |

|                      | slave                                             |                                            | 0                  | 80        | 0                    | 80                                               | ns |

| t <sub>SPIDIS</sub>  | SPI disable time                                  | see Figure 25, 26                          |                    |           |                      |                                                  |    |

|                      | slave                                             |                                            | 0                  | 160       | -                    | 160                                              | ns |

| t <sub>SPIDV</sub>   | SPI enable to output data valid time              | see <u>Figure 23, 24,</u><br><u>25, 26</u> |                    |           |                      | 160                                              |    |

|                      | slave                                             |                                            | -                  | 160       | -                    | 160                                              | ns |

|                      | master                                            |                                            | -                  | 111       | -                    | 111                                              | ns |

| t <sub>SPIOH</sub>   | SPI output data hold time                         | see <u>Figure 23, 24,</u><br><u>25, 26</u> | 0                  | -         | 0                    | -                                                | ns |

| t <sub>SPIR</sub>    | SPI rise time                                     | see Figure 23, 24,                         |                    |           |                      | -<br>80<br>160<br>111<br>-<br>100<br>2000        |    |

|                      | SPI outputs<br>(SPICLK, MOSI, MISO)               | <u>25, 26</u>                              | -                  | 100       | -                    | 100                                              | ns |

|                      | SPI inputs (SPICLK, MOSI, MISO, $\overline{SS}$ ) |                                            | -                  | 2000      | -                    | 2000                                             | ns |

| t <sub>SPIF</sub>    | SPI fall time                                     | see Figure 23, 24,                         |                    |           |                      |                                                  |    |

|                      | SPI outputs<br>(SPICLK, MOSI, MISO)               | <u>25, 26</u>                              | -                  | 100       | -                    | 100                                              | ns |

|                      | SPI inputs<br>(SPICLK, MOSI, MISO, SS)            |                                            | -                  | 2000      | -                    | 2000                                             | ns |

[1] Parameters are valid over ambient temperature range unless otherwise specified.

[2] Parts are tested to 2 MHz, but are guaranteed to operate down to 0 Hz.