Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                           |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 50MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, Microwire, SmartCard, SPI, SSP, UART/USART, USB         |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Number of I/O              | 40                                                                        |

| Program Memory Size        | 16KB (16K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 6K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

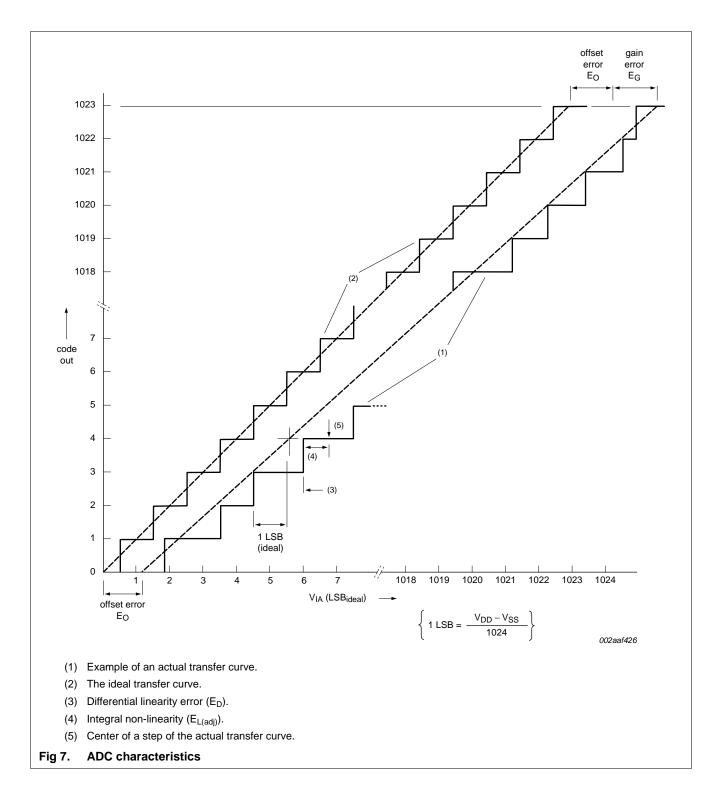

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 48-LQFP                                                                   |

| Supplier Device Package    | 48-LQFP (7x7)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc11u12fbd48-201 |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 32-bit ARM Cortex-M0 microcontroller

| Symbol                             | Pin HVQFN33 | Pin LQFP48 | Ball TFBGA48 |     | Reset<br>state<br>[1] | Туре | Description                                                                                                                                                                                                                                                         |

|------------------------------------|-------------|------------|--------------|-----|-----------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TMS/PIO0_12/AD1/                   | 22          | 33         | C7           | [7] | I; PU                 | I    | <b>TMS</b> — Test Mode Select for JTAG interface.                                                                                                                                                                                                                   |

| CT32B1_CAP0                        |             |            |              |     | -                     | I/O  | PIO_12 — General purpose digital input/output pin.                                                                                                                                                                                                                  |

|                                    |             |            |              |     | -                     | I    | AD1 — A/D converter, input 1.                                                                                                                                                                                                                                       |

|                                    |             |            |              |     | -                     | I    | CT32B1_CAP0 — Capture input 0 for 32-bit timer 1.                                                                                                                                                                                                                   |

| TDO/PIO0_13/AD2/                   | 23          | 34         | C8           | [7] | I; PU                 | 0    | <b>TDO</b> — Test Data Out for JTAG interface.                                                                                                                                                                                                                      |

| CT32B1_MAT0                        |             |            |              |     | -                     | I/O  | <b>PIO0_13</b> — General purpose digital input/output pin.                                                                                                                                                                                                          |

|                                    |             |            |              |     | -                     | I    | AD2 — A/D converter, input 2.                                                                                                                                                                                                                                       |

|                                    |             |            |              |     | -                     | 0    | CT32B1_MAT0 — Match output 0 for 32-bit timer 1.                                                                                                                                                                                                                    |

| TRST/PIO0_14/AD3/                  | 24          | 35         | B7           | [7] | I; PU                 | I    | <b>TRST</b> — Test Reset for JTAG interface.                                                                                                                                                                                                                        |

| CT32B1_MAT1                        |             |            |              |     | -                     | I/O  | <b>PIO0_14</b> — General purpose digital input/output pin.                                                                                                                                                                                                          |

|                                    |             |            |              |     | -                     | I    | AD3 — A/D converter, input 3.                                                                                                                                                                                                                                       |

|                                    |             |            |              |     | -                     | 0    | CT32B1_MAT1 — Match output 1 for 32-bit timer 1.                                                                                                                                                                                                                    |

| SWDIO/PIO0_15/AD4/                 | 25          | 39         | B6           | [7] | I; PU                 | I/O  | SWDIO — Serial wire debug input/output.                                                                                                                                                                                                                             |

| CT32B1_MAT2                        |             |            |              |     | -                     | I/O  | <b>PIO0_15</b> — General purpose digital input/output pin.                                                                                                                                                                                                          |

|                                    |             |            |              |     | -                     | I    | AD4 — A/D converter, input 4.                                                                                                                                                                                                                                       |

|                                    |             |            |              |     | -                     | 0    | <b>CT32B1_MAT2</b> — Match output 2 for 32-bit timer 1.                                                                                                                                                                                                             |

| PIO0_16/AD5/<br>CT32B1_MAT3/WAKEUP | 26          | 40         | A6           | [7] | I; PU                 | I/O  | <b>PIO0_16</b> — General purpose digital input/output pin.                                                                                                                                                                                                          |

|                                    |             |            |              |     | -                     | I    | AD5 — A/D converter, input 5.                                                                                                                                                                                                                                       |

|                                    |             |            |              |     | -                     | 0    | CT32B1_MAT3 — Match output 3 for 32-bit timer 1.                                                                                                                                                                                                                    |

|                                    |             |            |              |     | -                     | 1    | <b>WAKEUP</b> — Deep power-down mode wake-up<br>pin with 20 ns glitch filter. This pin must be<br>pulled HIGH externally to enter Deep<br>power-down mode and pulled LOW to exit Deep<br>power-down mode. A LOW-going pulse as short<br>as 50 ns wakes up the part. |

| PIO0_17/RTS/<br>CT32B0_CAP0/SCLK   | 30          | 45         | A3           | [3] | I; PU                 | I/O  | <b>PIO0_17</b> — General purpose digital input/output pin.                                                                                                                                                                                                          |

|                                    |             |            |              |     | -                     | 0    | RTS — Request To Send output for USART.                                                                                                                                                                                                                             |

|                                    |             |            |              |     | -                     | I    | <b>CT32B0_CAP0</b> — Capture input 0 for 32-bit timer 0.                                                                                                                                                                                                            |

|                                    |             |            |              |     | -                     | I/O  | <b>SCLK</b> — Serial clock input/output for USART in synchronous mode.                                                                                                                                                                                              |

## Table 3. Pin description ...continued

### 32-bit ARM Cortex-M0 microcontroller

| Symbol                            | Pin HVQFN33 | Pin LQFP48 | Ball TFBGA48 |            | Reset<br>state<br>[1] | Туре | Description                                                       |

|-----------------------------------|-------------|------------|--------------|------------|-----------------------|------|-------------------------------------------------------------------|

| PIO0_18/RXD/<br>CT32B0_MAT0       | 31          | 46         | В3           | <u>[3]</u> | I; PU                 | I/O  | <b>PIO0_18</b> — General purpose digital input/output pin.        |

|                                   |             |            |              |            | -                     | I    | <b>RXD</b> — Receiver input for USART.Used in UART ISP mode.      |

|                                   |             |            |              |            | -                     | 0    | CT32B0_MAT0 — Match output 0 for 32-bit timer 0.                  |

| PIO0_19/TXD/<br>CT32B0_MAT1       | 32          | 47         | B2           | [3]        | I; PU                 | I/O  | <b>PIO0_19</b> — General purpose digital input/output pin.        |

|                                   |             |            |              |            | -                     | 0    | <b>TXD</b> — Transmitter output for USART. Used in UART ISP mode. |

|                                   |             |            |              |            | -                     | 0    | <b>CT32B0_MAT1</b> — Match output 1 for 32-bit timer 0.           |

| PIO0_20/CT16B1_CAP0               | 7           | 9          | F2           | <u>[3]</u> | I; PU                 | I/O  | <b>PIO0_20</b> — General purpose digital input/output pin.        |

|                                   |             |            |              |            | -                     | I    | CT16B1_CAP0 — Capture input 0 for 16-bit timer 1.                 |

| PIO0_21/CT16B1_MAT0/<br>MOSI1     | 12          | 17         | G4           | [3]        | I; PU                 | I/O  | <b>PIO0_21</b> — General purpose digital input/output pin.        |

|                                   |             |            |              |            | -                     | 0    | CT16B1_MAT0 — Match output 0 for 16-bit timer 1.                  |

|                                   |             |            |              |            | -                     | I/O  | MOSI1 — Master Out Slave In for SSP1.                             |

| PIO0_22/AD6/<br>CT16B1_MAT1/MISO1 | 20          | 30         | E8           | [7]        | I; PU                 | I/O  | <b>PIO0_22</b> — General purpose digital input/output pin.        |

|                                   |             |            |              |            | -                     | I    | AD6 — A/D converter, input 6.                                     |

|                                   |             |            |              |            | -                     | 0    | <b>CT16B1_MAT1</b> — Match output 1 for 16-bit timer 1.           |

|                                   |             |            |              |            | -                     | I/O  | MISO1 — Master In Slave Out for SSP1.                             |

| PIO0_23/AD7                       | 27          | 42         | A5           | [7]        | I; PU                 | I/O  | <b>PIO0_23</b> — General purpose digital input/output pin.        |

|                                   |             |            |              |            | -                     | I    | AD7 — A/D converter, input 7.                                     |

| PIO1_5/CT32B1_CAP1                | -           | -          | H8           | [3]        | I; PU                 | I/O  | <b>PIO1_5</b> — General purpose digital input/output pin.         |

|                                   |             |            |              |            | -                     | I    | <b>CT32B1_CAP1</b> — Capture input 1 for 32-bit timer 1.          |

| PIO1_13/DTR/<br>CT16B0_MAT0/TXD   | -           | 36         | B8           | <u>[3]</u> | I; PU                 | I/O  | <b>PIO1_13</b> — General purpose digital input/output pin.        |

|                                   |             |            |              |            | -                     | 0    | <b>DTR</b> — Data Terminal Ready output for USART.                |

|                                   |             |            |              |            | -                     | 0    | CT16B0_MAT0 — Match output 0 for 16-bit timer 0.                  |

|                                   |             |            |              |            | -                     | 0    | <b>TXD</b> — Transmitter output for USART.                        |

## Table 3. Pin description ...continued

## 7. Functional description

### 7.1 On-chip flash programming memory

The LPC11U1x contain up to 32 kB on-chip flash program memory. The flash can be programmed using In-System Programming (ISP) or In-Application Programming (IAP) via the on-chip boot loader software.

### 7.2 SRAM

The LPC11U1x contain a total of 6 kB on-chip static RAM memory.

## 7.3 On-chip ROM

The on-chip ROM contains the boot loader and the following Application Programming Interfaces (APIs):

- In-System Programming (ISP) and In-Application Programming (IAP) support for flash programming

- Power profiles for configuring power consumption and PLL settings

- 32-bit integer division routines

## 7.4 Memory map

The LPC11U1x incorporates several distinct memory regions, shown in the following figures. <u>Figure 5</u> shows the overall map of the entire address space from the user program viewpoint following reset. The interrupt vector area supports address remapping.

The AHB peripheral area is 2 MB in size and is divided to allow for up to 128 peripherals. The APB peripheral area is 512 kB in size and is divided to allow for up to 32 peripherals. Each peripheral of either type is allocated 16 kB of space. This allows simplifying the address decoding for each peripheral.

#### 7.7.1 Features

- GPIO pins can be configured as input or output by software.

- All GPIO pins default to inputs with interrupt disabled at reset.

- Pin registers allow pins to be sensed and set individually.

- Up to eight GPIO pins can be selected from all GPIO pins to create an edge- or level-sensitive GPIO interrupt request.

- Port interrupts can be triggered by any pin or pins in each port.

### 7.8 USB interface

The Universal Serial Bus (USB) is a 4-wire bus that supports communication between a host and one or more (up to 127) peripherals. The host controller allocates the USB bandwidth to attached devices through a token-based protocol. The bus supports hot-plugging and dynamic configuration of the devices. All transactions are initiated by the host controller.

The LPC11U1x USB interface consists of a full-speed device controller with on-chip PHY for device functions.

**Remark:** Configure the LPC11U1x in default power mode with the power profiles before using the USB (see <u>Section 7.16.5.1</u>). Do not use the USB with the part in performance, efficiency, or low-power mode.

#### 7.8.1 Full-speed USB device controller

The device controller enables 12 Mbit/s data exchange with a USB Host controller. It consists of a register interface, serial interface engine, and endpoint buffer memory. The serial interface engine decodes the USB data stream and writes data to the appropriate endpoint buffer. The status of a completed USB transfer or error condition is indicated via status registers. An interrupt is also generated if enabled.

#### 7.8.1.1 Features

- Dedicated USB PLL available.

- Fully compliant with USB 2.0 specification (full speed).

- Supports 10 physical (5 logical) endpoints including one control endpoint.

- Single and double buffering supported.

- Each non-control endpoint supports bulk, interrupt, or isochronous endpoint types.

- Supports wake-up from Deep-sleep mode and Power-down mode on USB activity and remote wake-up.

- Supports SoftConnect.

## 7.9 USART

The LPC11U1x contains one USART.

The USART includes full modem control, support for synchronous mode, and a smart card interface. The RS-485/9-bit mode allows both software address detection and automatic address detection using 9-bit mode.

#### 32-bit ARM Cortex-M0 microcontroller

- Four match registers per timer that allow:

- Continuous operation with optional interrupt generation on match.

- Stop timer on match with optional interrupt generation.

- Reset timer on match with optional interrupt generation.

- Up to four external outputs corresponding to match registers, with the following capabilities:

- Set LOW on match.

- Set HIGH on match.

- Toggle on match.

- Do nothing on match.

- The timer and prescaler may be configured to be cleared on a designated capture event. This feature permits easy pulse-width measurement by clearing the timer on the leading edge of an input pulse and capturing the timer value on the trailing edge.

### 7.14 System tick timer

The ARM Cortex-M0 includes a system tick timer (SYSTICK) that is intended to generate a dedicated SYSTICK exception at a fixed time interval (typically 10 ms).

## 7.15 Windowed WatchDog Timer (WWDT)

The purpose of the watchdog is to reset the controller if software fails to periodically service it within a programmable time window.

#### 7.15.1 Features

- Internally resets chip if not periodically reloaded during the programmable time-out period.

- Optional windowed operation requires reload to occur between a minimum and maximum time period, both programmable.

- Optional warning interrupt can be generated at a programmable time prior to watchdog time-out.

- Enabled by software but requires a hardware reset or a watchdog reset/interrupt to be disabled.

- Incorrect feed sequence causes reset or interrupt if enabled.

- Flag to indicate watchdog reset.

- Programmable 24-bit timer with internal prescaler.

- Selectable time period from  $(T_{cy(WDCLK)} \times 256 \times 4)$  to  $(T_{cy(WDCLK)} \times 2^{24} \times 4)$  in multiples of  $T_{cy(WDCLK)} \times 4$ .

- The Watchdog Clock (WDCLK) source can be selected from the IRC or the dedicated watchdog oscillator (WDO). This gives a wide range of potential timing choices of watchdog operation under different power conditions.

## 7.16 Clocking and power control

#### 7.16.1 Integrated oscillators

The LPC11U1x include three independent oscillators. These are the system oscillator, the Internal RC oscillator (IRC), and the watchdog oscillator. Each oscillator can be used for more than one purpose as required in a particular application.

Following reset, the LPC11U1x will operate from the internal RC oscillator until switched by software. This allows systems to operate without any external crystal and the bootloader code to operate at a known frequency.

See Figure 6 for an overview of the LPC11U1x clock generation.

#### 32-bit ARM Cortex-M0 microcontroller

## 7.17 Emulation and debugging

Debug functions are integrated into the ARM Cortex-M0. Serial wire debug functions are supported in addition to a standard JTAG boundary scan. The ARM Cortex-M0 is configured to support up to four breakpoints and two watch points.

The  $\overline{\text{RESET}}$  pin selects between the JTAG boundary scan ( $\overline{\text{RESET}}$  = LOW) and the ARM SWD debug ( $\overline{\text{RESET}}$  = HIGH). The ARM SWD debug port is disabled while the LPC11U1x is in reset.

To perform boundary scan testing, follow these steps:

- 1. Erase any user code residing in flash.

- 2. Power up the part with the RESET pin pulled HIGH externally.

- 3. Wait for at least 250  $\mu$ s.

- 4. Pull the RESET pin LOW externally.

- 5. Perform boundary scan operations.

- 6. Once the boundary scan operations are completed, assert the TRST pin to enable the SWD debug mode and release the RESET pin (pull HIGH).

**Remark:** The JTAG interface cannot be used for debug purposes.

LPC11U1X

29 of 72

#### 32-bit ARM Cortex-M0 microcontroller

| Symbol                | Parameter                                                                   | Conditions                                                                                                                                                                                       |         | Min         | Typ[1]       | Max         | Unit |

|-----------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------|--------------|-------------|------|

| I <sup>2</sup> C-bus  | pins (PIO0_4 and PIO0_5                                                     | j)                                                                                                                                                                                               |         | I           |              | <b>L</b>    |      |

| V <sub>IH</sub>       | HIGH-level input voltage                                                    |                                                                                                                                                                                                  |         | $0.7V_{DD}$ | -            | -           | V    |

| V <sub>IL</sub>       | LOW-level input voltage                                                     |                                                                                                                                                                                                  |         | -           | -            | $0.3V_{DD}$ | V    |

| V <sub>hys</sub>      | hysteresis voltage                                                          |                                                                                                                                                                                                  |         | -           | $0.05V_{DD}$ | -           | V    |

| I <sub>OL</sub>       | LOW-level output<br>current                                                 | $\label{eq:Volume} \begin{array}{l} V_{OL} = 0.4 \mbox{ V}; \mbox{ I}^2C\mbox{-bus pins configured} \\ \mbox{as standard mode pins} \\ 2.0 \mbox{ V} \leq V_{DD} \leq 3.6 \mbox{ V} \end{array}$ |         | 3.5         | -            | -           | mA   |

|                       |                                                                             | $1.8~V \leq V_{DD} < 2.0~V$                                                                                                                                                                      |         | 3           | -            | -           |      |

| I <sub>OL</sub>       | LOW-level output<br>current                                                 | $V_{OL}$ = 0.4 V; I <sup>2</sup> C-bus pins configured<br>as Fast-mode Plus pins<br>2.0 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V                                                                    |         | 20          | -            | -           | mA   |

|                       |                                                                             | $1.8 \text{ V} \le \text{V}_{\text{DD}} < 2.0 \text{ V}$                                                                                                                                         |         | 16          | -            | -           |      |

| ILI                   | input leakage current                                                       | $V_{I} = V_{DD}$                                                                                                                                                                                 | [15]    | -           | 2            | 4           | μA   |

|                       |                                                                             | V <sub>1</sub> = 5 V                                                                                                                                                                             |         | -           | 10           | 22          | μA   |

| Oscillate             | or pins                                                                     | I                                                                                                                                                                                                |         |             |              |             |      |

| V <sub>i(xtal)</sub>  | crystal input voltage                                                       |                                                                                                                                                                                                  |         | -0.5        | 1.8          | 1.95        | V    |

| V <sub>o(xtal)</sub>  | crystal output voltage                                                      |                                                                                                                                                                                                  |         | -0.5        | 1.8          | 1.95        | V    |

| USB pin               | S                                                                           |                                                                                                                                                                                                  |         | 1           | l            |             |      |

| I <sub>OZ</sub>       | OFF-state output current                                                    | 0 V < V <sub>I</sub> < 3.3 V                                                                                                                                                                     | [2]     | -           | -            | ±10         | μA   |

| V <sub>BUS</sub>      | bus supply voltage                                                          |                                                                                                                                                                                                  | [2]     | -           | -            | 5.25        | V    |

| V <sub>DI</sub>       | differential input sensitivity voltage                                      | (D+) – (D–)                                                                                                                                                                                      | [2]     | 0.2         | -            | -           | V    |

| V <sub>CM</sub>       | differential common mode voltage range                                      | includes V <sub>DI</sub> range                                                                                                                                                                   | [2]     | 0.8         | -            | 2.5         | V    |

| V <sub>th(rs)se</sub> | single-ended receiver<br>switching threshold<br>voltage                     |                                                                                                                                                                                                  | [2]     | 0.8         | -            | 2.0         | V    |

| V <sub>OL</sub>       | LOW-level output voltage                                                    | for low-/full-speed; $R_L$ of 1.5 k\Omega to 3.6 V                                                                                                                                               | [2]     | -           | -            | 0.18        | V    |

| V <sub>OH</sub>       | HIGH-level output voltage                                                   | driven; for low-/full-speed; $R_L$ of 15 k $\Omega$ to GND                                                                                                                                       | [2]     | 2.8         | -            | 3.5         | V    |

| C <sub>trans</sub>    | transceiver capacitance                                                     | pin to GND                                                                                                                                                                                       | [2]     | -           | -            | 20          | pF   |

| Z <sub>DRV</sub>      | driver output<br>impedance for driver<br>which is not high-speed<br>capable | with 33 $\Omega$ series resistor; steady state drive                                                                                                                                             | [16][2] | 36          | -            | 44.1        | Ω    |

## Table 6. Static characteristics ... continued

$T_{amb} = -40 \text{ °C to } +85 \text{ °C}$ , unless otherwise specified.

### **NXP Semiconductors**

# LPC11U1x

#### 32-bit ARM Cortex-M0 microcontroller

#### 32-bit ARM Cortex-M0 microcontroller

#### 32-bit ARM Cortex-M0 microcontroller

## 9.3 Peripheral power consumption

The supply current per peripheral is measured as the difference in supply current between the peripheral block enabled and the peripheral block disabled in the SYSAHBCLKCFG and PDRUNCFG (for analog blocks) registers. All other blocks are disabled in both registers and no code is executed. Measured on a typical sample at  $T_{amb} = 25$  °C. Unless noted otherwise, the system oscillator and PLL are running in both measurements.

The supply currents are shown for system clock frequencies of 12 MHz and 48 MHz.

## **10.** Dynamic characteristics

### 10.1 Flash memory

#### Table 10. Flash characteristics

$T_{amb} = -40$  °C to +85 °C, unless otherwise specified.

| Symbol            | Parameter        | Conditions                                |    | Min   | Тур    | Max  | Unit   |

|-------------------|------------------|-------------------------------------------|----|-------|--------|------|--------|

| N <sub>endu</sub> | endurance        | [1                                        | ]  | 10000 | 100000 | -    | cycles |

| t <sub>ret</sub>  | retention time   | powered                                   |    | 10    | -      | -    | years  |

|                   |                  | unpowered                                 |    | 20    | -      | -    | years  |

| t <sub>er</sub>   | erase time       | sector or multiple<br>consecutive sectors |    | 95    | 100    | 105  | ms     |

| t <sub>prog</sub> | programming time | [2                                        | 2] | 0.95  | 1      | 1.05 | ms     |

[1] Number of program/erase cycles.

[2] Programming times are given for writing 256 bytes from RAM to the flash. Data must be written to the flash in blocks of 256 bytes.

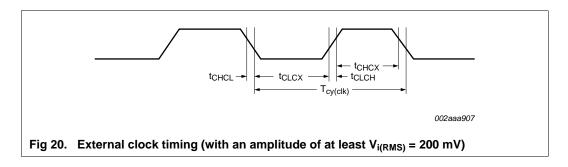

## 10.2 External clock

#### Table 11. Dynamic characteristic: external clock

$T_{amb} = -40 \degree C$  to +85  $\degree C$ ;  $V_{DD}$  over specified ranges.[1]

| Symbol               | Parameter            | Conditions | Min                     | Typ <u>[2]</u> | Max  | Unit |

|----------------------|----------------------|------------|-------------------------|----------------|------|------|

| f <sub>osc</sub>     | oscillator frequency |            | 1                       | -              | 25   | MHz  |

| T <sub>cy(clk)</sub> | clock cycle time     |            | 40                      | -              | 1000 | ns   |

| t <sub>CHCX</sub>    | clock HIGH time      |            | $T_{cy(clk)} 	imes 0.4$ | -              | -    | ns   |

| t <sub>CLCX</sub>    | clock LOW time       |            | $T_{cy(clk)} 	imes 0.4$ | -              | -    | ns   |

| t <sub>CLCH</sub>    | clock rise time      |            | -                       | -              | 5    | ns   |

| t <sub>CHCL</sub>    | clock fall time      |            | -                       | -              | 5    | ns   |

[1] Parameters are valid over operating temperature range unless otherwise specified.

[2] Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages.

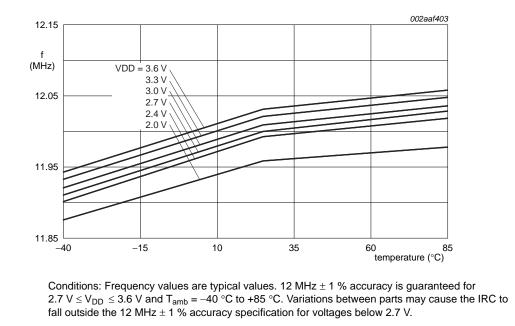

### 10.3 Internal oscillators

#### Table 12. Dynamic characteristics: IRC

$T_{amb} = -40 \text{ °C to } +85 \text{ °C}; 2.7 \text{ V} \le V_{DD} \le 3.6 \text{ V}_{11}.$

| Symbol               | Parameter                           | Conditions | Min   | Typ <u>[2]</u> | Max   | Unit |

|----------------------|-------------------------------------|------------|-------|----------------|-------|------|

| f <sub>osc(RC)</sub> | internal RC oscillator<br>frequency | -          | 11.88 | 12             | 12.12 | MHz  |

[1] Parameters are valid over operating temperature range unless otherwise specified.

[2] Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages.

Fig 21. Internal RC oscillator frequency versus temperature

#### Table 13. Dynamic characteristics: Watchdog oscillator

| Symbol                | Parameter                        | Conditions                                                  |        | Min | Typ[1] | Max | Unit |

|-----------------------|----------------------------------|-------------------------------------------------------------|--------|-----|--------|-----|------|

| f <sub>osc(int)</sub> | internal oscillator<br>frequency | DIVSEL = 0x1F, FREQSEL = 0x1<br>in the WDTOSCCTRL register; | [2][3] | -   | 7.8    | -   | kHz  |

|                       |                                  | DIVSEL = 0x00, FREQSEL = 0xF<br>in the WDTOSCCTRL register  | [2][3] | -   | 1700   | -   | kHz  |

[1] Typical ratings are not guaranteed. The values listed are at nominal supply voltages.

[2] The typical frequency spread over processing and temperature (T<sub>amb</sub> =  $-40 \degree C$  to +85  $\degree C$ ) is ±40 %.

[3] See the LPC11U1x user manual.

#### 32-bit ARM Cortex-M0 microcontroller

### 10.4 I/O pins

#### Table 14. Dynamic characteristics: I/O pins<sup>[1]</sup>

$T_{amb} = -40$  °C to +85 °C; 3.0 V  $\leq V_{DD} \leq 3.6$  V.

| Symbol         | Parameter | Conditions               | Min | Тур | Max | Unit |

|----------------|-----------|--------------------------|-----|-----|-----|------|

| t <sub>r</sub> | rise time | pin configured as output | 3.0 | -   | 5.0 | ns   |

| t <sub>f</sub> | fall time | pin configured as output | 2.5 | -   | 5.0 | ns   |

[1] Applies to standard port pins and RESET pin.

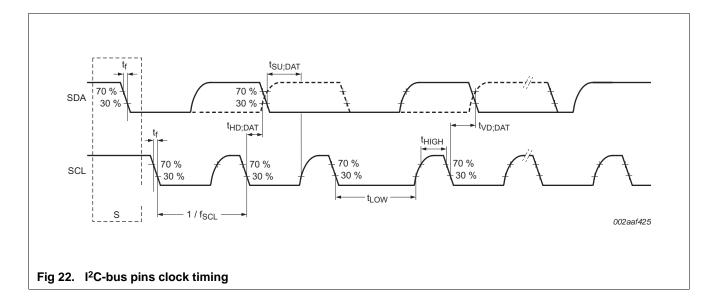

### 10.5 I<sup>2</sup>C-bus

#### Table 15. Dynamic characteristic: I<sup>2</sup>C-bus pins<sup>[1]</sup>

$T_{amb} = -40 \ ^{\circ}C \ to +85 \ ^{\circ}C.$ <sup>[2]</sup>

| Symbol              | Parameter                      |              | Conditions                  | Min                   | Max | Unit |

|---------------------|--------------------------------|--------------|-----------------------------|-----------------------|-----|------|

| f <sub>SCL</sub>    | SCL clock                      |              | Standard-mode               | 0                     | 100 | kHz  |

|                     | frequency                      | frequency    |                             | 0                     | 400 | kHz  |

|                     |                                |              | Fast-mode Plus              | 0                     | 1   | MHz  |

| t <sub>f</sub>      | fall time                      | [4][5][6][7] | of both SDA and SCL signals | -                     | 300 | ns   |

|                     |                                |              | Standard-mode               |                       |     |      |

|                     |                                |              | Fast-mode                   | $20 + 0.1 \times C_b$ | 300 | ns   |

|                     |                                |              | Fast-mode Plus              | -                     | 120 | ns   |

| t <sub>LOW</sub>    | LOW period of the<br>SCL clock |              | Standard-mode               | 4.7                   | -   | μs   |

|                     |                                |              | Fast-mode                   | 1.3                   | -   | μs   |

|                     |                                |              | Fast-mode Plus              | 0.5                   | -   | μs   |

| t <sub>HIGH</sub>   | HIGH period of the             |              | Standard-mode               | 4.0                   | -   | μs   |

|                     | SCL clock                      |              | Fast-mode                   | 0.6                   | -   | μs   |

|                     |                                |              | Fast-mode Plus              | 0.26                  | -   | μs   |

| t <sub>HD;DAT</sub> | data hold time                 | [3][4][8]    | Standard-mode               | 0                     | -   | μs   |

|                     |                                |              | Fast-mode                   | 0                     | -   | μs   |

|                     |                                |              | Fast-mode Plus              | 0                     | -   | μs   |

| t <sub>SU;DAT</sub> | data set-up time               | [9][10]      | Standard-mode               | 250                   | -   | ns   |

|                     |                                |              | Fast-mode                   | 100                   | -   | ns   |

|                     |                                |              | Fast-mode Plus              | 50                    | -   | ns   |

[1] See the I<sup>2</sup>C-bus specification *UM10204* for details.

[2] Parameters are valid over operating temperature range unless otherwise specified.

[3] tHD;DAT is the data hold time that is measured from the falling edge of SCL; applies to data in transmission and the acknowledge.

- [4] A device must internally provide a hold time of at least 300 ns for the SDA signal (with respect to the V<sub>IH</sub>(min) of the SCL signal) to bridge the undefined region of the falling edge of SCL.

- [5]  $C_b = total capacitance of one bus line in pF.$

- [6] The maximum t<sub>f</sub> for the SDA and SCL bus lines is specified at 300 ns. The maximum fall time for the SDA output stage t<sub>f</sub> is specified at 250 ns. This allows series protection resistors to be connected in between the SDA and the SCL pins and the SDA/SCL bus lines without exceeding the maximum specified t<sub>f</sub>.

- [7] In Fast-mode Plus, fall time is specified the same for both output stage and bus timing. If series resistors are used, designers should allow for this when considering bus timing.

### **NXP Semiconductors**

# LPC11U1x

#### 32-bit ARM Cortex-M0 microcontroller

- [8] The maximum t<sub>HD;DAT</sub> could be 3.45 μs and 0.9 μs for Standard-mode and Fast-mode but must be less than the maximum of t<sub>VD;DAT</sub> or t<sub>VD;ACK</sub> by a transition time (see *UM10204*). This maximum must only be met if the device does not stretch the LOW period (t<sub>LOW</sub>) of the SCL signal. If the clock stretches the SCL, the data must be valid by the set-up time before it releases the clock.

- [9] tSU;DAT is the data set-up time that is measured with respect to the rising edge of SCL; applies to data in transmission and the acknowledge.

- [10] A Fast-mode l<sup>2</sup>C-bus device can be used in a Standard-mode l<sup>2</sup>C-bus system but the requirement  $t_{SU;DAT} = 250$  ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line  $t_{r(max)} + t_{SU;DAT} = 1000 + 250 = 1250$  ns (according to the Standard-mode l<sup>2</sup>C-bus specification) before the SCL line is released. Also the acknowledge timing must meet this set-up time.

#### 32-bit ARM Cortex-M0 microcontroller

| Table 18. | Recommended values for $C_{X1}/C_{X2}$ in oscillation mode (crystal and external |

|-----------|----------------------------------------------------------------------------------|

|           | components parameters) low frequency mode                                        |

| Fundamental oscillation frequency F <sub>OSC</sub> | Crystal load<br>capacitance C <sub>L</sub> | Maximum crystal<br>series resistance R <sub>S</sub> | External load<br>capacitors C <sub>X1</sub> , C <sub>X2</sub> |

|----------------------------------------------------|--------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------|

| 1 MHz to 5 MHz                                     | 10 pF                                      | < 300 Ω                                             | 18 pF, 18 pF                                                  |

|                                                    | 20 pF                                      | < 300 Ω                                             | 39 pF, 39 pF                                                  |

|                                                    | 30 pF                                      | < 300 Ω                                             | 57 pF, 57 pF                                                  |

| 5 MHz to 10 MHz                                    | 10 pF                                      | < 300 Ω                                             | 18 pF, 18 pF                                                  |

|                                                    | 20 pF                                      | < 200 Ω                                             | 39 pF, 39 pF                                                  |

|                                                    | 30 pF                                      | < 100 Ω                                             | 57 pF, 57 pF                                                  |

| 10 MHz to 15 MHz                                   | 10 pF                                      | < 160 Ω                                             | 18 pF, 18 pF                                                  |

|                                                    | 20 pF                                      | < 60 Ω                                              | 39 pF, 39 pF                                                  |

| 15 MHz to 20 MHz                                   | 10 pF                                      | < 80 Ω                                              | 18 pF, 18 pF                                                  |

Table 19. Recommended values for  $C_{\chi_1}/C_{\chi_2}$  in oscillation mode (crystal and external components parameters) high frequency mode

| Fundamental oscillation frequency F <sub>OSC</sub> | Crystal load<br>capacitance C <sub>L</sub> | Maximum crystal<br>series resistance R <sub>S</sub> | External load<br>capacitors C <sub>X1</sub> , C <sub>X2</sub> |

|----------------------------------------------------|--------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------|

| 15 MHz to 20 MHz                                   | 10 pF                                      | < 180 Ω                                             | 18 pF, 18 pF                                                  |

|                                                    | 20 pF                                      | < 100 Ω                                             | 39 pF, 39 pF                                                  |

| 20 MHz to 25 MHz                                   | 10 pF                                      | < 160 Ω                                             | 18 pF, 18 pF                                                  |

|                                                    | 20 pF                                      | < 80 Ω                                              | 39 pF, 39 pF                                                  |

## 11.3 XTAL Printed-Circuit Board (PCB) layout guidelines

The crystal should be connected on the PCB as close as possible to the oscillator input and output pins of the chip. Take care that the load capacitors  $C_{x1}$ ,  $C_{x2}$ , and  $C_{x3}$  in case of third overtone crystal usage have a common ground plane. The external components must also be connected to the ground plain. Loops must be made as small as possible in order to keep the noise coupled in via the PCB as small as possible. Also parasitics should stay as small as possible. Values of  $C_{x1}$  and  $C_{x2}$  should be chosen smaller accordingly to the increase in parasitics of the PCB layout.

32-bit ARM Cortex-M0 microcontroller

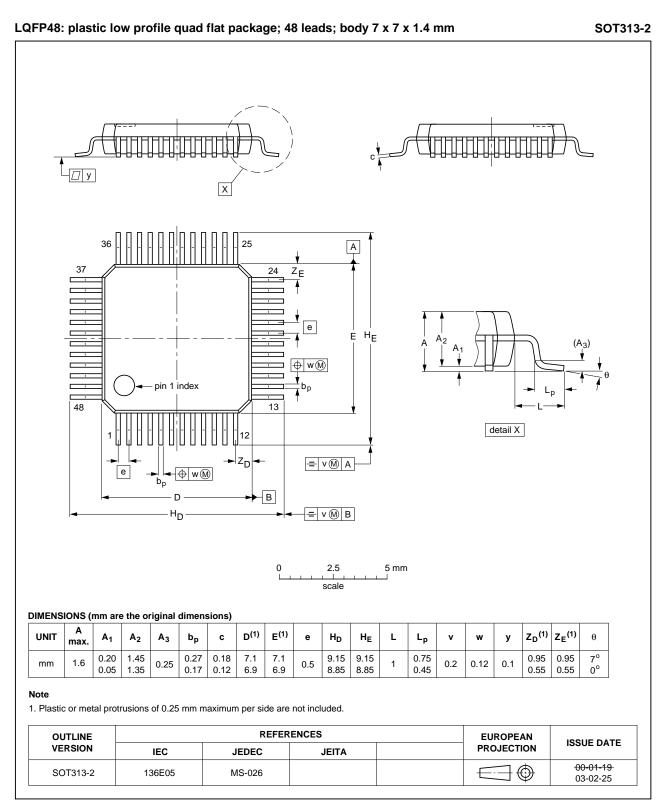

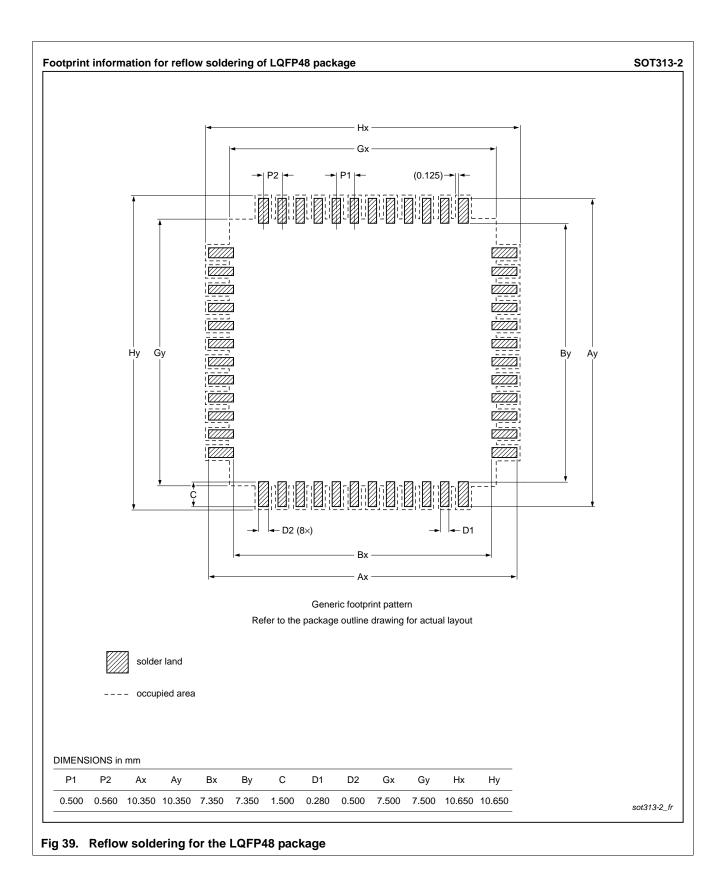

#### Fig 35. Package outline LQFP48 (SOT313-2)

All information provided in this document is subject to legal disclaimers.

### **NXP Semiconductors**

## LPC11U1x

#### 32-bit ARM Cortex-M0 microcontroller

## 16. Revision history

| Document ID    | Release date                                                                                                                                                                                                                                                                                                  | Data sheet status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Change notice          | Supersedes     |  |  |  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------|--|--|--|

| LPC11U1X v.2.2 | 20140311                                                                                                                                                                                                                                                                                                      | Product data sheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -                      | LPC11U1X v.2.1 |  |  |  |

| Modifications: | Updated Sec                                                                                                                                                                                                                                                                                                   | Updated Section 11.1 "Suggested USB interface solutions" for clarity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                        |                |  |  |  |

|                | Open-drain I2C-bus and RESET pin descriptions updated for clarity. See <u>Table 3</u> .                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                        |                |  |  |  |

| LPC11U1X v.2.1 | 20130924                                                                                                                                                                                                                                                                                                      | Product data sheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -                      | LPC11U1X v.2   |  |  |  |

| Modifications: | <ul> <li>Table 3:</li> <li>Added Ta</li> <li>Added Ta</li> <li>Table 8: Rem</li> <li>Added Section</li> <li>Programmab</li> <li>Table 6 "State</li> <li>Updated Section</li> <li>Table 5 "Liminitian"</li> <li>Updated Version</li> <li>Updated Version</li> <li>Changed title with soft-continues</li> </ul> | <ul> <li>Table 3:</li> <li>Added Table note 2 "5 V tolerant pad" to RESET/PIO0_0.</li> <li>Added Table note 4 "For parts with bootloader version 7.0" .</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                        |                |  |  |  |

| LPC11U1X v.2   | 20120111                                                                                                                                                                                                                                                                                                      | Product data sheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -                      | LPC11U1X v.1   |  |  |  |

| Modifications: | <ul> <li>Use of JTAG</li> <li>Sampling fre</li> <li>Conditions for</li> <li>Part LPC11L</li> <li>Editorial upd</li> <li>ROM-based</li> <li>Use of USB</li> <li>Power consult</li> <li>SSP dynamic</li> <li>IRC dynamic</li> </ul>                                                                             | 20120111       Product data sheet       -       LPC11U1X v.1         • Number of physical and logical endpoints corrected in Section 7.8.1.       • Use of JTAG updated in Section 2 (for BSDL only).         • Sampling frequency corrected in Table note 7 of Table 7.       • Conditions for parameter T <sub>stg</sub> updated in Table 5.         • Part LPC11U14FHI33/201 added.       • Editorial updates.         • ROM-based integer division routines added (Section 2).       • Use of USB with power profiles specified (Section 7.8).         • Power consumption data added in Section 9.2.       • SSP dynamic characteristics added (Table 16).         • IRC dynamic characteristics added to Product data sheet.       • Section 13 added.         • Description of pin PIO0_3 updated in Table 3: this pin is not used by the boot loader. |                        |                |  |  |  |

|                | Section 13 a                                                                                                                                                                                                                                                                                                  | dded.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Or this sis is not use |                |  |  |  |

#### Table 21. Revision history

#### 32-bit ARM Cortex-M0 microcontroller

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Non-automotive qualified products — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b)

## 18. Contact information

whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

## 17.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

I<sup>2</sup>C-bus — logo is a trademark of NXP Semiconductors N.V.

For more information, please visit: <u>http://www.nxp.com</u>

For sales office addresses, please send an email to: salesaddresses@nxp.com