Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Last Time Buy                                                                 |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | XC800                                                                         |

| Core Size                  | 8-Bit                                                                         |

| Speed                      | 24MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, SSC, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                                    |

| Number of I/O              | 23                                                                            |

| Program Memory Size        | 8KB (8K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | <u>.</u>                                                                      |

| RAM Size                   | 512 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 8x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-TSSOP (0.173", 4.40mm Width)                                               |

| Supplier Device Package    | PG-TSSOP-28-1                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc836m2friabfxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Summary of Features

# **1** Summary of Features

The XC835/836 has the following features:

- High-performance XC800 Core

- compatible with standard 8051 processor

- two clocks per machine cycle architecture (for memory access without wait state)

- two data pointers

- On-chip memory

- 8 Kbytes of Boot ROM, Library ROM and User routines

- 256 bytes of RAM

- 256 bytes of XRAM

- 4/8 Kbytes of Flash (includes memory protection strategy)

- I/O port supply at 2.5 V 5.5 V and core logic supply at 2.5 V (generated by embedded voltage regulator)

| 8/4K Bytes<br>Flash  | On-Chip De                     | bug Support       | IIC               | UART              | SSC                 | Port 0            | 8-bit Digital VO |

|----------------------|--------------------------------|-------------------|-------------------|-------------------|---------------------|-------------------|------------------|

| Boot ROM<br>8K Bytes |                                | V 0000 0 are      |                   |                   | ompare Unit<br>-bit | Port 1            | 6-bit Digital VO |

| XRAM<br>256 Bytes    |                                | XC800 Core        |                   |                   | are Unit<br>-bit    | Port 2            | 8-bit Digital/   |

| RAM<br>256 Bytes     | LED and Touch Sense Controller |                   |                   | 10                | DC<br>-bit<br>annel | Port 3            | 3-bit Digital VO |

| MDU                  | CORDIC                         | Timer 0<br>16-bit | Timer 1<br>16-bit | Timer 2<br>16-bit | Real-Time<br>Clock  | Watchdog<br>Timer |                  |

|                      | 1                              |                   |                   | 1                 | 1                   |                   | y                |

### Figure 1 XC835/836 Functional Units

- Power-on reset generation

- Brownout detection for IO supply and core logic supply

- 48 MHz on-chip OSC for clock generation

Loss-of-Clock detection

(more features on next page)

### **Summary of Features**

Features: (continued)

- Power saving modes

- idle mode

- power-down mode with wake-up capability via real-time clock event

- clock gating control to each peripheral

- Programmable 16-bit Watchdog Timer (WDT) running on independent oscillator with programmable window feature for refresh operation and warning prior to overflow

- Three general purpose I/O ports

- 4 high current I/O

- 2 high sink I/O

- Up to 25 pins as digital I/O

- Up to 8 pins as digital/analog input

- Up to 8 channels, 10-bit A/D Converter

- support up to 7 differential input channel

- results filtering by data reduction or digital low-pass filter, for up to 13-bit results

- Up to 8 channels, Out of range comparator

- Three 16-bit timers

٠

- Timer 0 and Timer 1 (T0 and T1)

- Timer 2 (T2)

- Real-time clock with 32.768 kHz crystal pad

- 16-bit Vector Computer for Field-Oriented Control (FOC)

- Multiplication/Division Unit (MDU) for arithmetic calculation

- CORDIC Unit for trigonometric calculation

- Capture and Compare unit for PWM signal generation (CCU6)

- A full-duplex or half-duplex serial interface (UART)

- Synchronous serial channel (SSC)

- Inter-IC (IIC) serial interface

- LED and Touch-sense Controller (LEDTSCU)

- Software libraries to support fixed-point control and EEPROM emulation

- On-chip debug support via single pin DAP interface (SPD)

- Packages:

- PG-DSO-24

- PG-TSSOP-28

- Temperature range  $T_A$ :

- SAF (-40 to 85 °C)

- SAK (-40 to 125 °C)

#### Summary of Features

#### XC835/836 Variant Devices

The XC835/836 product family features devices with different configurations, program memory sizes, packages options and temperature profiles, to offer cost-effective solutions for different application requirements.

The list of XC835/836 device configurations are summarized in **Table 1**. The type of packages available are DSO-24 for XC835 and TSSOP-28 for XC836.

| Device Name | MDU and CORDIC Module | LEDTSCU Module |

|-------------|-----------------------|----------------|

| XC835/836   | No                    | No             |

| XC835/836M  | Yes                   | No             |

| XC835/836T  | No                    | Yes            |

| XC835/836MT | Yes                   | Yes            |

#### Table 1 Device Configuration

Table 2 shows the device sales type available, based on above device.

| Sales Type       | Device<br>Type | Program<br>Memory<br>(Kbytes) | Temp-<br>erature<br>Profile<br>(°C) | Package<br>Type | Quality<br>Profile |

|------------------|----------------|-------------------------------|-------------------------------------|-----------------|--------------------|

| SAF-XC835MT-2FGI | Flash          | 8                             | -40 to 85                           | PG-DSO-24-1     | Industrial         |

| SAF-XC836-2FRI   | Flash          | 8                             | -40 to 85                           | PG-TSSOP-28-1   | Industrial         |

| SAF-XC836T-2FRI  | Flash          | 8                             | -40 to 85                           | PG-TSSOP-28-1   | Industrial         |

| SAF-XC836M-2FRI  | Flash          | 8                             | -40 to 85                           | PG-TSSOP-28-1   | Industrial         |

| SAF-XC836M-1FRI  | Flash          | 4                             | -40 to 85                           | PG-TSSOP-28-1   | Industrial         |

| SAF-XC836MT-2FRI | Flash          | 8                             | -40 to 85                           | PG-TSSOP-28-1   | Industrial         |

| SAF-XC836-2FRA   | Flash          | 8                             | -40 to 85                           | PG-TSSOP-28-12  | Automotive         |

| SAF-XC836MT-2FRA | Flash          | 8                             | -40 to 85                           | PG-TSSOP-28-12  | Automotive         |

| SAF-XC836MT-1FRA | Flash          | 4                             | -40 to 85                           | PG-TSSOP-28-12  | Automotive         |

| SAK-XC836MT-2FRA | Flash          | 8                             | -40 to 125                          | PG-TSSOP-28-12  | Automotive         |

| SAK-XC836MT-1FRA | Flash          | 4                             | -40 to 125                          | PG-TSSOP-28-12  | Automotive         |

As this document refers to all the derivatives, some description may not apply to a specific product. For simplicity, all versions are referred to by the term XC835/836 throughout this document.

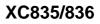

## 2.3 Pin Configuration

The pin configuration of the XC835 in Figure 4.

Figure 4 XC835 Pin Configuration, PG-DSO-24 Package (top view)

## 2.4 Pin Definitions and Functions

The functions and default states of the XC835/836 external pins are provided in Table 3.

### Table 3 Pin Definitions and Functions for XC835/836

| Symbol | Pin<br>Number<br>TSSOP28/<br>DS024 | Туре | Reset<br>State | Function                                                                                                                                                                        |                                                    |  |  |

|--------|------------------------------------|------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|--|

| P0     |                                    | I/O  |                | <b>Port 0</b><br>Port 0 is a bidirectional general purpose I/O port<br>It can be used as alternate functions for<br>LEDTSCU, Timer 0, 1 and 2, SSC, CCU6, IIC,<br>SPD and UART. |                                                    |  |  |

| P0.0   | 21/19                              |      | Hi-Z           | T2_0                                                                                                                                                                            | Timer 2 Input                                      |  |  |

|        |                                    |      |                | T13HR_1                                                                                                                                                                         | CCU6 Timer 13 Hardware Run<br>Input                |  |  |

|        |                                    |      |                | MTSR_2                                                                                                                                                                          | SSC Master Transmit Output/<br>Slave Receive Input |  |  |

|        |                                    |      |                | MRST_3                                                                                                                                                                          | SSC Master Receive Input                           |  |  |

|        |                                    |      |                | T12HR_0                                                                                                                                                                         | CCU6 Timer 12 Hardware Run<br>Input                |  |  |

|        |                                    |      |                | CCPOS0_0                                                                                                                                                                        | CCU6 Hall Input 0                                  |  |  |

|        |                                    |      |                | TSIN0                                                                                                                                                                           | Touch-sense Input 0                                |  |  |

|        |                                    |      |                | LINE0                                                                                                                                                                           | LED Line 0                                         |  |  |

|        |                                    |      |                | COUT61_1                                                                                                                                                                        | Output of Capture/Compare<br>Channel 1             |  |  |

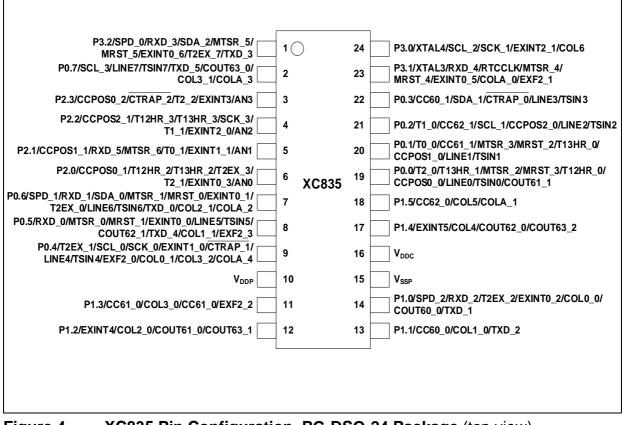

### 2.5 Memory Organization

The XC835/836 CPU operates in the following five address spaces:

- 8 Kbytes of Boot ROM, Library ROM and User routines

- 256 bytes of internal RAM

- 256 bytes of XRAM (XRAM can be read/written as program memory or external data memory)

- A 128-byte Special Function Register area

- 4/8 Kbytes of Flash

Figure 6 illustrates the memory address spaces of the 4 Kbyte Flash devices. Figure 7 illustrates the memory address spaces of the 8 Kbyte Flash devices.

Figure 6 Memory Map of XC835/836 with 4 Kbytes of Flash memory

### 2.6 JTAG ID

JTAG ID register is a read-only register located inside the JTAG module, and is used to recognize the device(s) connected to the JTAG interface. Its content is shifted out when INSTRUCTION register contains the IDCODE command (opcode  $04_H$ ), and the same is also true immediately after reset.

The JTAG ID register contents for the XC835/836 Flash devices are given in Table 4.

| Device Type | Device Name | JTAG ID                |  |

|-------------|-------------|------------------------|--|

| Flash       | XC835*-2FG  | 101B A083 <sub>H</sub> |  |

|             | XC836*-2FR  |                        |  |

|             | XC836*-1FR  | 101B B083 <sub>H</sub> |  |

#### Table 4JTAG ID Summary

Note: The asterisk (\*) above denotes all possible device configurations.

# 3 Electrical Parameters

**Chapter 3** provides the characteristics of the electrical parameters which are implementation-specific for the XC835/836.

### 3.1 General Parameters

The general parameters are described here to aid the users in interpreting the parameters mainly in **Section 3.2** and **Section 3.3**.

### 3.1.1 Parameter Interpretation

The parameters listed in this section represent partly the characteristics of the XC835/836 and partly its requirements on the system. To aid interpreting the parameters easily when evaluating them for a design, they are indicated by the abbreviations in the "Symbol" column:

- CC

- These parameters indicate **C**ontroller **C**haracteristics, which are distinctive features of the XC835/836 and must be regarded for a system design.

- SR

- These parameters indicate System Requirements, which must be provided by the microcontroller system in which the XC835/836 is designed in.

### 3.1.2 Absolute Maximum Rating

Maximum ratings are the extreme limits to which the XC835/836 can be subjected to without permanent damage.

| Parameter                                                    | Symbol                | Lim  | it Values | Unit | Notes      |

|--------------------------------------------------------------|-----------------------|------|-----------|------|------------|

|                                                              |                       | Min. | Max.      |      |            |

| Ambient temperature                                          | T <sub>A</sub>        | -40  | 125       | °C   | under bias |

| Storage temperature                                          | T <sub>ST</sub>       | -65  | 150       | °C   | -          |

| Junction temperature                                         | TJ                    | -40  | 150       | °C   | under bias |

| Voltage on power supply pin with respect to $V_{\rm SS}$     | $V_{DDP}$             | -0.5 | 6         | V    |            |

| Maximum current per pin for P1[3:0]                          | I <sub>M</sub>        | -115 | 115       | mA   |            |

| Input current on any pin during overload condition           | I <sub>IN</sub>       | -10  | 10        | mA   |            |

| Absolute sum of all input currents during overload condition | $\Sigma  I_{\sf IN} $ | -    | 50        | mA   |            |

Table 6Absolute Maximum Rating Parameters

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. During absolute maximum rating overload conditions ( $V_{IN} > V_{DDP}$  or  $V_{IN} < V_{SS}$ ) the voltage on  $V_{DDP}$  pin with respect to ground ( $V_{SS}$ ) must not exceed the values defined by the absolute maximum ratings.

#### Table 8 Input/Output Characteristics (Operating Conditions apply) (cont'd)

| Parameter                                                                           | Symbol             |    | Limit | Values | Unit | Test Conditions |  |

|-------------------------------------------------------------------------------------|--------------------|----|-------|--------|------|-----------------|--|

|                                                                                     |                    |    | Min.  | Max.   |      |                 |  |

| Voltage on any pin during $V_{\text{DDP}}$ power off                                | V <sub>PO</sub>    | SR | -     | 0.3    | V    | 5)              |  |

| Maximum current per<br>pin (excluding P1,<br>$V_{\text{DDP}}$ and $V_{\text{SS}}$ ) | I <sub>MP</sub>    | SR | -15   | 25     | mA   | _               |  |

| Maximum current per<br>pin for P1[3:0]                                              | I <sub>MP1A</sub>  | SR | -50   | 50     | mA   | _               |  |

| Maximum current per pin for P1[5:4]                                                 | I <sub>MP1B</sub>  | SR | -30   | 50     | mA   | -               |  |

| Maximum current into $V_{\text{DDP}}$                                               | I <sub>MVDDP</sub> | SR | -     | 130    | mA   | 4)              |  |

| $\frac{1}{10000000000000000000000000000000000$                                      | I <sub>MVSS</sub>  | SR | -     | 130    | mA   | 4)              |  |

1) Not subjected to production test, verified by design/characterization. Hysteresis is implemented to avoid meta stable states and switching due to internal ground bounce. It cannot be guaranteed that it suppresses switching due to external system noise.

2) An additional error current ( $I_{INJ}$ ) will flow if an overload current flows through an adjacent pin.

3) Over current detection is available for 5V application only.

4) Not subjected to production test, verified by design/characterization.

5) Not subjected to production test, verified by design/characterization. However, for applications with strict low power-down current requirements, it is mandatory that no active voltage source is supplied at any GPIO pin when V<sub>DDP</sub> is powered off.

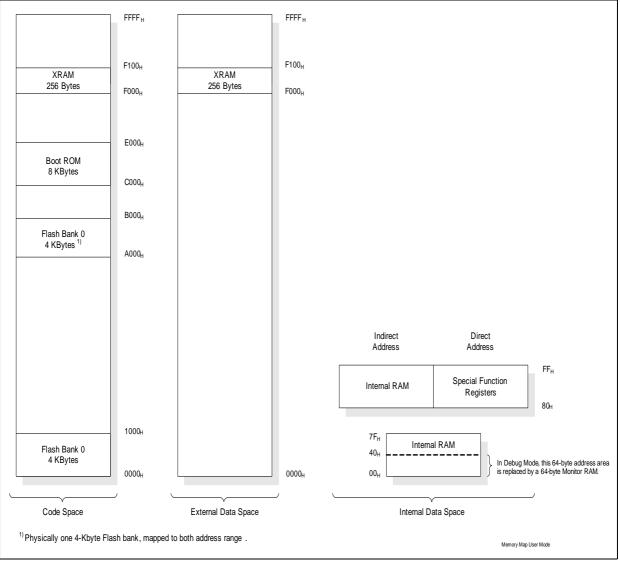

## 3.2.2 Supply Threshold Characteristics

Table 9 provides the characteristics of the supply threshold in the XC835/836.

#### Figure 8 Supply Threshold Parameters

#### Table 9 Supply Threshold Parameters (Operating Conditions apply)

| •••                  | -                                                                                                                                                             |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                      |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol               |                                                                                                                                                               | Lin                                                                                      | nit Val                                                                                                                                                                                                                                                                                                                                                                                                                            | ues                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Unit                                                                                                                                                                                                                                                                                                                 |

|                      |                                                                                                                                                               | Min.                                                                                     | Тур.                                                                                                                                                                                                                                                                                                                                                                                                                               | Max.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                      |

| $V_{DDPPW}$          | CC                                                                                                                                                            | 3.0                                                                                      | 3.6                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | V                                                                                                                                                                                                                                                                                                                    |

| $V_{DDPBOA}$         | CC                                                                                                                                                            | 2.65                                                                                     | 2.75                                                                                                                                                                                                                                                                                                                                                                                                                               | 2.87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | V                                                                                                                                                                                                                                                                                                                    |

| V <sub>DDPBOPD</sub> |                                                                                                                                                               | 3.0                                                                                      | 3.6                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | V                                                                                                                                                                                                                                                                                                                    |

| $V_{\rm DDPSRR}$     | CC                                                                                                                                                            | 2.7                                                                                      | 2.8                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | V                                                                                                                                                                                                                                                                                                                    |

| $V_{DDCPW}$          | CC                                                                                                                                                            | 2.3                                                                                      | 2.4                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | V                                                                                                                                                                                                                                                                                                                    |

| $V_{\rm DDCBOA}$     | CC                                                                                                                                                            | 2.25                                                                                     | 2.3                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | V                                                                                                                                                                                                                                                                                                                    |

| $V_{\rm DDCBOPD}$    | CC                                                                                                                                                            | 1.35                                                                                     | 1.5                                                                                                                                                                                                                                                                                                                                                                                                                                | 1.95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | V                                                                                                                                                                                                                                                                                                                    |

| $V_{\rm DDCSRR}$     | CC                                                                                                                                                            | 2.28                                                                                     | 2.3                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | V                                                                                                                                                                                                                                                                                                                    |

| $V_{\rm DDCRDR}$     | CC                                                                                                                                                            | 1.1                                                                                      | _                                                                                                                                                                                                                                                                                                                                                                                                                                  | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V                                                                                                                                                                                                                                                                                                                    |

|                      | V <sub>DDPPW</sub><br>V <sub>DDPBOA</sub><br>V <sub>DDPBOPD</sub><br>V <sub>DDPSRR</sub><br>V <sub>DDCPW</sub><br>V <sub>DDCBOA</sub><br>V <sub>DDCBOPD</sub> | VDDPPWCCVDDPBOACCVDDPBOPDCCVDDPSRRCCVDDCPWCCVDDCBOACCVDCBOACCVDCCBOACCVDCCBOACCVDCCSRRCC | и         и           V <sub>DDPPW</sub> CC         3.0           V <sub>DDPBOA</sub> CC         2.65           V <sub>DDPBOPD</sub> .         3.0           V <sub>DDPBOPD</sub> .         3.0           V <sub>DDPBOPD</sub> .         2.7           V <sub>DDPSRR</sub> CC         2.3           V <sub>DDCPW</sub> CC         2.35           V <sub>DDCBOA</sub> CC         1.35           V <sub>DDCSRR</sub> CC         2.28 | Min.         Typ. $V_{\text{DDPPW}}$ CC         3.0         3.6 $V_{\text{DDPBOA}}$ CC         2.65         2.75 $V_{\text{DDPBOA}}$ CC         3.0         3.6 $V_{\text{DDPBOA}}$ CC         2.65         2.75 $V_{\text{DDPBOPD}}$ .         3.0         3.6 $V_{\text{DDPBOPD}}$ .         2.75         2.75 $V_{\text{DDCPW}}$ CC         2.77         2.8 $V_{\text{DDCBOA}}$ CC         2.3         2.4 $V_{\text{DDCBOA}}$ CC         2.255         2.3 $V_{\text{DDCBOA}$ CC         1.355         1.5 $V_{\text{DDCSRR}}$ CC         2.28         2.3 | Min.Typ.Max. $V_{\text{DDPPW}}$ CC3.03.64.5 $V_{\text{DDPBOA}}$ CC2.652.752.87 $V_{\text{DDPBOPD}}$ 3.03.64.5 $V_{\text{DDPBOPD}}$ 3.03.64.5 $V_{\text{DDPBOPD}}$ 2.772.82.92 $V_{\text{DDPSRR}}$ CC2.32.42.48 $V_{\text{DDCPW}}$ CC2.252.32.42 $V_{\text{DDCBOA}}$ CC1.351.51.95 $V_{\text{DDCSRR}}$ CC2.282.342.47 |

Detection is enabled via SDCON register in active mode. It is automatically disabled in power down mode. Detection should be disabled for V<sub>DDP</sub> less than maximum of V<sub>DDPPW</sub>.

2) This parameter has a hysteresis of 50 mV.

- Detection is enabled via SDCON register. Detection must be disabled for application with V<sub>DDP</sub> less than the specified values.

- 4) V<sub>DDPSRR</sub> and V<sub>DDCSRR</sub> must be met before the system reset is released.

- 5) Detection is enabled via SDCON register in active mode. It is automatically disabled in power down mode.

## 3.2.3 ADC Characteristics

The values in **Table 10** are given for an analog power supply of 5.0 V. The ADC can be used with an analog power supply down to 3 V. But in this case, analog parameters may show a reduced performance. In the reduced voltage mode (2.5 V <  $V_{\text{DDP}}$  < 3 V), the ADC is not recommended to be used.

|                                                                           | - 12 101112)       |    |                           |                  |                   |      |                                                             |

|---------------------------------------------------------------------------|--------------------|----|---------------------------|------------------|-------------------|------|-------------------------------------------------------------|

| Parameter                                                                 | Symbol             |    | Li                        | mit Va           | lues              | Unit | Test                                                        |

|                                                                           |                    |    | Min.                      | Тур.             | Max.              |      | Conditions /<br>Remarks                                     |

| Analog reference voltage                                                  | V <sub>AREF</sub>  |    | _                         | $V_{DDP}$        | _                 | V    | Connect internally to $V_{\text{DDP}}$                      |

| Analog reference ground                                                   | V <sub>AGND</sub>  |    | _                         | V <sub>SSP</sub> | -                 | V    | Connect internally to $V_{\rm SSP}$                         |

| Alternate analog<br>reference ground                                      | $V_{\rm AGNDALT}$  | SR | V <sub>SSP</sub> -<br>0.1 | -                | 2.5 <sup>1)</sup> | V    | Connect to AN0<br>in differential<br>mode, See<br>Figure 9. |

| Internal voltage<br>reference                                             | VINTREF            | SR | 1.19                      | 1.23             | 1.28              | V    | 4)                                                          |

| Analog input voltage range                                                | V <sub>AIN</sub>   | SR | $V_{AGND}$                | -                | $V_{AREF}$        | V    | -                                                           |

| ADC clock                                                                 | f <sub>adci</sub>  |    | 8                         | -                | 16                | MHz  | internal analog<br>clock                                    |

| Sample time                                                               | t <sub>S</sub>     | CC | (2 + IN)<br>$t_{ADCI}$    | PCR0.            | STC) ×            | μs   | -                                                           |

| Conversion time                                                           | t <sub>C</sub>     | CC | See Se                    | ection           | 3.2.3.1           | μs   | -                                                           |

| Set-up time between<br>conversions using<br>internal voltage<br>reference | t <sub>SETUP</sub> | SR | _                         | 35               | _                 | μs   | 2)                                                          |

| Table 10 | ADC Characteristics (Operating Conditions apply; $V_{\text{DDP}}$ = 5 V; |

|----------|--------------------------------------------------------------------------|

|          | <i>f</i> <sub>ADCI</sub> <= 12 MHz)                                      |

| Table 10 | ADC Characteristics (Operating Conditions apply; $V_{\text{DDP}}$ = 5 V; |

|----------|--------------------------------------------------------------------------|

|          | f <sub>ADCI</sub> <b>&lt;= 12 MHz)</b> (cont'd)                          |

| Parameter                                     | Symbol             |    | Li   | imit Va | lues     | Unit  | Test                                                               |

|-----------------------------------------------|--------------------|----|------|---------|----------|-------|--------------------------------------------------------------------|

|                                               |                    |    | Min. | Тур.    | Max.     |       | Conditions /<br>Remarks                                            |

| Total unadjusted<br>error                     | TUE <sup>3)</sup>  | CC | _    | -       | ±1       | LSB8  | 8-bit conversion<br>with internal<br>reference <sup>4)</sup>       |

|                                               |                    |    | _    | _       | +4/-2    | LSB10 | 10-bit<br>conversion with<br>internal<br>reference <sup>4)5)</sup> |

|                                               |                    |    | _    | _       | +14/-2   | LSB12 | 12-bit<br>conversion using<br>the Low Pass<br>Filter <sup>4)</sup> |

| Differential<br>Nonlinearity                  | EA <sub>DNL</sub>  | CC | -    | -       | +1.5/ -1 | LSB   | 10-bit<br>conversion <sup>4)</sup>                                 |

| Integral Nonlinearity                         | EA <sub>INL</sub>  | CC | -    | -       | ±1.5     | LSB   | 10-bit<br>conversion <sup>4)</sup>                                 |

| Offset                                        | EA <sub>OFF</sub>  | CC | -    | +4      | -        | LSB   | 10-bit<br>conversion <sup>4)</sup>                                 |

| Gain                                          | EA <sub>GAIN</sub> | CC | -    | -4      | -        | LSB   | 10-bit<br>conversion <sup>4)</sup>                                 |

| Switched<br>capacitance at an<br>analog input | C <sub>AINSW</sub> | CC | _    | 2       | 3        | pF    | 4)6)                                                               |

| Total capacitance at an analog input          | C <sub>AINT</sub>  | CC | -    | -       | 12       | pF    | 4)6)                                                               |

| Input resistance of<br>an analog input        | R <sub>AIN</sub>   | CC | -    | 1.5     | 2        | kΩ    | 4)                                                                 |

1) 1.2 V at  $V_{\text{DDP}} = 3.0$  V.

2) Not subject to production test, verified at CPU clock ( $f_{SCLK, CCLK}$ ) = 8 MHz,  $T_A$  = + 25 °C and  $V_{DDP}$  = 5 V.

3) TUE is tested at  $V_{AREF} = V_{DDP} = 5.0 \text{ V}$  and CPU clock ( $f_{SCLK, CCLK}$ ) = 8 MHz.

4) Not subject to production test, verified by design/characterization.

5) If a reduced positive reference voltage is used, TUE will increase. If the positive reference is reduced by a factor of K, the TUE will increased by 1/K. Example:K = 0.8, 1/K = 1.25; 1.25 X TUE = 2.5 LSB10.

6) The sampling capacity of the conversion C-Network is pre-charged to  $V_{AREF}/2$  before connecting the input to the C-Network. Because of the parasitic elements, the voltage measured at ANx is lower than  $V_{AREF}/2$ .

### 3.2.4 Flash Memory Parameters

The XC835/836 is delivered with all Flash sectors erased (read all zeros).

The data retention time of the XC835/836's Flash memory (i.e. the time after which stored data can still be retrieved) depends on the number of times the Flash memory has been erased and programmed.

Note: Flash memory parameters are not subject to production test but verified by design and/or characterization.

| Parameter                           | Symbol               |    | Lir  | nit Val | ues  | Unit | Remarks            |

|-------------------------------------|----------------------|----|------|---------|------|------|--------------------|

|                                     |                      |    | Min. | Тур.    | Max. |      |                    |

| Read access time<br>(per byte)      | t <sub>ACC</sub>     | CC | -    | 125     | -    | ns   |                    |

| Programming time<br>(per wordline)  | t <sub>PR</sub>      | CC | -    | 2.2     | -    | ms   |                    |

| Erase time<br>(one or more sectors) | t <sub>ER</sub>      | CC | -    | 120     | -    | ms   |                    |

| Flash wait states                   | N <sub>WSFLASH</sub> | CC |      | 0       |      |      | CPU clock = 8 MHz  |

|                                     |                      |    |      | 1       |      |      | CPU clock = 24 MHz |

#### Table 12Flash Timing Parameters (Operating Conditions apply)

#### Table 13 Flash Data Retention and Endurance (Operating Conditions apply)

|           |                         | · ·            | • • • • • |

|-----------|-------------------------|----------------|-----------|

| Retention | Endurance <sup>1)</sup> | Size           | Remarks   |

| 20 years  | 1,000 cycles            | up to 8 Kbytes |           |

| 5 years   | 10,000 cycles           | 1 Kbyte        |           |

| 2 years   | 70,000 cycles           | 512 bytes      |           |

| 2 years   | 100,000 cycles          | 128 bytes      |           |

1) One cycle refers to the programming of all wordlines in a sector and erasing of sector. The Flash endurance data specified in **Table 13** is valid only if the following conditions are fulfilled:

- the maximum number of erase cycles per Flash sector must not exceed 100,000 cycles.

- the maximum number of erase cycles per Flash bank must not exceed 300,000 cycles.

- the maximum number of program cycles per Flash bank must not exceed 2,500,000 cycles.

- 7) Timer 2 active current is measured with: module enabled, timer running in 8 MHz

- 8) MDU active current is measured with: module enabled, division operation was performed.

- 9) CORDIC active mode is measured with: module enabled, circular mode was selected for the calculation.

- 10) LEDTSCU active curent is measured with: module enabled, counter running in 8 MHz.

- 11) IIC active current is measured with: module enabled, performing a master transmit with the master clock running at 400 KHz.

### 3.3.2 Output Rise/Fall Times

Table 18 provides the characteristics of the output rise/fall times in the XC835/836.

| Table 18 | Output Rise/Fall Times Parameters (Operating Conditions apply) |

|----------|----------------------------------------------------------------|

|----------|----------------------------------------------------------------|

| Parameter                                                     | Symbol                                   | Limit | Values | Unit | Test Conditions                              |

|---------------------------------------------------------------|------------------------------------------|-------|--------|------|----------------------------------------------|

|                                                               |                                          | Min.  | Max.   |      |                                              |

| Rise/fall times on High<br>Current Pad Type A <sup>1)2)</sup> | t <sub>HCPR</sub> ,<br>t <sub>HCPF</sub> | -     | 15     | ns   | 20 pF @ Fast edge<br>(5 V) <sup>3)</sup> .   |

|                                                               |                                          | -     | 150    | ns   | 20 pF @ Slow Edge<br>(5 V) <sup>3)</sup> .   |

|                                                               |                                          | _     | 25     | ns   | 20 pF @ Fast edge<br>(3.3 V) <sup>4)</sup> . |

|                                                               |                                          | _     | 300    | ns   | 20 pF @ Slow edge<br>(3.3 V) <sup>4)</sup> . |

| Rise/fall times on High<br>Current Pad Type B <sup>1)2)</sup> | t <sub>R</sub> , t <sub>F</sub>          | -     | 10     | ns   | 20 pF <sup>3)4)</sup><br>(5 V & 3.3 V).      |

| Rise/fall times on<br>Standard Pad <sup>1)2)</sup>            | t <sub>R</sub> , t <sub>F</sub>          | -     | 10     | ns   | 20 pF <sup>3)4)</sup><br>(5 V & 3.3 V).      |

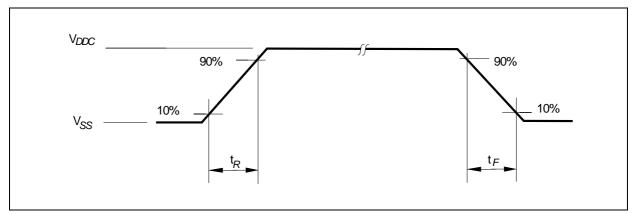

1) Rise/Fall time parameters are taken with 10% - 90% of supply.

2) Not all parameters are 100% tested, but are verified by design/characterisation and test correlation.

3) Additional rise/fall time valid for  $C_L = 20 \text{ pF} - C_L = 100 \text{ pF} @ 0.125 \text{ ns/pF} at 5 \text{ V}$  supply voltage.

4) Additional rise/fall time valid for  $C_L = 20 \text{ pF} - C_L = 100 \text{ pF} \cdot @ 0.225 \text{ ns/pF}$  at 3.3 V supply voltage.

Figure 14 Rise/Fall Times Parameters

Table 21 provides the characteristics of the 75 kHz oscillator in the XC835/836.

| Parameter                      | Symbol              |    | Limit Values |      |      | Unit | Test Conditions                                                                    |  |

|--------------------------------|---------------------|----|--------------|------|------|------|------------------------------------------------------------------------------------|--|

|                                |                     |    | Min.         | Тур. | Max. |      |                                                                                    |  |

| Nominal frequency              | f <sub>nom</sub>    | CC | -1%          | 75   | +1%  | KHz  | under nominal conditions <sup>1)</sup> after trimming                              |  |

| Long term frequency deviation  | $\Delta f_{\rm LT}$ | CC | -4.5         | _    | 4.5  | %    | with respect to $f_{NOM}$ , over<br>lifetime and temperature<br>(-40 °C to 125 °C) |  |

| Short term frequency deviation | $\Delta f_{\rm ST}$ | CC | -1.5         | _    | 1.5  | %    | with respect to $f_{\rm NOM}$ , over $V_{\rm DDC}$                                 |  |

| Table 21 | 75 kHz Oscillator Characteristics (Operating Conditions apply) |

|----------|----------------------------------------------------------------|

|----------|----------------------------------------------------------------|

1) Nominal condition:  $V_{\text{DDC}} = 2.5 \text{ V}, T_{\text{A}} = +25^{\circ}\text{C}.$

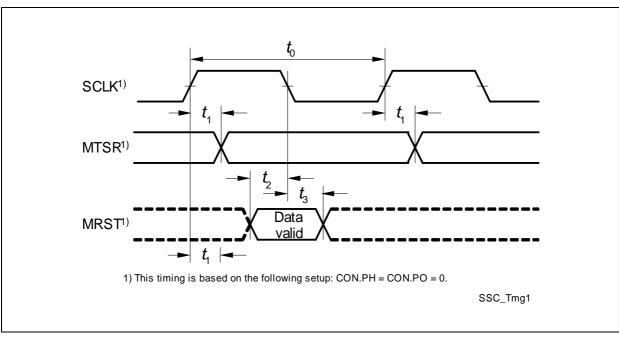

### 3.3.5 SSC Timing

### 3.3.5.1 SSC Master Mode Timing

Table 22 provides the SSC master mode timing in the XC835/836.

### Table 22SSC Master Mode Timing<sup>1)</sup> (Operating Conditions apply; CL = 50 pF)

| Parameter            | Sym            | nbol | Limit                              | Unit |    |

|----------------------|----------------|------|------------------------------------|------|----|

|                      |                |      | Min.                               | Max. |    |

| SCLK clock period    | t <sub>0</sub> | CC   | 2 * T <sub>SSC</sub> <sup>2)</sup> | -    | ns |

| MTSR delay from SCLK | t <sub>1</sub> | CC   | 0                                  | 3    | ns |

| MRST set-up to SCLK  | t <sub>2</sub> | SR   | 32                                 | -    | ns |

| MRST hold from SCLK  | t <sub>3</sub> | SR   | 0                                  | -    | ns |

1) Not subject to production test, verified by design/characterisation.

2)  $T_{SSCmin} = T_{CPU} = 1/f_{CPU}$ . When  $f_{CPU} = 24$  MHz,  $t_0 = 83.3$  ns.  $T_{CPU}$  is the CPU clock period.

Figure 15 SSC Master Mode Timing

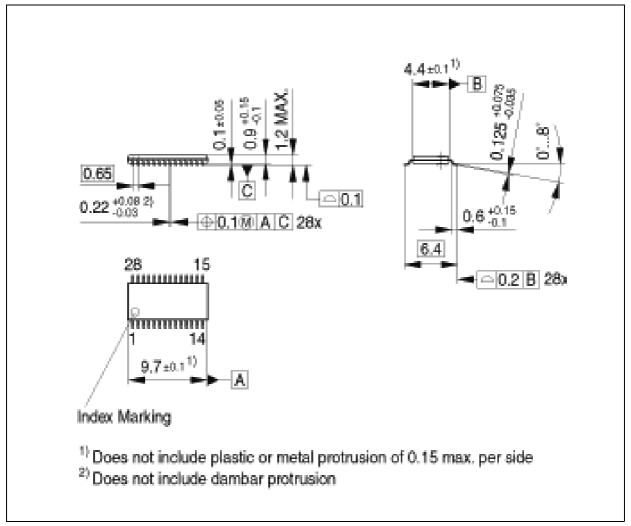

### Package and Quality Declaration

# 4 Package and Quality Declaration

Chapter 4 provides the information of the XC835/836 package and reliability section.

### 4.1 Package Parameters

Table 24 provides the thermal characteristics of the packages used in XC835 and XC836 respectively.

| Parameter                   | Symb      | Symbol |      | t Values | Unit | Package Types  |

|-----------------------------|-----------|--------|------|----------|------|----------------|

|                             |           |        | Min. | Max.     |      |                |

| Thermal resistance junction | $R_{TJC}$ | CC     | -    | 30.8     | K/W  | PG-DSO-24-1    |

| case <sup>1)</sup>          |           |        | -    | 27.0     | K/W  | PG-TSSOP-28-1  |

|                             |           |        | -    | 20.2     | K/W  | PG-TSSOP-28-12 |

| Thermal resistance junction | $R_{TJL}$ | CC     | -    | 30.5     | K/W  | PG-DSO-24-1    |

| lead <sup>1)</sup>          |           |        | -    | 195.3    | K/W  | PG-TSSOP-28-1  |

|                             |           |        | -    | 41       | K/W  | PG-TSSOP-28-12 |

#### Table 24 Thermal Characteristics of the Packages

1) The thermal resistances between the case and the ambient  $(R_{TCA})$ , the lead and the ambient  $(R_{TLA})$  are to be combined with the thermal resistances between the junction and the case  $(R_{TJC})$ , the junction and the lead  $(R_{TJL})$  given above, in order to calculate the total thermal resistance between the junction and the ambient  $(R_{TJA})$ . The thermal resistances between the case and the ambient  $(R_{TLA})$ , the lead and the ambient  $(R_{TLA})$  depend on the external system (PCB, case) characteristics, and are under user responsibility.

The junction temperature can be calculated using the following equation:  $T_J=T_A+R_{TJA} \times P_D$ , where the  $R_{TJA}$  is the total thermal resistance between the junction and the ambient. This total junction ambient resistance  $R_{TJA}$  can be obtained from the upper four partial thermal resistances, by

a) simply adding only the two thermal resistances (junction lead and lead ambient), or

b) by taking all four resistances into account, depending on the precision needed.

### Package and Quality Declaration

Figure 19 PG-TSSOP-28-12 Package Outline