#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | AVR                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 4MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 32                                                                       |

| Program Memory Size        | 16KB (8K × 16)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 512 x 8                                                                  |

| RAM Size                   | 1K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                              |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | 0°C ~ 70°C                                                               |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-TQFP                                                                  |

| Supplier Device Package    | 44-TQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega163l-4ac |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

The ATmega163 provides the following features: 16K bytes of In-System Self-Programmable Flash, 512 bytes EEPROM, 1024 bytes SRAM, 32 general purpose I/O lines, 32 general purpose working registers, three flexible Timer/Counters with compare modes, internal and external interrupts, a byte oriented Two-wire Serial Interface, an 8-channel, 10-bit ADC, a programmable Watchdog Timer with internal Oscillator, a programmable serial UART, an SPI serial port, and four software selectable power saving modes. The Idle mode stops the CPU while allowing the SRAM, Timer/Counters, SPI port, and interrupt system to continue functioning. The Power-down mode saves the register contents but freezes the Oscillator, disabling all other chip functions until the next interrupt or Hardware Reset. In Power-save mode, the asynchronous Timer Oscillator continues to run, allowing the user to maintain a timer base while the rest of the device is sleeping. The ADC Noise Reduction mode stops the CPU and all I/O modules except asynchronous timer and ADC, to minimize switching noise during ADC conversions.

The On-chip ISP Flash can be programmed through an SPI serial interface or a conventional programmer. By installing a Self-Programming Boot Loader, the microcontroller can be updated within the application without any external components. The Boot Program can use any interface to download the application program in the Application Flash memory. By combining an 8-bit CPU with In-System Self-Programmable Flash on a monolithic chip, the Atmel ATmega163 is a powerful microcontroller that provides a highly flexible and cost effective solution to many embedded control applications.

The ATmega163 AVR is supported with a full suite of program and system development tools including: C compilers, macro assemblers, program debugger/simulators, In-Circuit Emulators, and evaluation kits.

#### **Pin Descriptions**

| VCC             | Digital supply voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND             | Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Port A (PA7PA0) | Port A serves as the analog inputs to the A/D Converter.<br>Port A also serves as an 8-bit bi-directional I/O port, if the A/D Converter is not used.<br>Port pins can provide internal pull-up resistors (selected for each bit). The Port A output<br>buffers can sink 20mA and can drive LED displays directly. When pins PA0 to PA7 are<br>used as inputs and are externally pulled low, they will source current if the internal pull-<br>up resistors are activated. The Port A pins are tristated when a reset condition becomes<br>active, even if the clock is not running. |

| Port B (PB7PB0) | Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers can sink 20 mA. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. Port B also serves the functions of various special features of the ATmega83/163 as listed on page 117. The Port B pins are tristated when a reset condition becomes active, even if the clock is not running.                                                                                                       |

| Port C (PC7PC0) | Port C is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port C output buffers can sink 20 mA. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tristated when a reset condition becomes active, even if the clock is not running.                                                                                                                                                                                                               |

| Table 3. Reset and interrupt vectors (Continued) |                    |            |                           |  |  |  |  |  |

|--------------------------------------------------|--------------------|------------|---------------------------|--|--|--|--|--|

| Vector No.                                       | Program<br>Address | Source     | Interrupt Definition      |  |  |  |  |  |

| 13                                               | \$018              | UART, UDRE | UART Data Register Empty  |  |  |  |  |  |

| 14                                               | \$01A              | UART, TXC  | UART, Tx Complete         |  |  |  |  |  |

| 15                                               | \$01C              | ADC        | ADC Conversion Complete   |  |  |  |  |  |

| 16                                               | \$01E              | EE_RDY     | EEPROM Ready              |  |  |  |  |  |

| 17                                               | \$020              | ANA_COMP   | Analog Comparator         |  |  |  |  |  |

| 18                                               | \$022              | тwi        | Two-wire Serial Interface |  |  |  |  |  |

| Table 3. | Reset and | Interrupt | Vectors | (Continued) |

|----------|-----------|-----------|---------|-------------|

|----------|-----------|-----------|---------|-------------|

1. When the BOOTRST Fuse is programmed, the device will jump to the Boot Loader Note: address at reset, see "Boot Loader Support" on page 134.

The most typical and general program setup for the Reset and Interrupt Vector Addresses in ATmega163 is:

| Addres | s Labels | Code | C            | Comments                                  |

|--------|----------|------|--------------|-------------------------------------------|

| \$000  |          | jmp  | RESET ;      | Reset Handler                             |

| \$002  |          | jmp  | EXT_INTO ;   | ; IRQ0 Handler                            |

| \$004  |          | jmp  | EXT_INT1 ;   | ; IRQ1 Handler                            |

| \$006  |          | jmp  | TIM2_COMP ;  | ; Timer2 Compare Handler                  |

| \$008  |          | jmp  | TIM2_OVF ;   | ; Timer2 Overflow Handler                 |

| \$00a  |          | jmp  | TIM1_CAPT ;  | ; Timerl Capture Handler                  |

| \$00c  |          | jmp  | TIM1_COMPA ; | ; Timerl Compare A Handler                |

| \$00e  |          | jmp  | TIM1_COMPB ; | ; Timerl Compare B Handler                |

| \$010  |          | jmp  | TIM1_OVF ;   | ; Timerl Overflow Handler                 |

| \$012  |          | jmp  | TIM0_OVF ;   | Timer0 Overflow Handler                   |

| \$014  |          | jmp  | SPI_STC ;    | SPI Transfer Complete Handler             |

| \$016  |          | jmp  | UART_RXC ;   | UART RX Complete Handler                  |

| \$018  |          | jmp  | UART_DRE ;   | UDR Empty Handler                         |

| \$01a  |          | jmp  | UART_TXC ;   | UART TX Complete Handler                  |

| \$01c  |          | jmp  | ADC ; ADC    | C Conversion Complete Interrupt Handler   |

| \$01e  |          | jmp  | EE_RDY ;     | EEPROM Ready Handler                      |

| \$020  |          | jmp  | ANA_COMP ;   | Analog Comparator Handler                 |

| \$022  |          | jmp  | TWI ; Two    | o-wire Serial Interface Interrupt Handler |

| ;      |          |      |              |                                           |

| \$024  | MAIN:    | ldi  | rl6,high(RAM | IEND) ; Main program start                |

| \$025  |          | out  | SPH,r16 ;    | Set stack pointer to top of RAM           |

| \$026  |          | ldi  | r16,low(RAME | ND)                                       |

| \$027  |          | out  | SPL,r16      |                                           |

|        |          |      |              |                                           |

\_\_\_\_\_

Timer/Counter2 Overflow Interrupt is executed. In up/down PWM mode, this bit is set when Timer/Counter2 changes counting direction at \$00.

#### • Bit 5 – ICF1: Input Capture Flag1

The ICF1 bit is set (one) to Flag an Input Capture Event, indicating that the Timer/Counter1 value has been transferred to the Input Capture Register – ICR1. ICF1 is cleared by hardware when executing the corresponding Interrupt Handling Vector. Alternatively, ICF1 is cleared by writing a logic one to the flag.

#### • Bit 4 – OCF1A: Output Compare Flag 1A

The OCF1A bit is set (one) when a Compare Match occurs between the Timer/Counter1 and the data in OCR1A – Output Compare Register 1A. OCF1A is cleared by hardware when executing the corresponding Interrupt Handling Vector. Alternatively, OCF1A is cleared by writing a logic one to the flag. When the I-bit in SREG, and OCIE1A (Timer/Counter1 Compare Match Interrupt A Enable), and the OCF1A are set (one), the Timer/Counter1A Compare Match Interrupt is executed.

#### • Bit 3 – OCF1B: Output Compare Flag 1B

The OCF1B bit is set (one) when a Compare Match occurs between the Timer/Counter1 and the data in OCR1B – Output Compare Register 1B. OCF1B is cleared by hardware when executing the corresponding Interrupt Handling Vector. Alternatively, OCF1B is cleared by writing a logic one to the flag. When the I-bit in SREG, and OCIE1B (Timer/Counter1 Compare Match Interrupt B Enable), and the OCF1B are set (one), the Timer/Counter1B Compare Match Interrupt is executed.

#### • Bit 2 – TOV1: Timer/Counter1 Overflow Flag

The TOV1 is set (one) when an overflow occurs in Timer/Counter1. TOV1 is cleared by hardware when executing the corresponding Interrupt Handling Vector. Alternatively, TOV1 is cleared by writing a logic one to the flag. When the I-bit in SREG, and TOIE1 (Timer/Counter1 Overflow Interrupt Enable), and TOV1 are set (one), the Timer/Counter1 Overflow Interrupt is executed. In up/down PWM mode, this bit is set when Timer/Counter1 changes counting direction at \$0000.

#### • Bit 1 - Res: Reserved Bit

This bit is a reserved bit in the ATmega163 and the read value is undefined.

#### • Bit 0 – TOV0: Timer/Counter0 Overflow Flag

The bit TOV0 is set (one) when an overflow occurs in Timer/Counter0. TOV0 is cleared by hardware when executing the corresponding Interrupt Handling Vector. Alternatively, TOV0 is cleared by writing a logic one to the flag. When the SREG I-bit, and TOIE0 (Timer/Counter0 Overflow Interrupt Enable), and TOV0 are set (one), the Timer/Counter0 Overflow interrupt is executed.

#### **External Interrupts**

The external interrupts are triggered by the INT0 and INT1 pins. Observe that, if enabled, the interrupts will trigger even if the INT0/INT1 pins are configured as outputs. This feature provides a way of generating a software interrupt. The external interrupts can be triggered by a falling or rising edge or a low level. This is set up as indicated in the specification for the MCU Control Register – MCUCR. When the external interrupt is enabled and is configured as level triggered, the interrupt will trigger as long as the pin is held low.

set), the 9th bit is one for an address byte and zero for a data byte, whereas the stop bit is always high.

The following procedure should be used to exchange data in Multi-Processor Communication mode:

- All Slave MCUs are in Multi-Processor Communication mode (MPCM in UCSRA is set).

- 2. The Master MCU sends an address byte, and all slaves receive and read this byte. In the Slave MCUs, the RXC Flag in UCSRA will be set as normal.

- 3. Each Slave MCU reads the UDR Register and determines if it has been selected. If so, it clears the MPCM bit in UCSRA, otherwise it waits for the next address byte.

- 4. For each received data byte, the receiving MCU will set the Receive Complete Flag (RXC in UCSRA). In 8-bit mode, the receiving MCU will also generate a Framing Error (FE in UCSRA set), since the stop bit is zero. The other slave MCUs, which still have the MPCM bit set, will ignore the data byte. In this case, the UDR Register and the RXC or FE Flags will not be affected.

- 5. After the last byte has been transferred, the process repeats from step 2.

#### UART Control

#### UART I/O Data Register – UDR

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   | _   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| \$0C (\$2C)   | MSB |     |     |     |     |     |     | LSB | UDR |

| Read/Write    | R/W | -   |

| Initial Value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |     |

The UDR Register is actually two physically separate registers sharing the same I/O address. When writing to the register, the UART Transmit Data Register is written. When reading from UDR, the UART Receive Data Register is read.

#### UART Control and Status Register A – UCSRA

| Bit           | 7   | 6   | 5    | 4  | 3  | 2 | 1   | 0    | _     |

|---------------|-----|-----|------|----|----|---|-----|------|-------|

| \$0B (\$2B)   | RXC | TXC | UDRE | FE | OR | - | U2X | MPCM | UCSRA |

| Read/Write    | r   | R/W | R    | R  | R  | R | R/W | R/W  | •     |

| Initial Value | 0   | 0   | 0    | 0  | 0  | 0 | 0   | 0    |       |

#### • Bit 7 – RXC: UART Receive Complete

This bit is set (one) when a received character is transferred from the Receiver Shift Register to UDR. The bit is set regardless of any detected framing errors. When the RXCIE bit in UCR is set, the UART Receive Complete interrupt will be executed when RXC is set(one). RXC is cleared by reading UDR. When interrupt-driven data reception is used, the UART Receive Complete Interrupt routine must read UDR in order to clear RXC, otherwise a new interrupt will occur once the interrupt routine terminates.

#### • Bit 6 – TXC: UART Transmit Complete

This bit is set (one) when the entire character (including the stop bit) in the Transmit Shift Register has been shifted out and no new data has been written to UDR. This Flag is especially useful in half-duplex communications interfaces, where a transmitting application must enter receive mode and free the communications bus immediately after completing the transmission. number of samples are reduced, and the system clock might have some variance (this applies especially when using resonators), it is recommended that the baud rate error is less than 0.5%.

| 1.0000 MHz      | % Error | 1.8432 MHz      | % Error | 2.0000 MHz       | % Error |

|-----------------|---------|-----------------|---------|------------------|---------|

| UBR = <b>51</b> | 0.2     | UBR = <b>95</b> | 0.0     | UBR = <b>103</b> | 0.2     |

| UBR = <b>25</b> | 0.2     | UBR = <b>47</b> | 0.0     | UBR = <b>51</b>  | 0.2     |

| UBR = <b>12</b> | 0.2     | UBR = <b>23</b> | 0.0     | UBR = <b>25</b>  | 0.2     |

| UBR = 8         | 3.7     | UBR = <b>15</b> | 0.0     | UBR = 16         | 2.1     |

| UBR = 6         | 7.5     | UBR = <b>11</b> | 0.0     | UBR = <b>12</b>  | 0.2     |

| UBR = 3         | 7.8     | UBR = <b>7</b>  | 0.0     | UBR = 8          | 3.7     |

| UBR = 2         | 7.8     | UBR = <b>5</b>  | 0.0     | UBR = 6          | 7.5     |

| UBR = 1         | 7.8     | UBR = <b>3</b>  | 0.0     | UBR = 3          | 7.8     |

| UBR = 1         | 22.9    | UBR = <b>2</b>  | 0.0     | UBR = 2          | 7.8     |

| UBR = 0         | 84.3    | UBR = 1         | 0.0     | UBR = 1          | 7.8     |

| -               | -       | UBR = <b>0</b>  | 0.0     | -                | -       |

| Table 28. | UBR Settings at | Various Crysta | al Frequencies i | n Double Speed Mode |

|-----------|-----------------|----------------|------------------|---------------------|

|           |                 |                |                  |                     |

| 3.2768 MHz       | % Error | 3.6864 MHz       | % Error | 4.0000 MHz       | % Error |

|------------------|---------|------------------|---------|------------------|---------|

| UBR = <b>170</b> | 0.2     | UBR = <b>191</b> | 0.0     | UBR = <b>207</b> | 0.2     |

| UBR = <b>84</b>  | 0.4     | UBR = <b>95</b>  | 0.0     | UBR = <b>103</b> | 0.2     |

| UBR = <b>42</b>  | 0.8     | UBR = <b>47</b>  | 0.0     | UBR = <b>51</b>  | 0.2     |

| UBR = 27         | 1.6     | UBR = <b>31</b>  | 0.0     | UBR = <b>34</b>  | 0.8     |

| UBR = 20         | 1.6     | UBR = <b>23</b>  | 0.0     | UBR = <b>25</b>  | 0.2     |

| UBR = 13         | 1.6     | UBR = <b>15</b>  | 0.0     | UBR = 16         | 2.1     |

| UBR = 10         | 3.1     | UBR = 11         | 0.0     | UBR = <b>12</b>  | 0.2     |

| UBR = 6          | 1.6     | UBR = <b>7</b>   | 0.0     | UBR = 8          | 3.7     |

| UBR = 4          | 6.2     | UBR = <b>5</b>   | 0.0     | UBR = 6          | 7.5     |

| UBR = 3          | 12.5    | UBR = <b>3</b>   | 0.0     | UBR = 3          | 7.8     |

| UBR = 1          | 12.5    | UBR = 1          | 0.0     | UBR = 1          | 7.8     |

| UBR = 0          | 12.5    | UBR = <b>0</b>   | 0.0     | UBR = 0          | 7.8     |

| 7.3728 MHz       | % Error | 8.0000 MHz       | % Error |

|------------------|---------|------------------|---------|

| UBR = <b>383</b> | 0.0     | UBR = <b>416</b> | 0.1     |

| UBR = <b>191</b> | 0.0     | UBR = <b>207</b> | 0.2     |

| UBR = <b>95</b>  | 0.0     | UBR = <b>103</b> | 0.2     |

| UBR = <b>63</b>  | 0.0     | UBR = <b>68</b>  | 0.6     |

| UBR = <b>47</b>  | 0.0     | UBR = <b>51</b>  | 0.2     |

| UBR = <b>31</b>  | 0.0     | UBR = <b>34</b>  | 0.8     |

| UBR = <b>23</b>  | 0.0     | UBR = <b>25</b>  | 0.2     |

| UBR = 15         | 0.0     | UBR = 16         | 2.1     |

| UBR = 11         | 0.0     | UBR = 12         | 0.2     |

| UBR = <b>7</b>   | 0.0     | UBR = 8          | 3.7     |

| UBR = <b>3</b>   | 0.0     | UBR = 3          | 7.8     |

| UBR = <b>1</b>   | 0.0     | UBR = 1          | 7.8     |

| UBR = <b>0</b>   | 0.0     | UBR = 0          | 7.8     |

### Two-wire Serial Interface (Byte Oriented)

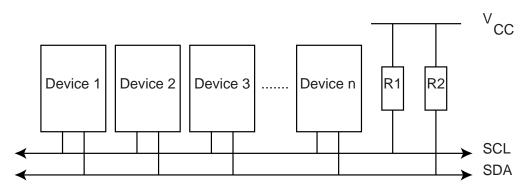

The Two-wire Serial Interface supports bi-directional serial communication. It is designed primarily for simple but efficient integrated circuit (IC) control. The system is comprised of two lines, SCL (Serial Clock) and SDA (Serial Data) that carry information between the ICs connected to them. Various communication configurations can be designed using this bus. Figure 49 shows a typical Two-wire Serial Bus configuration. Any device connected to the bus can be master or slave. Note that all AVR devices connected to the bus must be powered to allow any bus operation.

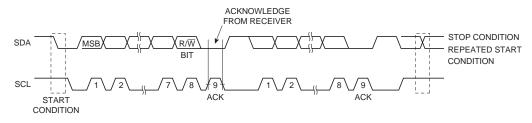

The Two-wire Serial Interface supports Master/Slave and Transmitter/Receiver operation at up to 217 kHz bus clock rate. The Two-wire Serial Interface has hardware support for 7-bit addressing, but is easily extended to, e.g., a 10-bit addressing format in software. When the Two-wire Serial Interface is enabled (TWEN in TWCR is set), a glitch filter is enabled for the input signals from the pins PC0 (SCL) and PC1 (SDA), and the output from these pins is slew-rate controlled. The Two-wire Serial Interface is byte oriented. The operation of the Two-wire Serial Bus is shown as a pulse diagram in Figure 50, including the START and STOP conditions and generation of ACK signal by the bus receiver.

#### Figure 50. Two-wire Serial Bus Timing Diagram

The block diagram of the Two-wire Serial Interface is shown in Figure 51.

#### • Bit 0 – TWIE: Two-wire Serial Interface Interrupt Enable

When this bit is enabled, and the I-bit in SREG is set, the Two-wire Serial Interface interrupt will be activated for as long as the TWINT Flag is high.

The TWCR is used to control the operation of the Two-wire Serial Interface. It is used to enable the Two-wire Serial Interface, to initiate a Master access by applying a START condition to the bus, to generate a receiver acknowledge, to generate a stop condition, and to control halting of the bus while the data to be written to the bus are written to the TWDR. It also indicates a write collision if data is attempted written to TWDR while the register is inaccessible.

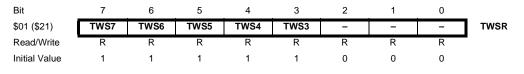

#### The Two-wire Serial Interface Status Register – TWSR

#### • Bits 7..3 – TWS: Two-wire Serial Interface Status

These five bits reflect the status of the Two-wire Serial Interface logic and the Two-wire Serial Bus.

#### • Bits 2..0 - Res: Reserved bits

These bits are reserved in ATmega163 and will always read as zero

The TWSR is read only. It contains a status code which reflects the status of the Twowire Serial Interface logic and the Two-wire Serial Bus. There are 26 possible status codes. When TWSR contains \$F8, no relevant state information is available and no Two-wire Serial Interface interrupt is requested. A valid status code is available in TWSR one CPU clock cycle after the Two-wire Serial Interface Interrupt Flag (TWINT) is set by hardware and is valid until one CPU clock cycle after TWINT is cleared by software. Table 32 to Table 36 give the status information for the various modes.

#### The Two-wire Serial Interface Data Register – TWDR

| Bit           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    | _    |

|---------------|------|------|------|------|------|------|------|------|------|

| \$03 (\$23)   | TWD7 | TWD6 | TWD5 | TWD4 | TWD3 | TWD2 | TWD1 | TWD0 | TWDR |

| Read/Write    | R/W  | 1    |

| Initial Value | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |      |

#### • Bits 7..0 – TWD: Two-wire Serial Interface Data Register

These eight bits constitute the next data byte to be transmitted, or the latest data byte received on the Two-wire Serial Bus.

In Transmit mode, TWDR contains the next byte to be transmitted. In Receive mode, the TWDR contains the last byte received. It is writeable while the Two-wire Serial Interface is not in the process of shifting a byte. This occurs when the Two-wire Serial Interface Interrupt Flag (TWINT) is set by hardware. Note that the Data Register cannot be initialized by the user before the first interrupt occurs. The data in TWDR remain stable as long as TWINT is set. While data is shifted out, data on the bus is simultaneously shifted in. TWDR always contains the last byte present on the bus, except after a wake up from ADC Noise Reduction mode, Power-down mode, or Power-save mode by the Two-wire Serial Interface interrupt. For example, in the case of a lost bus arbitration, no data is lost in the transition from Master to Slave. Handling of the ACK Flag is controlled automatically by the Two-wire Serial Interface logic, the CPU cannot access the ACK bit directly.

;Part specific include file and TWI include file must be included. ; <Initialize registers TWAR and TWBR> ldi r16, (1<<TWINT) | (1<<TWSTA) | (1<<TWEN) TWCR, r16 ;Send START condition out wait5:in r16,TWCR ; Wait for TWINT flag set. This indicates that r16, TWINT ; the START condition has been transmitted sbrs rjmp wait5 in r16, TWSR ; Check value of TWI Status Register. If status r16, START ; different from START, go to ERROR cpi brne ERROR ldi r16, 0xc9 ; Load SLA+R into TWDR Register TWDR, r16 out. r16, (1<<TWINT) | (1<<TWEN) 1di TWCR, r16 ; Clear TWINT bit in TWCR to start transmission of out ; SLA+R wait6:in r16,TWCR ; Wait for TWINT flag set. This indicates that ; SLA+R has been transmitted, and ACK/NACK has sbrs r16, TWINT wait6 ; been received rjmp in r16, TWSR ; Check value of TWI Status Register. If status r16, MR\_SLA\_ACK; different from MR\_SLA\_ACK, go to ERROR cpi ERROR brne r16, (1<<TWINT) | (1<<TWEA) | (1<<TWEN) ldi TWCR, r16 ; Clear TWINT bit in TWCR to start reception of out ; data. ; Setting TWEA causes ACK to be returned after ; reception of data byte wait7:in r16,TWCR ; Wait for TWINT flag set. This indicates that sbrs r16, TWINT ; data has been received and ACK returned wait7 rjmp r16, TWSR ; Check value of TWI Status Register. If status in cpi r16, MR\_DATA\_ACK ; different from MR\_DATA\_ACK, go to ERROR ERROR brne r16, TWDR ; Input received data from TWDR. in ;<do something with received data> nop r16, (1<<TWINT) | (1<<TWEA) | (1<<TWEN) ldi TWCR, r16 ; Clear TWINT bit in TWCR to start reception of out ; data. Setting TWEA causes ACK to be returned ; after reception of data byte ;<Receive more data bytes if needed>

;receive next to last data byte.

wait8:in r16,TWCR ; Wait for TWINT flag set. This indicates that

Assembly Code Example –

**Master Receiver Mode**

| mei   |

|-------|

| IIIEL |

|       |

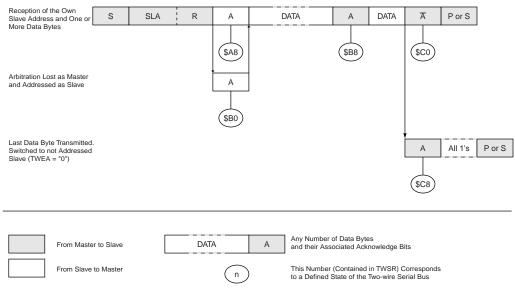

| Table 35. | Status | Codes | for | Slave | Transmitter | Mode |

|-----------|--------|-------|-----|-------|-------------|------|

|-----------|--------|-------|-----|-------|-------------|------|

|             |                                                                                                 | Applicat                                                                      | ion Softv   | vare Res    | ponse            |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------|-------------|------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Status Code | Status of the Two-wire Serial Bus<br>and Two-wire Serial Interface                              |                                                                               | To TV       | /CR         |                  |                  | Next Action Taken by Two-wire Serial Interface Hard-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| (TWSR)      | hardware                                                                                        | To/from TWDR                                                                  | STA         | STO         | TWINT            | TWEA             | ware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| \$A8        | Own SLA+R has been received;<br>ACK has been returned                                           | Load data byte or<br>Load data byte                                           | x<br>x      | 0<br>0      | 1<br>1           | 0<br>1           | Last data byte will be transmitted and NOT ACK should<br>be received<br>Data byte will be transmitted and ACK should be re-<br>ceived                                                                                                                                                                                                                                                                                                                                                                                                                  |

| \$B0        | Arbitration lost in SLA+R/W as<br>master; own SLA+R has been<br>received; ACK has been returned | Load data byte or<br>Load data byte                                           | x<br>x      | 0           | 1                | 0                | Last data byte will be transmitted and NOT ACK should<br>be received<br>Data byte will be transmitted and ACK should be re-<br>ceived                                                                                                                                                                                                                                                                                                                                                                                                                  |

| \$B8        | Data byte in TWDR has been<br>transmitted; ACK has been<br>received                             | Load data byte or<br>Load data byte                                           | x<br>x      | 0<br>0      | 1<br>1           | 0<br>1           | Last data byte will be transmitted and NOT ACK should<br>be received<br>Data byte will be transmitted and ACK should be re-<br>ceived                                                                                                                                                                                                                                                                                                                                                                                                                  |

| \$C0        | Data byte in TWDR has been<br>transmitted; NOT ACK has been<br>received                         | No TWDR action or<br>No TWDR action or<br>No TWDR action or<br>No TWDR action | 0 0 1 1     | 0<br>0<br>0 | 1<br>1<br>1<br>1 | 0<br>1<br>0<br>1 | Switched to the not addressed Slave mode;<br>no recognition of own SLA or GCA<br>Switched to the not addressed Slave mode;<br>own SLA will be recognized;<br>GCA will be recognized if TWGCE = "1"<br>Switched to the not addressed Slave mode;<br>no recognition of own SLA or GCA;<br>a START condition will be transmitted when the bus<br>becomes free<br>Switched to the not addressed Slave mode;<br>own SLA will be recognized;<br>GCA will be recognized if TWGCE = "1";<br>a START condition will be transmitted when the bus<br>becomes free |

| \$C8        | Last data byte in TWDR has been<br>transmitted (TWEA = "0"); ACK<br>has been received           | No TWDR action or<br>No TWDR action or<br>No TWDR action or<br>No TWDR action | 0<br>0<br>1 | 0<br>0<br>0 | 1<br>1<br>1<br>1 | 0<br>1<br>0<br>1 | Switched to the not addressed Slave mode;<br>no recognition of own SLA or GCA<br>Switched to the not addressed Slave mode;<br>own SLA will be recognized;<br>GCA will be recognized if TWGCE = "1"<br>Switched to the not addressed slave mode;<br>no recognition of own SLA or GCA;<br>a START condition will be transmitted when the bus<br>becomes free<br>Switched to the not addressed Slave mode;<br>own SLA will be recognized;<br>GCA will be recognized;<br>a START condition will be transmitted when the bus<br>becomes free                |

#### Figure 55. Formats and States in the Slave Transmitter Mode

| ; be received after data byte Master signalling en                            | ıd |

|-------------------------------------------------------------------------------|----|

| ; of transmission)                                                            |    |

| wait17:in r16,TWCR ; Wait for TWINT flag set. This indicates that             |    |

| sbrs r16, TWINT ; data has been transmitted, and ACK/NACK has                 |    |

| rjmp wait17 ; been received                                                   |    |

|                                                                               |    |

| in r16, TWSR ; Check value of TWI Status Register. If status                  |    |

| cpi r16, ST_LAST_DATA ; different from ST_LAST_DATA, go to ERROR              |    |

| brne ERROR                                                                    |    |

|                                                                               |    |

| ldi r16, (1< <twint) (1<<twea)="" (1<<twen)<="" td=""  =""><td></td></twint)> |    |

| out TWCR, r16 ; Continue address reckognition in Slave                        |    |

| Transmitter mode                                                              |    |

#### Table 36. Status Codes for Miscellaneous States

| o                     |                                                                 | Applica        | tion Softw       | are Resp | onse    |           |                    |                                                                                                                                       |  |  |

|-----------------------|-----------------------------------------------------------------|----------------|------------------|----------|---------|-----------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Status Code<br>(TWSR) | Status of the Two-wire Serial<br>Bus and Two-wire Serial Inter- | To/from T      | WDR              | To TWCR  |         |           |                    | Next Action Taken by Two-wire Serial Interface Hard                                                                                   |  |  |

|                       | face hardware                                                   |                |                  | STA      | STO     | TWINT     | TWEA               | ware                                                                                                                                  |  |  |

| \$F8                  | No relevant state information available; TWINT = "0"            | No TWDF        | R action         |          | No TW   | CR action |                    | Wait or proceed current transfer                                                                                                      |  |  |

| \$00                  | Bus error due to an illegal START or STOP condition             |                | R action         | 0        | 1       | 1         | х                  | Only the internal hardware is affected, no STOP condition is sent on the bus. In all cases, the bus is released and TWSTO is cleared. |  |  |

| WI Include            | e File                                                          | ;****          | General          | Maste    | r stau  | s codes   | 5 ****             |                                                                                                                                       |  |  |

|                       |                                                                 | .equ<br>transm | START<br>itted   |          |         | =\$08     |                    | ;START has been                                                                                                                       |  |  |

|                       |                                                                 | .equ<br>transm | REP_ST.<br>itted | ART      |         | =\$10     |                    | ;Repeated START has been                                                                                                              |  |  |

|                       |                                                                 | ;****          | Master           | Transm   | itter   | staus c   | codes *            | ****                                                                                                                                  |  |  |

|                       |                                                                 | .equ           | MT_SLA           | _ACK     | =\$18   | 3 ;SI     | LA+W ha            | s been tramsmitted and ACK received                                                                                                   |  |  |

|                       |                                                                 | .equ           | MT_SLA           | _NACK    | =\$20   | ) ;SI     | LA+W ha            | s been tramsmitted and NACK received                                                                                                  |  |  |

|                       |                                                                 | .equ           | MT_DAT.          | A_ACK    | =\$28   |           | ata byt<br>eceived | e has been tramsmitted and ACK<br>N                                                                                                   |  |  |

|                       |                                                                 | .equ<br>receiv | MT_DAT.<br>ed    | A_NACK   | =\$30   | ) ;Da     | ata byt            | e has been tramsmitted and NACK                                                                                                       |  |  |

|                       |                                                                 | .equ           | MT_ARB           | _LOST    | =\$38   | 3 ;A1     | rbitrat            | ion lost in SLA+W or data bytes                                                                                                       |  |  |

|                       |                                                                 | ;****          | Master           | Receiv   | er sta  | us code   | es ****            | *                                                                                                                                     |  |  |

|                       |                                                                 | .equ           | MR_ARB           | _LOST    | =\$38   | 3 ;Ar     | rbitrat            | ion lost in SLA+R or NACK bit                                                                                                         |  |  |

|                       |                                                                 | .equ           | MR_SLA           | _ACK     | =\$40   | ) ;SI     | LA+R ha            | s been tramsmitted and ACK received                                                                                                   |  |  |

|                       |                                                                 | .equ           | MR_SLA           | _NACK    | =\$48   | 3 ;SI     | LA+R ha            | s been tramsmitted and NACK received                                                                                                  |  |  |

|                       |                                                                 | .equ           | MR_DAT           | A_ACK    | =\$50   | ) ;Da     | ata byt            | e has been received and ACK returned                                                                                                  |  |  |

|                       |                                                                 | .equ           | MR_DAT.          | A_NACK   | =\$58   |           | ata byt<br>ramsmi  | e has been received and NACK<br>tted                                                                                                  |  |  |

|                       |                                                                 | ;****          | Slave 1          | Fransmi  | tter s  | taus co   | odes **            | * * *                                                                                                                                 |  |  |

|                       |                                                                 | .equ           | ST_SLA           | _ACK     | =\$A8   | 3 ; Ov    | vn SLA+            | R has been received and ACK returned                                                                                                  |  |  |

|                       |                                                                 | .equ           | ST_ARB           | _LOST_S  | SLA_ACI |           |                    | tion lost in SLA+R/W as Master. Own<br>as been received and ACK returned                                                              |  |  |

|                       |                                                                 | .equ           | ST_DAT           | A_ACK    | =\$B8   |           | ata byt            | e has been tramsmitted and ACK                                                                                                        |  |  |

;received

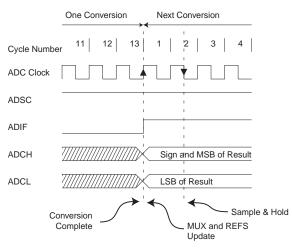

#### Table 39. ADC Conversion Time

| Condition           | Sample & Hold (Cycles<br>from Start of<br>Conversion) | Conversion Time<br>(Cycles) | Conversion Time<br>(μs) |

|---------------------|-------------------------------------------------------|-----------------------------|-------------------------|

| Extended Conversion | 13.5                                                  | 25                          | 125 - 500               |

| Normal Conversions  | 1.5                                                   | 13                          | 65 - 260                |

# ADC Noise Canceler Function

The ADC features a Noise Canceler that enables conversion during ADC Noise Reduction mode (see "Sleep Modes" on page 35) to reduce noise induced from the CPU core and other I/O peripherals. If other I/O peripherals must be active during conversion, this mode works equivalently for Idle mode. To make use of this feature, the following procedure should be used:

- Make sure that the ADC is enabled and is not busy converting. Single Conversion Mode must be selected and the ADC conversion complete interrupt must be enabled.

- ADEN = 1

- ADSC = 0

- ADFR = 0

- ADIE = 1

- 2. Enter ADC Noise Reduction mode (or Idle mode). The ADC will start a conversion once the CPU has been halted.

- 3. If no other interrupts occur before the ADC conversion completes, the ADC interrupt will wake up the CPU and execute the ADC Conversion Complete interrupt routine.

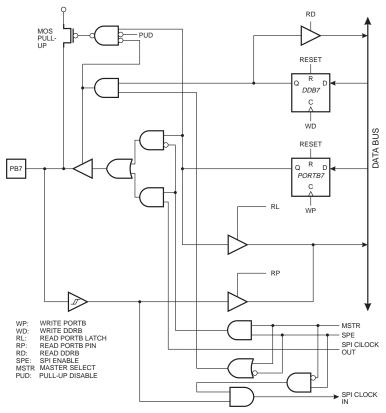

#### Port B As General Digital I/O

All eight bits in Port B are equal when used as digital I/O pins. PBn, General I/O pin: The DDBn bit in the DDRB Register selects the direction of this pin, if DDBn is set (one), PBn is configured as an output pin. If DDBn is cleared (zero), PBn is configured as an input pin. If PORTBn is set (one) when the pin configured as an input pin, the MOS pull up resistor is activated. To switch the pull up resistor off, the PORTBn has to be cleared (zero), the pin has to be configured as an output pin, or the PUD bit has to be set. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running.

| DDBn | PORTBn | PUD | I/O    | Pull Up | Comment                                     |

|------|--------|-----|--------|---------|---------------------------------------------|

| 0    | 0      | х   | Input  | No      | Tri-state (Hi-Z)                            |

| 0    | 1      | 1   | Input  | No      | Tri-state (Hi-Z)                            |

| 0    | 1      | 0   | Input  | Yes     | PBn will source current if ext. pulled low. |

| 1    | 0      | x   | Output | No      | Push-pull Zero Output                       |

| 1    | 1      | х   | Output | No      | Push-pull One Output                        |

| Table 46. | DDBn | Effects | on | Port B | Pins <sup>(1)</sup> |

|-----------|------|---------|----|--------|---------------------|

|           |      |         |    |        | 1 1110              |

Note: 1. n: 7,6...0, pin number.

The alternate pin configuration is as follows:

#### • SCK – PORTB, Bit 7

SCK: Master Clock output, Slave Clock input pin for SPI channel. When the SPI is enabled as a Slave, this pin is configured as an input regardless of the setting of DDB7. When the SPI is enabled as a Master, the data direction of this pin is controlled by DDB7. When the pin is forced to be an input, the pull-up can still be controlled by the PORTB7 bit. See the description of the SPI port for further details.

#### • MISO – PORTB, Bit 6

MISO: Master Data input, Slave Data output pin for SPI channel. When the SPI is enabled as a Master, this pin is configured as an input regardless of the setting of DDB6. When the SPI is enabled as a Slave, the data direction of this pin is controlled by DDB6. When the pin is forced to be an input, the pull-up can still be controlled by the PORTB6 bit. See the description of the SPI port for further details.

#### • MOSI – PORTB, Bit 5

MOSI: SPI Master Data output, Slave Data input for SPI channel. When the SPI is enabled as a Slave, this pin is configured as an input regardless of the setting of DDB5. When the SPI is enabled as a Master, the data direction of this pin is controlled by DDB5. When the pin is forced to be an input, the pull-up can still be controlled by the PORTB5 bit. See the description of the SPI port for further details.

#### • SS – PORTB, Bit 4

SS: Slave Port Select input. When the SPI is enabled as a Slave, this pin is configured as an input regardless of the setting of DDB4. As a slave, the SPI is activated when this pin is driven low. When the SPI is enabled as a Master, the data direction of this pin is controlled by DDB4. When the pin is forced to be an input, the pull-up can still be controlled by the PORTB4 bit. See the description of the SPI port for further details.

## Alternate Functions Of PORTB

Figure 69. PORTB Schematic Diagram (Pin PB7)

#### Port D

Port D is an 8 bit bi-directional I/O port with internal pull-up resistors.

Three I/O memory address locations are allocated for Port D, one each for the Data Register – PORTD, \$12(\$32), Data Direction Register – DDRD, \$11(\$31) and the Port D Input Pins – PIND, \$10(\$30). The Port D Input Pins address is read only, while the Data Register and the Data Direction Register are read/write.

The Port D output buffers can sink 20 mA. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. Some Port D pins have alternate functions as shown in Table 49.

| Port Pin | Alternate Function                                 |

|----------|----------------------------------------------------|

| PD0      | RXD (UART Input Pin)                               |

| PD1      | TXD (UART Output Pin)                              |

| PD2      | INT0 (External Interrupt 0 Input)                  |

| PD3      | INT1 (External Interrupt 1 Input)                  |

| PD4      | OC1B (Timer/Counter1 Output CompareB Match Output) |

| PD5      | OC1A (Timer/Counter1 Output CompareA Match Output) |

| PD6      | ICP (Timer/Counter1 Input Capture Pin)             |

| PD7      | OC2 (Timer/Counter2 Output Compare Match Output)   |

Table 49. Port D Pins Alternate Functions

| The Port D Data Register –    |               |        |        |        |        |        |        |        |        |       |

|-------------------------------|---------------|--------|--------|--------|--------|--------|--------|--------|--------|-------|

| PORTD                         | Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      | -     |

|                               | \$12 (\$32)   | PORTD7 | PORTD6 | PORTD5 | PORTD4 | PORTD3 | PORTD2 | PORTD1 | PORTD0 | PORTD |

|                               | Read/Write    | R/W    | I     |

|                               | Initial Value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |       |

| The Port D Data Direction     |               |        |        |        |        |        |        |        |        |       |

| Register – DDRD               | Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|                               | \$11 (\$31)   | DDD7   | DDD6   | DDD5   | DDD4   | DDD3   | DDD2   | DDD1   | DDD0   | DDRD  |

|                               | Read/Write    | R/W    | 1     |

|                               | Initial Value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |       |

| The Port D Input Pins Address |               |        |        |        |        |        |        |        |        |       |

| – PIND                        | Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|                               | \$10 (\$30)   | PIND7  | PIND6  | PIND5  | PIND4  | PIND3  | PIND2  | PIND1  | PIND0  | PIND  |

|                               | Read/Write    | R      | R      | R      | R      | R      | R      | R      | R      | 1     |

|                               | Initial Value | N/A    |       |

|                               |               |        |        | _      |        |        |        |        |        |       |

The Port D Input Pins Address – PIND – is not a register, and this address enables access to the physical value on each Port D pin. When reading PORTD, the PORTD Data Latch is read, and when reading PIND, the logical values present on the pins are read.

Reading the Signature Bytes

The algorithm for reading the Signature bytes is as follows (refer to Programming the Flash for details on Command and Address loading):

- 1. A: Load Command "0000 1000".

- 2. C: Load Address Low Byte (\$00 \$02).

- 3. Set OE to "0", and BS to "0". The selected Signature byte can now be read at DATA.

- 4. Set OE to "1".

**Reading the Calibration Byte** The algorithm for reading the Calibration byte is as follows (refer to Programming the Flash for details on Command and Address loading):

- 1. A: Load Command "0000 1000".

- 2. C: Load Address Low Byte, \$00.

Set OE to "0", and BS1 to "1". The Calibaration byte can now be read at DATA.

3. Set OE to "1".

## Instruction Set Summary

| Mnemonics                            | Operands         | Description                                                                                | Operation                                                                                | Flags        | #Clocks    |

|--------------------------------------|------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------|------------|

| ARITHMETIC AN                        | D LOGIC INSTRUC  | TIONS                                                                                      |                                                                                          |              |            |

| ADD                                  | Rd, Rr           | Add two Registers                                                                          | $Rd \leftarrow Rd + Rr$                                                                  | Z,C,N,V,H    | 1          |

| ADC                                  | Rd, Rr           | Add with Carry two Registers                                                               | $Rd \leftarrow Rd + Rr + C$                                                              | Z,C,N,V,H    | 1          |

| ADIW                                 | Rdl,K            | Add Immediate to Word                                                                      | $Rdh:Rdl \leftarrow Rdh:Rdl + K$                                                         | Z,C,N,V,S    | 2          |

| SUB                                  | Rd, Rr           | Subtract two Registers                                                                     | $Rd \leftarrow Rd - Rr$                                                                  | Z,C,N,V,H    | 1          |

| SUBI                                 | Rd, K            | Subtract Constant from Register                                                            | $Rd \leftarrow Rd - K$                                                                   | Z,C,N,V,H    | 1          |

| SBC                                  | Rd, Rr           | Subtract with Carry two Registers                                                          | $Rd \leftarrow Rd - Rr - C$                                                              | Z,C,N,V,H    | 1          |

| SBCI                                 | Rd, K            | Subtract with Carry Constant from Reg.                                                     | $Rd \leftarrow Rd - K - C$                                                               | Z,C,N,V,H    | 1          |

| SBIW                                 | Rdl,K            | Subtract Immediate from Word                                                               | Rdh:Rdl ← Rdh:Rdl - K                                                                    | Z,C,N,V,S    | 2          |

| AND                                  | Rd, Rr           | Logical AND Registers                                                                      | $Rd \leftarrow Rd \bullet Rr$                                                            | Z,N,V        | 1          |

| ANDI                                 | Rd, K            | Logical AND Register and Constant                                                          | $Rd \gets Rd \bullet K$                                                                  | Z,N,V        | 1          |

| OR                                   | Rd, Rr           | Logical OR Registers                                                                       | $Rd \leftarrow Rd \lor Rr$                                                               | Z,N,V        | 1          |

| ORI                                  | Rd, K            | Logical OR Register and Constant                                                           | $Rd \leftarrow Rd \lor K$                                                                | Z,N,V        | 1          |

| EOR                                  | Rd, Rr           | Exclusive OR Registers                                                                     | $Rd \leftarrow Rd \oplus Rr$                                                             | Z,N,V        | 1          |

| COM                                  | Rd               | One's Complement                                                                           | $Rd \leftarrow \$FF - Rd$                                                                | Z,C,N,V      | 1          |

| NEG                                  | Rd               | Two's Complement                                                                           | Rd ← \$00 – Rd                                                                           | Z,C,N,V,H    | 1          |

| SBR                                  | Rd,K             | Set Bit(s) in Register                                                                     | $Rd \leftarrow Rd \lor K$                                                                | Z,N,V        | 1          |

| CBR                                  | Rd,K             | Clear Bit(s) in Register                                                                   | $Rd \leftarrow Rd \bullet (\$FF - K)$                                                    | Z,N,V        | 1          |

| INC                                  | Rd               | Increment                                                                                  | $Rd \leftarrow Rd + 1$                                                                   | Z,N,V        | 1          |

| DEC                                  | Rd               | Decrement                                                                                  | $Rd \leftarrow Rd - 1$                                                                   | Z,N,V        | 1          |

| TST                                  | Rd               | Test for Zero or Minus                                                                     | $Rd \leftarrow Rd \bullet Rd$                                                            | Z,N,V        | 1          |

| CLR                                  | Rd               | Clear Register                                                                             | $Rd \leftarrow Rd \oplus Rd$                                                             | Z,N,V        | 1          |

| SER                                  | Rd               | Set Register                                                                               | $Rd \leftarrow \$FF$                                                                     | None         | 1          |

| MUL                                  | Rd, Rr           | Multiply Unsigned                                                                          | $R1:R0 \leftarrow Rd \times Rr$                                                          | Z,C          | 2          |

| MULS                                 | Rd, Rr           | Multiply Signed                                                                            | $R1:R0 \leftarrow Rd x Rr$                                                               | Z,C          | 2          |

| MULSU                                | Rd, Rr           | Multiply Signed with Unsigned                                                              | $R1:R0 \leftarrow Rd \times Rr$                                                          | Z,C          | 2          |

| FMUL                                 | Rd, Rr           | Fractional Multiply Unsigned                                                               | $R1:R0 \leftarrow (Rd x Rr) << 1$                                                        | Z,C          | 2          |

| FMULS                                | Rd, Rr           | Fractional Multiply Signed                                                                 | $R1:R0 \leftarrow (Rd \times Rr) << 1$                                                   | Z,C          | 2          |

| FMULSU                               | Rd, Rr           | Fractional Multiply Signed with Unsigned                                                   | $R1:R0 \leftarrow (Rd \times Rr) << 1$                                                   | Z,C          | 2          |

| BRANCH INSTRU                        |                  | Tractional multiply bighed with onsighed                                                   |                                                                                          | 2,0          |            |

| RJMP                                 | k                | Relative Jump                                                                              | $PC \leftarrow PC + k + 1$                                                               | None         | 2          |

| IJMP                                 | ĸ                | Indirect Jump to (Z)                                                                       | $PC \leftarrow Z$                                                                        | None         | 2          |

| JMP                                  | k                | Direct Jump                                                                                | $PC \leftarrow k$                                                                        | None         | 3          |

| RCALL                                | k                | Relative Subroutine Call                                                                   | $PC \leftarrow K$<br>$PC \leftarrow PC + k + 1$                                          | None         | 3          |

| ICALL                                | ĸ                | Indirect Call to (Z)                                                                       | $PC \leftarrow PC + R + 1$<br>$PC \leftarrow Z$                                          | None         | 3          |

| CALL                                 | k                |                                                                                            | $PC \leftarrow Z$                                                                        |              | 4          |

| RET                                  | ĸ                | Direct Subroutine Call                                                                     | $PC \leftarrow k$ $PC \leftarrow STACK$                                                  | None         | 4          |

|                                      |                  | Subroutine Return                                                                          |                                                                                          | None         |            |

| RETI                                 | D I D.           | Interrupt Return                                                                           | $PC \leftarrow STACK$                                                                    | l News       | 4          |

| CPSE                                 | Rd,Rr            | Compare, Skip if Equal                                                                     | if $(Rd = Rr) PC \leftarrow PC + 2 \text{ or } 3$                                        | None         | 1/2/3      |

| CP                                   | Rd,Rr            | Compare                                                                                    | Rd – Rr                                                                                  | Z, N,V,C,H   | 1          |

| CPC                                  | Rd,Rr            | Compare with Carry                                                                         | Rd – Rr – C                                                                              | Z, N,V,C,H   | 1          |

| CPI                                  | Rd,K             | Compare Register with Immediate                                                            | Rd – K                                                                                   | Z, N,V,C,H   | 1          |

| SBRC                                 | Rr, b            | Skip if Bit in Register Cleared                                                            | if (Rr(b)=0) PC $\leftarrow$ PC + 2 or 3                                                 | None         | 1/2/3      |

| SBRS                                 | Rr, b            | Skip if Bit in Register is Set                                                             | if $(\text{Rr}(b)=1) \text{ PC} \leftarrow \text{PC} + 2 \text{ or } 3$                  | None         | 1/2/3      |

| SBIC                                 | P, b             | Skip if Bit in I/O Register Cleared                                                        | if $(P(b)=0) PC \leftarrow PC + 2 \text{ or } 3$                                         | None         | 1/2/3      |

| SBIS                                 | P, b             | Skip if Bit in I/O Register is Set                                                         | if $(P(b)=1) PC \leftarrow PC + 2 \text{ or } 3$                                         | None         | 1/2/3      |

| BRBS                                 | s, k             | Branch if Status Flag Set                                                                  | if (SREG(s) = 1) then PC $\leftarrow$ PC+k + 1                                           | None         | 1/2        |

| BRBC                                 | s, k             | Branch if Status Flag Cleared                                                              | if (SREG(s) = 0) then $PC \leftarrow PC + k + 1$                                         | None         | 1/2        |

| BREQ                                 | k                | Branch if Equal                                                                            | if (Z = 1) then PC $\leftarrow$ PC + k + 1                                               | None         | 1/2        |

| BRNE                                 | k                | Branch if Not Equal                                                                        | if (Z = 0) then PC $\leftarrow$ PC + k + 1                                               | None         | 1/2        |

| BRCS                                 | k                | Branch if Carry Set                                                                        | if (C = 1) then PC $\leftarrow$ PC + k + 1                                               | None         | 1/2        |

| BRCC                                 | k                | Branch if Carry Cleared                                                                    | if (C = 0) then PC $\leftarrow$ PC + k + 1                                               | None         | 1/2        |

| BRSH                                 | k                | Branch if Same or Higher                                                                   | if (C = 0) then PC $\leftarrow$ PC + k + 1                                               | None         | 1/2        |

| BRLO                                 | k                | Branch if Lower                                                                            | if (C = 1) then PC $\leftarrow$ PC + k + 1                                               | None         | 1/2        |

| BRMI                                 | k                | Branch if Minus                                                                            | if (N = 1) then PC $\leftarrow$ PC + k + 1                                               | None         | 1/2        |

| BRPL                                 | k                | Branch if Plus                                                                             | if (N = 0) then PC $\leftarrow$ PC + k + 1                                               | None         | 1/2        |

|                                      | k                | Branch if Greater or Equal, Signed                                                         | if (N $\oplus$ V= 0) then PC $\leftarrow$ PC + k + 1                                     | None         | 1/2        |

| BRGE                                 | K                | Dran shift and Then Zone Ginned                                                            | if (N $\oplus$ V= 1) then PC $\leftarrow$ PC + k + 1                                     | None         | 1/2        |

|                                      | k                | Branch if Less Than Zero, Signed                                                           |                                                                                          |              | 1/2        |

| BRGE                                 |                  | Branch if Less Than Zero, Signed<br>Branch if Half Carry Flag Set                          | if (H = 1) then PC $\leftarrow$ PC + k + 1                                               | None         | 172        |

| BRGE<br>BRLT                         | k                |                                                                                            | if (H = 1) then PC $\leftarrow$ PC + k + 1<br>if (H = 0) then PC $\leftarrow$ PC + k + 1 | None<br>None | 1/2        |

| BRGE<br>BRLT<br>BRHS                 | k<br>k           | Branch if Half Carry Flag Set                                                              |                                                                                          |              |            |

| BRGE<br>BRLT<br>BRHS<br>BRHC<br>BRTS | k<br>k<br>k<br>k | Branch if Half Carry Flag Set<br>Branch if Half Carry Flag Cleared<br>Branch if T Flag Set | if (H = 0) then PC $\leftarrow$ PC + k + 1<br>if (T = 1) then PC $\leftarrow$ PC + k + 1 | None<br>None | 1/2<br>1/2 |

| BRGE<br>BRLT<br>BRHS<br>BRHC         | k<br>k<br>k      | Branch if Half Carry Flag Set<br>Branch if Half Carry Flag Cleared                         | if (H = 0) then PC $\leftarrow$ PC + k + 1                                               | None         | 1/2        |

### Instruction Set Summary (Continued)

| BRIE                                                                                                                                                                                                                    | k                     | Branch if Interrupt Enabled                                                                                                                                                                                                                                                                                                                                                                                                                          | if (I = 1) then PC $\leftarrow$ PC + k + 1                                                                                                                                                                                                                                                                                                                                                                      | None                                                                                                                                                                         | 1/2                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|