# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

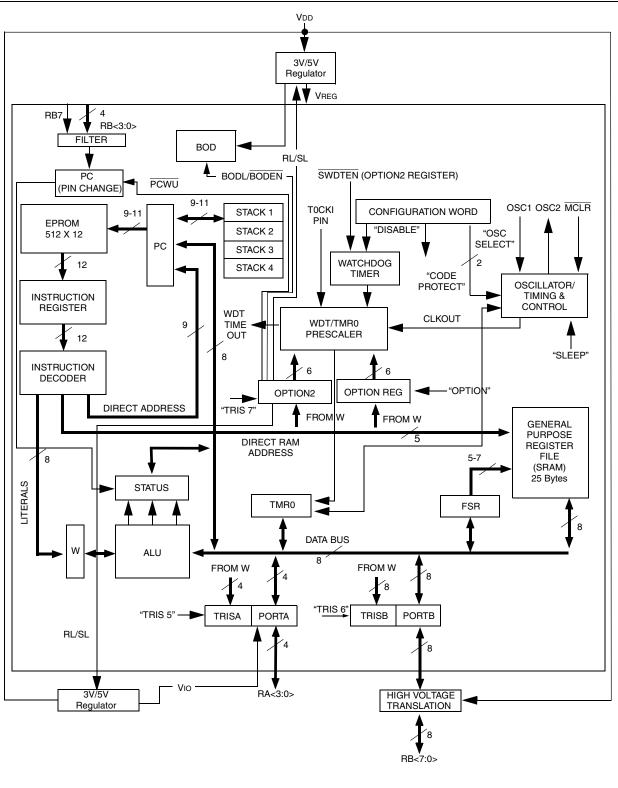

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

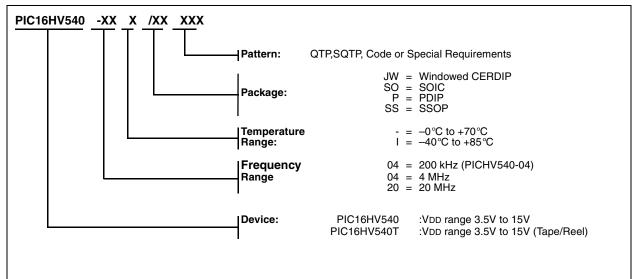

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 12                                                                         |

| Program Memory Size        | 768B (512 x 12)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 25 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 15V                                                                 |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16hv540-20-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

### 4.5 OPTION2 Register

The OPTION2 register is a 6-bit wide, write-only register which contains various control bits to configure the added features on the PIC16HV540. A Power-on Reset sets the OPTION2<5:0> bits.

Example 4-2 illustrates how to initialize the OPTION2 register.

| Note: | All Power-on Resets will disable the     |

|-------|------------------------------------------|

|       | Brown-out Detect circuit. All subsequent |

|       | resets will not disable the Brown-out    |

|       | Detect if enabled.                       |

### EXAMPLE 4-2: INSTRUCTIONS FOR INITIALIZING OPTION2 REGISTER

movlw `0001 0111'b ; load OPTION2 setup value into W

tris 0x07 ; initialize OPTION2 register

### REGISTER 4-3: OPTION2 REGISTER (TRIS 07H)

| U-0      | U-0                                                                                                                                                                                                               | W-1   | W-1        | W-1 | W-1 | W-1  | W-1   |                                                   |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|-----|-----|------|-------|---------------------------------------------------|

|          |                                                                                                                                                                                                                   | PCWU  | SWDTEN     | RL  | SL  | BODL | BODEN | W = Writable bit                                  |

| bit7     |                                                                                                                                                                                                                   |       |            |     |     |      | 0     | U = Unimplemented bit<br>- n = Value at POR reset |

| bit 7-6: | Unimplem                                                                                                                                                                                                          | ented |            |     |     |      |       |                                                   |

| bit 5:   | <b>PCWU</b> : Wa<br>1 = Disable<br>0 = Enable                                                                                                                                                                     | ed .  | Pin Change |     |     |      |       |                                                   |

| bit 4:   | <b>SWDTEN</b> : Software Controlled WDT Enable bit<br>1 = WDT is turned off it the WDTEN configuration bit = 0<br>0 = WDT is on if the WDTEN configuration bit = 0; if WDTEN bit = 1, then SWDTEN is 'don't care' |       |            |     |     |      |       |                                                   |

| bit 3:   | RL: Regulated Voltage Level Select bit<br>1 = 5 volt<br>0 = 3 volt                                                                                                                                                |       |            |     |     |      |       |                                                   |

| bit 2:   | SL: Sleep Voltage Level Select bit<br>1 = RL bit setting<br>0 = 3 volt                                                                                                                                            |       |            |     |     |      |       |                                                   |

| bit 1:   | BODL: Brown-out Voltage Level Select bit<br>1 = RL bit setting, but SL during SLEEP<br>0 = 3 volt                                                                                                                 |       |            |     |     |      |       |                                                   |

| bit 0:   | <b>BODEN</b> : B<br>1 = Disable<br>0 = Enable                                                                                                                                                                     | ed    | Enabled    |     |     |      |       |                                                   |

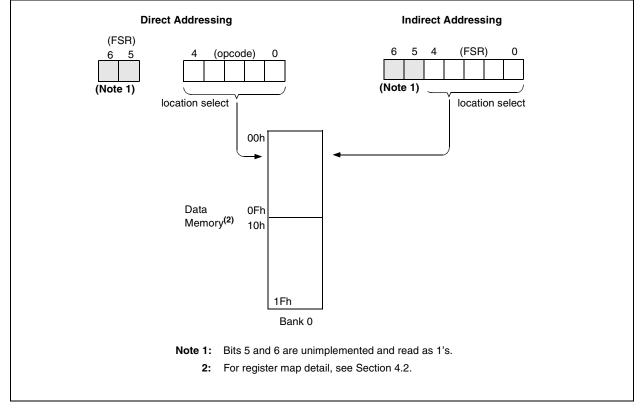

#### 4.8 Indirect Data Addressing; INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

### EXAMPLE 4-3: INDIRECT ADDRESSING

- Register file 05 contains the value 10h

- Register file 06 contains the value 0Ah

- Load the value 05 into the FSR register

- A read of the INDF register will return the value of 10h

- Increment the value of the FSR register by one (FSR = 06)

- A read of the INDR register now will return the value of 0Ah.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected).

A simple program to clear RAM locations 10h-1Fh using indirect addressing is shown in Example 4-4.

## FIGURE 4-4: DIRECT/INDIRECT ADDRESSING

#### EXAMPLE 4-4: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

| NEXT     | movlw<br>movwf<br>clrf<br>incf<br>btfsc<br>goto | 0x10<br>FSR<br>INDF<br>FSR,F<br>FSR,4<br>NEXT | <pre>;initialize pointer<br/>; to RAM<br/>;clear INDF register<br/>;inc pointer<br/>;all done?<br/>;NO, clear next</pre> |

|----------|-------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| CONTINUE | J                                               |                                               | , ,                                                                                                                      |

|          | :                                               | ;                                             | YES, continue                                                                                                            |

The FSR is a 5-bit (PIC16HV540) wide register. It is used in conjunction with the INDF register to indirectly address the data memory area.

The FSR<4:0> bits are used to select data memory addresses 00h to 1Fh.

**PIC16HV540:** Do not use banking. FSR<6:5> are unimplemented and read as '1's.

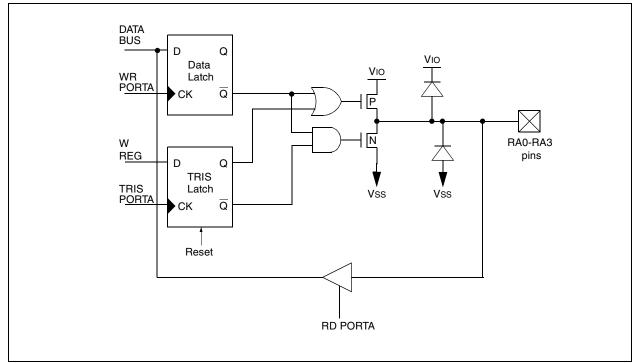

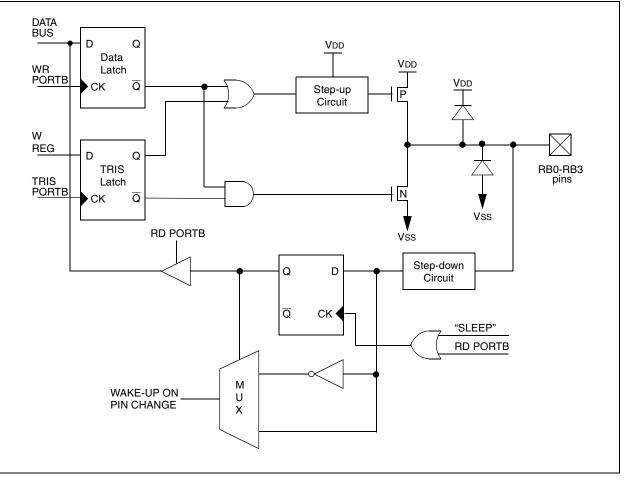

### FIGURE 5-1: BLOCK DIAGRAM OF PORTA<0:3> PINS

| Address | Name    | Bit 7       | Bit 6                                | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1     | Bit 0     | Value on<br>Power-On<br>Reset | Value on<br>MCLR and<br>WDT Reset | Value on<br>Wake-up on<br>Pin Change | Value on<br>Brown-Out<br>Reset |

|---------|---------|-------------|--------------------------------------|-------|--------|-------|-------|-----------|-----------|-------------------------------|-----------------------------------|--------------------------------------|--------------------------------|

| N/A     | TRIS    | I/O control | I/O control registers (TRISA, TRISB) |       |        |       |       | 1111 1111 | 1111 1111 | 1111 1111                     | 1111 1111                         |                                      |                                |

| 05h     | PORTA   | _           | _                                    | _     | _      | RA3   | RA2   | RA1       | RA0       | xxxx                          | uuuu                              | uuuu                                 | xxxx                           |

| 06h     | PORTB   | RB7         | RB6                                  | RB5   | RB4    | RB3   | RB2   | RB1       | RB0       | XXXX XXXX                     | uuuu uuuu                         | uuuu uuuu                            | xxxx xxxx                      |

| 03h     | STATUS  | PCWUF       | PA1                                  | PA0   | TO     | PD    | Z     | DC        | С         | 100x xxxx                     | 100q quuu                         | 000u uuuu                            | x00x xxxx                      |

| N/A     | OPTION2 | _           | _                                    | PCWU  | SWDTEN | RL    | SL    | BODL      | BODEN     | 11 1111                       | uu uuuu                           | uu uuuu                              | xx xxxx                        |

#### TABLE 5-1: SUMMARY OF PORT REGISTERS

Legend: Shaded boxes = unimplemented, read as '0', --= unimplemented, read as '0', x = unknown, u = unchanged.

#### 5.5 I/O Programming Considerations

#### 5.5.1 BI-DIRECTIONAL I/O PORTS

Some instructions operate internally as read followed by write operations. The BCF and BSF instructions, for example, read the entire port into the CPU, execute the bit operation and re-write the result. Caution must be used when these instructions are applied to a port where one or more pins are used as input/outputs. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU, bit5 to be set and the PORTB value to be written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (say bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched into output mode later on, the content of the data latch may now be unknown.

Example 5-1 shows the effect of two sequential read-modify-write instructions (e.g.,  ${\tt BCF}\,,~{\tt BSF},$  etc.) on an I/ O port.

A pin actively outputting a high or a low should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

#### EXAMPLE 5-1: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

;Initial PORT Settings

; PORTB<7:4> Inputs

; PORTB<3:0> Outputs

;PORTB<7:6> have external pull-ups and are ;not connected to other circuitry

| ,<br>;<br>; |       |                                   | PORT                         | latch | PORT                 | pins |

|-------------|-------|-----------------------------------|------------------------------|-------|----------------------|------|

| ,           | MOVLW | PORTB,<br>PORTB,<br>03Fh<br>PORTB | ;01pp<br>;10pp<br>;<br>;10pp | pppp  | 11pp<br>11pp<br>10pp | pppp |

| •           |       |                                   |                              |       |                      |      |

;Note that the user may have expected the pin ;values to be 00pp pppp. The 2nd BCF caused ;RB7 to be latched as the pin value (High).

# 5.5.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-5). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should allow the pin voltage to stabilize (load dependent) before the next instruction, which causes that file to be read into the CPU, is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

# FIGURE 5-5: SUCCESSIVE I/O OPERATION

|                         | PC                   | PC + 1                             | PC + 2                          | V PC + 3                              |                                         |

|-------------------------|----------------------|------------------------------------|---------------------------------|---------------------------------------|-----------------------------------------|

| Instruction<br>fetched  | 1<br>1               | MOVF PORTB,W                       |                                 | NOP                                   | This example shows a write              |

| RB7:RB0                 | <u>۱</u>             | I                                  | X                               | ·                                     | to PORTB followed by a read from PORTB. |

|                         | 1<br> <br> <br> <br> | Port pin<br>written here           | Port pin<br>sampled here        | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |                                         |

| Instruction<br>executed |                      | MOVWF PORTB<br>(Write to<br>PORTB) | MOVF PORTB,W<br>(Read<br>PORTB) | NOP                                   |                                         |

|                         |                      | Write to                           | (Read                           |                                       | •                                       |

NOTES:

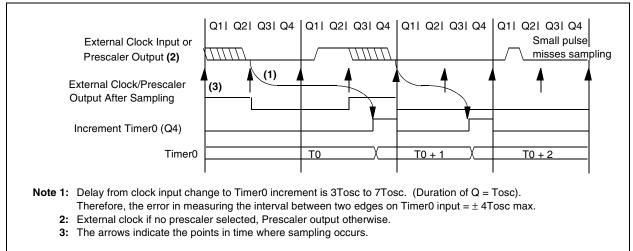

### 6.1 Using Timer0 with an External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 6.1.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple counter-type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### 6.1.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 6-5 shows the delay from the external clock edge to the timer incrementing.

### FIGURE 6-5: TIMER0 TIMING WITH EXTERNAL CLOCK

### 7.7 <u>Watchdog Timer (WDT)</u>

The Watchdog Timer (WDT) is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins have been stopped, for example, by execution of a SLEEP instruction. During normal operation or SLEEP, a WDT Reset or Wake-up Reset generates a device RESET.

The  $\overline{\text{TO}}$  bit (STATUS<4>) will be cleared upon a Watchdog Timer Reset.

The Watchdog Timer is enabled/disabled by a device configuration bit (see Figure 7-1). If the WDT is enabled, software execution may not disable this function. When the WDTEN configuration bit is cleared, the SWDTEN bit, OPTION2<4>, enables/disables the operation of the WDT.

#### 7.7.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms, (with no prescaler). If a longer time-out period is desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT (under software control) by writing to the OPTION register. Thus, time-out a period of a nominal 2.3 seconds can be realized. These periods vary with temperature, VDD and part-to-part process variations (see DC specs).

Under worst case conditions (VDD = Min., Temperature = Max., max. WDT prescaler), it may take several seconds before a WDT time-out occurs.

### 7.7.2 WDT PROGRAMMING CONSIDERATIONS

The CLRWDT instruction clears the WDT and the postscaler, if assigned to the WDT, and prevents it from timing out and generating a device RESET.

The SLEEP instruction resets the WDT and the postscaler, if assigned to the WDT. This gives the maximum SLEEP time before a WDT Wake-up Reset.

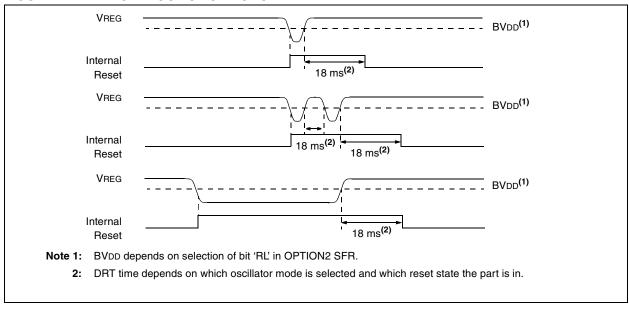

## 7.8 Internal Voltage Regulators

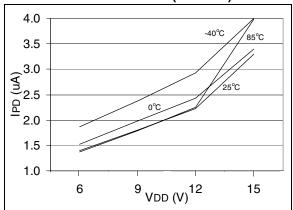

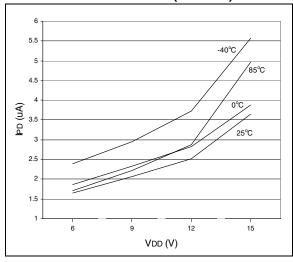

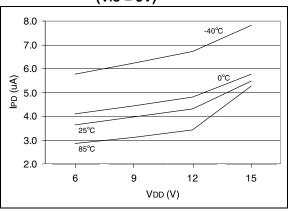

The PIC16HV540 has 2 internal voltage regulators. The PORTA I/O pads and OSC2 are powered by one internal voltage regulator  $V_{IO}$ , while the second internal voltage regulator  $V_{REG}$ , powers the PICmicro<sup>®</sup> device core. Both regulated voltage levels can be synchronously switched in the active modes between 3V and 5V through bit "RL" in the OPTION2 register. In addition, the "SL" bit in the OPTION2 register can be used to control the core's regulated voltage level during SLEEP mode.  $V_{REG}$  regulates the 15V power applied to the  $V_{DD}$  pin.

The on-chip Brown-out Detect circuitry monitors the CPU regulated voltage  $V_{REG}$ , for determining if a brown-out reset is generated (see Section 7.6 for more details on the BOD).

The regulator circuits are identical in functional nature but only the  $V_{IO}$  regulator voltage can be measured, externally (See Section 10.1 for  $V_{IO}$  parameters). The operational voltage range and pin loading requirements must be considered to ensure proper system operation. For example, if 3V regulation is implemented during the SLEEP mode and 40mA is being sourced from PORTA, the  $V_{IO}$  regulation voltage may approach the specified minimum voltage. This may be an issue to consider for connections to external circuitry. Likewise, if zero current is sourced from the PORTA pins, the regulation

| BSF                 | Bit Set f                                                                                                                                                                               | BTFSS              | Bit Test f, Skip if Set                                                          |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------------------------------------------------------------------|

| Syntax:             | [ <i>label</i> ] BSF f,b                                                                                                                                                                | Syntax:            | [label] BTFSS f,b                                                                |

| Operands:           | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                      | Operands:          | $0 \le f \le 31$<br>$0 \le b < 7$                                                |

| Operation:          | $1 \rightarrow (f < b >)$                                                                                                                                                               | Operation:         | skip if (f <b>) = 1</b>                                                          |

| Status Affected:    | None                                                                                                                                                                                    | Status Affected:   | None                                                                             |

| Encoding:           | 0101 bbbf ffff                                                                                                                                                                          | Encoding:          | 0111 bbbf ffff                                                                   |

| Description:        | Bit 'b' in register 'f' is set.                                                                                                                                                         | Description:       | If bit 'b' in register 'f' is '1' then the next                                  |

| Words:              | 1                                                                                                                                                                                       |                    | instruction is skipped.<br>If bit 'b' is '1', then the next instruction          |

| Cycles:             | 1                                                                                                                                                                                       |                    | fetched during the current instruction                                           |

| Example:            | BSF FLAG_REG, 7                                                                                                                                                                         |                    | execution, is discarded and an NOP is<br>executed instead, making this a 2 cycle |

| Before Instru       |                                                                                                                                                                                         |                    | instruction.                                                                     |

|                     | EG = 0x0A                                                                                                                                                                               | Words:             | 1                                                                                |

| After Instruc       | tion<br>EG = 0x8A                                                                                                                                                                       | Cycles:            | 1(2)                                                                             |

|                     |                                                                                                                                                                                         | Example:           | HERE BTFSS FLAG,1                                                                |

| BTFSC               | Bit Test f, Skip if Clear                                                                                                                                                               |                    | FALSE GOTO PROCESS_CODE<br>TRUE •                                                |

| Syntax:             | [label] BTFSC f,b                                                                                                                                                                       |                    | •                                                                                |

| Operands:           | $0 \le f \le 31$                                                                                                                                                                        |                    | •                                                                                |

|                     | $0 \le b \le 7$                                                                                                                                                                         | Before Instr<br>PC | = address (HERE)                                                                 |

| Operation:          | skip if $(f < b >) = 0$                                                                                                                                                                 | After Instruc      |                                                                                  |

| Status Affected:    | None                                                                                                                                                                                    | If FLAG            | <1> = 0,                                                                         |

| Encoding:           | 0110 bbbf ffff                                                                                                                                                                          | PC<br>if FLAG∢     | = address (FALSE);<br><1> = 1,                                                   |

| Description:        | If bit 'b' in register 'f' is 0 then the next instruction is skipped.                                                                                                                   | PC                 | = address (TRUE)                                                                 |

|                     | If bit 'b' is 0 then the next instruction<br>fetched during the current instruction<br>execution is discarded, and an NOP is<br>executed instead, making this a 2 cycle<br>instruction. |                    |                                                                                  |

| Words:              | 1                                                                                                                                                                                       |                    |                                                                                  |

| Cycles:             | 1(2)                                                                                                                                                                                    |                    |                                                                                  |

| Example:            | HERE BTFSC FLAG,1<br>FALSE GOTO PROCESS_CODE<br>TRUE •<br>•                                                                                                                             |                    |                                                                                  |

| Before Instru<br>PC | uction<br>= address (HERE)                                                                                                                                                              |                    |                                                                                  |

| After Instruc       |                                                                                                                                                                                         |                    |                                                                                  |

| if FLAG<<br>PC      | <pre>:1&gt; = 0,<br/>= address (TRUE);</pre>                                                                                                                                            |                    |                                                                                  |

| if FLAG<            | :1> = 1,                                                                                                                                                                                |                    |                                                                                  |

| PC                  | = address (FALSE)                                                                                                                                                                       |                    |                                                                                  |

| COMF                      | Complement f                                                                                                                                                         |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                   | [label] COMF f,d                                                                                                                                                     |

| Operands:                 | $\begin{array}{l} 0\leq f\leq 31\\ d\in \left[0,1\right] \end{array}$                                                                                                |

| Operation:                | $(\overline{f}) \rightarrow (dest)$                                                                                                                                  |

| Status Affected:          | Z                                                                                                                                                                    |

| Encoding:                 | 0010 01df ffff                                                                                                                                                       |

| Description:              | The contents of register 'f' are comple-<br>mented. If 'd' is 0 the result is stored in<br>the W register. If 'd' is 1 the result is<br>stored back in register 'f'. |

| Words:                    | 1                                                                                                                                                                    |

| Cycles:                   | 1                                                                                                                                                                    |

| Example:                  | COMF REG1,0                                                                                                                                                          |

| Before Instru<br>REG1     | uction<br>= 0x13                                                                                                                                                     |

| After Instruc             | tion                                                                                                                                                                 |

| REG1<br>W                 | = 0x13<br>= 0xEC                                                                                                                                                     |

| vv                        |                                                                                                                                                                      |

| DECF                      | Decrement f                                                                                                                                                          |

| Syntax:                   | [label] DECF f,d                                                                                                                                                     |

| Operands:                 | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                                     |

| Operation:                | (f) – 1 $\rightarrow$ (dest)                                                                                                                                         |

| Status Affected:          | Z                                                                                                                                                                    |

| Encoding:                 | 0000 11df ffff                                                                                                                                                       |

| Description:              | Decrement register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd' is<br>1 the result is stored back in register 'f'.                             |

| Words:                    | 1                                                                                                                                                                    |

| Cycles:                   | 1                                                                                                                                                                    |

| Example:                  | DECF CNT, 1                                                                                                                                                          |

| Before Instru<br>CNT<br>Z | uction<br>= 0x01<br>= 0                                                                                                                                              |

| After Instruc             |                                                                                                                                                                      |

| CNT                       | = 0x00                                                                                                                                                               |

| Z                         | = 1                                                                                                                                                                  |

|                           |                                                                                                                                                                      |

| DECFSZ                                               | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                               |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                              | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                                   |

| Operands:                                            | $\begin{array}{l} 0\leq f\leq 31\\ d\in \ [0,1] \end{array}$                                                                                                                                                                                                                                                                         |

| Operation:                                           | $(f) - 1 \rightarrow d;$ skip if result = 0                                                                                                                                                                                                                                                                                          |

| Status Affected:                                     | None                                                                                                                                                                                                                                                                                                                                 |

| Encoding:                                            | 0010 11df ffff                                                                                                                                                                                                                                                                                                                       |

| Description:                                         | The contents of register 'f' are decre-<br>mented. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>placed back in register 'f'.<br>If the result is 0, the next instruction,<br>which is already fetched, is discarded<br>and an NOP is executed instead mak-<br>ing it a two cycle instruction. |

| Words:                                               | 1                                                                                                                                                                                                                                                                                                                                    |

| Cycles:                                              | 1(2)                                                                                                                                                                                                                                                                                                                                 |

| Example:                                             | HERE DECFSZ CNT, 1<br>GOTO LOOP                                                                                                                                                                                                                                                                                                      |

|                                                      | CONTINUE •                                                                                                                                                                                                                                                                                                                           |

|                                                      | •                                                                                                                                                                                                                                                                                                                                    |

| Before Instru<br>PC                                  | uction<br>= address (HERE)                                                                                                                                                                                                                                                                                                           |

| After Instruc<br>CNT<br>if CNT<br>PC<br>if CNT<br>PC | <pre>= CNT - 1;<br/>= 0,<br/>= address (CONTINUE);</pre>                                                                                                                                                                                                                                                                             |

| GOTO                                                 | Unconditional Branch                                                                                                                                                                                                                                                                                                                 |

| Syntax:                                              | [ <i>label</i> ] GOTO k                                                                                                                                                                                                                                                                                                              |

| Operands:                                            | $0 \le k \le 511$                                                                                                                                                                                                                                                                                                                    |

| Operation:                                           | $k \rightarrow PC < 8:0>;$<br>STATUS<6:5> $\rightarrow PC < 10:9>$                                                                                                                                                                                                                                                                   |

| Status Affected:                                     | None                                                                                                                                                                                                                                                                                                                                 |

| Encoding:                                            | 101k kkkk kkkk                                                                                                                                                                                                                                                                                                                       |

| Description:                                         | GOTO is an unconditional branch. The<br>9-bit immediate value is loaded into PC<br>bits <8:0>. The upper bits of PC are<br>loaded from STATUS<6:5>. GOTO is a<br>two cycle instruction.                                                                                                                                              |

| Words:                                               | 1                                                                                                                                                                                                                                                                                                                                    |

| Cycles:                                              | 2                                                                                                                                                                                                                                                                                                                                    |

| Example:                                             | GOTO THERE                                                                                                                                                                                                                                                                                                                           |

| After Instruc                                        |                                                                                                                                                                                                                                                                                                                                      |

| PC =                                                 | address (THERE)                                                                                                                                                                                                                                                                                                                      |

| MOVF             | Move f                                                                                    | MOVWF            | Move W to f                             |

|------------------|-------------------------------------------------------------------------------------------|------------------|-----------------------------------------|

| Syntax:          | [label] MOVF f,d                                                                          | Syntax:          | [label] MOVWF f                         |

| Operands:        | $0 \le f \le 31$                                                                          | Operands:        | $0 \le f \le 31$                        |

|                  | $d \in [0,1]$                                                                             | Operation:       | $(W) \to (f)$                           |

| Operation:       | $(f) \rightarrow (dest)$                                                                  | Status Affected: | None                                    |

| Status Affected: | Z                                                                                         | Encoding:        | 0000 001f ffff                          |

| Encoding:        | 0010 00df ffff                                                                            | Description:     | Move data from the W register to regis- |

| Description:     | The contents of register 'f' is moved to                                                  |                  | ter 'f'.                                |

|                  | destination 'd'. If 'd' is 0, destination is the W register. If 'd' is 1, the destination | Words:           | 1                                       |

|                  | is file register 'f'. 'd' is 1 is useful to test                                          | Cycles:          | 1                                       |

|                  | a file register since status flag Z is affected.                                          | Example:         | MOVWF TEMP_REG                          |

| Words:           | 1                                                                                         | Before Instr     |                                         |

| Cycles:          | 1                                                                                         | TEMP_F<br>W      | REG = 0xFF<br>= 0x4F                    |

| Example:         | MOVF FSR, 0                                                                               | After Instruc    |                                         |

| After Instruc    |                                                                                           | TEMP_F           |                                         |

| W =              | value in FSR register                                                                     | W                | = 0x4F                                  |

|                  |                                                                                           | NOP              | No Operation                            |

| MOVLW            | Move Literal to W                                                                         | Syntax:          | [label] NOP                             |

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                  | Operands:        | None                                    |

| Operands:        | $0 \le k \le 255$                                                                         | Operation:       | No operation                            |

| Operation:       | $k \rightarrow (W)$                                                                       | Status Affected: | None                                    |

| Status Affected: | None                                                                                      | Encoding:        | 0000 0000 0000                          |

| Encoding:        | 1100 kkkk kkkk                                                                            | Description:     | No operation.                           |

| Description:     | The eight bit literal 'k' is loaded into the                                              | Words:           | 1                                       |

|                  | W register. The don't cares will assem-<br>ble as 0s.                                     | Cycles:          | 1                                       |

| Words:           | 1                                                                                         | Example:         | NOP                                     |

| Cycles:          | 1                                                                                         |                  |                                         |

| Example:         | MOVLW 0x5A                                                                                |                  |                                         |

| Litample.        | NCVIW UXDA                                                                                |                  |                                         |

After Instruction W = 0x5

0x5A

| OPTION               | Load OPTION Regis                                                                                                                                                                   | ter              |  |  |  |  |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--|--|--|--|

| Syntax:              | [label] OPTION                                                                                                                                                                      |                  |  |  |  |  |

| Operands:            | None                                                                                                                                                                                |                  |  |  |  |  |

| Operation:           | $(W) \rightarrow OPTION$                                                                                                                                                            |                  |  |  |  |  |

| Status Affected:     | None                                                                                                                                                                                |                  |  |  |  |  |

| Encoding:            | 0000 0000 00                                                                                                                                                                        | 10               |  |  |  |  |

| Description:         | The content of the W reg                                                                                                                                                            | gister is loaded |  |  |  |  |

|                      | into the OPTION registe                                                                                                                                                             | r.               |  |  |  |  |

| Words:               | 1                                                                                                                                                                                   |                  |  |  |  |  |

| Cycles:              | 1                                                                                                                                                                                   |                  |  |  |  |  |

| Example              | OPTIO<br>N                                                                                                                                                                          |                  |  |  |  |  |

| Before Instru        |                                                                                                                                                                                     |                  |  |  |  |  |

| W                    | = 0x07                                                                                                                                                                              |                  |  |  |  |  |

| After Instruct       | ion                                                                                                                                                                                 |                  |  |  |  |  |

| OPTION               | = 0x07                                                                                                                                                                              |                  |  |  |  |  |

| RETLW                | Return with Literal i                                                                                                                                                               | n W              |  |  |  |  |

| Syntax:              | [label] RETLW k                                                                                                                                                                     |                  |  |  |  |  |

| Operands:            | $0 \leq k \leq 255$                                                                                                                                                                 |                  |  |  |  |  |

| Operation:           | $k \rightarrow$ (W);                                                                                                                                                                |                  |  |  |  |  |

|                      | $TOS \rightarrow PC$                                                                                                                                                                |                  |  |  |  |  |

| Status Affected:     | None                                                                                                                                                                                |                  |  |  |  |  |

| Encoding:            | 1000 kkkk kkk                                                                                                                                                                       | :k               |  |  |  |  |

| Description:         | The W register is loaded with the eight<br>bit literal 'k'. The program counter is<br>loaded from the top of the stack (the<br>return address). This is a two cycle<br>instruction. |                  |  |  |  |  |

| Words:               | 1                                                                                                                                                                                   |                  |  |  |  |  |

| Cycles:              | 2                                                                                                                                                                                   |                  |  |  |  |  |

| Example:             | CALL TABLE ;W cont                                                                                                                                                                  | ains             |  |  |  |  |

|                      | ;table                                                                                                                                                                              |                  |  |  |  |  |

|                      | ; value.                                                                                                                                                                            | has table        |  |  |  |  |

|                      | <ul> <li>, w now</li> <li>; value.</li> </ul>                                                                                                                                       |                  |  |  |  |  |

| TABLE                |                                                                                                                                                                                     |                  |  |  |  |  |

| TABLE                | ADDWF PC ;W = of<br>RETLW k1 ;Begin                                                                                                                                                 |                  |  |  |  |  |

|                      | RETLW k2 ;                                                                                                                                                                          |                  |  |  |  |  |

|                      | •                                                                                                                                                                                   |                  |  |  |  |  |

|                      | •                                                                                                                                                                                   |                  |  |  |  |  |

|                      | RETLW kn ; End c                                                                                                                                                                    | of table         |  |  |  |  |

| Before Instru<br>W = |                                                                                                                                                                                     |                  |  |  |  |  |

|                      |                                                                                                                                                                                     |                  |  |  |  |  |

| After Instruct       | IOU                                                                                                                                                                                 |                  |  |  |  |  |

|                      | value of k8                                                                                                                                                                         |                  |  |  |  |  |

| RLF                                                                                                                                           | Rotate Left f through Carry                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                                                                       | [label] RLF f,d                                                                                                                                                                                                                                                                                                                                                                        |

| Operands:                                                                                                                                     | $\begin{array}{l} 0\leq f\leq 31\\ d\in \ [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                           |

| Operation:                                                                                                                                    | See description below                                                                                                                                                                                                                                                                                                                                                                  |

| Status Affected:                                                                                                                              | С                                                                                                                                                                                                                                                                                                                                                                                      |

| Encoding:                                                                                                                                     | 0011 01df ffff                                                                                                                                                                                                                                                                                                                                                                         |

| Description:                                                                                                                                  | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is stored<br>back in register 'f'.                                                                                                                                                                            |

| Words:                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                      |

| Cycles:                                                                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                      |

| Example:                                                                                                                                      | RLF REG1,0                                                                                                                                                                                                                                                                                                                                                                             |

| Before Instru<br>REG1<br>C                                                                                                                    | uction<br>= 1110 0110<br>= 0                                                                                                                                                                                                                                                                                                                                                           |

| After Instruc<br>REG1<br>W<br>C                                                                                                               | -                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                        |

| RRF                                                                                                                                           | Rotate Right f through Carry                                                                                                                                                                                                                                                                                                                                                           |

| RRF<br>Syntax:                                                                                                                                | Rotate Right f through Carry<br>[ <i>label</i> ] RRF f,d                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                        |

| Syntax:                                                                                                                                       | [label] RRF f,d<br>0 $\leq$ f $\leq$ 31                                                                                                                                                                                                                                                                                                                                                |

| Syntax:<br>Operands:                                                                                                                          | $\begin{bmatrix} label \end{bmatrix} RRF f,d$<br>$0 \le f \le 31$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                                                     |

| Syntax:<br>Operands:<br>Operation:                                                                                                            | $\begin{bmatrix} label \end{bmatrix} RRF f,d$<br>$0 \le f \le 31$<br>$d \in [0,1]$<br>See description below                                                                                                                                                                                                                                                                            |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                                                                        | $\begin{bmatrix} label \end{bmatrix} RRF f,d$ $0 \le f \le 31$ $d \in [0,1]$ See description below C $0011  00df  ffff$ The contents of register 'f' are rotated one bit to the right through the Carry Flag. If 'd' is 0 the result is placed in the W register. If 'd' is 1 the result is placed back in register 'f'.                                                               |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                                                                           | $\begin{bmatrix} label \end{bmatrix} RRF f,d$ $0 \le f \le 31$ $d \in [0,1]$ See description below C $0011  00df  ffff$ The contents of register 'f' are rotated one bit to the right through the Carry Flag. If 'd' is 0 the result is placed in the W register. If 'd' is 1 the result is placed                                                                                     |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                                                                           | $\begin{bmatrix} label \end{bmatrix} RRF f,d$ $0 \le f \le 31$ $d \in [0,1]$ See description below C $0011  00df  ffff$ The contents of register 'f' are rotated one bit to the right through the Carry Flag. If 'd' is 0 the result is placed in the W register. If 'd' is 1 the result is placed back in register 'f'.                                                               |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:                                                           | [ <i>label</i> ] RRF f,d<br>$0 \le f \le 31$<br>$d \in [0,1]$<br>See description below<br>C<br>0011 00df ffff<br>The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'<br>register 'f'                                           |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:                                                 | [ <i>label</i> ] RRF f,d<br>$0 \le f \le 31$<br>$d \in [0,1]$<br>See description below<br>C<br>0011 00df ffff<br>The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'<br>register 'f'<br>1                                      |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:                                      | [ <i>label</i> ] RRF f,d<br>$0 \le f \le 31$<br>$d \in [0,1]$<br>See description below<br>C<br>0011 00df ffff<br>The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'<br>1<br>1<br>RRF REG1, 0                                  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles:<br>Example:<br>Before Instru<br>REG1 | [ <i>label</i> ] RRF f,d<br>$0 \le f \le 31$<br>$d \in [0,1]$<br>See description below<br>C<br>0011 00df ffff<br>The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'.<br>1<br>1<br>RRF REG1, 0<br>iction<br>= 1110 0110<br>= 0 |

| SWAPF                   | SWAPF Swap Nibbles in f                                                                                                                                               |  |  |  |  |  |  |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:                 | [label] SWAPF f,d                                                                                                                                                     |  |  |  |  |  |  |

| Operands:               | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \left[ 0,1 \right] \end{array}$                                                                                           |  |  |  |  |  |  |

| Operation:              | $\begin{array}{l} (f{<}3:0{>}) \rightarrow (dest{<}7:4{>});\\ (f{<}7:4{>}) \rightarrow (dest{<}3:0{>}) \end{array}$                                                   |  |  |  |  |  |  |

| Status Affected:        | None                                                                                                                                                                  |  |  |  |  |  |  |

| Encoding:               | 0011 10df ffff                                                                                                                                                        |  |  |  |  |  |  |

| Description:            | The upper and lower nibbles of register<br>'f' are exchanged. If 'd' is 0 the result is<br>placed in W register. If 'd' is 1 the result<br>is placed in register 'f'. |  |  |  |  |  |  |