Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               |                                                                             |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                            |

| Number of I/O              | 12                                                                          |

| Program Memory Size        | 768B (512 x 12)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                |                                                                             |

| RAM Size                   | 25 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 15V                                                                  |

| Data Converters            |                                                                             |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 20-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16hv540-20i-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 1.2.6 INCREASED STACK DEPTH

The stack depth is 4 levels to allow modular program implementation by using functions and subroutines.

#### 1.2.7 ENHANCED WATCHDOG TIMER (WDT) OPERATION

The WDT is enabled by setting FUSE 2 in the configuration word. The WDT setting is latched and the fuse disabled during SLEEP mode to reduce current consumption.

If the WDT is disabled by FUSE 2, it can be enabled/disabled under program control using bit 4 in OPTION2 Register (SWDTEN). The software WDT control is disabled at power-up.

The current consumption of the on-chip oscillator (used for the watchdog, oscillator startup timer and sleep timer) is less than  $1\mu A$  (typical) at 3 Volt operation.

#### 1.2.8 REDUCED EXTERNAL RC OSCILLATOR STARTUP TIME

If the RC oscillator option is selected in the Configuration word (FOSC1=1 and FOSCO=1), the oscillator startup time is 1.0 ms nominal instead of 18 ms nominal. This is applicable after power-up (POR), either WDT interrupt or wake-up, external reset on MCLR, PCWU (wake on pin change) and Brown-out.

# 1.2.9 LOW-VOLTAGE OPERATION OF THE ENTIRE CPU DURING SLEEP

The voltage regulator can automatically lower the voltage to the core from 5 Volt to 3 Volt during sleep, resulting in reduced current consumption. This is an option bit (SL) in the OPTION2 register.

# 1.2.10 GLITCH FILTERS ON WAKE-UP PINS AND MCLR

Glitch sensitive inputs for wake-up on pin change are filtered to reduce susceptibility to interference. A similar filter reduces false reset on MCLR.

#### 1.2.11 PROGRAMMABLE CLOCK GENERATOR

When used in RC mode, the CLKOUT pin can be used as a programmable clock output. The output is connected to TMR0, bit 0 and by setting the prescaler, clock out frequencies of CLKIN/8 to CLKIN/1024 can be generated. The CLKOUT pin can also be used as a general purpose output by modifying TMR0, bit 0.

## TABLE 1-1:PIC16HV540 DEVICE

|             |                         | PIC16HV540                        |

|-------------|-------------------------|-----------------------------------|

| Clock       | Maximum Frequency (MHz) | 20                                |

| Memory      | EPROM Program Memory    | 512                               |

|             | RAM Data Memory (bytes) | 25                                |

| Peripherals | Timer Module(s)         | TMR0                              |

| Packages    | I/O Pins                | 12                                |

|             | Voltage Range (Volts)   | 3.5V-15V                          |

|             | Number of Instructions  | 33                                |

|             | Packages                | 18-pin DIP<br>SOIC<br>20-pin SSOP |

All PICmicro<sup>®</sup> devices have Power-on Reset, selectable WDT, selectable code protect and high I/O current capability.

NOTES:

| Name        | DIP, SOIC<br>No. | SSOP<br>No. | I/O/P<br>Type | Input<br>Levels | Description                                                                                                                                                                                                            |                         |  |  |

|-------------|------------------|-------------|---------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|--|

| RA0         | 17               | 19          | I/O           | TTL             | Independently regulated Bi-directiona                                                                                                                                                                                  | I I/O port — VIO        |  |  |

| RA1         | 18               | 20          | I/O           | TTL             |                                                                                                                                                                                                                        | ·                       |  |  |

| RA2         | 1                | 1           | I/O           | TTL             |                                                                                                                                                                                                                        |                         |  |  |

| RA3         | 2                | 2           | I/O           | TTL             |                                                                                                                                                                                                                        |                         |  |  |

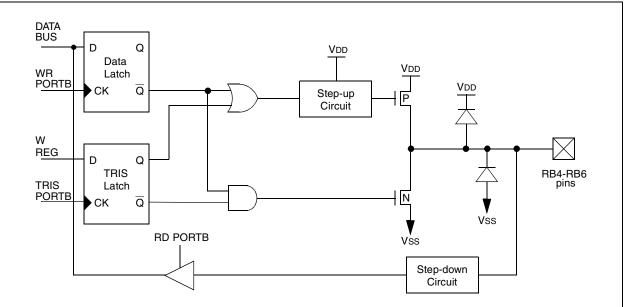

| RB0         | 6                | 7           | I/O           | TTL             | High-voltage Bi-directional I/O port.                                                                                                                                                                                  | Wake-up on pin          |  |  |

| RB1         | 7                | 8           | I/O           | TTL             | Sourced from VDD.                                                                                                                                                                                                      | change                  |  |  |

| RB2         | 8                | 9           | I/O           | TTL             |                                                                                                                                                                                                                        | -                       |  |  |

| RB3         | 9                | 10          | I/O           | TTL             |                                                                                                                                                                                                                        |                         |  |  |

| RB4         | 10               | 11          | I/O           | TTL             |                                                                                                                                                                                                                        |                         |  |  |

| RB5         | 11               | 12          | I/O           | TTL             |                                                                                                                                                                                                                        |                         |  |  |

| RB6         | 12               | 13          | I/O           | TTL             |                                                                                                                                                                                                                        |                         |  |  |

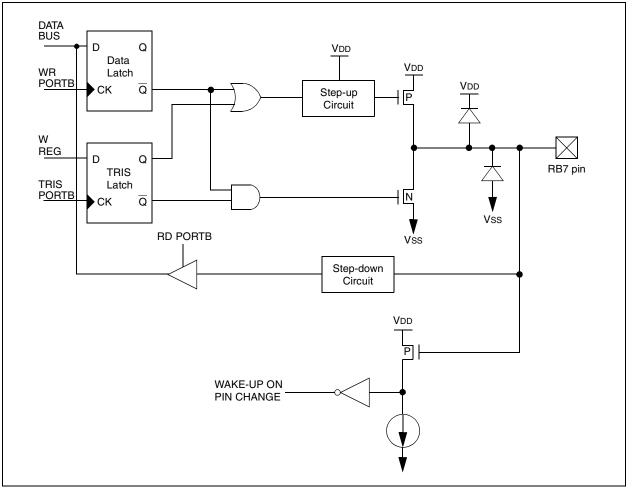

| RB7         | 13               | 14          | I/O           | TTL             |                                                                                                                                                                                                                        | Wake-up on SLOW         |  |  |

|             |                  |             |               |                 |                                                                                                                                                                                                                        | rising pin change.      |  |  |

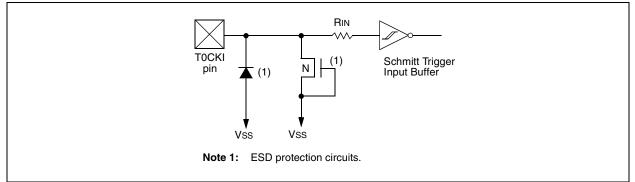

| TOCKI       | 3                | 3           | I             | ST              | Clock input to Timer 0. Must be tied to                                                                                                                                                                                | o Vss or VDD, if not in |  |  |

|             |                  |             |               |                 | use, to reduce current consumption.                                                                                                                                                                                    |                         |  |  |

| MCLR/Vpp    | 4                | 4           | I             | ST              | Master clear (reset) input/programming voltage input. This pin is an active low reset to the device. Voltage on the MCLI VPP pin must not exceed VDD <sup>(1)</sup> to avoid unintended entering of programming mode.  |                         |  |  |

| OSC1/CLKIN  | 16               | 18          | I             | ST              | Oscillator crystal input/external clock                                                                                                                                                                                | source input.           |  |  |

| OSC2/CLKOUT | 15               | 17          | 0             | _               | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, OSC2/CLKOUT output is connected to TMR0, bit 0. Frequencies of CLKIN/8 to CLKIN/1024 can be generated on this pin. |                         |  |  |

| Vdd         | 14               | 15,16       | Р             | —               | Positive supply.                                                                                                                                                                                                       |                         |  |  |

| Vss         | 5                | 5,6         | Р             |                 | Ground reference.                                                                                                                                                                                                      |                         |  |  |

| <b>TABLE 3-1:</b> | <b>PINOUT DESCRIPTION - PIC16HV540</b> |

|-------------------|----------------------------------------|

|                   |                                        |

$\label{eq:legend: Legend: I = input, O = output, I/O = input/output, P = power, --- = Not Used, TTL = TTL input, ST = Schmitt Trigger input.$

**Note 1:** VDD during programming mode can not exceed parameter PD1 called out in the PIC16C5X Programming Specification (Literature number DS30190).

## 4.4 OPTION Register

The OPTION register is a 6-bit wide, write-only register which contains various control bits to configure the Timer0/WDT prescaler and Timer0.

By executing the OPTION instruction, the contents of the W register will be transferred to the OPTION register. A RESET sets the OPTION<5:0> bits.

Example 4-1 illustrates how to initialize the OPTION register.

### EXAMPLE 4-1: INSTRUCTIONS FOR INITIALIZING OPTION REGISTER

| movlw  | <b>`</b> 0000 | 0111′b | ; | load | OPTION | setup  | value  | into | W |

|--------|---------------|--------|---|------|--------|--------|--------|------|---|

| OPTION |               |        | ; | init | ialize | OPTION | regist | cer  |   |

## **REGISTER 4-2: OPTION REGISTER**

| U-0      | U-0                                                                                                                                                         | W-1                                       | N-1                                    | W-1                          | W-1 | W-1 | W-1 |                                                   |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|----------------------------------------|------------------------------|-----|-----|-----|---------------------------------------------------|

| —        | _                                                                                                                                                           | TOCS T                                    | 0SE                                    | PSA                          | PS2 | PS1 | PS0 | W = Writable bit                                  |

| bit7     |                                                                                                                                                             |                                           |                                        |                              |     |     | 0   | U = Unimplemented bit<br>- n = Value at POR reset |

| bit 7-6: | Unimplemented                                                                                                                                               |                                           |                                        |                              |     |     |     |                                                   |

| bit 5:   | TOCS: Time                                                                                                                                                  | r0 Clock Sour                             | ce Seleo                               | ct bit                       |     |     |     |                                                   |

|          | 1 = Transitio                                                                                                                                               | n on T0CKI pi                             | n                                      |                              |     |     |     |                                                   |

|          | 0 = Internal                                                                                                                                                | instruction cyc                           | le clock                               | (CLKOUT                      | .)  |     |     |                                                   |

| bit 4:   | <b>TOSE</b> : Timer0 Source Edge Select bit<br>1 = Increment on high-to-low transition on T0CKI pin<br>0 = Increment on low-to-high transition on T0CKI pin |                                           |                                        |                              |     |     |     |                                                   |

| bit 3:   | PSA: Prescaler Assignment bit<br>1 = Prescaler assigned to the WDT<br>0 = Prescaler assigned to Timer0                                                      |                                           |                                        |                              |     |     |     |                                                   |

| bit 2-0: | <b>PS&lt;2:0&gt;</b> : Pi                                                                                                                                   | rescaler Rate                             | Select b                               | its                          |     |     |     |                                                   |

|          |                                                                                                                                                             |                                           |                                        |                              |     |     |     |                                                   |

|          | Bit Value                                                                                                                                                   | Timer0 Rate                               | WDT                                    | Rate                         |     |     |     |                                                   |

|          | Bit Value                                                                                                                                                   | Timer0 Rate                               | WDT                                    |                              |     |     |     |                                                   |

|          |                                                                                                                                                             |                                           |                                        | 1                            |     |     |     |                                                   |

|          | 000                                                                                                                                                         | 1:2<br>1:4<br>1:8                         | 1:<br>1:<br>1:                         | 1<br>2<br>4                  |     |     |     |                                                   |

|          | 000                                                                                                                                                         | 1:2<br>1:4<br>1:8<br>1:16                 | 1:<br>1:<br>1:<br>1:                   | 1<br>2<br>4<br>8             |     |     |     |                                                   |

|          | 000<br>001<br>010<br>011<br>100                                                                                                                             | 1:2<br>1:4<br>1:8<br>1:16<br>1:32         | 1:<br>1:<br>1:<br>1:<br>1:             | 1<br>2<br>4<br>8<br>16       |     |     |     |                                                   |

|          | 000<br>001<br>010<br>011<br>100<br>101                                                                                                                      | 1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64 | 1:<br>1:<br>1:<br>1:<br>1:<br>1:       | 1<br>2<br>4<br>8<br>16<br>32 |     |     |     |                                                   |

|          | 000<br>001<br>010<br>011<br>100                                                                                                                             | 1:2<br>1:4<br>1:8<br>1:16<br>1:32         | 1:<br>1:<br>1:<br>1:<br>1:<br>1:<br>1: | 1<br>2<br>4<br>8<br>16<br>32 |     |     |     |                                                   |

# FIGURE 5-5: SUCCESSIVE I/O OPERATION

|                         | PC                   | PC + 1                             | PC + 2                          | V PC + 3                              |                                         |

|-------------------------|----------------------|------------------------------------|---------------------------------|---------------------------------------|-----------------------------------------|

| Instruction<br>fetched  | 1<br>1               | MOVF PORTB,W                       |                                 | NOP                                   | This example shows a write              |

| RB7:RB0                 | <u>۱</u>             | I                                  | X                               | ·                                     | to PORTB followed by a read from PORTB. |

|                         | 1<br> <br> <br> <br> | Port pin<br>written here           | Port pin<br>sampled here        | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |                                         |

| Instruction<br>executed |                      | MOVWF PORTB<br>(Write to<br>PORTB) | MOVF PORTB,W<br>(Read<br>PORTB) | NOP                                   |                                         |

|                         |                      | Write to                           | (Read                           |                                       | •                                       |

## FIGURE 6-2: ELECTRICAL STRUCTURE OF TOCKI PIN

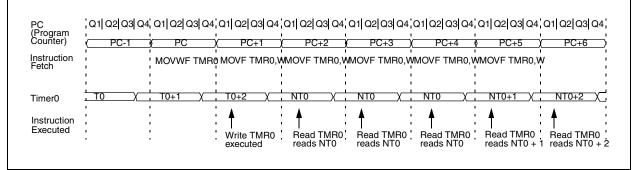

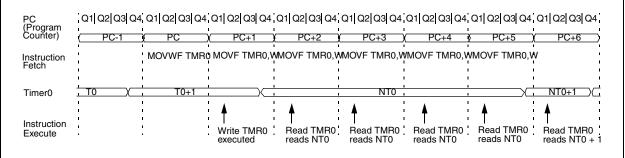

#### FIGURE 6-3: TIMER0 TIMING: INTERNAL CLOCK/NO PRESCALE

#### FIGURE 6-4: TIMER0 TIMING: INTERNAL CLOCK/PRESCALE 1:2

#### TABLE 6-1: REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7                                  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0     | Value on<br>Power-On<br>Reset | Value on<br>MCLR and<br>WDT Reset | Value on<br>Wake-up on<br>Pin Change | Value on<br>Brown-out<br>Reset |

|---------|--------|----------------------------------------|-------|-------|-------|-------|-------|-------|-----------|-------------------------------|-----------------------------------|--------------------------------------|--------------------------------|

| 01h     | TMR0   | Timer0 - 8-bit real-time clock/counter |       |       |       |       |       |       | XXXX XXXX | uuuu uuuu                     | uuuu uuuu                         | XXXX XXXX                            |                                |

| N/A     | OPTION | _                                      | -     | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0       | 11 1111                       | 11 1111                           | 11 1111                              | 11 1111                        |

Legend: Shaded cells: Unimplemented bits, - = unimplemented, x = unknown, u = unchanged.

#### 6.1 Using Timer0 with an External Clock

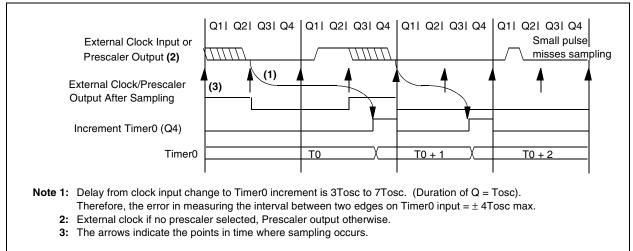

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 6.1.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple counter-type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### 6.1.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 6-5 shows the delay from the external clock edge to the timer incrementing.

## FIGURE 6-5: TIMER0 TIMING WITH EXTERNAL CLOCK

## TABLE 7-3: RESET CONDITIONS FOR SPECIAL REGISTERS

| Condition                        | PCL<br>Addr: 02h | STATUS<br>Addr: 03h      |

|----------------------------------|------------------|--------------------------|

| Power-on Reset                   | 1111 1111        | 1001 1xxx                |

| MCLR Reset (normal operation)    | 1111 1111        | u00u uuuu <sup>(1)</sup> |

| MCLR Wake-up (from SLEEP)        | 1111 1111        | 1001 Ouuu                |

| WDT Reset (normal operation)     | 1111 1111        | u000 luuu <sup>(2)</sup> |

| WDT Wake-up (from SLEEP)         | 1111 1111        | 1000 Ouuu                |

| Wake-up from SLEEP on Pin Change | 1111 1111        | 000u uuuu                |

| Brown-out Reset                  | 1111 1111        | x00x xxxx                |

Legend: u = unchanged, x = unknown, - = unimplemented read as '0'.

Note 1: TO and PD bits retain their last value until one of the other reset conditions occur.

**2:** The CLRWDT instruction will set the  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits.

## TABLE 7-4: RESET CONDITIONS FOR ALL REGISTERS

| Register                       | Address | Power-On Reset | MCLR or WDT<br>Reset | Wake-up on Pin<br>Change | Brown-out<br>Reset |

|--------------------------------|---------|----------------|----------------------|--------------------------|--------------------|

| W                              | N/A     | xxxx xxxx      | uuuu uuuu            | uuuu uuuu                | xxxx xxxx          |

| TRIS                           | N/A     | 1111 1111      | 1111 1111            | 1111 1111                | 1111 1111          |

| OPTION                         | N/A     | 11 1111        | 11 1111              | 11 1111                  | 11 1111            |

| OPTION2                        | N/A     | 11 1111        | uu uuuu              | uu uuuu                  | xx xxxx            |

| INDF                           | 00h     | XXXX XXXX      | uuuu uuuu            | uuuu uuuu                | xxxx xxxx          |

| TMR0                           | 01h     | XXXX XXXX      | uuuu uuuu            | uuuu uuuu                | xxxx xxxx          |

| PCL <sup>(1)</sup>             | 02h     | 1111 1111      | 1111 1111            | 1111 1111                | 1111 1111          |

| STATUS <sup>(1)</sup>          | 03h     | 1001 1xxx      | 100? ?uuu            | 000u uuuu                | x00x xxxx          |

| FSR                            | 04h     | 111x xxxx      | 111u uuuu            | 111u uuuu                | 111x xxxx          |

| PORTA                          | 05h     | xxxx           | uuuu                 | uuuu                     | xxxx               |

| PORTB                          | 06h     | xxxx xxxx      | uuuu uuuu            | uuuu uuuu                | xxxx xxxx          |

| General Purpose Register Files | 07-1Fh  | xxxx xxxx      | uuuu uuuu            | uuuu uuuu                | xxxx xxxx          |

Legend: u = unchanged, x = unknown, - = unimplemented, read as '0', q = see tables in Section 7.10 for possible values. ? = value depends on condition.

**Note 1:** See Table 7-3 for reset value for specific conditions.

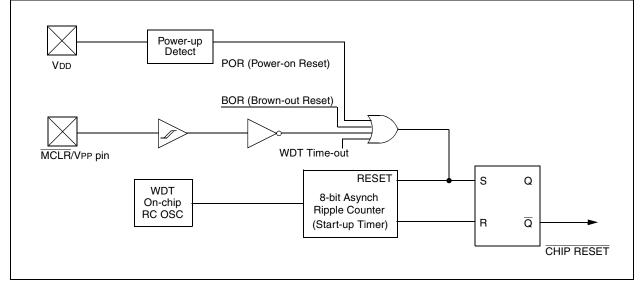

# FIGURE 7-6: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

© 2000 Microchip Technology Inc.

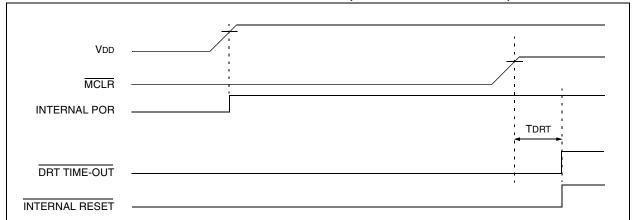

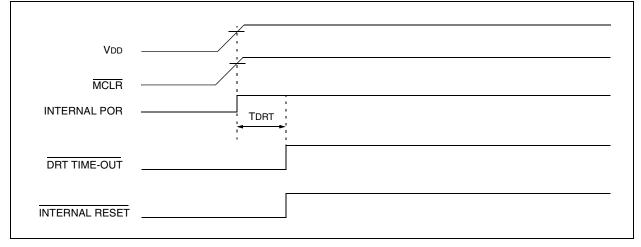

FIGURE 7-8: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD)

# FIGURE 7-9: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD): FAST VDD RISE TIME

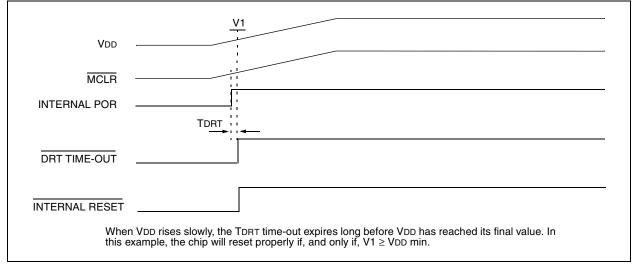

## FIGURE 7-10: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD): SLOW VDD RISE TIME

#### 7.11 Program Verification/Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip does not recommend code pro- |

|-------|----------------------------------------|

|       | tecting windowed devices.              |

# 7.12 ID Locations

Four memory locations are designated as ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution but are readable and writable during program/verify.

Use only the lower 4 bits of the ID locations and always program the upper 8 bits as '1's.

| Note: | Microchip will assign a unique pattern    |

|-------|-------------------------------------------|

|       | number for QTP and SQTP requests and      |

|       | for ROM devices. This pattern number will |

|       | be unique and traceable to the submitted  |

|       | code.                                     |

| Mnemonic,<br>Operands |        | <b>D</b>                     |        | 12-l | Bit Opc | ode  | Status        |       |

|-----------------------|--------|------------------------------|--------|------|---------|------|---------------|-------|

|                       |        | Description                  | Cycles | MSb  | MSb     |      | Affected      | Notes |

| ADDWF                 | f,d    | Add W and f                  | 1      | 0001 | 11df    | ffff | C,DC,Z        | 1,2,4 |

| ANDWF                 | f,d    | AND W with f                 | 1      | 0001 | 01df    | ffff | Z             | 2,4   |

| CLRF                  | f      | Clear f                      | 1      | 0000 | 011f    | ffff | Z             | 4     |

| CLRW                  | _      | Clear W                      | 1      | 0000 | 0100    | 0000 | Z             |       |

| COMF                  | f, d   | Complement f                 | 1      | 0010 | 01df    | ffff | Z             |       |

| DECF                  | f, d   | Decrement f                  | 1      | 0000 | 11df    | ffff | Z             | 2,4   |

| DECFSZ                | f, d   | Decrement f, Skip if 0       | 1(2)   | 0010 | 11df    | ffff | None          | 2,4   |

| INCF                  | f, d   | Increment f                  | 1      | 0010 | 10df    | ffff | Z             | 2,4   |

| INCFSZ                | f, d   | Increment f, Skip if 0       | 1(2)   | 0011 | 11df    | ffff | None          | 2,4   |

| IORWF                 | f, d   | Inclusive OR W with f        | 1      | 0001 | 00df    | ffff | Z             | 2,4   |

| MOVF                  | f, d   | Move f                       | 1      | 0010 | 00df    | ffff | Z             | 2,4   |

| MOVWF                 | f      | Move W to f                  | 1      | 0000 | 001f    | ffff | None          | 1,4   |

| NOP                   | _      | No Operation                 | 1      | 0000 | 0000    | 0000 | None          |       |

| RLF                   | f, d   | Rotate left f through Carry  | 1      | 0011 | 01df    | ffff | С             | 2,4   |

| RRF                   | f, d   | Rotate right f through Carry | 1      | 0011 | 00df    | ffff | С             | 2,4   |

| SUBWF                 | f, d   | Subtract W from f            | 1      | 0000 | 10df    | ffff | C,DC,Z        | 1,2,4 |

| SWAPF                 | f, d   | Swap f                       | 1      | 0011 | 10df    | ffff | None          | 2,4   |

| XORWF                 | f, d   | Exclusive OR W with f        | 1      | 0001 | 10df    | ffff | Z             | 2,4   |

| BIT-ORIENT            | ED FIL | E REGISTER OPERATIONS        |        |      |         |      |               |       |

| BCF                   | f, b   | Bit Clear f                  | 1      | 0100 | bbbf    | ffff | None          | 2,4   |

| BSF                   | f, b   | Bit Set f                    | 1      | 0101 | bbbf    | ffff | None          | 2,4   |

| BTFSC                 | f, b   | Bit Test f, Skip if Clear    | 1 (2)  | 0110 | bbbf    | ffff | None          |       |

| BTFSS                 | f, b   | Bit Test f, Skip if Set      | 1 (2)  | 0111 | bbbf    | ffff | None          |       |

| LITERAL A             | ND CON | ITROL OPERATIONS             |        |      |         |      |               |       |

| ANDLW                 | k      | AND literal with W           | 1      | 1110 | kkkk    | kkkk | Z             |       |

| CALL                  | k      | Call subroutine              | 2      | 1001 | kkkk    | kkkk | None          | 1     |

| CLRWDT                | k      | Clear Watchdog Timer         | 1      | 0000 | 0000    | 0100 | TO, PD        |       |

| GOTO                  | k      | Unconditional branch         | 2      | 101k | kkkk    | kkkk | None          |       |

| IORLW                 | k      | Inclusive OR Literal with W  | 1      | 1101 | kkkk    | kkkk | Z             |       |

| MOVLW                 | k      | Move Literal to W            | 1      | 1100 | kkkk    | kkkk | None          |       |

| OPTION                | k      | Load OPTION register         | 1      | 0000 | 0000    | 0010 | None          |       |

| RETLW                 | k      | Return, place Literal in W   | 2      | 1000 | kkkk    | kkkk | None          |       |

| SLEEP                 | _      | Go into standby mode         | 1      | 0000 | 0000    | 0011 | TO, PD, PCWUF |       |

| TRIS                  | f      | Load TRIS register           | 1      | 0000 | 0000    | Offf | None          | 3     |

| XORLW                 | k      | Exclusive OR Literal to W    | 1      | 1111 | kkkk    | kkkk | Z             | -     |

#### TABLE 8-2: INSTRUCTION SET SUMMARY

Note 1: The 9th bit of the program counter will be forced to a '0' by any instruction that writes to the PC except for GOTO. (See individual device data sheets, Memory Section/Indirect Data Addressing, INDF and FSR Registers)

2: When an I/O register is modified as a function of itself (e.g. MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

**3:** The instruction TRIS f, where f = 5 or 6 causes the contents of the W register to be written to the tristate latches of PORTA or B respectively. A '1' forces the pin to a hi-impedance state and disables the output buffers.

**4:** If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared (if assigned to TMR0).

| CALL                                                                                                               | Subroutine Call                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:                                                                                                            | [ <i>label</i> ] CALL k                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| Operands:                                                                                                          | $0 \le k \le 255$                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Operation:                                                                                                         | (PC) + 1 $\rightarrow$ Top of Stack;<br>k $\rightarrow$ PC<7:0>;<br>(STATUS<6:5>) $\rightarrow$ PC<10:9>;<br>0 $\rightarrow$ PC<8>                                                                                                                                |  |  |  |  |  |  |  |

| Status Affected:                                                                                                   | None                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| Encoding:                                                                                                          | 1001 kkkk kkkk                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| Description:                                                                                                       | Subroutine call. First, return address<br>(PC+1) is pushed onto the stack. The<br>eight bit immediate address is loaded<br>into PC bits <7:0>. The upper bits<br>PC<10:9> are loaded from STA-<br>TUS<6:5>, PC<8> is cleared. CALL is<br>a two cycle instruction. |  |  |  |  |  |  |  |

| Words:                                                                                                             | 1                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Cycles:                                                                                                            | 2                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Example:                                                                                                           | HERE CALL THERE                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| Before Instruction<br>PC = address (HERE)<br>After Instruction<br>PC = address (THERE)<br>TOS = address (HERE + 1) |                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| CLRF                                                                                                               | Clear f                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| Syntax:                                                                                                            | [label] CLRF f                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| Operands:                                                                                                          | $0 \le f \le 31$                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| Operation:                                                                                                         | $\begin{array}{l} 00h \rightarrow (f); \\ 1 \rightarrow Z \end{array}$                                                                                                                                                                                            |  |  |  |  |  |  |  |

| Status Affected:                                                                                                   | Z                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Encoding:                                                                                                          | 0000 011f ffff                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| Description:                                                                                                       | The contents of register 'f' are cleared<br>and the Z bit is set.                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Words:                                                                                                             | 1                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Cycles:                                                                                                            | 1                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Example:                                                                                                           | CLRF FLAG_REG                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| Before Instru<br>FLAG_RI                                                                                           |                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| After Instruct<br>FLAG_RI                                                                                          |                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| CLRW                                              | Clear W                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Syntax:                                           | [label] CLRW                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| Operands:                                         | None                                                                                                                                                        |  |  |  |  |  |  |  |  |  |

| Operation:                                        | $\begin{array}{l} 00h \rightarrow (W); \\ 1 \rightarrow Z \end{array}$                                                                                      |  |  |  |  |  |  |  |  |  |

| Status Affected:                                  | Z                                                                                                                                                           |  |  |  |  |  |  |  |  |  |

| Encoding:                                         | 0000 0100 0000                                                                                                                                              |  |  |  |  |  |  |  |  |  |

| Description:                                      | escription: The W register is cleared. Zero bit (Z) is set.                                                                                                 |  |  |  |  |  |  |  |  |  |

| Words:                                            | 1                                                                                                                                                           |  |  |  |  |  |  |  |  |  |

| Cycles:                                           | 1                                                                                                                                                           |  |  |  |  |  |  |  |  |  |

| Example:                                          | CLRW                                                                                                                                                        |  |  |  |  |  |  |  |  |  |

| Before Instruction<br>W = 0x5A                    |                                                                                                                                                             |  |  |  |  |  |  |  |  |  |

| After Instruct<br>W =<br>Z =                      | ion<br>0x00<br>1                                                                                                                                            |  |  |  |  |  |  |  |  |  |

| CLRWDT                                            | Clear Watchdog Timer                                                                                                                                        |  |  |  |  |  |  |  |  |  |

| Syntax:                                           | [label] CLRWDT                                                                                                                                              |  |  |  |  |  |  |  |  |  |

| Operands:                                         | None                                                                                                                                                        |  |  |  |  |  |  |  |  |  |

| Operation:                                        | 00h $\rightarrow$ WDT;<br>0 $\rightarrow$ WDT prescaler (if assigned);<br>1 $\rightarrow$ TO;<br>1 $\rightarrow$ PD                                         |  |  |  |  |  |  |  |  |  |

| Status Affected:                                  | TO, PD                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

| Encoding:                                         | 0000 0000 0100                                                                                                                                              |  |  |  |  |  |  |  |  |  |

| Description:                                      | The CLRWDT instruction resets the WDT. It also resets the prescaler, if the prescaler is assigned to the WDT and not Timer0. Status bits TO and PD are set. |  |  |  |  |  |  |  |  |  |

| Words:                                            | 1                                                                                                                                                           |  |  |  |  |  |  |  |  |  |

| Cycles:                                           | 1                                                                                                                                                           |  |  |  |  |  |  |  |  |  |

| Example:                                          | CLRWDT                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

| Before Instru<br>WDT cou                          |                                                                                                                                                             |  |  |  |  |  |  |  |  |  |

| After Instruct<br>WDT cou<br>WDT pres<br>TO<br>PD | nter = $0x00$                                                                                                                                               |  |  |  |  |  |  |  |  |  |

Z

= 1

| MOVF                      | Move f                                                                                       | MOVWF                               | Move W to f                             |  |  |  |  |  |

|---------------------------|----------------------------------------------------------------------------------------------|-------------------------------------|-----------------------------------------|--|--|--|--|--|

| Syntax:                   | [label] MOVF f,d                                                                             | Syntax:                             | [label] MOVWF f                         |  |  |  |  |  |

| Operands:                 | $0 \le f \le 31$                                                                             | $Operands: \qquad 0 \leq f \leq 31$ |                                         |  |  |  |  |  |

|                           | $d \in [0,1]$                                                                                | Operation: $(W) \rightarrow (f)$    |                                         |  |  |  |  |  |

| Operation:                | $(f) \rightarrow (dest)$                                                                     | Status Affected:                    | None                                    |  |  |  |  |  |

| Status Affected:          | Z                                                                                            | Encoding:                           | 0000 001f ffff                          |  |  |  |  |  |

| Encoding:                 | 0010 00df ffff                                                                               | Description:                        | Move data from the W register to regis- |  |  |  |  |  |

| Description:              | The contents of register 'f' is moved to                                                     | ·                                   | ter 'f'.                                |  |  |  |  |  |

|                           | destination 'd'. If 'd' is 0, destination is<br>the W register. If 'd' is 1, the destination | Words: 1                            |                                         |  |  |  |  |  |

|                           | is file register 'f'. 'd' is 1 is useful to test                                             | Cycles:                             | 1                                       |  |  |  |  |  |

|                           | a file register since status flag Z is affected.                                             | Example:                            | MOVWF TEMP_REG                          |  |  |  |  |  |

| Words:                    | 1                                                                                            | Before Instr                        |                                         |  |  |  |  |  |

| Cycles:                   | 1                                                                                            | TEMP_F<br>W                         | REG = 0xFF<br>= 0x4F                    |  |  |  |  |  |

| Example:                  | MOVF FSR, 0                                                                                  | After Instruc                       |                                         |  |  |  |  |  |

| After Instruc             |                                                                                              | TEMP_F                              |                                         |  |  |  |  |  |

| W = value in FSR register |                                                                                              | W                                   | = 0x4F                                  |  |  |  |  |  |

|                           |                                                                                              | NOP                                 | No Operation                            |  |  |  |  |  |

| MOVLW                     | Move Literal to W                                                                            | Syntax:                             | [label] NOP                             |  |  |  |  |  |

| Syntax:                   | [ <i>label</i> ] MOVLW k                                                                     | Operands:                           | None                                    |  |  |  |  |  |

| Operands:                 | $0 \le k \le 255$                                                                            | Operation:                          | No operation                            |  |  |  |  |  |

| Operation:                | $k \rightarrow (W)$                                                                          | Status Affected:                    | None                                    |  |  |  |  |  |

| Status Affected:          | None                                                                                         | Encoding:                           | 0000 0000 0000                          |  |  |  |  |  |

| Encoding:                 | 1100 kkkk kkkk                                                                               | Description:                        | No operation.                           |  |  |  |  |  |

| Description:              | The eight bit literal 'k' is loaded into the                                                 | Words:                              | 1                                       |  |  |  |  |  |

|                           | W register. The don't cares will assem-<br>ble as 0s.                                        | Cycles:                             | 1                                       |  |  |  |  |  |

| Words:                    | 1                                                                                            | Example:                            | NOP                                     |  |  |  |  |  |

| Cycles:                   | 1                                                                                            |                                     |                                         |  |  |  |  |  |

| Example:                  | MOVLW 0x5A                                                                                   |                                     |                                         |  |  |  |  |  |

| Example.                  |                                                                                              |                                     |                                         |  |  |  |  |  |

After Instruction W = 0x5

0x5A

#### 9.4 MPLINK/MPLIB Linker/Librarian

MPLINK is a relocatable linker for MPASM and MPLAB-C17 and MPLAB-C18. It can link relocatable objects from assembly or C source files along with precompiled libraries using directives from a linker script.

MPLIB is a librarian for pre-compiled code to be used with MPLINK. When a routine from a library is called from another source file, only the modules that contains that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications. MPLIB manages the creation and modification of library files.

MPLINK features include:

- MPLINK works with MPASM and MPLAB-C17 and MPLAB-C18.

- MPLINK allows all memory areas to be defined as sections to provide link-time flexibility.

MPLIB features include:

- MPLIB makes linking easier because single libraries can be included instead of many smaller files.

- MPLIB helps keep code maintainable by grouping related modules together.

- MPLIB commands allow libraries to be created and modules to be added, listed, replaced, deleted, or extracted.

#### 9.5 MPLAB-SIM Software Simulator

The MPLAB-SIM Software Simulator allows code development in a PC host environment by simulating the PICmicro series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file or user-defined key press to any of the pins. The execution can be performed in single step, execute until break, or trace mode.

MPLAB-SIM fully supports symbolic debugging using MPLAB-C17 and MPLAB-C18 and MPASM. The Software Simulator offers the flexibility to develop and debug code outside of the laboratory environment making it an excellent multi-project software development tool.

#### 9.6 MPLAB-ICE High Performance Universal In-Circuit Emulator with MPLAB IDE

The MPLAB-ICE Universal In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PICmicro microcontrollers (MCUs). Software control of MPLAB-ICE is provided by the MPLAB Integrated Development Environment (IDE), which allows editing, "make" and download, and source debugging from a single environment. Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB-ICE allows expansion to support new PICmicro microcontrollers.

The MPLAB-ICE Emulator System has been designed as a real-time emulation system with advanced features that are generally found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows 3.x/95/98 environment were chosen to best make these features available to you, the end user.

MPLAB-ICE 2000 is a full-featured emulator system with enhanced trace, trigger, and data monitoring features. Both systems use the same processor modules and will operate across the full operating speed range of the PICmicro MCU.

# 9.7 PICMASTER/PICMASTER CE

The PICMASTER system from Microchip Technology is a full-featured, professional quality emulator system. This flexible in-circuit emulator provides a high-quality, universal platform for emulating Microchip 8-bit PICmicro microcontrollers (MCUs). PICMASTER systems are sold worldwide, with a CE compliant model available for European Union (EU) countries.

# 9.8 ICEPIC

ICEPIC is a low-cost in-circuit emulation solution for the Microchip Technology PIC16C5X, PIC16C6X, PIC16C7X, and PIC16CXXX families of 8-bit one-timeprogrammable (OTP) microcontrollers. The modular system can support different subsets of PIC16C5X or PIC16CXXX products through the use of interchangeable personality modules or daughter boards. The emulator is capable of emulating without target application circuitry being present.

## 9.9 MPLAB-ICD In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB-ICD, is a powerful, low-cost run-time development tool. This tool is based on the flash PIC16F877 and can be used to develop for this and other PICmicro microcontrollers from the PIC16CXXX family. MPLAB-ICD utilizes the In-Circuit Debugging capability built into the PIC16F87X. This feature, along with Microchip's In-Circuit Serial Programming protocol, offers cost-effective in-circuit flash programming and debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by watching variables, single-stepping and setting break points. Running at full speed enables testing hardware in real-time. The MPLAB-ICD is also a programmer for the flash PIC16F87X family.

### 10.4 Timing Diagrams and Specifications

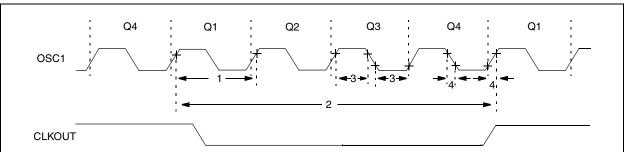

# FIGURE 10-2: EXTERNAL CLOCK TIMING - PIC16HV540

#### TABLE 10-1: EXTERNAL CLOCK TIMING REQUIREMENTS - PIC16HV540

| AC Characteristics                                  |       | Standard Operating Conditions (unless otherwise specified)              |      |                     |        |           |               |  |  |  |

|-----------------------------------------------------|-------|-------------------------------------------------------------------------|------|---------------------|--------|-----------|---------------|--|--|--|

|                                                     |       | Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ (commercial) |      |                     |        |           |               |  |  |  |

| $-40^{\circ}C \le TA \le +85^{\circ}C$ (industrial) |       |                                                                         |      |                     |        |           |               |  |  |  |

| Parameter<br>No.                                    | Sym.  | Characteristic                                                          |      | Typ. <sup>(1)</sup> | Max.   | Unit<br>s | Conditions    |  |  |  |

|                                                     | Fosc  | External CLKIN Frequency <sup>(2)</sup>                                 | DC   | _                   | 4.0    | MHz       | RC osc mode   |  |  |  |

|                                                     |       |                                                                         | DC   | _                   | 2.0    | MHz       | HS osc mode   |  |  |  |

|                                                     |       |                                                                         | DC   | _                   | 4.0    | MHz       | XT osc mode   |  |  |  |

|                                                     |       |                                                                         | DC   | _                   | 200    | kHz       | LP osc mode   |  |  |  |

|                                                     |       | Oscillator Frequency <sup>(2)</sup>                                     | DC   | _                   | 4.0    | MHz       | RC osc mode   |  |  |  |

|                                                     |       |                                                                         | 0.1  | —                   | 2.0    | MHz       | HS osc mode   |  |  |  |

|                                                     |       |                                                                         | 0.1  | —                   | 4.0    | MHz       | XT osc mode   |  |  |  |

|                                                     |       |                                                                         | 5    | —                   | 200    | kHz       | LP osc mode   |  |  |  |

| 1                                                   | Tosc  | External CLKIN Period <sup>(2)</sup>                                    | 250  | _                   | _      | ns        | RC osc mode   |  |  |  |

|                                                     |       |                                                                         | 250  | —                   | —      | ns        | HS osc mode   |  |  |  |

|                                                     |       |                                                                         | 250  | —                   | —      | ns        | XT osc mode   |  |  |  |

|                                                     |       |                                                                         | 5.0  | —                   | —      | μs        | LP osc mode   |  |  |  |

|                                                     |       | Oscillator Period <sup>(2)</sup>                                        | 250  | _                   | _      | ns        | RC osc mode   |  |  |  |

|                                                     |       |                                                                         | 250  | —                   | 10,000 | ns        | HS osc mode   |  |  |  |

|                                                     |       |                                                                         | 250  | —                   | 10,000 | ns        | XT osc mode   |  |  |  |

|                                                     |       |                                                                         | 50   | —                   | 200    | μs        | LP osc mode   |  |  |  |

| 2                                                   | Тсү   | Instruction Cycle Time <sup>(3)</sup>                                   | —    | 4/Fosc              | _      | _         |               |  |  |  |

| 3                                                   | TosL, | Clock in (OSC1) Low or High Time                                        | 50*  | —                   | —      | ns        | XT oscillator |  |  |  |

|                                                     | TosH  |                                                                         | 20*  | —                   | —      | ns        | HS oscillator |  |  |  |

|                                                     |       |                                                                         | 2.0* | —                   | —      | μs        | LP oscillator |  |  |  |

| 4                                                   | TosR, | Clock in (OSC1) Rise or Fall Time                                       | —    | _                   | 25*    | ns        | XT oscillator |  |  |  |

|                                                     | TosF  |                                                                         | —    | —                   | 25*    | ns        | HS oscillator |  |  |  |

|                                                     |       |                                                                         | —    | —                   | 50*    | ns        | LP oscillator |  |  |  |

\* These parameters are characterized but not tested.

**Note 1:** Data in the Typical ("Typ") column is at VREG = 5V, VDD = 9V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

2: All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption.

When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

**3:** Instruction cycle period (TCY) equals four times the input oscillator time base period.

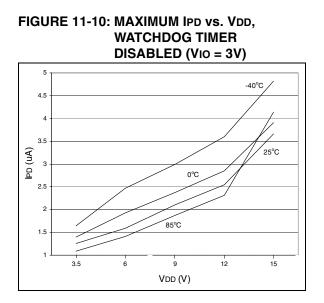

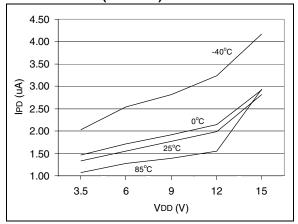

FIGURE 11-11: TYPICAL IPD vs. VDD, WATCHDOG TIMER ENABLED (VIO = 3V)

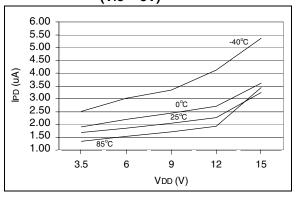

FIGURE 11-12: MAXIMUM IPD vs. VDD, WATCHDOG TIMER ENABLED (VIO = 3V)

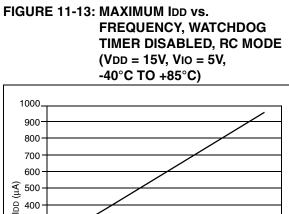

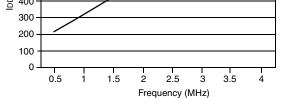

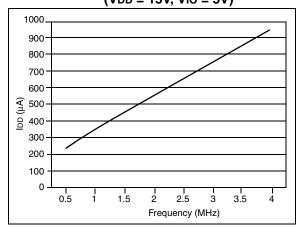

#### FIGURE 11-14: MAXIMUM IDD vs. FREQUENCY, WATCHDOG TIMER ENABLED, RC MODE (VDD = 15V, VIO = 5V)

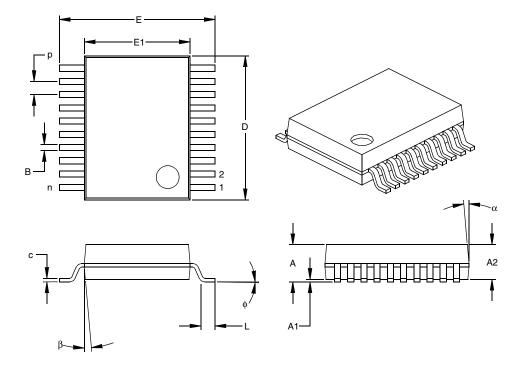

# 12.4 20-Lead Plastic Shrink Small Outline (SS) - 209 mil, 5.30 mm (SSOP)

|                          | Units  |      | INCHES* |      | N    | IILLIMETERS | ;      |

|--------------------------|--------|------|---------|------|------|-------------|--------|

| Dimension                | Limits | MIN  | NOM     | MAX  | MIN  | NOM         | MAX    |

| Number of Pins           | n      |      | 20      |      |      | 20          |        |

| Pitch                    | р      |      | .026    |      |      | 0.65        |        |

| Overall Height           | Α      | .068 | .073    | .078 | 1.73 | 1.85        | 1.98   |

| Molded Package Thickness | A2     | .064 | .068    | .072 | 1.63 | 1.73        | 1.83   |

| Standoff §               | A1     | .002 | .006    | .010 | 0.05 | 0.15        | 0.25   |

| Overall Width            | E      | .299 | .309    | .322 | 7.59 | 7.85        | 8.18   |

| Molded Package Width     | E1     | .201 | .207    | .212 | 5.11 | 5.25        | 5.38   |

| Overall Length           | D      | .278 | .284    | .289 | 7.06 | 7.20        | 7.34   |

| Foot Length              | L      | .022 | .030    | .037 | 0.56 | 0.75        | 0.94   |

| Lead Thickness           | С      | .004 | .007    | .010 | 0.10 | 0.18        | 0.25   |

| Foot Angle               | φ      | 0    | 4       | 8    | 0.00 | 101.60      | 203.20 |

| Lead Width               | В      | .010 | .013    | .015 | 0.25 | 0.32        | 0.38   |

| Mold Draft Angle Top     | α      | 0    | 5       | 10   | 0    | 5           | 10     |

| Mold Draft Angle Bottom  |        | 0    | 5       | 10   | 0    | 5           | 10     |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side.

JEDEC Equivalent: MO-150

Drawing No. C04-072

NOTES:

# WORLDWIDE SALES AND SERVICE

#### AMERICAS

**Corporate Office** 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: 480-792-7627 Web Address: http://www.microchip.com

#### **Rocky Mountain**

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7966 Fax: 480-792-7456

#### Atlanta

500 Sugar Mill Road, Suite 200B Atlanta, GA 30350 Tel: 770-640-0034 Fax: 770-640-0307

#### Boston

2 Lan Drive, Suite 120 Westford, MA 01886 Tel: 978-692-3848 Fax: 978-692-3821

#### Chicago

333 Pierce Road, Suite 180 Itasca, IL 60143 Tel: 630-285-0071 Fax: 630-285-0075

Dallas

4570 Westgrove Drive, Suite 160 Addison, TX 75001 Tel: 972-818-7423 Fax: 972-818-2924

Detroit Tri-Atria Office Building 32255 Northwestern Highway, Suite 190

Farmington Hills, MI 48334 Tel: 248-538-2250 Fax: 248-538-2260 Kokomo

# 2767 S. Albright Road Kokomo, Indiana 46902 Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles

18201 Von Karman, Suite 1090 Irvine, CA 92612

Tel: 949-263-1888 Fax: 949-263-1338 New York

150 Motor Parkway, Suite 202 Hauppauge, NY 11788 Tel: 631-273-5305 Fax: 631-273-5335

#### San Jose

Microchip Technology Inc. 2107 North First Street, Suite 590 San Jose, CA 95131 Tel: 408-436-7950 Fax: 408-436-7955

Toronto

6285 Northam Drive, Suite 108 Mississauga, Ontario L4V 1X5, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Australia

Microchip Technology Australia Pty Ltd Suite 22, 41 Rawson Street Epping 2121, NSW Australia

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755 China - Beijing

Microchip Technology Consulting (Shanghai) Co., Ltd., Beijing Liaison Office Unit 915 Bei Hai Wan Tai Bldg. No. 6 Chaoyangmen Beidajie Beijing, 100027, No. China Tel: 86-10-85282100 Fax: 86-10-85282104

#### China - Chengdu

Microchip Technology Consulting (Shanghai) Co., Ltd., Chengdu Liaison Office Rm. 2401, 24th Floor, Ming Xing Financial Tower No. 88 TIDU Street Chengdu 610016, China Tel: 86-28-6766200 Fax: 86-28-6766599

#### China - Fuzhou

Microchip Technology Consulting (Shanghai) Co., Ltd., Fuzhou Liaison Office Unit 28F, World Trade Plaza No. 71 Wusi Road Fuzhou 350001, China Tel: 86-591-7503506 Fax: 86-591-7503521 China - Shanghai

Microchip Technology Consulting (Shanghai) Co., Ltd. Room 701, Bldg. B Far East International Plaza No. 317 Xian Xia Road Shanghai, 200051 Tel: 86-21-6275-5700 Fax: 86-21-6275-5060

#### China - Shenzhen

Microchip Technology Consulting (Shanghai) Co., Ltd., Shenzhen Liaison Office Rm. 1315, 13/F, Shenzhen Kerry Centre, Renminnan Lu Shenzhen 518001, China Tel: 86-755-2350361 Fax: 86-755-2366086 Hong Kong Microchip Technology Hongkong Ltd. Unit 901-6, Tower 2, Metroplaza

223 Hing Fong Road Kwai Fong, N.T., Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431

#### India

Microchip Technology Inc. India Liaison Office **Divvasree Chambers** 1 Floor, Wing A (A3/A4) No. 11, O'Shaugnessey Road Bangalore, 560 025, India Tel: 91-80-2290061 Fax: 91-80-2290062

#### Japan

Microchip Technology Japan K.K. Benex S-1 6F 3-18-20, Shinyokohama Kohoku-Ku, Yokohama-shi Kanagawa, 222-0033, Japan Tel: 81-45-471- 6166 Fax: 81-45-471-6122 Korea Microchip Technology Korea 168-1, Youngbo Bldg. 3 Floor Samsung-Dong, Kangnam-Ku Seoul, Korea 135-882 Tel: 82-2-554-7200 Fax: 82-2-558-5934 Singapore Microchip Technology Singapore Pte Ltd. 200 Middle Road #07-02 Prime Centre Singapore, 188980 Tel: 65-6334-8870 Fax: 65-6334-8850 Taiwan Microchip Technology Taiwan 11F-3, No. 207 Tung Hua North Road Taipei, 105, Taiwan Tel: 886-2-2717-7175 Fax: 886-2-2545-0139

#### EUROPE

Denmark

Microchip Technology Nordic ApS **Regus Business Centre** Lautrup hoj 1-3 Ballerup DK-2750 Denmark Tel: 45 4420 9895 Fax: 45 4420 9910 France Microchip Technology SARL Parc d'Activite du Moulin de Massy 43 Rue du Saule Trapu Batiment A - ler Etage 91300 Massy, France Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79 Germany Microchip Technology GmbH

Gustav-Heinemann Ring 125 D-81739 Munich, Germany Tel: 49-89-627-144 0 Fax: 49-89-627-144-44 Italy

Microchip Technology SRL Centro Direzionale Colleoni Palazzo Taurus 1 V. Le Colleoni 1 20041 Agrate Brianza Milan, Italy Tel: 39-039-65791-1 Fax: 39-039-6899883

#### United Kinadom

Arizona Microchip Technology Ltd. 505 Eskdale Road Winnersh Triangle Wokingham Berkshire, England RG41 5TU Tel: 44 118 921 5869 Fax: 44-118 921-5820

03/01/02