# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                    |

|----------------------------|--------------------------------------------------------------------|

| Product Status             | Obsolete                                                           |

| Core Processor             | ST6                                                                |

| Core Size                  | 8-Bit                                                              |

| Speed                      | 8MHz                                                               |

| Connectivity               | -                                                                  |

| Peripherals                | LVD, POR, WDT                                                      |

| Number of I/O              | 12                                                                 |

| Program Memory Size        | 2KB (2K x 8)                                                       |

| Program Memory Type        | ОТР                                                                |

| EEPROM Size                | -                                                                  |

| RAM Size                   | 64 x 8                                                             |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6V                                                            |

| Data Converters            | A/D 8x8b                                                           |

| Oscillator Type            | Internal                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                  |

| Mounting Type              | Through Hole                                                       |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                            |

| Supplier Device Package    | -                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st62t10cb6 |

|                            |                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

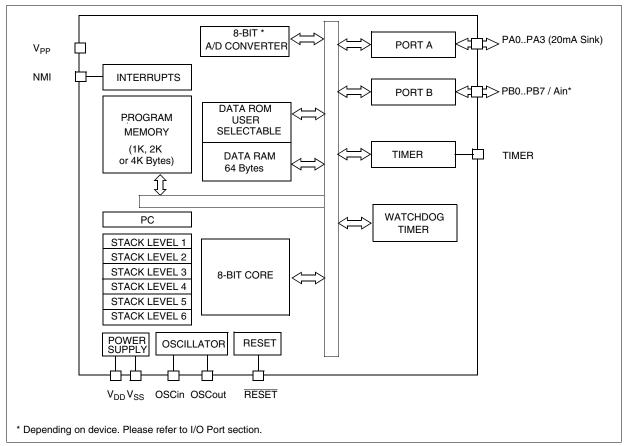

## **1 INTRODUCTION**

The ST6208C, 09C, 10C and 20C devices are low cost members of the ST62xx 8-bit HCMOS family of microcontrollers, which is targeted at low to medium complexity applications. All ST62xx devices are based on a building block approach: a common core is surrounded by a number of on-chip peripherals.

The ST62E20C is the erasable EPROM version of the ST62T08C, T09C, T10C and T20C devices, which may be used during the development phase for the ST62T08C, T09C, T10C and T20C target devices, as well as the respective ST6208C, 09C, 10C and 20C ROM devices.

OTP and EPROM devices are functionally identical. OTP devices offer all the advantages of user programmability at low cost, which make them the ideal choice in a wide range of applications where frequent code changes, multiple code versions or last minute programmability are required.

The ROM based versions offer the same functionality, selecting the options defined in the programmable option bytes of the OTP/EPROM versions in the ROM option list (See Section 11.6 on page 96).

The ST62P08C/P09C/P10C/P20C are the **F**actory **A**dvanced **S**ervice **T**echnique ROM (FASTROM) versions of ST62T08C, T09C, T10C and T20C OTP devices.

They offer the same functionality as OTP devices, but they do not have to be programmed by the customer (See Section 11 on page 90).

These compact low-cost devices feature a Timer comprising an 8-bit counter with a 7-bit programmable prescaler, an 8-bit A/D Converter with up to 8 analog inputs (depending on device) and a Digital Watchdog timer, making them well suited for a wide range of automotive, appliance and industrial applications.

For easy reference, all parametric data are located in Section 11 on page 90.

47/

#### Figure 1. Block Diagram

## **2 PIN DESCRIPTION**

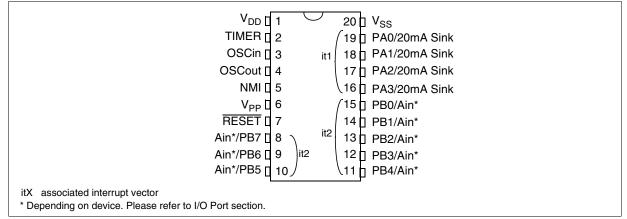

#### Figure 2. 20-Pin Package Pinout

#### Table 1. Device Pin Description

| Pin n° | Pin Name        | Type | Main Function<br>(after Reset)                                                                                 | Alternate Function |  |  |

|--------|-----------------|------|----------------------------------------------------------------------------------------------------------------|--------------------|--|--|

| 1      | V <sub>DD</sub> | S    | Main power supply                                                                                              |                    |  |  |

| 2      | TIMER           | I/O  | Timer input or output                                                                                          |                    |  |  |

| 3      | OSCin           | I    | External clock input or resonator oscillator inverter inp                                                      | put                |  |  |

| 4      | OSCout          | 0    | Resonator oscillator inverter output or resistor input for                                                     | or RC oscillator   |  |  |

| 5      | NMI             | Ι    | Non maskable interrupt (falling edge sensitive)                                                                |                    |  |  |

| 6      | V <sub>PP</sub> |      | Must be held at Vss for normal operation, if a 12.5V le<br>during the reset phase, the device enters EPROM pro |                    |  |  |

| 7      | RESET           | I/O  | Top priority non maskable interrupt (active low)                                                               |                    |  |  |

| 8      | PB7/Ain*        | I/O  | Pin B7 (IPU)                                                                                                   | Analog input       |  |  |

| 9      | PB6/Ain*        | I/O  | Pin B6 (IPU)                                                                                                   | Analog input       |  |  |

| 10     | PB5/Ain*        | I/O  | Pin B5 (IPU)                                                                                                   | Analog input       |  |  |

| 11     | PB4/Ain*        | I/O  | Pin B4 (IPU)                                                                                                   | Analog input       |  |  |

| 12     | PB3/Ain*        | I/O  | Pin B3 (IPU)                                                                                                   | Analog input       |  |  |

| 13     | PB2/Ain*        | I/O  | Pin B2 (IPU)                                                                                                   | Analog input       |  |  |

| 14     | PB1/Ain*        | I/O  | Pin B1 (IPU)                                                                                                   | Analog input       |  |  |

| 15     | PB0/Ain*        | I/O  | Pin B0 (IPU)                                                                                                   | Analog input       |  |  |

| 16     | PA3/ 20mA Sink  | I/O  | Pin A3 (IPU)                                                                                                   |                    |  |  |

| 17     | PA2/ 20mA Sink  | I/O  | Pin A2 (IPU)                                                                                                   |                    |  |  |

| 18     | PA1/20mA Sink   | I/O  | Pin A1 (IPU)                                                                                                   |                    |  |  |

## **4 CENTRAL PROCESSING UNIT**

#### **4.1 INTRODUCTION**

The CPU Core of ST6 devices is independent of the I/O or Memory configuration. As such, it may be thought of as an independent central processor communicating with on-chip I/O, Memory and Peripherals via internal address, data, and control buses.

#### **4.2 MAIN FEATURES**

- 40 basic instructions

- 9 main addressing modes

- Two 8-bit index registers

- Two 8-bit short direct registers

- Low power modes

- Maskable hardware interrupts

- 6-level hardware stack

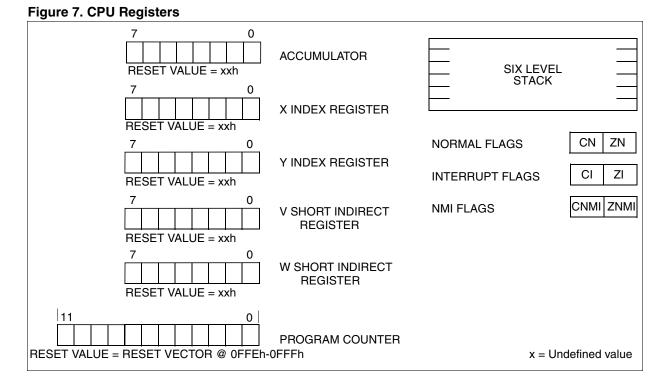

#### 4.3 CPU REGISTERS

<u>ل</u>حک

The ST6 Family CPU core features six registers and three pairs of flags available to the programmer. These are described in the following paragraphs.

Accumulator (A). The accumulator is an 8-bit general purpose register used in all arithmetic calculations, logical operations, and data manipulations. The accumulator can be addressed in Data Space as a RAM location at address FFh. Thus the ST6 can manipulate the accumulator just like any other register in Data Space.

**Index Registers (X, Y).** These two registers are used in Indirect addressing mode as pointers to memory locations in Data Space. They can also be accessed in Direct, Short Direct, or Bit Direct addressing modes. They are mapped in Data Space at addresses 80h (X) and 81h (Y) and can be accessed like any other memory location.

**Short Direct Registers (V, W).** These two registers are used in Short Direct addressing mode. This means that the data stored in V or W can be accessed with a one-byte instruction (four CPU cycles). V and W can also be accessed using Direct and Bit Direct addressing modes. They are mapped in Data Space at addresses 82h (V) and 83h (W) and can be accessed like any other memory location.

**Note**: The X and Y registers can also be used as Short Direct registers in the same way as V and W.

**Program Counter (PC)**. The program counter is a 12-bit register which contains the address of the next instruction to be executed by the core. This ROM location may be an opcode, an operand, or the address of an operand.

#### RESET (Cont'd)

#### 5.3.4 Watchdog Reset

The MCU provides a Watchdog timer function in order to be able to recover from software hangups. If the Watchdog register is not refreshed before an end-of-count condition is reached, a Watchdog reset is generated.

After a Watchdog reset, the MCU restarts in the same way as if a Reset was generated by the RE-SET pin.

**Note:** When a watchdog reset occurs, the **RESET** pin is tied low for very short time period, to flag the reset phase. This time is not long enough to reset external circuits.

For more details refer to the Watchdog Timer chapter.

#### 5.3.5 LVD Reset

Two different RESET sequences caused by the internal LVD circuitry can be distinguished:

- Power-On RESET

- Voltage Drop RESET

During an LVD reset, the  $\overline{\text{RESET}}$  pin is pulled low when  $V_{DD} < V_{IT+}$  (rising edge) or  $V_{DD} < V_{IT-}$  (falling edge).

For more details, refer to the LVD chapter.

**<u>Caution</u>**: Do not externally connect directly the RESET pin to  $V_{DD}$ , this may cause damage to the component in case of internal RESET (Watchdog or LVD).

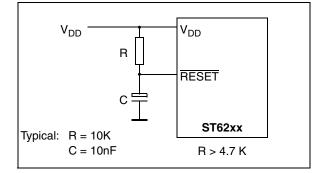

#### Figure 15. Simple External Reset Circuitry

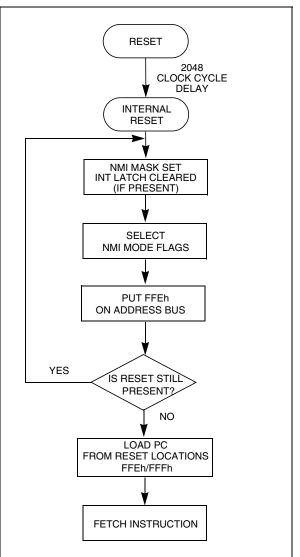

#### Figure 16. Reset Processing

## 5.5 INTERRUPT RULES AND PRIORITY MANAGEMENT

- A Reset can interrupt the NMI and peripheral interrupt routines

- The Non Maskable Interrupt request has the highest priority and can interrupt any peripheral interrupt routine at any time but cannot interrupt another NMI interrupt.

- No peripheral interrupt can interrupt another. If more than one interrupt request is pending, these are processed by the processor core according to their priority level: vector #1 has the highest priority while vector #4 the lowest. The priority of each interrupt source is fixed by hardware (see Interrupt Mapping table).

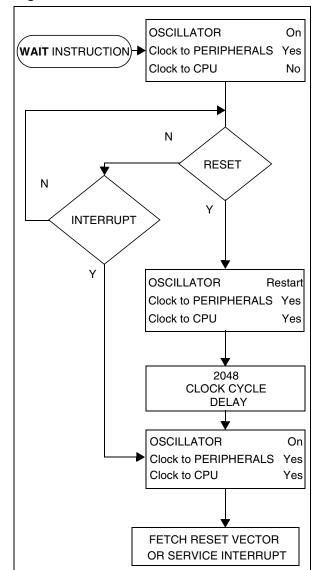

#### 5.6 INTERRUPTS AND LOW POWER MODES

All interrupts cause the processor to exit from WAIT mode. Only the external and some specific interrupts from the on-chip peripherals cause the processor to exit from STOP mode (refer to the "Exit from STOP" column in the Interrupt Mapping Table).

#### **5.7 NON MASKABLE INTERRUPT**

This interrupt is triggered when a falling edge occurs on the NMI pin regardless of the state of the GEN bit in the IOR register. An interrupt request on NMI vector #0 is latched by a flip flop which is automatically reset by the core at the beginning of the NMI service routine.

#### **5.8 PERIPHERAL INTERRUPTS**

Different peripheral interrupt flags in the peripheral control registers are able to cause an interrupt when they are active if both:

- The GEN bit of the IOR register is set

- The corresponding enable bit is set in the peripheral control register.

Peripheral interrupts are linked to vectors #3 and #4. Interrupt requests are flagged by a bit in their corresponding control register. This means that a request cannot be lost, because the flag bit must be cleared by user software.

#### 6.2 WAIT MODE

The MCU goes into WAIT mode as soon as the WAIT instruction is executed. This has the following effects:

- Program execution is stopped, the microcontroller software can be considered as being in a "frozen" state.

- RAM contents and peripheral registers are preserved as long as the power supply voltage is higher than the RAM retention voltage.

- The oscillator is kept running to provide a clock to the peripherals; they are still active.

WAIT mode can be used when the user wants to reduce the MCU power consumption during idle periods, while not losing track of time or the ability to monitor external events. WAIT mode places the MCU in a low power consumption mode by stopping the CPU. The active oscillator (main oscillator or LFAO) is kept running in order to provide a clock signal to the peripherals.

If the power consumption has to be further reduced, the Low Frequency Auxiliary Oscillator (LFAO) can be used in place of the main oscillator, if its operating frequency is lower. If required, the LFAO must be switched on before entering WAIT mode.

#### Exit from Wait mode

The MCU remains in WAIT mode until one of the following events occurs:

- RESET (Watchdog, LVD or RESET pin)

- A peripheral interrupt (timer, ADC,...),

- An external interrupt (I/O port, NMI)

The Program Counter then branches to the starting address of the interrupt or RESET service routine. Refer to Figure 20.

See also Section 6.4.1.

<u>ل</u>حک

#### Figure 20. WAIT Mode Flowchart

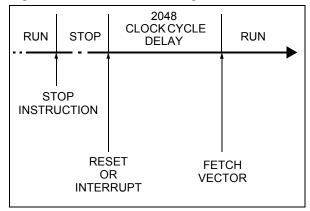

#### 6.3 STOP MODE

STOP mode is the lowest power consumption mode of the MCU (see Figure 22).

The MCU goes into STOP mode as soon as the STOP instruction is executed. This has the following effects:

- Program execution is stopped, the microcontroller can be considered as being "frozen".

- The contents of RAM and the peripheral registers are kept safely as long as the power supply voltage is higher than the RAM retention voltage.

- The oscillator is stopped, so peripherals cannot work except the those that can be driven by an external clock.

#### Exit from STOP Mode

The MCU remains in STOP mode until one of the following events occurs:

- RESET (Watchdog, LVD or RESET pin)

- A peripheral interrupt (assuming this peripheral can be driven by an external clock)

- An external interrupt (I/O port, NMI)

In all cases a delay of 2048 clock cycles  $(f_{\text{INT}})$  is generated to make sure the oscillator has started properly.

The Program Counter then points to the starting address of the interrupt or RESET service routine (see Figure 21).

#### **STOP Mode and Watchdog**

When the Watchdog is active (hardware or software activation), the STOP instruction is disabled and a WAIT instruction will be executed in its place unless the EXCTNL option bit is set to 1 in the option bytes and a a high level is present on the NMI pin. In this case, the STOP instruction will be executed and the Watchdog will be frozen.

#### 6.4 NOTES RELATED TO WAIT AND STOP MODES

#### 6.4.1 Exit from Wait and Stop Modes

#### 6.4.1.1 NMI Interrupt

It should be noted that when the GEN bit in the IOR register is low (interrupts disabled), the NMI interrupt is active but cannot cause a wake up from STOP/WAIT modes.

#### 6.4.1.2 Restart Sequence

When the MCU exits from WAIT or STOP mode, it should be noted that the restart sequence depends on the original state of the MCU (normal, interrupt or non-maskable interrupt mode) prior to entering WAIT or STOP mode, as well as on the interrupt type.

**Normal Mode.** If the MCU was in the main routine when the WAIT or STOP instruction was executed, exit from Stop or Wait mode will occur as soon as an interrupt occurs; the related interrupt routine is executed and, on completion, the instruction which follows the STOP or WAIT instruction is then executed, providing no other interrupts are pending.

**Non Maskable Interrupt Mode.** If the STOP or WAIT instruction has been executed during execution of the non-maskable interrupt routine, the MCU exits from Stop or Wait mode as soon as an interrupt occurs: the instruction which follows the STOP or WAIT instruction is executed, and the MCU remains in non-maskable interrupt mode, even if another interrupt has been generated.

**Normal Interrupt Mode.** If the MCU was in interrupt mode before the STOP or WAIT instruction was executed, it exits from STOP or WAIT mode as soon as an interrupt occurs. Nevertheless, two cases must be considered:

- If the interrupt is a normal one, the interrupt routine in which the WAIT or STOP mode was entered will be completed, starting with the execution of the instruction which follows the STOP or the WAIT instruction, and the MCU is still in interrupt mode. At the end of this routine pending interrupts will be serviced according to their priority.

- In the event of a non-maskable interrupt, the non-maskable interrupt service routine is processed first, then the routine in which the WAIT or STOP mode was entered will be completed by executing the instruction following the STOP or WAIT instruction. The MCU remains in normal interrupt mode.

#### 6.4.2 Recommended MCU Configuration

For lowest power consumption during RUN or WAIT modes, the user software must configure the MCU as follows:

- Configure unused I/Os as output push-pull low mode

- Place all peripherals in their power down modes before entering STOP mode

- Select the Low Frequency Auxiliary Oscillator (provided this runs at a lower frequency than the main oscillator).

The WAIT and STOP instructions are not executed if an enabled interrupt request is pending.

I/O PORTS (Cont'd)

#### 7.5 REGISTER DESCRIPTION

#### DATA REGISTER (DR)

Port x Data Register DRx with x = A or B. Address DRA: 0C0h - Read/Write Address DRB: 0C1h - Read/Write Reset Value: 0000 0000 (00h)

| 7  |    |    |    |    |    |    | 0  |

|----|----|----|----|----|----|----|----|

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

Bits 7:0 = **D**[7:0] *Data register bits.*

Reading the DR register returns either the DR register latch content (pin configured as output) or the digital value applied to the I/O pin (pin configured as input).

**Caution:** In input mode, modifying this register will modify the I/O port configuration (see Table 9).

Do not use the Single bit instructions on I/O port data registers. See (Section 7.2.5).

#### DATA DIRECTION REGISTER (DDR)

Port x Data Direction Register DDRx with x = A or B.

**67/**

Address DDRA: 0C4h - Read/Write Address DDRB: 0C5h - Read/Write Reset Value: 0000 0000 (00h)

| 7   |     |     |     |     |     |     | 0   |  |

|-----|-----|-----|-----|-----|-----|-----|-----|--|

| DD7 | DD6 | DD5 | DD4 | DD3 | DD2 | DD1 | DD0 |  |

#### Table 11. I/O Port Register Map and Reset Values

#### Bits 7:0 = **DD[7:0]** Data direction register bits.

The DDR register gives the input/output direction configuration of the pins. Each bit is set and cleared by software. 0: Input mode 1: Output mode

#### **OPTION REGISTER (OR)**

Port x Option Register ORx with x = A or B. Address ORA: 0CCh - Read/Write Address ORB: 0CDh - Read/Write Reset Value: 0000 0000 (00h)

| 7  |    |    |    |    |    |    | 0  |  |

|----|----|----|----|----|----|----|----|--|

| 07 | O6 | O5 | 04 | O3 | O2 | O1 | O0 |  |

#### Bits 7:0 = **O**[7:0] Option register bits.

The OR register allows to distinguish in output mode if the push-pull or open drain configuration is selected.

Output mode:

0: Open drain output(with P-Buffer deactivated)1: Push-pull Output

Input mode: See Table 9.

Each bit is set and cleared by software.

**Caution:** Modifying this register, will also modify the I/O port configuration in input mode. (see Table 9).

| Address<br>(Hex.) | Register<br>Label        | 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|-------------------|--------------------------|-------|---|---|---|---|---|---|-----|

|                   | t Value<br>ort registers | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0   |

| 0C0h              | DRA                      | MSB   |   |   |   |   |   |   | LSB |

| 0C1h              | DRB                      | IVISD |   |   |   |   |   |   | LOD |

| 0C4h              | DDRA                     | MSB   |   |   |   |   |   |   | LSB |

| 0C5h              | DDRB                     | IVISD |   |   |   |   |   |   | LOD |

| 0CCh              | ORA                      | MSB   |   |   |   |   |   |   | LSB |

| 0CDh              | ORB                      | IVIOD |   |   |   |   |   |   | LOD |

#### WATCHDOG TIMER (Cont'd)

#### 8.1.7 Register Description

#### WATCHDOG REGISTER (WDGR)

Address: 0D8h - Read/Write

Reset Value: 1111 1110 (FEh)

| 7  |    |    |    |    |    |    | 0 |

|----|----|----|----|----|----|----|---|

| то | T1 | T2 | Т3 | T4 | T5 | SR | С |

#### Bits 7:2 = T[5:0] Downcounter bits

**Caution:** These bits are reversed and shifted with respect to the physical counter: bit-7 (T0) is the LSB of the Watchdog downcounter and bit-2 (T5) is the MSB.

#### Bit 1 = SR: Software Reset bit

<u>ل</u>رک

Software can generate a reset by clearing this bit while the C bit is set. When C = 0 (Watchdog deactivated) the SR bit is the MSB of the 7-bit timer. 0: Generate (write)

1: No software reset generated, MSB of 7-bit timer

#### Bit 0 = **C** Watchdog Control bit.

If the hardware option is selected (WDACT bit in Option byte), this bit is forced high and cannot be changed by the user (the Watchdog is always active). When the software option is selected (WDACT bit in Option byte), the Watchdog function is activated by setting the C bit, and cannot then be deactivated (except by resetting the MCU).

When C is kept cleared the counter can be used as a 7-bit timer.

0: Watchdog deactivated

1: Watchdog activated

## A/D CONVERTER (Cont'd)

#### 8.3.5 Low Power Modes

| Mode | Description                                                                         |  |  |  |  |  |

|------|-------------------------------------------------------------------------------------|--|--|--|--|--|

| WAIT | No effect on A/D Converter. ADC interrupts cause the device to exit from Wait mode. |  |  |  |  |  |

| STOP | A/D Converter disabled.                                                             |  |  |  |  |  |

**Note**: The A/D converter may be disabled by clearing the PDS bit. This feature allows reduced power consumption when no conversion is needed.

#### 8.3.6 Interrupts

| Interrupt Event        | Event<br>Flag | Enable<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Stop |

|------------------------|---------------|---------------|----------------------|----------------------|

| End of Conver-<br>sion | EOC           | EAI           | Yes                  | No                   |

**Note:** The EOC bit is cleared only when a new conversion is started (it cannot be cleared by writing 0). To avoid generating further EOC interrupt, the EAI bit has to be cleared within the ADC interrupt subroutine.

#### 8.3.7 Register Description

## A/D CONVERTER CONTROL REGISTER (AD-CR)

Address: 0D1h - Read/Write (Bit 6 Read Only, Bit 5 Write Only)

Reset value: 0100 0000 (40h)

| 7   |     |     |     |           |            |           | 0         |

|-----|-----|-----|-----|-----------|------------|-----------|-----------|

| EAI | EOC | STA | PDS | ADCR<br>3 | OSC<br>OFF | ADCR<br>1 | ADCR<br>0 |

## Bit 7 = EAI Enable A/D Interrupt.

0: ADC interrupt disabled 1: ADC interrupt enabled

<u>(۲</u>/

.

Bit 6 = EOC End of conversion. Read Only When a conversion has been completed, this bit is set by hardware and an interrupt request is generated if the EAI bit is set. The EOC bit is automati-

| Table 16. ADC Register | Map and Reset Values |

|------------------------|----------------------|

|------------------------|----------------------|

cally cleared when the STA bit is set. Data in the data conversion register are valid only when this bit is set to "1".

0: Conversion is not complete

1: Conversion can be read from the ADR register

Bit 5 = **STA**: Start of Conversion. Write Only.

0: No effect

1: Start conversion

**Note:** Setting this bit automatically clears the EOC bit. If the bit is set again when a conversion is in progress, the present conversion is stopped and a new one will take place. This bit is write only, any attempt to read it will show a logical zero.

#### Bit 4 = **PDS** Power Down Selection.

0: A/D converter is switched off

1: A/D converter is switched on

Bit 3 = **ADCR3 Reserved**, must be cleared.

#### Bit 2 = OSCOFF Main Oscillator off.

0: Main Oscillator enabled

1: Main Oscillator disabled

**Note:** This bit does not apply to the ADC peripheral but to the main clock system. Refer to the Clock System section.

Bits 1:0 = ADCR[1:0] Reserved, must be cleared.

#### A/D CONVERTER DATA REGISTER (ADR)

Address: 0D0h - Read only

Reset value: xxxx xxxx (xxh)

| 7    |      |      |      |      |      |      | 0    |

|------|------|------|------|------|------|------|------|

| ADR7 | ADR6 | ADR5 | ADR4 | ADR3 | ADR2 | ADR1 | ADR0 |

|      |      |      |      |      |      |      |      |

Bits 7:0 = ADR[7:0]: 8 Bit A/D Conversion Result.

| Address<br>(Hex.) | Register<br>Label | 7    | 6    | 5    | 4    | 3     | 2      | 1     | 0     |

|-------------------|-------------------|------|------|------|------|-------|--------|-------|-------|

| 0D0h              | ADR               | ADR7 | ADR6 | ADR5 | ADR4 | ADR3  | ADR2   | ADR1  | ADR0  |

|                   | Reset Value       | 0    | 0    | 0    | 0    | 0     | 0      | 0     | 0     |

| 0D1h              | ADCR              | EAI  | EOC  | STA  | PDS  | ADCR3 | OSCOFF | ADCR1 | ADCR0 |

|                   | Reset Value       | 0    | 1    | 0    | 0    | 0     | 0      | 0     | 0     |

## ST6208C/ST6209C/ST6210C/ST6220C

| LOW       |   |           |        | -           |   |           |        |           |   |          |      |   |           | 511 |        |           |   |           | LOW       |

|-----------|---|-----------|--------|-------------|---|-----------|--------|-----------|---|----------|------|---|-----------|-----|--------|-----------|---|-----------|-----------|

| н         |   | 0<br>0000 |        | 1<br>0001   |   | 2<br>0010 |        | 3<br>0011 |   | 4<br>010 | 0    |   | 5<br>0101 |     |        | 6<br>0110 |   | 7<br>0111 | н         |

| 0         | 2 | JRNZ      | 4      | CALL        | 2 | JRNC      | 5      | JRR       | 2 |          | JRZ  |   |           |     | 2      | JRC       | 4 | LD        | 0         |

| 0<br>0000 |   | е         |        | abc         |   | е         |        | b0,rr,ee  |   | е        | NOP  |   | #         |     |        | е         |   | a,(x)     | 0000      |

|           | 1 | pcr       | 2      | ext         | 1 | pcr       | 3      | bt        | 1 |          | pcr  |   |           |     | 1      | prc       | 1 | ind       |           |

|           | 2 | JRNZ      | 4      | CALL        | 2 | JRNC      | 5      | JRS       | 2 |          | JRZ  | 4 | I         | INC | 2      | JRC       | 4 | LDI       |           |

| 1<br>0001 |   | е         |        | abc         |   | е         |        | b0,rr,ee  |   | е        |      |   | х         |     |        | е         |   | a,nn      | 1<br>0001 |

| 0001      | 1 | pcr       | 2      | ext         |   | pcr       | 3      |           | 1 |          | pcr  | 1 |           | sd  | 1      | prc       | 2 | imm       |           |

| •         | 2 | JRNZ      | 4      | CALL        | 2 | JRNC      | 5      | JRR       | 2 |          | JRZ  |   |           |     | 2      | JRC       | 4 | CP        | •         |

| 2<br>0010 |   | е         |        | abc         |   | е         |        | b4,rr,ee  |   | е        |      |   | #         |     |        | е         |   | a,(x)     | 2<br>0010 |

| 0010      | 1 | pcr       | 2      | ext         | 1 | pcr       | 3      | bt        | 1 |          | pcr  |   |           |     | 1      | prc       | 1 | ind       | 0010      |

| -         | 2 | JRNZ      | 4      | CALL        | 2 | JRNC      | 5      | JRS       | 2 |          | JRZ  | 4 |           | LD  | 2      | JRC       | 4 | CPI       | -         |

| 3<br>0011 |   | е         |        | abc         |   | е         |        | b4,rr,ee  | е |          |      |   | a,x       |     |        | е         |   | a,nn      | 3<br>0011 |

| 0011      | 1 | pcr       | 2      | ext         | 1 | pcr       | 3      | bt        | 1 |          | pcr  | 1 |           | sd  | 1      | prc       | 2 | imm       | 0011      |

|           | 2 | JRNZ      | 4      | CALL        | 2 | JRNC      | 5      | JRR       | 2 |          | JRZ  |   |           |     | 2      | JRC       | 4 | ADD       |           |

| 4         |   | е         |        | abc         |   | е         |        | b2,rr,ee  |   | е        |      |   | #         |     |        | е         |   | a,(x)     | 4         |

| 0100      | 1 | pcr       | 2      | ext         | 1 | pcr       | 3      |           | 1 |          | pcr  |   |           |     | 1      | prc       | 1 | ind       | 0100      |

|           | 2 |           | 4      | CALL        |   | JRNC      | 5      |           | 2 |          | JRZ  | 4 |           | NC  | 2      | JRC       | 4 | ADDI      |           |

| 5         | _ | e         | -      | abc         | _ | e         | -      | b2,rr,ee  | _ | е        |      | - | у         |     |        | e         | - | a,nn      | 5         |

| 0101      | 1 | pcr       | 2      | ext         | 1 | pcr       | 3      |           | 1 | 0        | pcr  | 1 | J         | sd  | 1      | prc       | 2 | imm       | 0101      |

|           | 2 | JRNZ      | _      | CALL        | 2 | JRNC      | 5      |           | 2 |          | JRZ  |   |           | ou  | 2      | JRC       | 4 | INC       |           |

| 6         | 2 | e         | -      | abc         | 2 | e         | 0      | b6,rr,ee  | 2 | е        | 0112 |   | #         |     | -      | e         | - | (x)       | 6         |

| 0110      | 1 |           | 2      | ext         | 1 | pcr       | 3      |           | 1 | U        | pcr  |   | "         |     | 1      | prc       | 1 | ind       | 0110      |

|           | 2 | JRNZ      |        | CALL        | 2 | JRNC      |        |           | 2 |          | JRZ  | 4 |           | LD  | 2      | JRC       |   | inu       |           |

| 7         | 2 | e         | 4      | abc         | 2 | e         | 5      |           | 2 | е        | JNZ  | 4 | <u> </u>  | LD  | 2      | e         |   | #         | 7         |

| 0111      | 4 | -         | 0      |             | 4 |           | 2      | b6,rr,ee  | 4 | е        | nor  | 4 | a,y       | ad  | 4      |           |   | #         | 0111      |

|           | 1 | 1         | 2<br>4 | ext<br>CALL |   | pcr       | 3<br>5 |           |   |          | pcr  | 1 |           | sd  | 1<br>2 | prc       | 4 |           |           |

| 8         | 2 | JRNZ      | 4      | -           | 2 | JRNC      | э      | -         | 2 | _        | JRZ  |   |           |     | 2      | JRC       | 4 | LD        | 8         |

| 1000      |   | е         | ~      | abc         |   | е         | _      | b1,rr,ee  |   | е        |      |   | #         |     |        | е         |   | (x),a     | 1000      |

|           | 1 | pcr       | 2      | ext         |   | pcr       | 3      |           |   |          | pcr  |   |           |     | 1      | prc       | 1 | ind       |           |

| 9         | 2 |           | 4      | CALL        | 2 | JRNC      | 5      |           | 2 |          | JRZ  | 4 |           | INC | 2      | JRC       |   |           | 9         |

| 1001      |   | е         | _      | abc         |   | е         | _      | b1,rr,ee  |   | е        |      |   | v         |     |        | е         |   | #         | 1001      |

|           | 1 | pcr       | 2      | ext         |   | pcr       |        |           |   |          | pcr  | 1 |           | sd  | 1      | prc       |   |           |           |

| Α         | 2 | JRNZ      | 4      | CALL        | 2 | JRNC      | 5      |           | 2 |          | JRZ  |   |           |     | 2      | JRC       | 4 | AND       | Α         |

| 1010      |   | е         |        | abc         |   | е         |        | b5,rr,ee  |   | е        |      |   | #         |     |        | е         |   | a,(x)     | 1010      |

| -         | 1 | pcr       |        | ext         |   | pcr       | 3      |           |   |          | pcr  |   |           |     | 1      | prc       |   | ind       |           |

| в         | 2 | JRNZ      | 4      | CALL        | 2 | JRNC      | 5      |           | 2 |          | JRZ  | 4 |           | LD  | 2      | JRC       | 4 | ANDI      | В         |

| 1011      |   | е         |        | abc         |   | е         |        | b5,rr,ee  |   | е        |      |   | a,v       |     |        | е         |   | a,nn      | 1011      |

|           | 1 | pcr       | 2      | ext         |   | pcr       | 3      |           |   |          | pcr  | 1 |           | sd  | 1      | prc       |   | imm       |           |

| С         | 2 | JRNZ      | 4      | CALL        | 2 | JRNC      | 5      |           | 2 |          | JRZ  |   |           |     | 2      | JRC       | 4 | SUB       | с         |

| 1100      |   | е         |        | abc         |   | е         |        | b3,rr,ee  |   | е        |      |   | #         |     |        | е         |   | a,(x)     | 1100      |

|           | 1 | pcr       | 2      | ext         |   | pcr       | 3      |           | 1 |          | pcr  |   |           |     | 1      | prc       | 1 | ind       |           |

| <b>P</b>  | 2 | JRNZ      | 4      | CALL        | 2 | JRNC      | 5      | JRS       | 2 |          | JRZ  | 4 | I         | INC | 2      | JRC       | 4 | SUBI      | ~         |

| D<br>1101 |   | е         |        | abc         |   | е         |        | b3,rr,ee  |   | е        |      |   | w         |     |        | е         |   | a,nn      | D<br>1101 |

|           | 1 | pcr       | 2      | ext         | 1 | pcr       | 3      | bt        | 1 |          | pcr  | 1 |           | sd  | 1      | prc       | 2 | imm       |           |

| _         | 2 | JRNZ      | 4      | CALL        | 2 | JRNC      | 5      | JRR       | 2 |          | JRZ  |   |           |     | 2      | JRC       | 4 | DEC       | _         |

| E<br>1110 |   | е         |        | abc         |   | е         |        | b7,rr,ee  |   | е        |      |   | #         |     |        | е         |   | (x)       | E<br>1110 |

| 1110      | 1 | pcr       | 2      | ext         | 1 | pcr       | 3      |           | 1 |          | pcr  |   |           |     | 1      | prc       | 1 | ind       | 1110      |

| _         | 2 | JRNZ      | 4      | CALL        |   | JRNC      |        |           |   |          | JRZ  | 4 |           | LD  | 2      | JRC       |   |           |           |

| F         |   | е         |        | abc         |   | е         |        | b7,rr,ee  |   | е        |      |   | a,w       |     |        | е         |   | #         | F         |

| 1111      | 1 | pcr       | 2      | ext         | 1 | pcr       | 3      |           | 1 |          | pcr  | 1 | , -       | sd  | 1      | prc       |   |           | 1111      |

|           |   | 201       | -      | 0/1         |   | 201       | 5      | ы         |   |          | 201  |   |           | 50  |        | pio       |   |           | 1         |

#### Opcode Map Summary. The following table contains an opcode map for the instructions used by the ST6

#### Abbreviations for Addressing Modes: Legend:

- Direct Short Direct dir sd imm Immediate inh Inherent Extended ext b.d Bit Direct Bit Test bt

- Indicates Illegal Instructions 5-bit Displacement # е

- b 3-bit Address

rr

- 1-byte Data space address 1-byte immediate data

- nn

- abc 12-bit address

- 8-bit displacement ee

- pcr ind Program Counter Relative

- Indirect

#### ST6208C/ST6209C/ST6210C/ST6220C

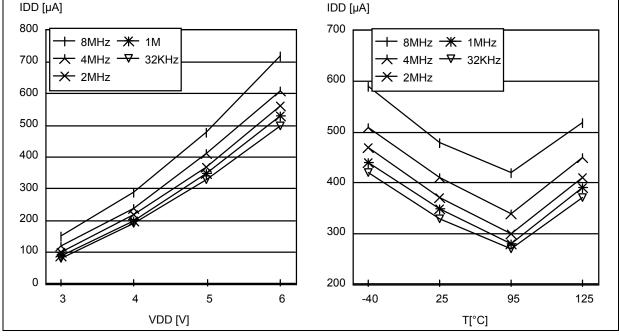

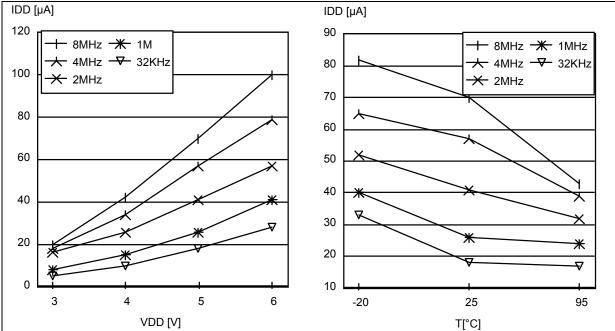

#### SUPPLY CURRENT CHARACTERISTICS (Cont'd)

## Figure 44. Typical $I_{DD}$ in WAIT vs $f_{CPU}$ and Temperature for OTP devices with option bytes not programmed

Figure 45. Typical  $I_{\text{DD}}$  in WAIT vs  $f_{\text{CPU}}$  and Temperature for OTP devices with option bytes programmed to 00H

#### CLOCK AND TIMING CHARACTERISTICS (Cont'd)

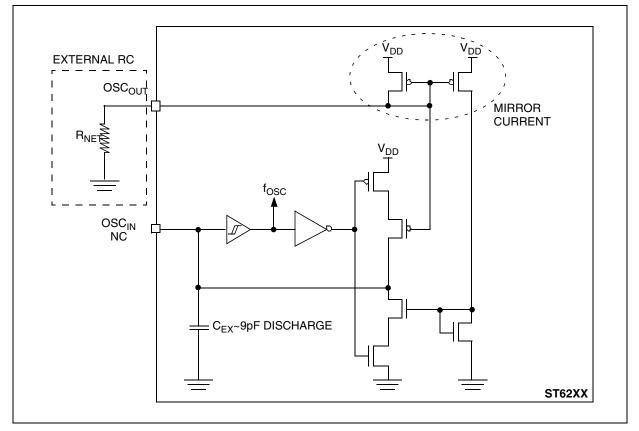

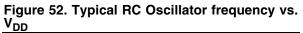

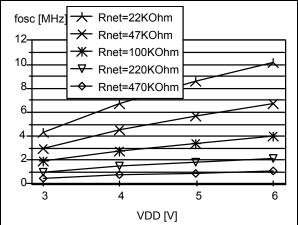

#### 10.5.4 RC Oscillator

The ST6 internal clock can be supplied with an external RC oscillator. Depending on the  $R_{NET}$  value, the accuracy of the frequency is about 20%, so it may not be suitable for some applications.

| Symbol           | Parameter                                     |                               | Conditions                                                                                                                                                        | Min                                    | Тур                                     | Max                                 | Unit |

|------------------|-----------------------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-----------------------------------------|-------------------------------------|------|

| f <sub>osc</sub> | RC oscillator frequency <sup>1)</sup>         | 6V 4.5V≤V <sub>DD</sub> ≤6.0V | R <sub>NET</sub> =22 kΩ<br>R <sub>NET</sub> =47 kΩ<br>R <sub>NET</sub> =100 kΩ<br>R <sub>NET</sub> =220 kΩ<br>R <sub>NET</sub> =470 kΩ<br>R <sub>NET</sub> =22 kΩ | 7.2<br>5.1<br>3.2<br>1.8<br>0.9<br>3.7 | 8.6<br>5.7<br>3.4<br>1.9<br>0.95<br>4.3 | 10<br>6.5<br>3.8<br>2<br>1.1<br>4.9 | MHz  |

|                  |                                               | 3V≤V <sub>DD</sub> ≤3.6V      | R <sub>NET</sub> =47 kΩ<br>R <sub>NET</sub> =100 kΩ<br>R <sub>NET</sub> =220 kΩ<br>R <sub>NET</sub> =470 kΩ                                                       | 2.8<br>1.8<br>1<br>0.5                 | 3<br>1.9<br>1.1<br>0.55                 | 3.3<br>2<br>1.2<br>0.6              |      |

| R <sub>NET</sub> | RC Oscillator external resistor <sup>2)</sup> |                               | see Figure 52 & Figure 53                                                                                                                                         | 22                                     |                                         | 870                                 | kΩ   |

Notes:

1. Data based on characterization results, not tested in production. These measurements were done with the OSCin pin unconnected (only soldered on the PCB).

2. R<sub>NET</sub> must have a positive temperature coefficient (ppm/°C), carbon resistors should therefore not be used.

Figure 51. Typical Application with RC Oscillator

#### CLOCK AND TIMING CHARACTERISTICS (Cont'd)

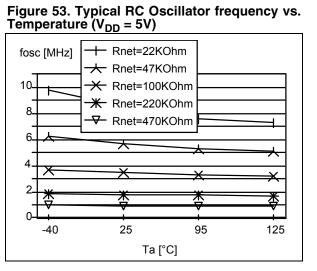

#### 10.5.5 Oscillator Safeguard (OSG) and Low Frequency Auxiliary Oscillator (LFAO)

| Symbol            | Parameter                          | Conditions                         | Min | Тур | Max | Unit  |

|-------------------|------------------------------------|------------------------------------|-----|-----|-----|-------|

| f                 | Low Frequency Auxiliary Oscillator | $T_A=25^{\circ}$ C, $V_{DD}=5.0$ V | 200 | 350 | 800 | kHz   |

| <sup>T</sup> LFAO | Frequency <sup>1)</sup>            | $T_A=25^{\circ} C, V_{DD}=3.3 V$   | 86  | 150 | 340 | KI IZ |

| f                 | Internal Frequency with OSG ena-   | $T_A=25^{\circ} C, V_{DD}=4.5 V$   | 4   |     |     | MHz   |

| TOSG              | bled                               | $T_A=25^{\circ} C, V_{DD}=3.3 V$   | 2   |     |     |       |

#### Figure 54. Typical LFAO Frequencies

#### Note:

1. Data based on characterization results.

#### EMC CHARACTERISTICS (Cont'd)

#### 10.7.2 Absolute Electrical Sensitivity

Based on three different tests (ESD, LU and DLU) using specific measurement methods, the product is stressed in order to determine its performance in terms of electrical sensitivity. For more details, refer to the AN1181 application note.

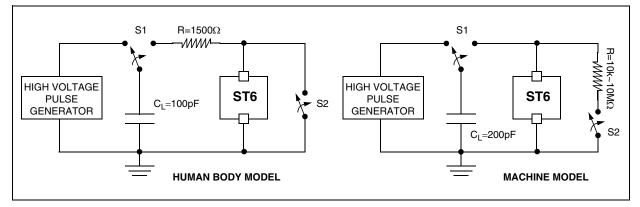

#### 10.7.2.1 Electro-Static Discharge (ESD)

Electro-Static Discharges (3 positive then 3 negative pulses separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends of the number of supply pins of the device (3 parts\*(n+1) supply pin). Two models are usually simulated: Human Body Model and Machine Model. This test conforms to the JESD22-A114A/A115A standard. See Figure 57 and the following test sequences.

#### Human Body Model Test Sequence

– C<sub>L</sub> is loaded through S1 by the HV pulse generator.

- S1 switches position from generator to R.

- A discharge from  $C_L$  through R (body resistance) to the ST6 occurs.

- S2 must be closed 10 to 100ms after the pulse delivery period to ensure the ST6 is not left in charge state. S2 must be opened at least 10ms prior to the delivery of the next pulse.

#### Machine Model Test Sequence

- C<sub>L</sub> is loaded through S1 by the HV pulse generator.

- S1 switches position from generator to ST6.

- A discharge from C<sub>L</sub> to the ST6 occurs.

- S2 must be closed 10 to 100ms after the pulse delivery period to ensure the ST6 is not left in charge state. S2 must be opened at least 10ms prior to the delivery of the next pulse.

- R (machine resistance), in series with S2, ensures a slow discharge of the ST6.

## Absolute Maximum Ratings

| Symbol                | Ratings                                                | Conditions            | Maximum value <sup>1)</sup> | Unit |

|-----------------------|--------------------------------------------------------|-----------------------|-----------------------------|------|

| V <sub>ESD(HBM)</sub> | Electro-static discharge voltage<br>(Human Body Model) | T <sub>A</sub> =+25°C | 2000                        | V    |

| V <sub>ESD(MM)</sub>  | Electro-static discharge voltage (Machine Model)       | T <sub>A</sub> =+25°C | 200                         | v    |

#### Notes:

1. Data based on characterization results, not tested in production.

#### Figure 57. Typical Equivalent ESD Circuits

#### **10.8 I/O PORT PIN CHARACTERISTICS**

#### **10.8.1 General Characteristics**

Subject to general operating conditions for  $V_{DD}$ ,  $f_{OSC}$ , and  $T_A$  unless otherwise specified.

| Symbol                | Parameter                                        | Con                                                  | ditions               | Min                             | <b>Typ</b> <sup>1)</sup> | Max                 | Unit             |

|-----------------------|--------------------------------------------------|------------------------------------------------------|-----------------------|---------------------------------|--------------------------|---------------------|------------------|

| V <sub>IL</sub>       | Input low level voltage <sup>2)</sup>            |                                                      |                       |                                 |                          | 0.3xV <sub>DD</sub> | V                |

| V <sub>IH</sub>       | Input high level voltage <sup>2)</sup>           |                                                      |                       | $0.7 \mathrm{xV}_{\mathrm{DD}}$ |                          |                     | v                |

| V.                    | Schmitt trigger voltage hysteresis 3)            | V <sub>DD</sub> =5V                                  |                       | 200                             | 400                      |                     | mV               |

| V <sub>hys</sub>      | Schmitt trigger voltage hysteresis               | V <sub>DD</sub> =3.3V                                |                       | 200                             | 400                      |                     | IIIV             |

| ١L                    | Input leakage current                            | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V<br>(no pull-up o |                       |                                 | 0.1                      | 1                   | μA               |

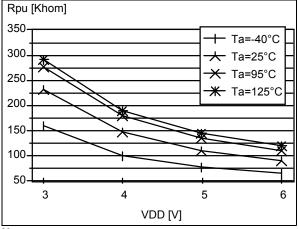

| D                     | Weak pull-up equivalent resistor 4)              | V _V                                                 | V <sub>DD</sub> =5V   | 40                              | 110                      | 350                 | kΩ               |

| R <sub>PU</sub>       | weak puil-up equivalent resistor                 | V <sub>IN</sub> =V <sub>SS</sub>                     | V <sub>DD</sub> =3.3V | 80                              | 230                      | 700                 | K52              |

| C <sub>IN</sub>       | I/O input pin capacitance                        |                                                      |                       |                                 | 5                        | 10                  | pF               |

| C <sub>OUT</sub>      | I/O output pin capacitance                       |                                                      |                       |                                 | 5                        | 10                  | pF               |

| t <sub>f(IO)out</sub> | Output high to low level fall time <sup>5)</sup> | C <sub>L</sub> =50pF                                 |                       |                                 | 30                       |                     | ns               |

| t <sub>r(IO)out</sub> | Output low to high level rise time <sup>5)</sup> | Between 10                                           | % and 90%             |                                 | 35                       |                     | 115              |

| t <sub>w(IT)in</sub>  | External interrupt pulse time <sup>6)</sup>      |                                                      |                       | 1                               |                          |                     | t <sub>CPU</sub> |

### Figure 61. Typical $R_{PU}$ vs. $V_{DD}$ with $V_{IN} = V_{SS}$

#### Notes:

57

1. Unless otherwise specified, typical data are based on  $T_A\!=\!25^\circ C$  and  $V_{DD}\!=\!5V.$

- 2. Data based on characterization results, not tested in production.

- 3. Hysteresis voltage between Schmitt trigger switching levels. Based on characterization results, not tested.

- 4. The R<sub>PU</sub> pull-up equivalent resistor is based on a resistive transistor. This data is based on characterization results, not tested in production.

- 5. Data based on characterization results, not tested in production.

- To generate an external interrupt, a minimum pulse width has to be applied on an I/O port pin configured as an external interrupt source.

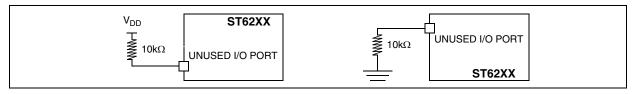

#### Figure 62. Two typical Applications with unused I/O Pin

#### **10.9 CONTROL PIN CHARACTERISTICS**

#### 10.9.1 Asynchronous RESET Pin

Subject to general operating conditions for  $V_{DD}$ ,  $f_{OSC}$ , and  $T_A$  unless otherwise specified.

| Symbol                  | Parameter                                    | Cor                              | ditions                                      | Min                             | <b>Typ</b> <sup>1)</sup> | Max                             | Unit                   |

|-------------------------|----------------------------------------------|----------------------------------|----------------------------------------------|---------------------------------|--------------------------|---------------------------------|------------------------|

| V <sub>IL</sub>         | Input low level voltage <sup>2)</sup>        |                                  |                                              |                                 |                          | $0.3 \mathrm{xV}_{\mathrm{DD}}$ | V                      |

| V <sub>IH</sub>         | Input high level voltage <sup>2)</sup>       |                                  |                                              | $0.7 \mathrm{xV}_{\mathrm{DD}}$ |                          |                                 | v                      |

| V <sub>hys</sub>        | Schmitt trigger voltage hysteresis 3)        |                                  |                                              | 200                             | 400                      |                                 | mV                     |

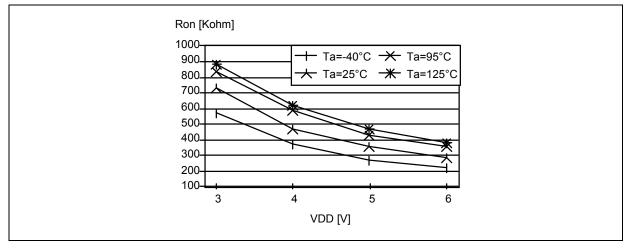

| R <sub>ON</sub>         | Weak pull-up equivalent resistor 4)          | VV                               | V <sub>DD</sub> =5V<br>V <sub>DD</sub> =3.3V | 150                             | 350                      | 900                             | kΩ                     |

| NON                     | wear puil-up equivalent resistor             | VIN-VSS                          | V <sub>DD</sub> =3.3V                        | 300                             | 730                      | 1900                            | KS 2                   |

| R <sub>ESD</sub>        | ESD resistor protection                      | V <sub>IN</sub> =V <sub>SS</sub> | V <sub>DD</sub> =5V<br>V <sub>DD</sub> =3.3V |                                 | 2.8                      |                                 | kΩ                     |

| "ESD                    |                                              | VIN-VSS                          | V <sub>DD</sub> =3.3V                        |                                 |                          |                                 | NS2                    |

| t <sub>w(RSTL)out</sub> | Generated reset pulse duration               | External p                       | oin or<br>eset sources                       |                                 |                          |                                 | t <sub>CPU</sub><br>μs |

| t <sub>h(RSTL)in</sub>  | External reset pulse hold time <sup>5)</sup> |                                  |                                              |                                 |                          |                                 | μs                     |

| t <sub>g(RSTL)in</sub>  | Filtered glitch duration <sup>6)</sup>       |                                  |                                              |                                 |                          |                                 | ns                     |

#### Notes:

<u>ل</u>رک

- 1. Unless otherwise specified, typical data are based on  $T_A{=}25^\circ\text{C}$  and  $V_{DD}{=}5V.$

- 2. Data based on characterization results, not tested in production.

- 3. Hysteresis voltage between Schmitt trigger switching levels. Based on characterization results, not tested.

- 4. The R<sub>ON</sub> pull-up equivalent resistor is based on a resistive transistor. This data is based on characterization results, not tested in production.

- 5. All short pulse applied on  $\overline{\text{RESET}}$  pin with a duration below  $t_{h(\text{RSTL})\text{in}}$  can be ignored.

- 6. The reset network protects the device against parasitic resets, especially in a noisy environment.

- 7. The output of the external reset circuit must have an open-drain output to drive the ST6 reset pad. Otherwise the device can be damaged when the ST6 generates an internal reset (LVD or watchdog).

## Figure 69. Typical $\rm R_{ON}$ vs $\rm V_{DD}$ with $\rm V_{IN}{=}V_{SS}$

## **11 GENERAL INFORMATION**

#### **11.1 PACKAGE MECHANICAL DATA**

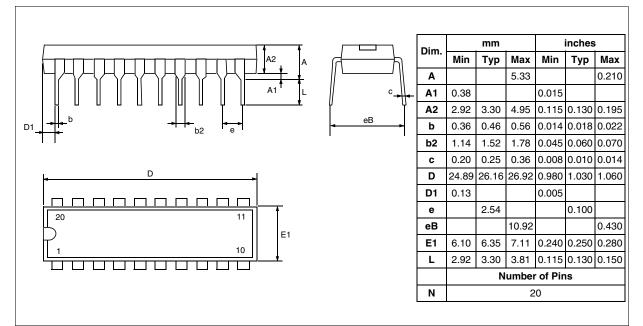

#### Figure 74. 20-Pin Plastic Dual In-Line Package, 300-mil Width

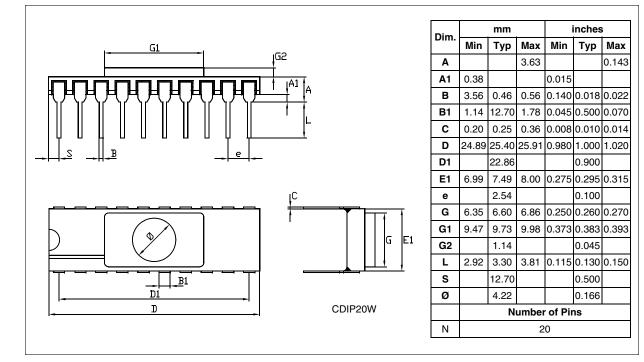

Figure 75. 20-Pin Ceramic Side-Brazed Dual In-Line Package

**لركم**

### TRANSFER OF CUSTOMER CODE (Cont'd)

57

| ST            | T6208C/09C/10C/200     | C/P08C/P09C/P10C/P20C MICR                              | OCONTROLLER OPTION LIST                                 |  |  |  |  |  |

|---------------|------------------------|---------------------------------------------------------|---------------------------------------------------------|--|--|--|--|--|

| Customer:     |                        |                                                         |                                                         |  |  |  |  |  |

| Address:      |                        |                                                         |                                                         |  |  |  |  |  |

|               |                        |                                                         |                                                         |  |  |  |  |  |

| Contact:      |                        |                                                         |                                                         |  |  |  |  |  |

| Phone:        |                        |                                                         |                                                         |  |  |  |  |  |

| Reference:    |                        |                                                         |                                                         |  |  |  |  |  |

| STMicroele    | ctronics references    | :                                                       |                                                         |  |  |  |  |  |

| Device:       |                        | [] ST6208C (1 KB)                                       | [] ST6209C (1 KB)                                       |  |  |  |  |  |

|               |                        |                                                         | [ ] ST6220C (4 KB)                                      |  |  |  |  |  |

|               |                        | [ ] ST62P08C (1 KB)<br>[ ] ST62P10C (2 KB)              | [ ] ST62P09C (1 KB)<br>[ ] ST62P20C (4 KB)              |  |  |  |  |  |

|               |                        |                                                         |                                                         |  |  |  |  |  |

| Package:      |                        | [ ] Dual in Line Plastic<br>[ ] Small Outline Plastic w | ith conditioning                                        |  |  |  |  |  |

|               |                        | [] Shrink Small Outline Pl                              | astic with conditioning                                 |  |  |  |  |  |

| Conditioning  |                        | [] Standard (Tube)                                      | [] Tape & Reel                                          |  |  |  |  |  |

| Temperature   | e Range:               | $[] 0^{\circ}C \text{ to } + 70^{\circ}C$               | [ ] - 40°C to + 85°C                                    |  |  |  |  |  |

|               |                        | [] - 40°C to + 125°C                                    |                                                         |  |  |  |  |  |

| Marking:      |                        | [] Standard marking                                     |                                                         |  |  |  |  |  |

| -             |                        | [] Special marking (ROM                                 | ] Special marking (ROM only):<br>PDIP20 (10 char. max): |  |  |  |  |  |

|               |                        | SO20 (8 char. max):                                     | (x):                                                    |  |  |  |  |  |

|               |                        | SSOP20 (11 char. m                                      | <br>ax):                                                |  |  |  |  |  |

| Authorized c  | characters are letters | , digits, '.', '-', '/' and spaces only.                |                                                         |  |  |  |  |  |

| Oscillator Sa | afeguard:              | [] Enabled                                              | [] Disabled                                             |  |  |  |  |  |

| Watchdog S    | election:              | [] Software Activation                                  | [] Hardware Activation                                  |  |  |  |  |  |

| Timer pull-u  | p:                     | [] Enabled                                              | [] Disabled                                             |  |  |  |  |  |

| NMI pull-up:  |                        | [] Enabled                                              | [] Disabled                                             |  |  |  |  |  |

| Oscillator Se | election:              | [] Quartz crystal / Cerami                              | ic resonator                                            |  |  |  |  |  |

|               |                        | [] RC network                                           |                                                         |  |  |  |  |  |

| Readout Pro   | otection: F            | ASTROM:                                                 |                                                         |  |  |  |  |  |

|               | _                      | [] Enabled                                              | [] Disabled                                             |  |  |  |  |  |

|               | F                      | OM:                                                     |                                                         |  |  |  |  |  |

|               |                        | [ ] Enabled:<br>[ ] Fuse is blown by S                  | TMicroelectronics                                       |  |  |  |  |  |

|               |                        | [] Fuse can be blown                                    |                                                         |  |  |  |  |  |

|               |                        | [] Disabled                                             |                                                         |  |  |  |  |  |

|               |                        | [] =                                                    |                                                         |  |  |  |  |  |

| Low Voltage   |                        | [] Enabled                                              | [] Disabled                                             |  |  |  |  |  |

|               | OP Mode Control:       | [] Enabled                                              | [] Disabled                                             |  |  |  |  |  |

| dentifier (FA | ASTROM only):          | [] Enabled                                              | [] Disabled                                             |  |  |  |  |  |

| Comments:     | 1                      |                                                         |                                                         |  |  |  |  |  |

| Oscillator Fr | equency in the applic  | ation:                                                  |                                                         |  |  |  |  |  |

|               | rating Range in the a  |                                                         |                                                         |  |  |  |  |  |

| Notes:        |                        |                                                         |                                                         |  |  |  |  |  |

| Date:         |                        |                                                         |                                                         |  |  |  |  |  |

| Signature:    |                        |                                                         |                                                         |  |  |  |  |  |

|               |                        |                                                         |                                                         |  |  |  |  |  |