Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Betano                     |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 26                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f18455-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Pin Allocation Tables**

## 1 28-Pin Allocation Table

| 0/1 | 28-pin SPDIP/SOIC/SSOP | 28-pin VQFN | ADC              | Reference | Comparator       | NCO | DAC                   | DSM       | Timers                                      | CCP       | MMd | CWG                   | MSSP                                | ZCD  | EUSART                                     | CLC       | CLKR | Interrupts | Pull-up | Basic             |

|-----|------------------------|-------------|------------------|-----------|------------------|-----|-----------------------|-----------|---------------------------------------------|-----------|-----|-----------------------|-------------------------------------|------|--------------------------------------------|-----------|------|------------|---------|-------------------|

| RA0 | 2                      | 27          | ANA0             | _         | C1IN0-<br>C2IN0- | _   | _                     | _         | -                                           | _         | _   | _                     | _                                   | _    | -                                          | CLCIN0(1) | _    | IOCA0      | Y       | _                 |

| RA1 | 3                      | 28          | ANA1             | _         | C1IN1-<br>C2IN1- | _   | _                     | _         | -                                           | _         | _   | _                     | _                                   | _    | -                                          | CLCIN1(1) | _    | IOCA1      | Y       | _                 |

| RA2 | 4                      | 1           | ANA2             | ADCVREF-  | C1IN0+<br>C2IN0+ | _   | DAC1VREF-<br>DAC1OUT1 | _         | _                                           | _         | _   | _                     | _                                   | _    | -                                          | _         | _    | IOCA2      | Y       | _                 |

| RA3 | 5                      | 2           | ANA3             | ADCVREF+  | C1IN1+           | —   | DAC1VREF+             | MDCARL(1) | -                                           | —         | —   | -                     | _                                   | —    | -                                          | —         | —    | IOCA3      |         | —                 |

| RA4 | 6                      | -           | ANA4             | -         | -                | —   | —                     | MDCARH(1) | T0CKI(1)                                    | CCP5IN(1) | -   | -                     |                                     | —    | -                                          | —         | —    | IOCA4      | _       | —                 |

| RA5 | 7                      | -           | ANA5             | _         | -                | -   | _                     | MDSRC(1)  | -                                           | -         | -   | -                     | <u>SS1</u> (1)                      | -    | -                                          | _         | -    | IOCA5      | _       | _                 |

| RA6 | 10                     | 7           | ANA6             | _         | _                | _   | _                     |           | _                                           | _         | -   | _                     | _                                   | _    | _                                          | _         | _    | IOCA6      | Y       | OSC2<br>CLKOUT    |

| RA7 | 9                      | 6           | ANA7             | _         | _                | _   | _                     | _         | _                                           | _         | _   | -                     | _                                   | _    | -                                          | _         | _    | IOCA7      | Y       | OSC1<br>CLKIN     |

| RB0 | 21                     | 18          | ANB0             | _         | C2IN1+           | _   | _                     |           | _                                           | CCP4IN(1) | _   | CWG1IN(1)             | _                                   | ZCD1 | _                                          | _         | _    | IOCB0      | Y       | INT(1)            |

| RB1 | -                      | 19          | ANB1             | _         | C1IN3-<br>C2IN3- |     | -                     | _         | -                                           | _         | _   | CWG2IN <sup>(1)</sup> | SCK2(1)<br>SCL2(1,3)                | -    | -                                          |           | -    | IOCB1      |         | _                 |

| RB2 | 23                     | 20          | ANB2             | _         | -                | _   | _                     | _         | -                                           | _         | _   | CWG3IN(1)             | SDI2(1)<br>SDA2(1,3) <u>SS2</u> (1) | _    | -                                          | _         | -    | IOCB2      | Y       | _                 |

| RB3 | 24                     | 21          | ANB3             | -         | C1IN2-<br>C2IN2- | _   | -                     | -         | -                                           | _         | _   | -                     | -                                   | _    | -                                          | _         | _    | IOCB3      | Y       | _                 |

| RB4 | 25                     | 22          | ANB4<br>ADACT(1) | _         | _                | _   | _                     | _         | <sub>T5G</sub> (1)<br>SMT2WIN(1)            | _         | -   | -                     | _                                   | _    | -                                          | _         | _    | IOCB4      | Y       | _                 |

| RB5 | 26                     | 23          | ANB5             | _         | _                | _   | _                     | _         | <sub>T1G</sub> (1)<br>SMT2SIG(1)            | CCP3IN(1) | _   | _                     | _                                   | _    | -                                          | _         | _    | IOCB5      | Y       | _                 |

| RB6 | 27                     | 24          | ANB6             | _         | _                | _   | _                     | _         | -                                           | _         | _   | _                     | _                                   | _    | <sub>CK2</sub> (1,3)                       | CLCIN2(1) | _    | IOCB6      | Y       | ICSPCLK<br>ICDCLK |

| RB7 | 28                     | 25          | ANB7             | _         | _                | _   | DAC10UT2              | _         | <sub>T6IN</sub> (1)                         | _         | _   | _                     | -                                   | _    | <sub>RX2</sub> (1)<br><sub>DT2</sub> (1,3) | _         | _    | IOCB7      | Y       | ICSPDAT<br>ICDDAT |

| RC0 | 11                     | 8           | ANC0             | _         | _                | _   | _                     | _         | т <sub>1СКI</sub> (1)<br>тзскі(1)<br>тзG(1) | _         | _   | _                     | _                                   |      | _                                          | _         | _    | IOCC0      | Y       | SOSCO             |

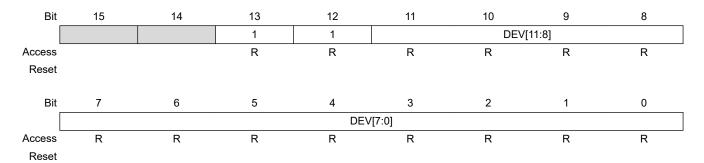

### 4.9.1 DEVICE ID

| Name:    | DEVICE ID |

|----------|-----------|

| Address: | 0x8006    |

**Device ID Register**

### **Bit 13 –** 1

These bit must be '1' to be distinguishable from the previous Device ID scheme

### **Bit 12 –** 1

These bit must be '1' to be distinguishable from the previous Device ID scheme

### Bits 11:0 - DEV[11:0]

Device ID bits

| Device       | Device ID |

|--------------|-----------|

| PIC16F18455  | 30D7h     |

| PIC16LF18455 | 30D8h     |

| PIC16F18456  | 30D9h     |

| PIC16LF18456 | 30DAh     |

### 7.10.5 FSR\_SHAD

| Name:    | FSRx_SHAD     |

|----------|---------------|

| Address: | 0x1FE8,0x1FEA |

Shadow of Indirect Address Register. The FSR value is the address of the data to which the INDF register points.

| Bit    | 15  | 14  | 13  | 12   | 11     | 10  | 9   | 8   |

|--------|-----|-----|-----|------|--------|-----|-----|-----|

|        |     |     |     | FSRI | H[7:0] |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W    | R/W | R/W | R/W |

| Reset  | х   | x   | х   | х    | х      | х   | х   | x   |

|        |     |     |     |      |        |     |     |     |

| Bit    | 7   | 6   | 5   | 4    | 3      | 2   | 1   | 0   |

|        |     |     |     | FSRI | _[7:0] |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W    | R/W | R/W | R/W |

| Reset  | х   | x   | x   | x    | x      | x   | x   | x   |

### Bits 15:8 - FSRH[7:0]

Most Significant address of INDF data Reset States: POR/BOR = xxxxxxx All Other Resets = uuuuuuuu

### Bits 7:0 - FSRL[7:0]

Least Significant address of INDF data Reset States: POR/BOR = xxxxxxx All Other Resets = uuuuuuu

## **Oscillator Module (with Fail-Safe Clock Monitor)**

| NDIV<3:0> | Clock Divider |

|-----------|---------------|

| 0001      | 2             |

| 0000      | 1             |

### Note:

- 1. The default value (f) is determined by the CONFIG1[RSTOSC] Configuration bits.

- 2. If NOSC is written with a reserved value, the operation is ignored and NOSC is not written.

- 3. When CONFIG1[CSWEN] = 0, this register is read-only and cannot be changed from the POR value.

- 4. When NOSC = 110 (HFINTOSC 1 MHz), the NDIV bits will default to '0010' upon Reset; for all other NOSC settings the NDIV bits will default to '0000' upon Reset.

- 5. EXTOSC configured by CONFIG1[FEXTOSC].

- 6. HFINTOSC frequency is set with the FRQ bits of the OSCFRQ register.

### **Related Links**

4.7.1 CONFIG1

42.4.3 PLL Specifications

### 9.6.3 OSCCON3

| Name:    | OSCCON3 |

|----------|---------|

| Address: | 0x88F   |

**Oscillator Control Register 3**

| Bit    | 7       | 6       | 5 | 4    | 3     | 2 | 1 | 0 |

|--------|---------|---------|---|------|-------|---|---|---|

|        | CSWHOLD | SOSCPWR |   | ORDY | NOSCR |   |   |   |

| Access | R/W/HC  | R/W     |   | RO   | RO    |   |   |   |

| Reset  | 0       | 0       |   | 0    | 0     |   |   |   |

Bit 7 – CSWHOLD Clock Switch Hold bit

| Value | Description                                                                                                           |

|-------|-----------------------------------------------------------------------------------------------------------------------|

| 1     | Clock switch will hold (with interrupt) when the oscillator selected by NOSC is ready                                 |

| 0     | Clock switch may proceed when the oscillator selected by NOSC is ready; when NOSCR becomes '1', the switch will occur |

### Bit 6 – SOSCPWR Secondary Oscillator Power Mode Select bit

| Value | Description                                       |

|-------|---------------------------------------------------|

| 1     | Secondary oscillator operating in High-Power mode |

| 0     | Secondary oscillator operating in Low-Power mode  |

### Bit 4 – ORDY Oscillator Ready bit (read-only)

| Value | Description                                                                |

|-------|----------------------------------------------------------------------------|

| 1     | OSCCON1 = OSCCON2; the current system clock is the clock specified by NOSC |

| 0     | A clock switch is in progress                                              |

### Bit 3 – NOSCR New Oscillator is Ready bit (read-only)<sup>(1)</sup>

| Value | Description                                                                                   |

|-------|-----------------------------------------------------------------------------------------------|

| 1     | A clock switch is in progress and the oscillator selected by NOSC indicates a ready condition |

| 0     | A clock switch is not in progress, or the NOSC-selected oscillator is not yet ready           |

### Note:

1. If CSWHOLD = 0, the user may not see this bit set because the bit is set for less than one instruction cycle.

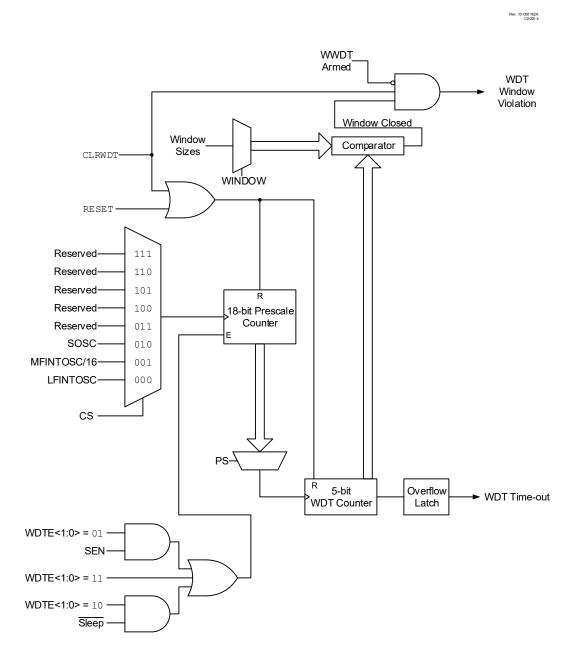

# PIC16(L)F18455/56 (WWDT) Windowed Watchdog Timer

## 12.1 Independent Clock Source

The WWDT can derive its time base from either the 31 kHz LFINTOSC or 31.25 kHz MFINTOSC internal oscillators, depending on the value of WDTE Configuration bits.

If WDTE = 'blx, then the clock source will be enabled depending on the WDTCCS Configuration bits.

If WDTE = 'b01, the SEN bit should be set by software to enable WWDT, and the clock source is enabled by the WDTCS bits.

Time intervals in this chapter are based on a minimum nominal interval of 1 ms. See *"Electrical Specifications"* for LFINTOSC and MFINTOSC tolerances.

© 2018 Microchip Technology Inc.

### 14.7.13 ANSELC

| Name:    | ANSELC |

|----------|--------|

| Address: | 0x1F4E |

Analog Select Register

| Bit    | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|--------|---------|---------|---------|---------|---------|---------|---------|---------|

|        | ANSELC7 | ANSELC6 | ANSELC5 | ANSELC4 | ANSELC3 | ANSELC2 | ANSELC1 | ANSELC0 |

| Access | R/W     |

| Reset  | 1       | 1       | 1       | 1       | 1       | 1       | 1       | 1       |

## Bits 0, 1, 2, 3, 4, 5, 6, 7 – ANSELCn Analog Select on Pins RC<7:0>

| Value | Description                          |

|-------|--------------------------------------|

| 1     | Digital Input buffers are disabled   |

| 0     | ST and TTL input buffers are enabled |

The threshold logic is selected by TMD bits. The threshold trigger option can be one of the following:

- Never interrupt

- Error is less than lower threshold

- Error is greater than or equal to lower threshold

- Error is between thresholds (inclusive)

- Error is outside of thresholds

- Error is less than or equal to upper threshold

- Error is greater than upper threshold

- Always interrupt regardless of threshold test results

- If the threshold condition is met, the threshold interrupt flag ADTIF is set.

### Note:

- 1. The threshold tests are signed operations.

- 2. If OV is set, a threshold interrupt is signaled. It is good practice for threshold interrupt handlers to verify the validity of the threshold by checking ADAOV.

### Table 20-6. ADC Error Calculation Mode

|      | Action During 1s               |                                                    |                                                                 |

|------|--------------------------------|----------------------------------------------------|-----------------------------------------------------------------|

| CALC | DSEN = 0 Single-Sample<br>Mode | DSEN = 1 CVD Double-<br>Sample Mode <sup>(1)</sup> | Application                                                     |

| 111  | Reserved                       | Reserved                                           | Reserved                                                        |

| 110  | Reserved                       | Reserved                                           | Reserved                                                        |

| 101  | ADLFTR-ADSTPT                  | ADFLTR-ADSTPT                                      | Average/filtered value vs. setpoint                             |

| 100  | ADPREV-ADFLTR                  | ADPREV-ADFLTR                                      | First derivative of filtered value <sup>(3)</sup><br>(negative) |

| 011  | Reserved                       | Reserved                                           | Reserved                                                        |

| 010  | ADRES-ADFLTR                   | (ADRES-ADPREV)-ADFLTR                              | Actual result vs. averaged/filtered value                       |

| 001  | ADRES-ADSTPT                   | (ADRES-ADPREV)-ADSTPT                              | Actual result vs. setpoint                                      |

| 000  | ADRES-ADPREV                   | ADRES-ADPREV                                       | First derivative of single<br>measurement <sup>(2)</sup>        |

|      |                                |                                                    | Actual CVD result in CVD mode <sup>(2)</sup>                    |

### Note:

- 1. When PSIS = 0, the value of ADRES-ADPREV) is the value of (S2-S1) from Computation Modes.

- 2. When **PSIS** = 0

- 3. When **PSIS** = 1.

### 20.6.8 Continuous Sampling Mode

Setting the CONT bit automatically retriggers a new conversion cycle after updating the ADACC register. The GO bit remains set and retriggering occurs automatically.

- 11. Select the clock source with the CS bits.

- 12. Set the EN bit to enable the module.

- 13. Clear the TRIS bits that correspond to the CWG outputs to set them as outputs.

If auto-restart is to be used, set the REN bit and the SHUTDOWN bit will be cleared automatically. Otherwise, clear the SHUTDOWN bit in software to start the CWG.

### 33.8.5 CLCxSEL2

| Name:    | CLCxSEL2                    |

|----------|-----------------------------|

| Address: | 0x1E14,0x1E1E,0x1E28,0x1E32 |

Generic CLCx Data 1 Select Register

| Bit    | 7 | 6 | 5   | 4   | 3   | 2     | 1   | 0   |

|--------|---|---|-----|-----|-----|-------|-----|-----|

| [      |   |   |     |     | D3S | [5:0] |     |     |

| Access |   |   | R/W | R/W | R/W | R/W   | R/W | R/W |

| Reset  |   |   | x   | x   | х   | х     | х   | х   |

### Bits 5:0 - D3S[5:0]

CLCx Data3 Input Selection bits Reset States: POR/BOR = xxxxx All Other Resets = uuuuu

| Value | Description                                     |

|-------|-------------------------------------------------|

| n     | Refer to CLC Input Sources for input selections |

· Master sends dummy data and slave sends useful data.

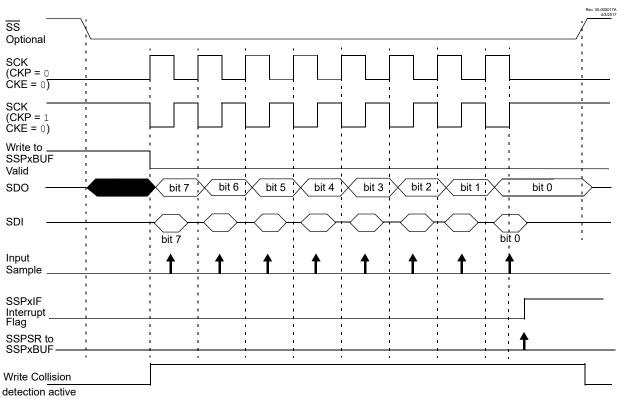

Transmissions may involve any number of clock cycles. When there is no more data to be transmitted, the master stops sending the clock signal and it deselects the slave.

Every slave device connected to the bus that has not been selected through its slave select line must disregard the clock and transmission signals and must not transmit out any data of its own.

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPxCON1<5:0> and SSPxSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select mode (Slave mode only)

To enable the serial port, SSP Enable bit, SSPEN, must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, re-initialize the SSPxCONx registers and then set the SSPEN bit. The SDI, SDO, SCK and  $\overline{SS}$  serial port pins are selected with the PPS controls. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed as follows:

- SDI must have corresponding TRIS bit set

- SDO must have corresponding TRIS bit cleared

- SCK (Master mode) must have corresponding TRIS bit cleared

- SCK (Slave mode) must have corresponding TRIS bit set

- The RxyPPS and SSPxCLKPPS controls must select the same pin

- SS must have corresponding TRIS bit set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

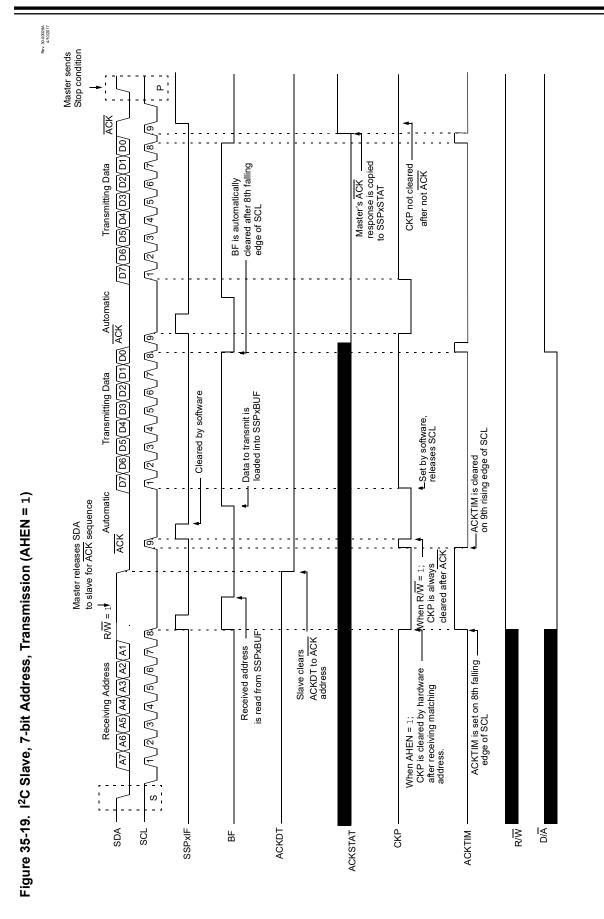

The MSSP consists of a transmit/receive shift register (SSPSR) and a buffer register (SSPxBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPxBUF holds the data that was written to the SSPSR until the received data is ready. Once the eight bits of data have been received, that byte is moved to the SSPxBUF register. Then, the Buffer Full Detect bit, BF, and the interrupt flag bit, SSPxIF, are set. This double-buffering of the received data (SSPxBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPxBUF register during transmission/ reception of data will be ignored and the write collision detect bit, WCOL, will be set. User software must clear the WCOL bit to allow the following write(s) to the SSPxBUF register to complete successfully.

When the application software is expecting to receive valid data, the SSPxBUF should be read before the next byte of data to transfer is written to the SSPxBUF. The Buffer Full bit, BF, indicates when SSPxBUF has been loaded with the received data (transmission is complete). When the SSPxBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur.

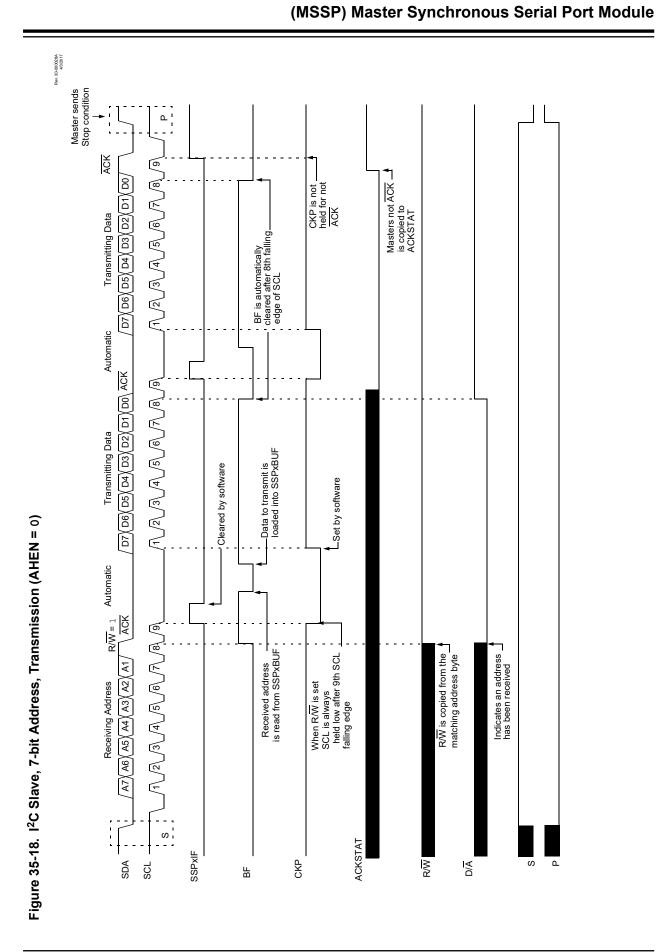

(MSSP) Master Synchronous Serial Port Module

Figure 35-7. SPI Mode Waveform (Slave Mode with CKE = 0)

© 2018 Microchip Technology Inc.

(MSSP) Master Synchronous Serial Port Module

© 2018 Microchip Technology Inc.

### 35.9.7 SSPxMSK

| Name:    | SSPxMSK     |

|----------|-------------|

| Address: | 0x18E,0x198 |

### MSSP Address Mask Register

| Bit    | 7   | 6   | 5   | 4        | 3   | 2   | 1   | 0    |

|--------|-----|-----|-----|----------|-----|-----|-----|------|

|        |     |     |     | MSK[6:0] |     |     |     | MSK0 |

| Access | R/W | R/W | R/W | R/W      | R/W | R/W | R/W | R/W  |

| Reset  | 1   | 1   | 1   | 1        | 1   | 1   | 1   | 1    |

### Bits 7:1 - MSK[6:0] Mask bits

| Value | Mode                   | Description                                                                                |

|-------|------------------------|--------------------------------------------------------------------------------------------|

| 1     | I <sup>2</sup> C Slave | The received address bit n is compared to SSPxADD bit n to detect I <sup>2</sup> C address |

|       |                        | match                                                                                      |

| 0     | I <sup>2</sup> C Slave | The received address bit n is not used to detect I <sup>2</sup> C address match            |

### Bit 0 – MSK0

Mask bit for I<sup>2</sup>C 10-bit Slave mode

| Value | Mode                          | Description                                                                        |

|-------|-------------------------------|------------------------------------------------------------------------------------|

| 1     | I <sup>2</sup> C 10-bit Slave | The received address bit 0 is compared to SSPxADD bit 0 to detect I <sup>2</sup> C |

|       |                               | address match                                                                      |

| 0     | I <sup>2</sup> C 10-bit Slave | The received address bit 0 is not used to detect I <sup>2</sup> C address match    |

| Х     | SPI or I <sup>2</sup> C 7-bit | Don't care                                                                         |

Important: The TSR register is not mapped in data memory, so it is not available to the user.

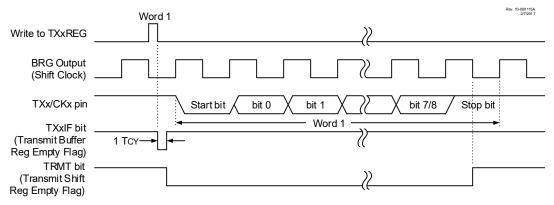

### 36.1.1.6 Transmitting 9-Bit Characters

The EUSART supports 9-bit character transmissions. When the TX9 bit of the TXxSTA register is set, the EUSART will shift nine bits out for each character transmitted. The TX9D bit of the TXxSTA register is the ninth, and Most Significant data bit. When transmitting 9-bit data, the TX9D data bit must be written before writing the eight Least Significant bits into the TXxREG. All nine bits of data will be transferred to the TSR shift register immediately after the TXxREG is written.

A special 9-bit Address mode is available for use with multiple receivers. See the 36.1.2.7 Address Detection section for more information on the Address mode.

### 36.1.1.7 Asynchronous Transmission Setup

- 1. Initialize the SPxBRGH, SPxBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see 36.2 EUSART Baud Rate Generator (BRG)).

- 2. Select the transmit output pin by writing the appropriate value to the RxyPPS register.

- 3. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 4. If 9-bit transmission is desired, set the TX9 control bit. A set ninth data bit will indicate that the eight Least Significant data bits are an address when the receiver is set for address detection.

- 5. Set SCKP bit if inverted transmit is desired.

- 6. Enable the transmission by setting the TXEN control bit. This will cause the TXxIF interrupt bit to be set.

- 7. If interrupts are desired, set the TXxIE interrupt enable bit of the PIEx register

- 8. An interrupt will occur immediately provided that the GIE and PEIE bits of the INTCON register are also set.

- 9. If 9-bit transmission is selected, the ninth bit should be loaded into the TX9D data bit.

- 10. Load 8-bit data into the TXxREG register. This will start the transmission.

### Figure 36-3. Asynchronous Transmission

## Instruction Set Summary

| Field | Description                                |

|-------|--------------------------------------------|

| n     | FSR or INDF number. (0-1)                  |

| mm    | Prepost increment-decrement mode selection |

### Table 40-2. Abbreviation Descriptions

| Field | Description     |

|-------|-----------------|

| PC    | Program Counter |

| TO    | Time-Out bit    |

| С     | Carry bit       |

| DC    | Digit Carry bit |

| Z     | Zero bit        |

| PD    | Power-Down bit  |

## 40.2 Standard Instruction Set

## Table 40-3. Instruction Set

| Mnemonic,<br>Operands    |      | Description                 | Cycles | 14-Bit Opcode |      |      |      | Status      |       |  |  |

|--------------------------|------|-----------------------------|--------|---------------|------|------|------|-------------|-------|--|--|

|                          |      | Description                 |        | MSb           |      |      | LSb  | Affected No | Notes |  |  |

| BYTE-ORIENTED OPERATIONS |      |                             |        |               |      |      |      |             |       |  |  |

| ADDWF                    | f, d | Add WREG and f              | 1      | 00            | 0111 | dfff | ffff | C, DC, Z    | 2     |  |  |

| ADDWFC                   | f, d | Add WREG and CARRY bit to f | 1      | 11            | 1101 | dfff | ffff | C, DC, Z    | 2     |  |  |

| ANDWF                    | f, d | AND WREG with f             | 1      | 00            | 0101 | dfff | ffff | Z           | 2     |  |  |

| ASRF                     | f, d | Arithmetic Right Shift      | 1      | 11            | 0111 | dfff | ffff | C, Z        | 2     |  |  |

| LSLF                     | f, d | Logical Left Shift          | 1      | 11            | 0101 | dfff | ffff | C, Z        | 2     |  |  |

| LSRF                     | f, d | Logical Right Shift         | 1      | 11            | 0110 | dfff | ffff | C, Z        | 2     |  |  |

| CLRF                     | f    | Clear f                     | 1      | 00            | 0001 | lfff | ffff | Z           | 2     |  |  |

| CLRW                     | -    | Clear WREG                  | 1      | 00            | 0001 | 0000 | 00xx | Z           |       |  |  |

| COMF                     | f, d | Complement f                | 1      | 00            | 1001 | dfff | ffff | Z           | 2     |  |  |

| DECF                     | f, d | Decrement f                 | 1      | 00            | 0011 | dfff | ffff | Z           | 2     |  |  |

| INCF                     | f, d | Increment f                 | 1      | 00            | 1010 | dfff | ffff | Z           | 2     |  |  |

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

## 41.4 MPLINK Object Linker/MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- · Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 41.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire device instruction set

- Support for fixed-point and floating-point data

- Command-line interface

- Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

### 41.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

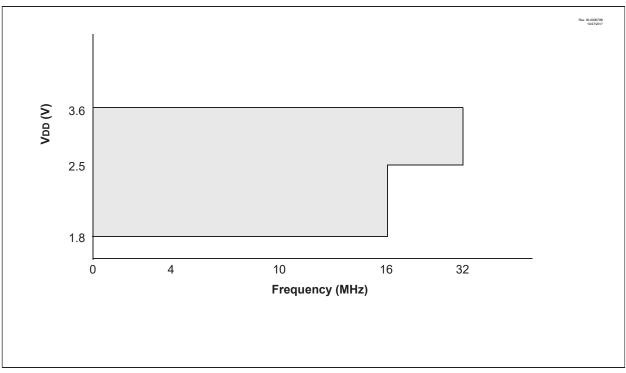

## **Electrical Specifications**

### Note:

- 1. The shaded region indicates the permissible combinations of voltage and frequency.

- 2. Refer to 42.4.1 External Clock/Oscillator Timing Requirements for each Oscillator mode's supported frequencies.

### **Related Links**

42.3.1 Supply Voltage

## 42.3 DC Characteristics

### 42.3.1 Supply Voltage

### Table 42-1.

| PIC16LF1       | 8455/56 only              | /                   |          |         |      |       |                           |  |  |

|----------------|---------------------------|---------------------|----------|---------|------|-------|---------------------------|--|--|

| Standard       | Operating C               | onditions (unless o | therwise | stated) |      |       |                           |  |  |

| Param.<br>No.  | Sym.                      | Characteristic      | Min.     | Typ.†   | Max. | Units | Conditions                |  |  |

| Supply Voltage |                           |                     |          |         |      |       |                           |  |  |

| D002           | V <sub>DD</sub>           |                     | 1.8      |         | 3.6  | V     | F <sub>OSC</sub> ≤ 16 MHz |  |  |

|                |                           |                     | 2.5      |         | 3.6  | V     | F <sub>OSC</sub> > 16 MHz |  |  |

| RAM Data       | a Retention <sup>(1</sup> | )                   |          | 1       | 1    |       |                           |  |  |

## **Electrical Specifications**

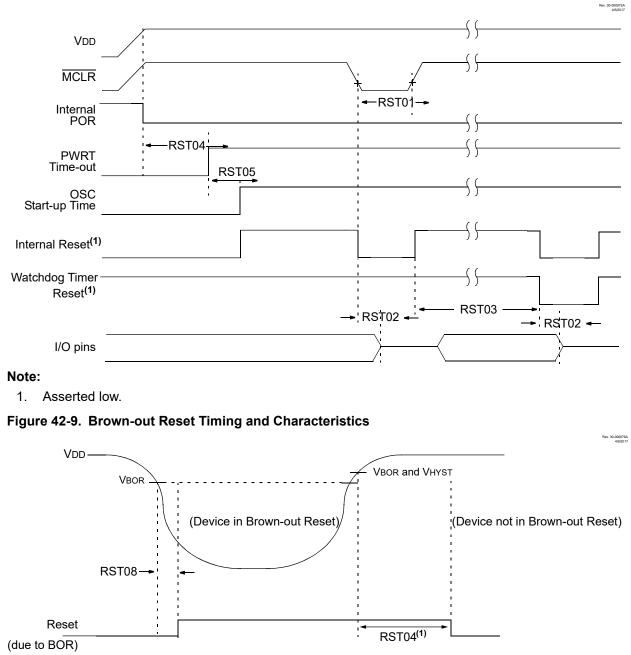

42.4.5 Reset, WDT, Oscillator Start-up Timer, Power-up Timer, Brown-Out Reset and Low-Power Brown-Out Reset Specifications

Figure 42-8. Reset, Watchdog Timer, Oscillator Start-up Timer and Power-up Timer Timing

### Note:

Only if <u>PWRTE</u> bit in the Configuration Word register is programmed to '1'; 2 ms delay if <u>PWRTE</u> = 0.