#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2000                       |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 26                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f18455-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

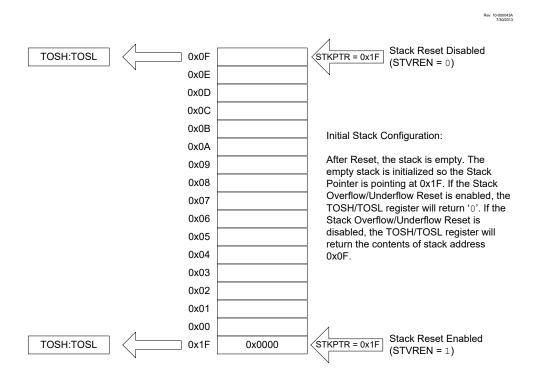

memory left at any given time. The STKPTR always points at the currently used place on the stack. Therefore, a CALL or CALLW will increment the STKPTR and then write the PC, and a return will unload the PC value from the stack and then decrement the STKPTR.

Reference the following figures for examples of accessing the stack.

# Figure 7-4. Accessing the Stack Example 1

#### Figure 7-7. Accessing the Stack Example 4

Rev. 10-000043D 7/30/2013

# Related Links

7.8.11 TOS

#### 7.5.2 Overflow/Underflow Reset

If the STVREN bit in Configuration Word 2 is programmed to '1', the device will be Reset if the stack is PUSHed beyond the sixteenth level or POPed beyond the first level, setting the appropriate bits (STKOVF or STKUNF, respectively) in the PCON register.

#### **Related Links**

4.7.2 CONFIG2

# 7.6 Indirect Addressing

The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the File Select Registers (FSR). If the FSRn address specifies one of the two INDFn registers, the read will return '0' and the write will not occur (though Status bits may be affected). The FSRn register value is created by the pair FSRnH and FSRnL.

The FSR registers form a 16-bit address that allows an addressing space with 65536 locations. These locations are divided into three memory regions:

- Traditional/Banked Data Memory

- Linear Data Memory

- Program Flash Memory

#### 7.10.1 STATUS\_SHAD

Name: STATUS\_SHAD Address: 0x1FE4

Shadow of Status Register

| Bit    | 7 | 6 | 5 | 4  | 3  | 2   | 1   | 0   |

|--------|---|---|---|----|----|-----|-----|-----|

|        |   |   |   | TO | PD | Z   | DC  | С   |

| Access |   |   |   | RO | RO | R/W | R/W | R/W |

| Reset  |   |   |   | х  | х  | х   | х   | x   |

#### Bit 4 – TO Time-Out bit

Reset States: POR/BOR = x

All Other Resets = u

| Value | Description                                                    |

|-------|----------------------------------------------------------------|

| 1     | Set at power-up or by execution of CLRWDT or SLEEP instruction |

| 0     | A WDT time-out occurred                                        |

Bit 3 – PD Power-Down bit

Reset States: POR/BOR = x

All Other Resets = u

| Value | Description                                           |

|-------|-------------------------------------------------------|

| 1     | Set at power-up or by execution of CLRWDT instruction |

| 0     | Cleared by execution of the SLEEP instruction         |

Bit 2 – Z Zero bit

Reset States: POR/BOR = x All Other Resets = u

| Value | Description                                                |

|-------|------------------------------------------------------------|

| 1     | The result of an arithmetic or logic operation is zero     |

| 0     | The result of an arithmetic or logic operation is not zero |

#### Bit 1 – DC Digit Carry/Borrow bit<sup>(1)</sup>

ADDWF, ADDLW, SUBLW, SUBWF instructions

Reset States: POR/BOR = x

All Other Resets = u

| Value | Description                                                   |

|-------|---------------------------------------------------------------|

| 1     | A carry-out from the 4th low-order bit of the result occurred |

| 0     | No carry-out from the 4th low-order bit of the result         |

Bit 0 – C Carry/Borrow bit<sup>(1)</sup>

ADDWF, ADDLW, SUBLW, SUBWF instructions

Reset States: POR/BOR = x

All Other Resets = u

## 10.7.17 PIR6

Name: PIR6 Address: 0x712

PIR6 Peripheral Interrupt Request (Flag) Register 6

| Bit    | 7 | 6 | 5 | 4      | 3      | 2      | 1      | 0      |

|--------|---|---|---|--------|--------|--------|--------|--------|

|        |   |   |   | CCP5IF | CCP4IF | CCP3IF | CCP2IF | CCP1IF |

| Access |   |   |   | R/W/HS | R/W/HS | R/W/HS | R/W/HS | R/W/HS |

| Reset  |   |   |   | 0      | 0      | 0      | 0      | 0      |

Bit 4 – CCP5IF CCP5 Interrupt Flag bit

| Value | Condition    | Description                                                 |

|-------|--------------|-------------------------------------------------------------|

| 1     | Capture mode | Capture occurred (must be cleared in software)              |

| 0     | Capture mode | Capture did not occur                                       |

| 1     | Compare mode | Compare match occurred (must be cleared in software)        |

| 0     | Compare mode | Compare match did not occur                                 |

| 1     | PWM mode     | Output trailing edge occurred (must be cleared in software) |

| 0     | PWM mode     | Output trailing edge did not occur                          |

#### Bit 3 – CCP4IF CCP4 Interrupt Flag bit

| Value | Condition    | Description                                                 |

|-------|--------------|-------------------------------------------------------------|

| 1     | Capture mode | Capture occurred (must be cleared in software)              |

| 0     | Capture mode | Capture did not occur                                       |

| 1     | Compare mode | Compare match occurred (must be cleared in software)        |

| 0     | Compare mode | Compare match did not occur                                 |

| 1     | PWM mode     | Output trailing edge occurred (must be cleared in software) |

| 0     | PWM mode     | Output trailing edge did not occur                          |

# Bit 2 – CCP3IF CCP3 Interrupt Flag bit

| Value | Condition    | Description                                                 |

|-------|--------------|-------------------------------------------------------------|

| 1     | Capture mode | Capture occurred (must be cleared in software)              |

| 0     | Capture mode | Capture did not occur                                       |

| 1     | Compare mode | Compare match occurred (must be cleared in software)        |

| 0     | Compare mode | Compare match did not occur                                 |

| 1     | PWM mode     | Output trailing edge occurred (must be cleared in software) |

| 0     | PWM mode     | Output trailing edge did not occur                          |

#### Bit 1 – CCP2IF CCP2 Interrupt Flag bit

| Value | Condition    | Description                                          |

|-------|--------------|------------------------------------------------------|

| 1     | Capture mode | Capture occurred (must be cleared in software)       |

| 0     | Capture mode | Capture did not occur                                |

| 1     | Compare mode | Compare match occurred (must be cleared in software) |

| 0     | Compare mode | Compare match did not occur                          |

#### 12.8.3 WDTPSH

Name:WDTPSHAddress:0x80F

WWDT Prescale Select High Register (Read-Only)

| Bit    | 7           | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|--------|-------------|----|----|----|----|----|----|----|

|        | PSCNTH[7:0] |    |    |    |    |    |    |    |

| Access | RO          | RO | RO | RO | RO | RO | RO | RO |

| Reset  | 0           | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

Bits 7:0 – PSCNTH[7:0] Prescale Select High Byte bits<sup>(1)</sup>

#### Note:

1. The 18-bit WDT prescale value, PSCNT<17:0> includes the WDTPSL, WDTPSH and the lower bits of the WDTTMR registers. PSCNT<17:0> is intended for debug operations and should be read during normal operation.

#### 14.7.3 PORTC

| Name:    | PORTC |

|----------|-------|

| Address: | 0x00E |

**PORTC Register**

| Bit    | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

|        | RC7 | RC6 | RC5 | RC4 | RC3 | RC2 | RC1 | RC0 |

| Access | R/W |

| Reset  | x   | x   | x   | x   | x   | x   | x   | x   |

#### Bits 0, 1, 2, 3, 4, 5, 6, 7 – RCn Port I/O Value bits Reset States: POR/BOR = xxxxxxx

All Other Resets = uuuuuuuu

| Value | Description               |

|-------|---------------------------|

| 1     | Port pin is $\geq V_{IH}$ |

| 0     | Port pin is $\leq V_{IL}$ |

**Note:** Writes to PORTC are actually written to the corresponding LATC register.

Reads from PORTC register return actual I/O pin values.

## 23.15.4 CMxPCH

| Name:    | CMxPCH      |

|----------|-------------|

| Address: | 0x993,0x997 |

Comparator x Non-Inverting Channel Select Register

|        | РСН |                     |                                         | Ро         | sitive Input S | ource |   |   |

|--------|-----|---------------------|-----------------------------------------|------------|----------------|-------|---|---|

|        | 111 | CxV <sub>P</sub> cc | $CxV_P$ connects to $V_{SS}$            |            |                |       |   |   |

|        | 110 | CxV <sub>P</sub> cc | onnects to FVF                          | R Buffer 2 |                |       |   |   |

|        | 101 | CxV <sub>P</sub> cc | onnects to DA                           | C1 output  |                |       |   |   |

|        | 100 | CxV <sub>P</sub> no | ot connected                            |            |                |       |   |   |

|        | 011 | CxV <sub>P</sub> no | ot connected                            |            |                |       |   |   |

|        | 010 | CxV <sub>P</sub> no | CxV <sub>P</sub> not connected          |            |                |       |   |   |

|        | 001 | CxV <sub>P</sub> co | CxV <sub>P</sub> connects to CxIN1+ pin |            |                |       |   |   |

|        | 000 | CxV <sub>P</sub> co | CxV <sub>P</sub> connects to CxIN0+ pin |            |                |       |   |   |

| Bit    | 7   | 6                   | 6 5 4 3 2 1 0                           |            |                |       |   |   |

|        |     | -                   | PCH[2:0]                                |            |                |       |   |   |

| Access |     |                     | R/W R/W R/W                             |            |                |       |   |   |

| Reset  |     |                     |                                         |            |                | 0     | 0 | 0 |

# Bits 2:0 - PCH[2:0] Comparator Non-Inverting Input Channel Select bits

# 26.11 CCP Special Event Trigger

When any of the CCPs are configured to trigger a special event, the trigger will clear the TMRxH:TMRxL register pair. This special event does not cause a Timer1 interrupt. The CCP module may still be configured to generate a CCP interrupt.

In this mode of operation, the CCPRxH:CCPRxL register pair becomes the period register for Timer1.

Timer1 should be synchronized and F<sub>OSC</sub>/4 should be selected as the clock source in order to utilize the special event trigger. Asynchronous operation of Timer1 can cause a special event trigger to be missed.

In the event that a write to TMRxH or TMRxL coincides with a special event trigger from the CCP, the write will take precedence.

# 26.12 Peripheral Module Disable

When a peripheral is not used or inactive, the module can be disabled by setting the Module Disable bit in the PMD registers. This will reduce power consumption to an absolute minimum. Setting the PMD bits holds the module in Reset and disconnects the module's clock source. The Module Disable bits for Timer1 (TMR1MD) are in the PMD1 register. See Peripheral Module Disable (PMD) chapter for more information.

#### **Related Links**

16.4 Register Summary - PMD

7. When TxTMR = TxPR, the next clock clears TxTMR, regardless of the operating mode.

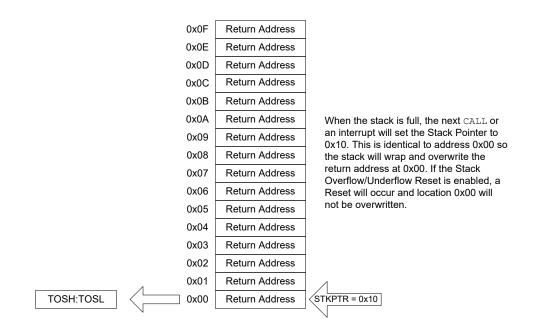

## 28.2.2 CCPTMRS1

| Name:    | CCPTMRS1 |

|----------|----------|

| Address: | 0x21F    |

CCP Timers Control Register

### Bits 2:3, 4:5 - PxTSEL PWMx Timer Selection bits

| Value | Description        |

|-------|--------------------|

| 11    | PWMx based on TMR6 |

| 10    | PWMx based on TMR4 |

| 01    | PWMx based on TMR2 |

| 00    | Reserved           |

### 31.15.6 CWGxAS0

| Name:    | CWGxAS0           |

|----------|-------------------|

| Address: | 0x612,0x61C,0x692 |

CWG Auto-Shutdown Control Register 0

| Bit    | 7         | 6   | 5    | 4      | 3    | 2      | 1 | 0 |

|--------|-----------|-----|------|--------|------|--------|---|---|

|        | SHUTDOWN  | REN | LSBE | D[1:0] | LSAC | C[1:0] |   |   |

| Access | R/W/HS/HC | R/W | R/W  | R/W    | R/W  | R/W    |   |   |

| Reset  | 0         | 0   | 0    | 1      | 0    | 1      |   |   |

**Bit 7 – SHUTDOWN** Auto-Shutdown Event Status bit<sup>(1,2)</sup>

| Value | Description                         |

|-------|-------------------------------------|

| 1     | An auto-shutdown state is in effect |

| 0     | No auto-shutdown event has occurred |

#### Bit 6 – REN Auto-Restart Enable bit

| Value | Description              |

|-------|--------------------------|

| 1     | Auto-restart is enabled  |

| 0     | Auto-restart is disabled |

#### Bits 5:4 – LSBD[1:0] CWGxB and CWGxD Auto-Shutdown State Control bits

| Value | Description                                                                                |

|-------|--------------------------------------------------------------------------------------------|

| 11    | A logic '1' is placed on CWGxB/D when an auto-shutdown event occurs.                       |

| 10    | A logic '0' is placed on CWGxB/D when an auto-shutdown event occurs.                       |

| 01    | Pin is tri-stated on CWGxB/D when an auto-shutdown event occurs.                           |

| 00    | The inactive state of the pin, including polarity, is placed on CWGxB/D after the required |

|       | dead-band interval when an auto-shutdown event occurs.                                     |

### Bits 3:2 - LSAC[1:0] CWGxA and CWGxC Auto-Shutdown State Control bits

| Value | Description                                                                                |

|-------|--------------------------------------------------------------------------------------------|

| 11    | A logic '1' is placed on CWGxA/C when an auto-shutdown event occurs.                       |

| 10    | A logic '0' is placed on CWGxA/C when an auto-shutdown event occurs.                       |

| 01    | Pin is tri-stated on CWGxA/C when an auto-shutdown event occurs.                           |

| 00    | The inactive state of the pin, including polarity, is placed on CWGxA/C after the required |

|       | dead-band interval when an auto-shutdown event occurs.                                     |

#### Note:

- 1. This bit may be written while EN = 0 (31.15.1 CWGxCON0), to place the outputs into the shutdown configuration.

- 2. The outputs will remain in auto-shutdown state until the next rising edge of the CWG data input after this bit is cleared.

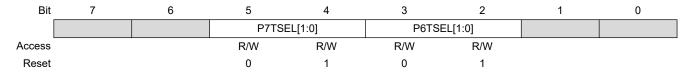

# PIC16(L)F18455/56 (DSM) Data Signal Modulator Module

## Figure 32-1. Simplified Block Diagram of the Data Signal Modulator

# 32.1 DSM Operation

The DSM module can be enabled by setting the EN bit in the MDCON0 register. Clearing the EN bit, disables the output of the module but retain the carrier and source signal selections. The module will resume operation when the EN bit is set again. The output of the DSM module can be rerouted to several pins using the RxyPPS register. When the EN bit is cleared the output pin is held low.

# 32.2 Modulator Signal Sources

The modulator signal can be supplied from the following sources selected with the SRCS bits:

#### • Gate 4: CLCxSEL3

Register number suffixes are different than the gate numbers because other variations of this module have multiple gate selections in the same register.

Data gating is indicated in the right side of Figure 33-2. Only one gate is shown in detail. The remaining three gates are configured identically with the exception that the data enables correspond to the enables for that gate.

#### 33.1.3 Logic Function

There are eight available logic functions including:

- AND-OR

- OR-XOR

- AND

- S-R Latch

- D Flip-Flop with Set and Reset

- D Flip-Flop with Reset

- J-K Flip-Flop with Reset

- Transparent Latch with Set and Reset

Logic functions are shown in the following diagram. Each logic function has four inputs and one output. The four inputs are the four data gate outputs of the previous stage. The output is fed to the inversion stage and from there to other peripherals, an output pin, and back to the CLC itself.

# PIC16(L)F18455/56 (MSSP) Master Synchronous Serial Port Module

© 2018 Microchip Technology Inc.

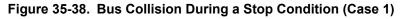

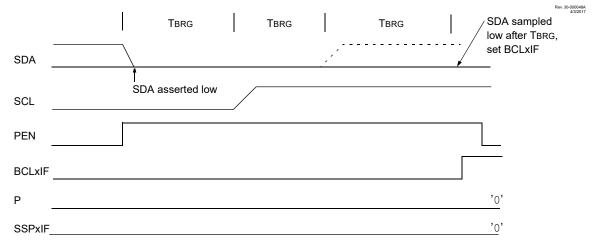

and counts down to zero. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 35-38). If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 35-39).

Figure 35-39. Bus Collision During a Stop Condition (Case 2)

## 35.7 Baud Rate Generator

The MSSP module has a Baud Rate Generator available for clock generation in both I<sup>2</sup>C and SPI Master modes. The Baud Rate Generator (BRG) reload value is placed in the SSPxADD register. When a write occurs to SSPxBUF, the Baud Rate Generator will automatically begin counting down.

Once the given operation is complete, the internal clock will automatically stop counting and the clock pin will remain in its last state.

An internal signal "Reload" shown in Figure 35-40 triggers the value from SSPxADD to be loaded into the BRG counter. This occurs twice for each oscillation of the module clock line. The logic dictating when the reload signal is asserted depends on the mode in which the MSSP is being operated.

© 2018 Microchip Technology Inc.

# PIC16(L)F18455/56 (SMT) Signal Measurement Timer

Rev. 10-000189A

Rev. 10-0001904

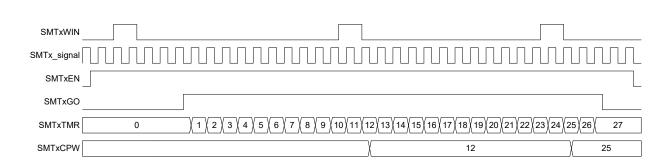

#### Figure 37-17. Counter Mode Timing Diagram

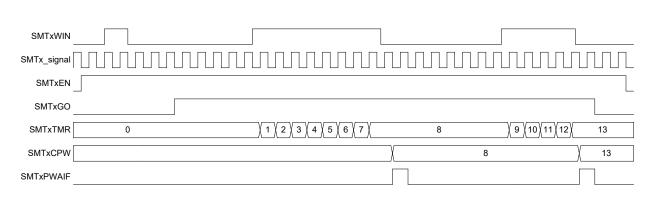

#### 37.1.6.10 Gated Counter Mode

This mode counts pulses on the signal input, gated by the window input. It begins incrementing the timer upon seeing a rising edge of the window input and updates the SMTxCPW register upon a falling edge on the window input. See figures below.

#### Figure 37-18. Gated Counter Mode, Repeat Acquisition Timing Diagram

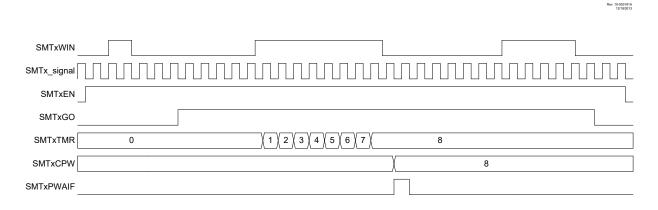

Figure 37-19. Gated Counter Mode, Single Acquisition Timing Diagram

#### 37.1.6.11 Windowed Counter Mode

This mode counts pulses on the signal input, within a window dictated by the window input. It begins counting upon seeing a rising edge of the window input, updates the SMTxCPW register on a falling edge

# PIC16(L)F18455/56

# Register Summary

| -       |          |          |           |       |          |       |              |        |            |        |  |

|---------|----------|----------|-----------|-------|----------|-------|--------------|--------|------------|--------|--|

| Address | Name     | Bit Pos. |           |       |          |       |              |        |            |        |  |

| 0x1E1B  | CLC2POL  | 7:0      | POL       |       |          |       | G4POL        | G3POL  | G2POL      | G1POL  |  |

| 0x1E1C  | CLC2SEL0 | 7:0      |           |       | D1S[5:0] |       |              |        |            |        |  |

| 0x1E1D  | CLC2SEL1 | 7:0      |           |       | D2S[5:0] |       |              |        |            |        |  |

| 0x1E1E  | CLC2SEL2 | 7:0      |           |       | D3S[5:0] |       |              |        |            |        |  |

| 0x1E1F  | CLC2SEL3 | 7:0      |           |       | D4S[5:0] |       |              |        |            |        |  |

| 0x1E20  | CLC2GLS0 | 7:0      | G1D4T     | G1D4N | G1D3T    | G1D3N | G1D2T        | G1D2N  | G1D1T      | G1D1N  |  |

| 0x1E21  | CLC2GLS1 | 7:0      | G2D4T     | G2D4N | G2D3T    | G2D3N | G2D2T        | G2D2N  | G2D1T      | G2D1N  |  |

| 0x1E22  | CLC2GLS2 | 7:0      | G3D4T     | G3D4N | G3D3T    | G3D3N | G3D2T        | G3D2N  | G3D1T      | G3D1N  |  |

| 0x1E23  | CLC2GLS3 | 7:0      | G4D4T     | G4D4N | G4D3T    | G4D3N | G4D2T        | G4D2N  | G4D1T      | G4D1N  |  |

| 0x1E24  | CLC3CON  | 7:0      | EN        |       | OUT      | INTP  | INTN         |        | MODE[2:0]  |        |  |

| 0x1E25  | CLC3POL  | 7:0      | POL       |       |          |       | G4POL        | G3POL  | G2POL      | G1POL  |  |

| 0x1E26  | CLC3SEL0 | 7:0      |           |       |          |       | D1S          | [5:0]  |            |        |  |

| 0x1E27  | CLC3SEL1 | 7:0      |           |       | D2S[5:0] |       |              |        |            |        |  |

| 0x1E28  | CLC3SEL2 | 7:0      |           |       |          |       | D3S          | 5[5:0] |            |        |  |

| 0x1E29  | CLC3SEL3 | 7:0      |           |       | D4S[5:0] |       |              |        |            |        |  |

| 0x1E2A  | CLC3GLS0 | 7:0      | G1D4T     | G1D4N | G1D3T    | G1D3N | G1D2T        | G1D2N  | G1D1T      | G1D1N  |  |

| 0x1E2B  | CLC3GLS1 | 7:0      | G2D4T     | G2D4N | G2D3T    | G2D3N | G2D2T        | G2D2N  | G2D1T      | G2D1N  |  |

| 0x1E2C  | CLC3GLS2 | 7:0      | G3D4T     | G3D4N | G3D3T    | G3D3N | G3D2T        | G3D2N  | G3D1T      | G3D1N  |  |

| 0x1E2D  | CLC3GLS3 | 7:0      | G4D4T     | G4D4N | G4D3T    | G4D3N | G4D2T        | G4D2N  | G4D1T      | G4D1N  |  |

| 0x1E2E  | CLC4CON  | 7:0      | EN        |       | OUT      | INTP  | INTN         |        | MODE[2:0]  |        |  |

| 0x1E2F  | CLC4POL  | 7:0      | POL       |       |          |       | G4POL        | G3POL  | G2POL      | G1POL  |  |

| 0x1E30  | CLC4SEL0 | 7:0      |           |       |          |       |              | 5[5:0] |            |        |  |

| 0x1E31  | CLC4SEL1 | 7:0      |           |       | D2S[5:0] |       |              |        |            |        |  |

| 0x1E32  | CLC4SEL2 | 7:0      |           |       | D3S[5:0] |       |              |        |            |        |  |

| 0x1E33  | CLC4SEL3 | 7:0      |           |       |          | 1     | D4S          | [5:0]  |            |        |  |

| 0x1E34  | CLC4GLS0 | 7:0      | G1D4T     | G1D4N | G1D3T    | G1D3N | G1D2T        | G1D2N  | G1D1T      | G1D1N  |  |

| 0x1E35  | CLC4GLS1 | 7:0      | G2D4T     | G2D4N | G2D3T    | G2D3N | G2D2T        | G2D2N  | G2D1T      | G2D1N  |  |

| 0x1E36  | CLC4GLS2 | 7:0      | G3D4T     | G3D4N | G3D3T    | G3D3N | G3D2T        | G3D2N  | G3D1T      | G3D1N  |  |

| 0x1E37  | CLC4GLS3 | 7:0      | G4D4T     | G4D4N | G4D3T    | G4D3N | G4D2T        | G4D2N  | G4D1T      | G4D1N  |  |

| 0x1E38  |          |          |           |       |          |       |              |        |            |        |  |

|         | Reserved |          |           |       |          |       |              |        |            |        |  |

| 0x1E7F  |          | 0        |           |       |          |       |              |        |            |        |  |

| 0x1E80  | INDF0    | 7:0      |           |       |          |       | 0[7:0]       |        |            |        |  |

| 0x1E81  | INDF1    | 7:0      |           |       |          |       | [1[7:0]      |        |            |        |  |

| 0x1E82  | PCL      | 7:0      |           |       |          |       | .[7:0]<br>PD | 7      | <b>D</b> 2 | 0      |  |

| 0x1E83  | STATUS   | 7:0      |           |       |          | TO    |              | Z      | DC         | С      |  |

| 0x1E84  | FSR0     | 7:0      |           |       |          |       | L[7:0]       |        |            |        |  |

|         | FSR1     | 15:8     | FSRH[7:0] |       |          |       |              |        |            |        |  |

| 0x1E86  |          | 7:0      |           |       |          |       | L[7:0]       |        |            |        |  |

| 0v1E00  | DCD      | 15:8     |           |       |          | FSRI  | H[7:0]       | 0[5:0] |            |        |  |

| 0x1E88  | BSR      | 7:0      |           |       |          |       |              | R[5:0] |            |        |  |

| 0x1E89  | WREG     | 7:0      |           |       |          | WRE   |              |        |            |        |  |

| 0x1E8A  | PCLATH   | 7:0      | CIE       | PEIE  |          |       | PCLATH[6:0]  |        |            |        |  |

| 0x1E8B  | INTCON   | 7:0      | GIE       | PEIE  |          |       |              |        |            | INTEDG |  |

| 0x1E8C  | Reserved |          |           |       |          |       |              |        |            |        |  |

|         |          |          |           |       |          |       |              |        |            |        |  |

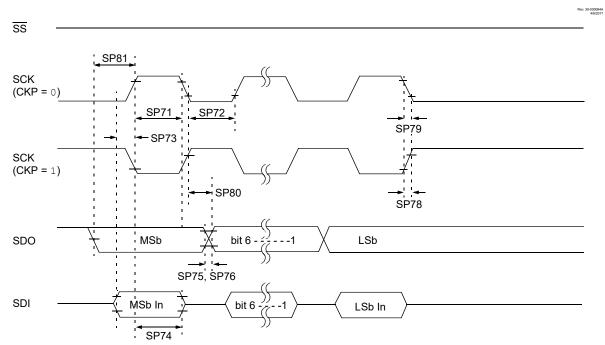

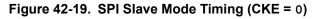

#### 42.4.18 SPI Mode Requirements

#### Table 42-24.

| Param Sym.<br>No. |                                                                           | Characteristic                                             | Min.                        | Тур. † | Max. | Units | Conditions                 |

|-------------------|---------------------------------------------------------------------------|------------------------------------------------------------|-----------------------------|--------|------|-------|----------------------------|

| SP70*             | T <sub>SS</sub> L2 <sub>SC</sub> H,                                       | $\overline{SS}\downarrow$ to SCK $\downarrow$ or           | 2.25*T <sub>CY</sub>        | _      | —    | ns    |                            |

|                   | T <sub>SS</sub> L2 <sub>SC</sub> L                                        | SCK↑ input                                                 |                             |        |      |       |                            |

| SP71*             | T <sub>SC</sub> H                                                         | SCK input high time<br>(Slave mode)                        | T <sub>CY</sub> + 20        | _      |      | ns    |                            |

| SP72*             | T <sub>SC</sub> L                                                         | SCK input low time<br>(Slave mode)                         | T <sub>CY</sub> + 20        |        |      | ns    |                            |

| SP73*             | T <sub>DI</sub> V2 <sub>SC</sub> H,<br>T <sub>DI</sub> V2 <sub>SC</sub> L | Setup time of SDI<br>data input to SCK<br>edge             | 100                         | _      |      | ns    |                            |

| SP74*             | T <sub>SC</sub> H2 <sub>DI</sub> L,<br>T <sub>SC</sub> L2 <sub>DI</sub> L | Hold time of SDI data input to SCK edge                    | 100                         |        |      | ns    |                            |

| SP75*             | T <sub>DO</sub> R                                                         | SDO data output rise                                       |                             | 10     | 25   | ns    | 3.0V≤V <sub>DD</sub> ≤5.5V |

|                   |                                                                           | time                                                       |                             | 25     | 50   | ns    | 1.8V≤V <sub>DD</sub> ≤5.5V |

| SP76*             | T <sub>DO</sub> F                                                         | SDO data output fall time                                  | _                           | 10     | 25   | ns    |                            |

| SP77*             | T <sub>SS</sub> H2 <sub>DO</sub> Z                                        | SS↑ to SDO output<br>high-impedance                        | 10                          |        | 50   | ns    |                            |

| SP78*             | T <sub>SC</sub> R                                                         | SCK output rise time<br>(Master mode)                      | _                           | 10     | 25   | ns    | 3.0V≤V <sub>DD</sub> ≤5.5V |

|                   |                                                                           |                                                            | _                           | 25     | 50   | ns    | 1.8V≤V <sub>DD</sub> ≤5.5V |

| SP79*             | T <sub>SC</sub> F                                                         | SCK output fall time<br>(Master mode)                      |                             | 10     | 25   | ns    |                            |

| SP80*             | T <sub>SC</sub> H2 <sub>DO</sub> V,                                       | SDO data output                                            |                             |        | 50   | ns    | 3.0V≤V <sub>DD</sub> ≤5.5V |

|                   | $T_{SC}L2_{DO}V$                                                          | valid after SCK edge                                       | —                           | _      | 145  | ns    | 1.8V≤V <sub>DD</sub> ≤5.5V |

| SP81*             | T <sub>DO</sub> V2 <sub>SC</sub> H,<br>T <sub>DO</sub> V2 <sub>SC</sub> L | SDO data output setup to SCK edge                          | 1 T <sub>CY</sub>           |        | —    | ns    |                            |

| SP82*             | T <sub>SS</sub> L2 <sub>DO</sub> V                                        | SDO data output valid after $\overline{SS}\downarrow$ edge | _                           | _      | 50   | ns    |                            |

| SP83*             | T <sub>SC</sub> H2 <sub>SS</sub> H,<br>T <sub>SC</sub> L2 <sub>SS</sub> H | SS                                                         | 1.5 T <sub>CY</sub><br>+ 40 | _      |      | ns    |                            |

\* - These parameters are characterized but not tested.

# PIC16(L)F18455/56

# **Electrical Specifications**

Figure 42-18. SPI Master Mode Timing (CKE = 1, SMP = 1)

**Note:** Refer to Figure 42-4 for load conditions.

# 43. DC and AC Characteristics Graphs and Tables

The graphs and tables provided in this section are for design guidance and are not tested. In some graphs or tables, the data presented are outside specified operating range (i.e., outside specified  $V_{DD}$  range). This is for information only and devices are ensured to operate properly only within the specified range. Unless otherwise noted, all graphs apply to both the L and LF devices.

## Note:

The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

### Note:

"Typical" represents the mean of the distribution at 25°C. "Maximum", "Max.", "Minimum" or "Min." represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over each temperature range.