#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 26                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf18455-i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                                                                                                                                                                 | Operation in Sleep Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 481                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32.9.                                                                                                                                                                           | Effects of a Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                       |

| 32.10                                                                                                                                                                           | ). Peripheral Module Disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 481                                                                                                                                                   |

| 32.11                                                                                                                                                                           | I. Register Summary - DSM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 482                                                                                                                                                   |

| 32.12                                                                                                                                                                           | 2. Register Definitions: Modulation Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                       |

|                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                       |

| 33. (CL                                                                                                                                                                         | C) Configurable Logic Cell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                       |

| 33.1.                                                                                                                                                                           | CLC Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 489                                                                                                                                                   |

| 33.2.                                                                                                                                                                           | CLC Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                       |

| 33.3.                                                                                                                                                                           | Output Mirror Copies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                       |

| 33.4.                                                                                                                                                                           | Effects of a Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                       |

| 33.5.                                                                                                                                                                           | Operation During Sleep                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 495                                                                                                                                                   |

| 33.6.                                                                                                                                                                           | CLC Setup Steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 496                                                                                                                                                   |

| 33.7.                                                                                                                                                                           | Register Summary - CLC Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 497                                                                                                                                                   |

| 33.8.                                                                                                                                                                           | Register Definitions: Configurable Logic Cell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                       |

|                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                       |

| 34. Refe                                                                                                                                                                        | erence Clock Output Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 510                                                                                                                                                   |

| 34.1.                                                                                                                                                                           | Clock Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 511                                                                                                                                                   |

| 34.2.                                                                                                                                                                           | Programmable Clock Divider                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 511                                                                                                                                                   |

| 34.3.                                                                                                                                                                           | Selectable Duty Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 512                                                                                                                                                   |

| 34.4.                                                                                                                                                                           | Operation in Sleep Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 512                                                                                                                                                   |

| 34.5.                                                                                                                                                                           | Register Summary: Reference CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 513                                                                                                                                                   |

| 34.6.                                                                                                                                                                           | Register Definitions: Reference Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 513                                                                                                                                                   |

| //                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                       |

| •                                                                                                                                                                               | SP) Master Synchronous Serial Port Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                       |

| 35.1.                                                                                                                                                                           | SPI Mode Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | E40                                                                                                                                                   |

|                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                       |

| 35.2.                                                                                                                                                                           | SPI Mode Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                       |

|                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 518                                                                                                                                                   |

| 35.3.                                                                                                                                                                           | SPI Mode Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 518<br>526                                                                                                                                            |

| 35.3.<br>35.4.                                                                                                                                                                  | SPI Mode Operation<br>I <sup>2</sup> C Mode Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 518<br>526<br>530                                                                                                                                     |

| 35.3.<br>35.4.<br>35.5.                                                                                                                                                         | SPI Mode Operation<br>I <sup>2</sup> C Mode Overview<br>I <sup>2</sup> C Mode Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 518<br>526<br>530<br>534                                                                                                                              |

| 35.3.<br>35.4.<br>35.5.<br>35.6.                                                                                                                                                | SPI Mode Operation<br>I <sup>2</sup> C Mode Overview<br>I <sup>2</sup> C Mode Operation<br>I <sup>2</sup> C Slave Mode Operation                                                                                                                                                                                                                                                                                                                                                                                                                                  | 518<br>526<br>530<br>534<br>553                                                                                                                       |

| 35.3.<br>35.4.<br>35.5.<br>35.6.<br>35.7.                                                                                                                                       | SPI Mode Operation<br>I <sup>2</sup> C Mode Overview<br>I <sup>2</sup> C Mode Operation<br>I <sup>2</sup> C Slave Mode Operation<br>I <sup>2</sup> C Master Mode                                                                                                                                                                                                                                                                                                                                                                                                  | 518<br>526<br>530<br>534<br>553<br>567                                                                                                                |

| 35.3.<br>35.4.<br>35.5.<br>35.6.<br>35.7.<br>35.8.                                                                                                                              | SPI Mode Operation<br>I <sup>2</sup> C Mode Overview<br>I <sup>2</sup> C Mode Operation<br>I <sup>2</sup> C Slave Mode Operation<br>I <sup>2</sup> C Master Mode<br>Baud Rate Generator                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                       |

| 35.3.<br>35.4.<br>35.5.<br>35.6.<br>35.7.<br>35.8.<br>35.8.<br>35.9.                                                                                                            | SPI Mode Operation<br>I <sup>2</sup> C Mode Overview<br>I <sup>2</sup> C Mode Operation<br>I <sup>2</sup> C Slave Mode Operation<br>I <sup>2</sup> C Master Mode<br>Baud Rate Generator<br>Register Summary: MSSP Control<br>Register Definitions: MSSP Control                                                                                                                                                                                                                                                                                                   |                                                                                                                                                       |

| 35.3.<br>35.4.<br>35.5.<br>35.6.<br>35.7.<br>35.8.<br>35.8.<br>35.9.                                                                                                            | SPI Mode Operation<br>I <sup>2</sup> C Mode Overview<br>I <sup>2</sup> C Mode Operation<br>I <sup>2</sup> C Slave Mode Operation<br>I <sup>2</sup> C Master Mode<br>Baud Rate Generator<br>Register Summary: MSSP Control<br>Register Definitions: MSSP Control<br>SART) Enhanced Universal Synchronous Asynchronous Receiver Tra                                                                                                                                                                                                                                 |                                                                                                                                                       |

| 35.3.<br>35.4.<br>35.5.<br>35.6.<br>35.7.<br>35.8.<br>35.8.<br>35.9.                                                                                                            | SPI Mode Operation<br>I <sup>2</sup> C Mode Overview<br>I <sup>2</sup> C Mode Operation<br>I <sup>2</sup> C Slave Mode Operation<br>I <sup>2</sup> C Master Mode<br>Baud Rate Generator<br>Register Summary: MSSP Control<br>Register Definitions: MSSP Control                                                                                                                                                                                                                                                                                                   |                                                                                                                                                       |

| 35.3.<br>35.4.<br>35.5.<br>35.6.<br>35.7.<br>35.8.<br>35.9.<br><b>36. (EU</b>                                                                                                   | SPI Mode Operation<br>I <sup>2</sup> C Mode Overview<br>I <sup>2</sup> C Mode Operation<br>I <sup>2</sup> C Slave Mode Operation<br>I <sup>2</sup> C Master Mode<br>Baud Rate Generator<br>Register Summary: MSSP Control<br>Register Definitions: MSSP Control<br>SART) Enhanced Universal Synchronous Asynchronous Receiver Tra                                                                                                                                                                                                                                 |                                                                                                                                                       |

| 35.3.<br>35.4.<br>35.5.<br>35.6.<br>35.7.<br>35.8.<br>35.9.<br><b>36. (EU</b><br><br>36.1.                                                                                      | SPI Mode Operation<br>I <sup>2</sup> C Mode Overview<br>I <sup>2</sup> C Mode Operation<br>I <sup>2</sup> C Slave Mode Operation<br>I <sup>2</sup> C Master Mode<br>Baud Rate Generator<br>Register Summary: MSSP Control<br>Register Definitions: MSSP Control<br>SART) Enhanced Universal Synchronous Asynchronous Receiver Tra                                                                                                                                                                                                                                 |                                                                                                                                                       |

| 35.3.<br>35.4.<br>35.5.<br>35.6.<br>35.7.<br>35.8.<br>35.9.<br><b>36. (EU</b><br><br>36.1.<br>36.2.                                                                             | SPI Mode Operation<br>I <sup>2</sup> C Mode Overview<br>I <sup>2</sup> C Mode Operation<br>I <sup>2</sup> C Slave Mode Operation<br>I <sup>2</sup> C Master Mode<br>Baud Rate Generator<br>Register Summary: MSSP Control<br>Register Definitions: MSSP Control<br>SART) Enhanced Universal Synchronous Asynchronous Receiver Tra<br>EUSART Asynchronous Mode                                                                                                                                                                                                     |                                                                                                                                                       |

| 35.3.<br>35.4.<br>35.5.<br>35.6.<br>35.7.<br>35.8.<br>35.9.<br><b>36. (EU</b><br><br>36.1.<br>36.2.<br>36.3.                                                                    | SPI Mode Operation<br>I <sup>2</sup> C Mode Overview<br>I <sup>2</sup> C Mode Operation<br>I <sup>2</sup> C Slave Mode Operation<br>I <sup>2</sup> C Master Mode<br>Baud Rate Generator<br>Register Summary: MSSP Control<br>Register Definitions: MSSP Control<br>SART) Enhanced Universal Synchronous Asynchronous Receiver Tra<br>EUSART Asynchronous Mode<br>EUSART Baud Rate Generator (BRG)                                                                                                                                                                 |                                                                                                                                                       |

| 35.3.<br>35.4.<br>35.5.<br>35.6.<br>35.7.<br>35.8.<br>35.9.<br><b>36. (EU</b><br><br>36.1.<br>36.2.<br>36.3.<br>36.4.                                                           | SPI Mode Operation<br>I <sup>2</sup> C Mode Overview<br>I <sup>2</sup> C Mode Operation<br>I <sup>2</sup> C Slave Mode Operation<br>I <sup>2</sup> C Master Mode<br>Baud Rate Generator<br>Register Summary: MSSP Control<br>Register Definitions: MSSP Control<br>SART) Enhanced Universal Synchronous Asynchronous Receiver Tra<br>EUSART Asynchronous Mode<br>EUSART Baud Rate Generator (BRG)<br>EUSART Synchronous Mode                                                                                                                                      | 518<br>526<br>530<br>534<br>553<br>567<br>569<br>569<br>ansmitter<br>581<br>583<br>598<br>598<br>604                                                  |

| 35.3.<br>35.4.<br>35.5.<br>35.6.<br>35.7.<br>35.8.<br>35.9.<br><b>36. (EU</b><br><br>36.1.<br>36.2.<br>36.3.<br>36.4.<br>36.4.<br>36.5.                                         | SPI Mode Operation<br>I <sup>2</sup> C Mode Overview<br>I <sup>2</sup> C Mode Operation<br>I <sup>2</sup> C Slave Mode Operation<br>I <sup>2</sup> C Master Mode<br>Baud Rate Generator<br>Register Summary: MSSP Control<br>Register Definitions: MSSP Control<br>SART) Enhanced Universal Synchronous Asynchronous Receiver Tra<br>EUSART Asynchronous Mode<br>EUSART Baud Rate Generator (BRG)<br>EUSART Synchronous Mode<br>EUSART Operation During Sleep.                                                                                                    |                                                                                                                                                       |

| 35.3.<br>35.4.<br>35.5.<br>35.6.<br>35.7.<br>35.8.<br>35.9.<br><b>36. (EU</b><br><br>36.1.<br>36.2.<br>36.3.<br>36.4.<br>36.5.<br>36.6.                                         | SPI Mode Operation<br>I <sup>2</sup> C Mode Overview<br>I <sup>2</sup> C Mode Operation<br>I <sup>2</sup> C Slave Mode Operation<br>I <sup>2</sup> C Master Mode<br>Baud Rate Generator<br>Register Summary: MSSP Control<br>Register Definitions: MSSP Control<br>SART) Enhanced Universal Synchronous Asynchronous Receiver Tra<br>EUSART Asynchronous Mode<br>EUSART Baud Rate Generator (BRG)<br>EUSART Synchronous Mode<br>EUSART Synchronous Mode<br>EUSART Operation During Sleep<br>Register Summary - EUSART<br>Register Definitions: EUSART Control     |                                                                                                                                                       |

| 35.3.<br>35.4.<br>35.5.<br>35.6.<br>35.7.<br>35.8.<br>35.9.<br><b>36. (EU</b><br><br>36.1.<br>36.2.<br>36.3.<br>36.4.<br>36.5.<br>36.6.                                         | SPI Mode Operation<br>I <sup>2</sup> C Mode Overview<br>I <sup>2</sup> C Mode Operation<br>I <sup>2</sup> C Slave Mode Operation<br>I <sup>2</sup> C Master Mode<br>Baud Rate Generator<br>Register Summary: MSSP Control<br>Register Definitions: MSSP Control<br>SART) Enhanced Universal Synchronous Asynchronous Receiver Tra<br>EUSART Asynchronous Mode<br>EUSART Baud Rate Generator (BRG)<br>EUSART Synchronous Mode<br>EUSART Operation During Sleep<br>Register Summary - EUSART                                                                        |                                                                                                                                                       |

| 35.3.<br>35.4.<br>35.5.<br>35.6.<br>35.7.<br>35.8.<br>35.9.<br><b>36. (EU</b><br><br>36.1.<br>36.2.<br>36.3.<br>36.4.<br>36.4.<br>36.5.<br>36.6.<br><b>37. (SM</b>              | SPI Mode Operation<br>I <sup>2</sup> C Mode Overview<br>I <sup>2</sup> C Mode Operation<br>I <sup>2</sup> C Slave Mode Operation<br>I <sup>2</sup> C Master Mode<br>Baud Rate Generator<br>Register Summary: MSSP Control<br>Register Definitions: MSSP Control<br>SART) Enhanced Universal Synchronous Asynchronous Receiver Tra<br>EUSART Asynchronous Mode<br>EUSART Baud Rate Generator (BRG)<br>EUSART Synchronous Mode<br>EUSART Synchronous Mode<br>EUSART Operation During Sleep<br>Register Summary - EUSART<br>Register Definitions: EUSART Control     |                                                                                                                                                       |

| 35.3.<br>35.4.<br>35.5.<br>35.6.<br>35.7.<br>35.8.<br>35.9.<br>36. (EU<br><br>36.1.<br>36.2.<br>36.3.<br>36.4.<br>36.5.<br>36.5.<br>36.6.<br>37. (SM<br>37.1.                   | SPI Mode Operation<br>I <sup>2</sup> C Mode Overview<br>I <sup>2</sup> C Mode Operation<br>I <sup>2</sup> C Slave Mode Operation<br>I <sup>2</sup> C Master Mode<br>Baud Rate Generator<br>Register Summary: MSSP Control<br>Register Definitions: MSSP Control<br>SART) Enhanced Universal Synchronous Asynchronous Receiver Tra<br>EUSART Asynchronous Mode<br>EUSART Baud Rate Generator (BRG)<br>EUSART Synchronous Mode<br>EUSART Operation During Sleep<br>Register Summary - EUSART<br>Register Definitions: EUSART Control<br>T) Signal Measurement Timer |                                                                                                                                                       |

| 35.3.<br>35.4.<br>35.5.<br>35.6.<br>35.7.<br>35.8.<br>35.9.<br>36. (EU<br><br>36.1.<br>36.2.<br>36.3.<br>36.4.<br>36.3.<br>36.4.<br>36.5.<br>36.6.<br>37. (SM<br>37.1.<br>37.2. | SPI Mode Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 518<br>526<br>530<br>534<br>553<br>567<br>569<br>569<br>569<br>ansmitter<br>581<br>583<br>590<br>598<br>604<br>606<br>606<br>606<br>616<br>616<br>630 |

# 4.7.3 CONFIG3

Name: CONFIG3 Address: 0x8009

**Configuration Word 3**

Windowed Watchdog Timer

| Bit    | 15 | 14   | 13     | 12          | 11  | 10          | 9           | 8   |

|--------|----|------|--------|-------------|-----|-------------|-------------|-----|

|        |    |      |        | WDTCCS[2:0] |     |             | WDTCWS[2:0] |     |

| Access |    |      | R/P    | R/P         | R/P | R/P         | R/P         | R/P |

| Reset  |    |      | 1      | 1           | 1   | 1           | 1           | 1   |

|        |    |      |        |             |     |             |             |     |

| Bit    | 7  | 6    | 5      | 4           | 3   | 2           | 1           | 0   |

|        |    | WDTI | Ξ[1:0] |             |     | WDTCPS[4:0] |             |     |

| Access | U  | R/P  | R/P    | R/P         | R/P | R/P         | R/P         | R/P |

| Reset  | 1  | 1    | 1      | 1           | 1   | 1           | 1           | 1   |

# Bits 13:11 - WDTCCS[2:0] WDT Input Clock Selector bits

| Value  | Description                                                     |

|--------|-----------------------------------------------------------------|

| 111    | Software Control                                                |

| 110 to | Reserved                                                        |

| 011    |                                                                 |

| 010    | 32 kHz SOSC                                                     |

| 001    | WDT reference clock is the 31.25 kHz HFINTOSC (MFINTOSC) output |

| 000    | WDT reference clock is the 31.0 kHz LFINTOSC                    |

## Bits 10:8 - WDTCWS[2:0] WDT Window Select bits

|        | WDTC  | ON1 [WINDOW] a                     | at POR                                  |                                   |                           |

|--------|-------|------------------------------------|-----------------------------------------|-----------------------------------|---------------------------|

| WDTCWS | Value | Window delay<br>Percent of<br>time | Window<br>opening<br>Percent of<br>time | Software<br>control of<br>WINDOW? | Keyed access<br>required? |

| 111    | 111   | n/a                                | 100                                     | Yes                               | No                        |

| 110    | 110   | n/a                                | 100                                     |                                   |                           |

| 101    | 101   | 25                                 | 75                                      | •                                 |                           |

| 100    | 100   | 37.5                               | 62.5                                    | •                                 |                           |

| 011    | 011   | 50                                 | 50                                      | No                                | Yes                       |

| 010    | 010   | 62.5                               | 37.5                                    |                                   |                           |

| 001    | 001   | 75                                 | 25                                      |                                   |                           |

| 000    | 000   | 87.5                               | 12.5                                    |                                   |                           |

Bits 6:5 – WDTE[1:0] WDT Operating Mode bits

# 7.8.3 PCL

| Name:    | PCL                   |

|----------|-----------------------|

| Address: | 0x02 + n*0x80 [n=063] |

Low byte of the Program Counter

| Bit    | 7   | 6   | 5   | 4   | 3     | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-------|-----|-----|-----|

|        |     |     |     | PCL | [7:0] |     |     |     |

| Access | R/W | R/W | R/W | R/W | R/W   | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0   | 0     | 0   | 0   | 0   |

# Bits 7:0 - PCL[7:0]

Provides direct read and write access to the Program Counter

Resets

| BOREN<1:0> | SBOREN | Device<br>Mode | BOR Mode | Instruction Execution upon: Release of POR<br>or Wake-up from Sleep |

|------------|--------|----------------|----------|---------------------------------------------------------------------|

| 11         | Х      | Х              | Active   | Waits for release of BOR <sup>(1)</sup> (BORRDY = 1)                |

| 10 X       |        | Awake          | Active   | Waits for release of BOR (BORRDY = 1) Waits                         |

|            |        | Sleep          | Disabled | for BOR Reset release                                               |

| 01         | 1      | Х              | Active   | Waits for BOR Reset release (BORRDY = 1)                            |

| 01         | 0      | Х              | Disabled | Begins immediately (BORRDY = $x$ )                                  |

| 0 0        | Х      | Х              | Disabled |                                                                     |

## Table 8-1. BOR Operating Conditions

#### Note:

In this specific case, "Release of POR" and "Wake-up from Sleep", there is no delay in start-up. The BOR ready flag, (BORRDY = 1), will be set before the CPU is ready to execute instructions because the BOR circuit is forced on by the BOREN<1:0> bits

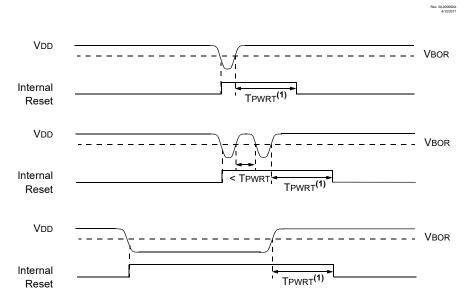

## Figure 8-2. Brown-out Situations

## 8.2.4 BOR is Always OFF

When the BOREN bits of the Configuration Words are programmed to '00', the BOR is off at all times. The device start-up is not delayed by the BOR ready condition or the  $V_{DD}$  level.

# 8.3 Low-Power Brown-out Reset (LPBOR)

The Low-Power Brown-out Reset (LPBOR) provides an additional BOR circuit for low-power operation. Refer to the figure below to see how the BOR interacts with other modules.

# 8.4.1 MCLR Enabled

When  $\overline{\text{MCLR}}$  is enabled and the pin is held low, the device is held in Reset. The  $\overline{\text{MCLR}}$  pin is connected to V<sub>DD</sub> through an internal weak pull-up.

The device has a noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

**Important:** An internal Reset event (RESET instruction, BOR, WWDT, POR, STKOVF, STKUNF) does not drive the MCLR pin low.

# **Related Links**

2.3 Master Clear (MCLR) Pin

## 8.4.2 MCLR Disabled

When  $\overline{\text{MCLR}}$  is disabled, the  $\overline{\text{MCLR}}$  becomes input-only and pin functions such as internal weak pull-ups are under software control.

#### **Related Links**

14.3 I/O Priorities

# 8.5 Windowed Watchdog Timer (WWDT) Reset

The Windowed Watchdog Timer generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period or window set. The  $\overline{TO}$  and  $\overline{PD}$  bits in the STATUS register and the  $\overline{RWDT}$  bit are changed to indicate a WDT Reset. The  $\overline{WDTWV}$  bit indicates if the WDT Reset has occurred due to a timeout or a window violation.

## **Related Links**

7.8.4 STATUS12. (WWDT) Windowed Watchdog Timer

# 8.6 RESET Instruction

A RESET instruction will cause a device Reset. The RI bit will be set to '0'. See *"Reset Condition for Special Registers"* table for default conditions after a RESET instruction has occurred.

# 8.7 Stack Overflow/Underflow Reset

The device can reset when the Stack Overflows or Underflows. The STKOVF or STKUNF bits register indicate the Reset condition. These Resets are enabled by setting the STVREN bit in Configuration Words.

## **Related Links**

4.7.2 CONFIG2 7.5.2 Overflow/Underflow Reset

# 8.8 Programming Mode Exit

Upon exit of Programming mode, the device will behave as if a POR had just occurred.

#### 10.7.9 PIE7

Name: PIE7 Address: 0x71D

Peripheral Interrupt Enable Register 7

| Bit    | 7 | 6 | 5     | 4      | 3 | 2      | 1      | 0      |

|--------|---|---|-------|--------|---|--------|--------|--------|

|        |   |   | NVMIE | NCO1IE |   | CWG3IE | CWG2IE | CWG1IE |

| Access |   |   | R/W   | R/W    |   | R/W    | R/W    | R/W    |

| Reset  |   |   | 0     | 0      |   | 0      | 0      | 0      |

#### Bit 5 – NVMIE NVM Interrupt Enable bit

| Value | Description |

|-------|-------------|

| 1     | Enabled     |

| 0     | Disabled    |

#### Bit 4 - NCO1IE NCO Interrupt Enable bit

| Value | Description |

|-------|-------------|

| 1     | Enabled     |

| 0     | Disabled    |

#### Bit 2 – CWG3IE CWG3 Interrupt Enable bit

| Value | Description |

|-------|-------------|

| 1     | Enabled     |

| 0     | Disabled    |

#### Bit 1 - CWG2IE CWG2 Interrupt Enable bit

| Value | Description |

|-------|-------------|

| 1     | Enabled     |

| 0     | Disabled    |

#### Bit 0 – CWG1IE CWG1 Interrupt Enable bit

| Value | Description |

|-------|-------------|

| 1     | Enabled     |

| 0     | Disabled    |

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt controlled by registers PIE1-PIE8.

# 12.8.5 WDTTMR

Name:WDTTMRAddress:0x810

WDT Timer Register (Read-Only)

| Bit    | 7           | 6  | 5  | 4  | 3  | 2     | 1    | 0       |

|--------|-------------|----|----|----|----|-------|------|---------|

|        | WDTTMR[4:0] |    |    |    |    | STATE | PSCN | IT[1:0] |

| Access | RO          | RO | RO | RO | RO | RO    | RO   | RO      |

| Reset  | 0           | 0  | 0  | 0  | 0  | 0     | 0    | 0       |

## Bits 7:3 – WDTTMR[4:0] Watchdog Window Value bits

| WINDOW | WDT Win     | Open Percent |      |

|--------|-------------|--------------|------|

|        | Closed      | Open         |      |

| 111    | N/A         | 00000-11111  | 100  |

| 110    | 00000-00011 | 00100-11111  | 87.5 |

| 101    | 00000-00111 | 01000-11111  | 75   |

| 100    | 00000-01011 | 01100-11111  | 62.5 |

| 011    | 00000-01111 | 10000-11111  | 50   |

| 010    | 00000-10011 | 10100-11111  | 37.5 |

| 001    | 00000-10111 | 11000-11111  | 25   |

| 000    | 00000-11011 | 11100-11111  | 12.5 |

## Bit 2 – STATE WDT Armed Status bit

| Value | Description      |

|-------|------------------|

| 1     | WDT is armed     |

| 0     | WDT is not armed |

Bits 1:0 – PSCNT[1:0] Prescale Select Upper Byte bits<sup>(1)</sup>

## Note:

1. The 18-bit WDT prescale value, PSCNT<17:0> includes the WDTPSL, WDTPSH and the lower bits of the WDTTMR registers. PSCNT<17:0> is intended for debug operations and should be read during normal operation.

# 13.4.9 WRERR Bit

The WRERR bit can be used to determine if a write error occurred. WRERR will be set if one of the following conditions occurs:

- If WR is set while the NVMADRH:NMVADRL points to a write-protected address

- A Reset occurs while a self-write operation was in progress

- An unlock sequence was interrupted

The WRERR bit is normally set by hardware, but can be set by the user for test purposes. Once set, WRERR must be cleared in software.

| Table 13-3. Actions for P | <b>PFM When WR = 1</b> |

|---------------------------|------------------------|

|---------------------------|------------------------|

| Free | LWLO | Actions for PFM when WR = 1                                           | Comments                                                                                                                                              |

|------|------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | x    | Erase the 32-word row of NVMADRH:NVMADRL location.                    | <ul> <li>If WP is enabled, WR is cleared and<br/>WRERR is set</li> <li>All 32 words are erased</li> <li>NVMDATH:NVMDATL is ignored</li> </ul>         |

| 0    | 1    | Copy NVMDATH:NVMDATL to the write latch corresponding to NVMADR LSBs. | <ul><li>Write protection is ignored</li><li>No memory access occurs</li></ul>                                                                         |

| 0    | 0    | Write the write-latch data to PFM row.                                | <ul> <li>If WP is enabled, WR is cleared and<br/>WRERR is set</li> <li>Write latches are reset to 3FFh</li> <li>NVMDATH:NVMDATL is ignored</li> </ul> |

## **Related Links**

13.4.4 NVMREG Erase of Program Memory

#### 14.4.4 Slew Rate Control

The SLRCONx register controls the slew rate option for each port pin. Slew rate for each port pin can be controlled independently. When an SLRCONx bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONx bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

#### 14.4.5 Input Threshold Control

The INLVLx register controls the input voltage threshold for each of the available PORTx input pins. A selection between the Schmitt Trigger CMOS or the TTL compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTx register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See link below for more information on threshold levels.

**Important:** Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

#### 14.4.6 Analog Control

The ANSELx register is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELx bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELx bits has no effect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing READ-MODIFY-WRITE instructions on the affected port.

# •

**Important:** The ANSELx bits default to the Analog mode after Reset. To use any pins as digital general purpose or peripheral inputs, the corresponding ANSEL bits must be initialized to '0' by user software.

#### 14.4.7 Weak Pull-up Control

The WPUx register controls the individual weak pull-ups for each port pin.

#### 14.4.8 PORTx Functions and Output Priorities

Each PORTx pin is multiplexed with other functions.

Each pin defaults to the PORT latch data after Reset. Other output functions are selected with the peripheral pin select logic, or by enabling an analog output, such as the DAC. See the link below for more information.

Analog input functions, such as ADC and comparator inputs are not shown in the peripheral pin select lists. Digital output functions may continue to control the pin when it is in Analog mode.

#### Related Links

15. (PPS) Peripheral Pin Select Module

# (PPS) Peripheral Pin Select Module

| Output Signal Name | RxyPPS Register Value |

|--------------------|-----------------------|

| NCO1OUT            | 0x18                  |

| PWM6OUT            | 0x0D                  |

| PWM7OUT            | 0x0E                  |

| SCK1               | 0x13                  |

| SCL1               | 0x13                  |

| SDA1               | 0x14                  |

| SDO1               | 0x14                  |

| SCK2               | 0x15                  |

| SCL2               | 0x15                  |

| SDA2               | 0x16                  |

| SDO2               | 0x16                  |

| TMR0OUT            | 0x17                  |

| Note:              |                       |

#### Note:

1. CK1/CK2 and DT1/DT2 are bidirectional signals used in EUSART Synchronous mode.

# 15.3 Bidirectional Pins

PPS selections for peripherals with bidirectional signals on a single pin must be made so that the PPS input and PPS output select the same pin. Peripherals that have bidirectional signals include:

- EUSART (DT/RXxPPS and TX/CKxPPS pins for synchronous operation)

- MSSP (I<sup>2</sup>C SDA/SSPxDATPPS and SCL/SSPxCLKPPS)

# ->

**Important:** The I<sup>2</sup>C default inputs, and a limited number of other alternate pins, are I<sup>2</sup>C and SMBus compatible. Clock and data signals can be routed to any pin, however pins without I<sup>2</sup>C compatibility will operate at standard TTL/ST logic levels as selected by the INLVL register. See the INLVL register for each port to determine which pins are I<sup>2</sup>C and SMBus compatible.

# 15.4 PPS Lock

The PPS includes a mode in which all input and output selections can be locked to prevent inadvertent changes. PPS selections are locked by setting the PPSLOCKED bit of the PPSLOCK register. Setting and clearing this bit requires a special sequence as an extra precaution against inadvertent changes. Examples of setting and clearing the PPSLOCKED bit are shown in the following examples.

Example 15-1. PPS Lock Sequence

```

; suspend interrupts

BCF INTCON,GIE

BANKSEL PPSLOCK ; set bank

```

(ADC2) Analog-to-Digital Converter with Comp...

| Auto-conversion trigger Source           Intil         Software write to ADPCH           Intil         Reserved, do not use           Intil         Software read of ADESH           Intil         Software read of ADERH           Intil         Reserved, do not use           Intil         Suff2_trigger           Intil         Reserved, do not use           Intil         Suff2_trigger           Intil         CLC4_out           Intil         CLC4_out           Intil         CLC2_out           Intil         Logical OR of all Interrupt-on-change Interrupt Flags           Intil         PWM7_out           Intil         PWM7_out           Intil         PWM7_out           Intil         PWM7_out           Intil |       |                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------------------------------------|

| 11100Reserved, do not use11101Software read of ADRESH11000Software read of ADERRH11011Reserved, do not use11010Reserved, do not use11010SMT2_trigger11000CCP5_trigger11010CLC4_out10110CLC2_out10110CLC2_out10110CLC2_out10110CLC1_out10110Clc1_out10110Clc1_out10111Clc2_out10111Clc1_out10111Clc1_out10111Clc1_out10111Clc1_out10111Clc1_out10111Cl_out10111Cl_out10111Cl_out10111Cl_out10111Cl-out10111Cl-out10111Cl-out10111Cl-out11111PWMT_out11111PWMT_out11111Cl-out11111Cl-out11111PWMT_out11111Cl-out11111PWMT_out11111Cl-out11111PWMT_out11111Cl-out11111Cl-out11111Cl-out11111Cl-out11111Cl-out11111PWMT_out11111PWMT_out11111PWMT_out11111Cl-out11111Cl-out11111Cl-out11111Cl-out11111Cl-out                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ACT   | Auto-conversion Trigger Source                        |

| 11101Software read of ADRESH1100Software read of ADERRH1101Reserved, do not use11010Reserved, do not use11010SMT2_trigger11000CCP5_trigger10110CLC4_out10110CLC3_out10110CLC2_out10110CLC2_out10110Clc2_out10111Logical OR of all Interrupt-on-change Interrupt Flags10110C2_out10110Cl_out10111PWM7_out10111PVM7_out10111CP4_trigger10111CCP4_trigger10111CCP4_trigger10111CCP4_trigger10111CCP4_trigger10111MR6_postscaled10111TMR6_postscaled10111TMR5_overflow10111TMR4_postscaled10111TMR4_postscaled10111TMR4_postscaled10111TMR4_postscaled10111TMR4_postscaled10111TMR4_postscaled10111TMR4_postscaled10111TMR4_postscaled10111TMR4_postscaled10111TMR4_postscaled10111TMR4_postscaled10112TMR4_postscaled10113TMR4_postscaled10114TMR4_postscaled10115TMR4_postscaled10116TMR4_postscaled10117TMR4_postscaled10118TMR4_postscaled10119TMR4_postscaled10110TMR4_postscaled                                                                                                                                                                                                                                                                        |       |                                                       |

| 11100         Software read of ADERRH           11011         Reserved, do not use           11010         Reserved, do not use           11010         SMT2_trigger           11010         SMT2_trigger           11010         CCP5_trigger           11010         CCP5_trigger           10111         CLC4_out           10110         CLC2_out           10110         CLC2_out           10101         CLC1_out           10101         CLC2_out           10101         CLC1_out           10101         CLC1_out           10101         Cloat           10101         Cloat           10101         Cloat           10101         Cloqut           10111         Digical OR of all Interrupt-on-change Interrupt Flags           10101         Cloqut           10101         Cloqut           10101         Cloqut           10101         Cloqut           10111         PWM7_out           11111         PWM6_out           11111         PWM6_out           11111         CCP4_trigger           11110         CCP1_trigger           11110         CCP1_tr                                                                                |       |                                                       |

| 11011Reserved, do not use11010Reserved, do not use11001SMT2_trigger11000CCP5_trigger10111CLC4_out10110CLC3_out10110CLC2_out10101CLC3_out10110CLC1_out10101CLC3_out10101CLC1_out10101CL0_out10111Second all Interrupt-on-change Interrupt Flags10110C2_out10110C1_out10111C1_out10111C1_out10111C1_out10111C1_out10111C1_out10111C1_out10111CP1_trigger11111CP1_trigger11111CP2_trigger11111CP2_trigger11111CP2_trigger11111CP1_trigger11111CP1_trigger11111CP1_trigger11111CP1_trigger11111CP1_trigger11111TMR5_overliow11111TMR5_overliow11111TMR5_overliow11111TMR5_overliow11111TMR3_overliow11111TMR3_overliow11111TMR3_overliow11111TMR3_overliow11111TMR3_overliow11111TMR3_overliow11111TMR3_overliow11111TMR3_overliow11111TMR3_overliow11111TMR3_overliow11111TMR3_overliow11111TMR3_overliow                                                                                                                                                                                                                                                                                                                                                    | 11101 | Software read of ADRESH                               |

| 11010         Reserved, do not use           11001         SMT2_trigger           11000         CCP5_trigger           10111         CLC4_out           10110         CLC3_out           10110         CLC2_out           10100         CLC1_out           10101         CLC2_out           10101         CLC2_out           10101         CLC1_out           10101         CLC1_out           10010         CL_out           10011         Logical OR of all Interrupt-on-change Interrupt Flags           10010         C2_out           10010         C1_out           10010         C1_out           10010         C1_out           10011         PWM7_out           10111         PWM7_out           10111         PWM6_out           10111         CCP1_trigger           10110         CCP1_trigger           10110         CCP1_trigger           10110         CCP1_trigger           10110         CCP1_trigger           10110         CCP1_trigger           10110         TMR6_postscaled           10111         TMR4_postscaled           10110         TMR                                                                                | 11100 | Software read of ADERRH                               |

| 11001         SMT2_trigger           11000         CCP5_trigger           10111         CLC4_out           10110         CLC3_out           10101         CLC2_out           10100         CLC1_out           10101         CLC1_out           10010         CLC1_out           10010         CL_0ut           10011         Logical OR of all Interrupt-on-change Interrupt Flags           10010         C2_out           10010         C1_out           10011         Cl_out           10010         C1_out           10010         Cl_out           10011         Cl_out           10011         Cl_out           10011         Cl_out           10011         Cl_out           10111         PWM7_out           10111         PWM6_out           10111         CCP4_trigger           10110         CCP1_trigger           10110         CCP1_trigger           10110         CCP1_trigger           10110         CCP1_trigger           10110         TMR6_postscaled           10111         TMR4_postscaled           10111         TMR3_overflow                                                                                                | 11011 | Reserved, do not use                                  |

| International         International           11000         CCP5_trigger           10111         CLC4_out           10110         CLC3_out           10101         CLC2_out           10100         CLC1_out           10011         Logical OR of all Interrupt-on-change Interrupt Flags           10010         C2_out           10011         Logical OR of all Interrupt-on-change Interrupt Flags           10010         C2_out           10011         Clout           10011         C2_out           10011         C1_out           10001         C1_out           10001         C1_out           10001         C1_out           10001         C1_out           11001         PWM7_out           11111         PWM6_out           11111         PWM6_out           11110         CCP4_trigger           1110         CCP4_trigger           1110         CCP1_trigger           1111         CCP1_trigger           1111         CCP1_trigger           1111         CCP1_trigger           1111         TMR6_postscaled           1111         TMR3_overflow           11                                                                       | 11010 | Reserved, do not use                                  |

| 10111CLC4_out10110CLC3_out10101CLC2_out10100CLC1_out10010Cl_out10010C2_out10010C1_out10010C1_out10010C1_out10011C1_out10011C1_out10011C1_out10011C1_out10011C1_out10111PWM7_out11110CCP4_trigger11101CCP3_trigger11101CCP2_trigger11101CCP1_trigger11101TMR6_postscaled11101TMR5_overflow11101TMR3_overflow11101TMR2_postscaled11101TMR2_postscaled1111TMR2_postscaled1111TMR1_overflow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11001 | SMT2_trigger                                          |

| Initial         CLC3_out           10110         CLC3_out           10100         CLC1_out           10010         CLC1_out           10010         Cl_out           10010         C2_out           10010         C2_out           10010         C1_out           10010         C1_out           10010         C1_out           10000         NCO1_out           10111         PWM7_out           10111         PWM6_out           10111         CCP4_trigger           10101         CCP3_trigger           10101         CCP1_trigger           10101         CCP1_trigger           10101         SMT1_trigger           10101         TMR6_postscaled           10111         TMR3_overflow           10110         TMR3_overflow           10110         TMR2_postscaled                                                                                                                                                                                                                                                                                                                                                                             | 11000 | CCP5_trigger                                          |

| 10101CLC2_out10100CLC1_out10011Logical OR of all Interrupt-on-change Interrupt Flags10010C2_out10010C1_out10000NC01_out10011PWM7_out01110PWM6_out01101CCP4_trigger01101CCP2_trigger01010CCP1_trigger01011SMT1_trigger01010TMR6_postscaled01110TMR4_postscaled01010TMR3_overflow01010TMR2_postscaled00111TMR1_overflow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10111 | CLC4_out                                              |