Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 26                                                                           |

| Program Memory Size        | 14KB (8K x 14)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 256 x 8                                                                      |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 28-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf18455t-i-so |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 24.4. ZCD Interrupts                                           | 355 |

|----------------------------------------------------------------|-----|

| 24.5. Correction for Z <sub>CPINV</sub> Offset                 | 355 |

| 24.6. Handling V <sub>PEAK</sub> Variations                    | 357 |

| 24.7. Operation During Sleep                                   | 358 |

| 24.8. Effects of a Reset                                       |     |

| 24.9. Disabling the ZCD Module                                 | 358 |

| 24.10. Register Summary: ZCD Control                           |     |

| 24.11. Register Definitions: ZCD Control                       |     |

| 25. Timer0 Module                                              | 361 |

| 25.1. Timer0 Operation                                         |     |

| 25.2. Clock Selection                                          |     |

| 25.3. Timer0 Output and Interrupt                              |     |

| 25.4. Operation During Sleep                                   |     |

| 25.5. Register Summary - Timer0                                |     |

| 25.6. Register Definitions: Timer0 Control                     |     |

| 26. Timer1 Module with Gate Control                            |     |

| 26.1. Timer1 Operation                                         |     |

| 26.2. Clock Source Selection                                   |     |

| 26.3. Timer1 Prescaler                                         |     |

| 26.4. Secondary Oscillator                                     |     |

| 26.5. Timer1 Operation in Asynchronous Counter Mode            |     |

| 26.6. Timer1 16-Bit Read/Write Mode                            |     |

| 26.7. Timer1 Gate                                              |     |

| 26.8. Timer1 Interrupt                                         |     |

| 26.9. Timer1 Operation During Sleep                            |     |

| 26.10. CCP Capture/Compare Time Base                           |     |

| 26.11. CCP Special Event Trigger                               |     |

| 26.12. Peripheral Module Disable                               |     |

| 26.13. Register Summary - Timer1                               |     |

| 26.14. Register Definitions: Timer1                            |     |

| 27. Timer2 Module                                              |     |

| 27.1. Timer2 Operation                                         |     |

| 27.2. Timer2 Output                                            |     |

| 27.3. External Reset Sources                                   |     |

| 27.4. Timer2 Interrupt                                         |     |

| 27.5. Operating Modes                                          |     |

| 27.6. Operation Examples                                       |     |

| 27.7. Timer2 Operation During Sleep                            |     |

| 27.8. Register Summary - Timer2                                |     |

| 27.9. Register Definitions: Timer2 Control                     |     |

| 28. CCP/PWM Timer Resource Selection                           | 417 |

| 28.1. Register Summary - Timer Selection Registers for CCP/PWM | 418 |

| 28.2. Register Definitions: CCP/PWM Timer Selection            |     |

| -                                                              |     |

| -0. 0 ar                                                                                                                                                | oture/Compare/PWM Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 421                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 29.1                                                                                                                                                    | CCP Module Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 421                                                                                                                               |

| 29.2                                                                                                                                                    | Capture Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 422                                                                                                                               |

| 29.3                                                                                                                                                    | Compare Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 424                                                                                                                               |

| 29.4                                                                                                                                                    | . PWM Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 426                                                                                                                               |

|                                                                                                                                                         | . Register Summary - CCP Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                   |

|                                                                                                                                                         | Register Definitions: CCP Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                   |

| 30. (PV                                                                                                                                                 | /M) Pulse-Width Modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 436                                                                                                                             |

| •                                                                                                                                                       | . Fundamental Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                   |

|                                                                                                                                                         | PWM Output Polarity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                   |

|                                                                                                                                                         | PWM Period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                   |

|                                                                                                                                                         | PWM Duty Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                   |

|                                                                                                                                                         | PWM Resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                   |

|                                                                                                                                                         | Operation in Sleep Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                   |

|                                                                                                                                                         | Changes in System Clock Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                   |

|                                                                                                                                                         | Effects of Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                   |

|                                                                                                                                                         | Setup for PWM Operation using PWMx Output Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                   |

|                                                                                                                                                         | 0. Setup for PWM Operation to Other Device Peripherals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                   |

|                                                                                                                                                         | 1. Register Summary - Registers Associated with PWM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                   |

|                                                                                                                                                         | 2. Register Definitions: PWM Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                   |

| 30.1                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 441                                                                                                                               |

| 31. (CV                                                                                                                                                 | VG) Complementary Waveform Generator Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 444                                                                                                                               |

| 31.1                                                                                                                                                    | Fundamental Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 444                                                                                                                               |

|                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                   |

|                                                                                                                                                         | . Operating Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 444                                                                                                                               |

|                                                                                                                                                         | . Operating Modes<br>Start-up Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                   |

| 31.3                                                                                                                                                    | Start-up Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 456                                                                                                                               |

| 31.3<br>31.4                                                                                                                                            | Start-up Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 456<br>456                                                                                                                        |

| 31.3<br>31.4<br>31.5                                                                                                                                    | Start-up Considerations<br>Clock Source<br>Selectable Input Sources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 456<br>456<br>456                                                                                                                 |

| 31.3<br>31.4<br>31.5<br>31.6                                                                                                                            | Start-up Considerations<br>Clock Source<br>Selectable Input Sources<br>Output Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 456<br>456<br>456<br>457                                                                                                          |

| 31.3<br>31.4<br>31.5<br>31.6<br>31.7                                                                                                                    | <ul> <li>Start-up Considerations.</li> <li>Clock Source.</li> <li>Selectable Input Sources.</li> <li>Output Control.</li> <li>Dead-Band Control.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 456<br>456<br>456<br>457<br>457                                                                                                   |

| 31.3<br>31.4<br>31.5<br>31.6<br>31.7<br>31.8                                                                                                            | <ul> <li>Start-up Considerations</li> <li>Clock Source</li> <li>Selectable Input Sources</li> <li>Output Control</li> <li>Dead-Band Control</li> <li>Rising Edge and Reverse Dead Band</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                   | 456<br>456<br>456<br>457<br>457<br>457                                                                                            |

| 31.3<br>31.4<br>31.5<br>31.6<br>31.7<br>31.8<br>31.9                                                                                                    | <ul> <li>Start-up Considerations</li> <li>Clock Source</li> <li>Selectable Input Sources</li> <li>Output Control</li> <li>Dead-Band Control</li> <li>Rising Edge and Reverse Dead Band</li> <li>Falling Edge and Forward Dead Band</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                       | 456<br>456<br>456<br>457<br>457<br>457<br>458                                                                                     |

| 31.3<br>31.4<br>31.5<br>31.6<br>31.7<br>31.8<br>31.9<br>31.1                                                                                            | <ul> <li>Start-up Considerations.</li> <li>Clock Source.</li> <li>Selectable Input Sources.</li> <li>Output Control.</li> <li>Dead-Band Control.</li> <li>Rising Edge and Reverse Dead Band.</li> <li>Falling Edge and Forward Dead Band.</li> <li>0. Dead-Band Jitter.</li> </ul>                                                                                                                                                                                                                                                                                                                                                  | 456<br>456<br>457<br>457<br>457<br>457<br>458<br>459                                                                              |

| 31.3<br>31.4<br>31.5<br>31.6<br>31.7<br>31.8<br>31.9<br>31.1<br>31.1                                                                                    | <ul> <li>Start-up Considerations.</li> <li>Clock Source.</li> <li>Selectable Input Sources.</li> <li>Output Control.</li> <li>Dead-Band Control.</li> <li>Rising Edge and Reverse Dead Band.</li> <li>Falling Edge and Forward Dead Band.</li> <li>Dead-Band Jitter.</li> <li>Auto-Shutdown.</li> </ul>                                                                                                                                                                                                                                                                                                                             | 456<br>456<br>457<br>457<br>457<br>457<br>458<br>459<br>459                                                                       |

| 31.3<br>31.4<br>31.5<br>31.6<br>31.7<br>31.8<br>31.9<br>31.1<br>31.1<br>31.1                                                                            | <ul> <li>Start-up Considerations</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 456<br>456<br>457<br>457<br>457<br>457<br>458<br>459<br>459<br>462                                                                |

| 31.3<br>31.4<br>31.5<br>31.6<br>31.7<br>31.8<br>31.9<br>31.1<br>31.1<br>31.1<br>31.1                                                                    | <ul> <li>Start-up Considerations.</li> <li>Clock Source.</li> <li>Selectable Input Sources.</li> <li>Output Control.</li> <li>Dead-Band Control.</li> <li>Rising Edge and Reverse Dead Band.</li> <li>Falling Edge and Forward Dead Band.</li> <li>Dead-Band Jitter.</li> <li>Auto-Shutdown.</li> <li>Operation During Sleep.</li> <li>Configuring the CWG.</li> </ul>                                                                                                                                                                                                                                                              | 456<br>456<br>457<br>457<br>457<br>457<br>458<br>459<br>459<br>459<br>462<br>462                                                  |

| 31.3<br>31.4<br>31.5<br>31.6<br>31.7<br>31.8<br>31.9<br>31.1<br>31.1<br>31.1<br>31.1<br>31.1                                                            | <ul> <li>Start-up Considerations.</li> <li>Clock Source.</li> <li>Selectable Input Sources.</li> <li>Output Control.</li> <li>Dead-Band Control.</li> <li>Rising Edge and Reverse Dead Band.</li> <li>Falling Edge and Forward Dead Band.</li> <li>Dead-Band Jitter.</li> <li>Auto-Shutdown.</li> <li>Operation During Sleep.</li> <li>Configuring the CWG.</li> <li>Register Summary - CWG Control.</li> </ul>                                                                                                                                                                                                                     | 456<br>456<br>457<br>457<br>457<br>457<br>459<br>459<br>459<br>462<br>462<br>464                                                  |

| 31.3<br>31.4<br>31.5<br>31.6<br>31.7<br>31.8<br>31.9<br>31.1<br>31.1<br>31.1<br>31.1<br>31.1<br>31.1                                                    | <ul> <li>Start-up Considerations.</li> <li>Clock Source.</li> <li>Selectable Input Sources.</li> <li>Output Control.</li> <li>Dead-Band Control.</li> <li>Rising Edge and Reverse Dead Band.</li> <li>Falling Edge and Forward Dead Band.</li> <li>Dead-Band Jitter.</li> <li>Auto-Shutdown.</li> <li>Operation During Sleep.</li> <li>Configuring the CWG.</li> <li>Register Summary - CWG Control.</li> <li>Register Definitions: CWG Control.</li> </ul>                                                                                                                                                                         | 456<br>456<br>457<br>457<br>457<br>457<br>459<br>459<br>459<br>462<br>462<br>464<br>464                                           |

| 31.3<br>31.4<br>31.5<br>31.6<br>31.7<br>31.8<br>31.9<br>31.1<br>31.1<br>31.1<br>31.1<br>31.1<br>31.1<br>31.1                                            | <ul> <li>Start-up Considerations.</li> <li>Clock Source.</li> <li>Selectable Input Sources.</li> <li>Output Control.</li> <li>Dead-Band Control.</li> <li>Rising Edge and Reverse Dead Band.</li> <li>Falling Edge and Forward Dead Band.</li> <li>Dead-Band Jitter.</li> <li>Auto-Shutdown.</li> <li>Operation During Sleep.</li> <li>Configuring the CWG.</li> <li>Register Summary - CWG Control.</li> <li>Register Definitions: CWG Control.</li> <li>M) Data Signal Modulator Module.</li> </ul>                                                                                                                               | 456<br>456<br>457<br>457<br>457<br>457<br>457<br>459<br>459<br>462<br>462<br>464<br>464<br>475                                    |

| 31.3<br>31.4<br>31.5<br>31.6<br>31.7<br>31.8<br>31.9<br>31.1<br>31.1<br>31.1<br>31.1<br>31.1<br>31.1<br>31.1                                            | <ul> <li>Start-up Considerations.</li> <li>Clock Source.</li> <li>Selectable Input Sources.</li> <li>Output Control.</li> <li>Dead-Band Control.</li> <li>Rising Edge and Reverse Dead Band.</li> <li>Falling Edge and Forward Dead Band.</li> <li>Dead-Band Jitter.</li> <li>Auto-Shutdown.</li> <li>Operation During Sleep.</li> <li>Configuring the CWG.</li> <li>Register Summary - CWG Control.</li> <li>Register Definitions: CWG Control.</li> </ul>                                                                                                                                                                         | 456<br>456<br>457<br>457<br>457<br>457<br>457<br>459<br>459<br>462<br>462<br>464<br>464<br>475                                    |

| 31.3<br>31.4<br>31.5<br>31.6<br>31.7<br>31.8<br>31.9<br>31.1<br>31.1<br>31.1<br>31.1<br>31.1<br>31.1<br>31.1                                            | <ul> <li>Start-up Considerations.</li> <li>Clock Source.</li> <li>Selectable Input Sources.</li> <li>Output Control.</li> <li>Dead-Band Control.</li> <li>Rising Edge and Reverse Dead Band.</li> <li>Falling Edge and Forward Dead Band.</li> <li>Dead-Band Jitter.</li> <li>Auto-Shutdown.</li> <li>Operation During Sleep.</li> <li>Configuring the CWG.</li> <li>Register Summary - CWG Control.</li> <li>Register Definitions: CWG Control.</li> <li>M) Data Signal Modulator Module.</li> <li>Modulator Signal Sources.</li> </ul>                                                                                            | 456<br>456<br>457<br>457<br>457<br>457<br>458<br>459<br>459<br>462<br>462<br>464<br>464<br>475<br>476                             |

| 31.3<br>31.4<br>31.5<br>31.6<br>31.7<br>31.8<br>31.9<br>31.1<br>31.1<br>31.1<br>31.1<br>31.1<br>31.1<br>31.1                                            | <ul> <li>Start-up Considerations.</li> <li>Clock Source.</li> <li>Selectable Input Sources.</li> <li>Output Control.</li> <li>Dead-Band Control.</li> <li>Rising Edge and Reverse Dead Band.</li> <li>Falling Edge and Forward Dead Band.</li> <li>Dead-Band Jitter.</li> <li>Auto-Shutdown.</li> <li>Operation During Sleep.</li> <li>Configuring the CWG.</li> <li>Register Summary - CWG Control.</li> <li>5. Register Definitions: CWG Control.</li> <li>M) Data Signal Modulator Module.</li> <li>DSM Operation.</li> </ul>                                                                                                    | 456<br>456<br>457<br>457<br>457<br>457<br>458<br>459<br>459<br>462<br>462<br>464<br>464<br>475<br>476                             |

| 31.3<br>31.4<br>31.5<br>31.6<br>31.7<br>31.8<br>31.9<br>31.1<br>31.1<br>31.1<br>31.1<br>31.1<br>31.1<br>31.1                                            | <ul> <li>Start-up Considerations.</li> <li>Clock Source.</li> <li>Selectable Input Sources.</li> <li>Output Control.</li> <li>Dead-Band Control.</li> <li>Rising Edge and Reverse Dead Band.</li> <li>Falling Edge and Forward Dead Band.</li> <li>Dead-Band Jitter.</li> <li>Auto-Shutdown.</li> <li>Operation During Sleep.</li> <li>Configuring the CWG.</li> <li>Register Summary - CWG Control.</li> <li>Register Definitions: CWG Control.</li> <li>M) Data Signal Modulator Module.</li> <li>DSM Operation.</li> <li>Modulator Signal Sources.</li> <li>Carrier Signal Sources.</li> <li>Carrier Synchronization.</li> </ul> | 456<br>456<br>457<br>457<br>457<br>457<br>459<br>459<br>462<br>462<br>464<br>464<br>475<br>476<br>476<br>477<br>479               |

| 31.3<br>31.4<br>31.5<br>31.6<br>31.7<br>31.8<br>31.9<br>31.1<br>31.1<br>31.1<br>31.1<br>31.1<br>31.1<br>31.1                                            | <ul> <li>Start-up Considerations</li> <li>Clock Source</li> <li>Selectable Input Sources</li> <li>Output Control</li> <li>Dead-Band Control</li> <li>Rising Edge and Reverse Dead Band</li> <li>Falling Edge and Forward Dead Band</li> <li>Dead-Band Jitter.</li> <li>Auto-Shutdown</li> <li>Operation During Sleep</li></ul>                                                                                                                                                                                                                                                                                                      | 456<br>456<br>457<br>457<br>457<br>457<br>459<br>459<br>462<br>462<br>464<br>464<br>475<br>476<br>476<br>477<br>479               |

| 31.3<br>31.4<br>31.5<br>31.6<br>31.7<br>31.8<br>31.9<br>31.1<br>31.1<br>31.1<br>31.1<br>31.1<br>31.1<br>32. (DS<br>32.1<br>32.2<br>32.3<br>32.4<br>32.5 | <ul> <li>Start-up Considerations.</li> <li>Clock Source.</li> <li>Selectable Input Sources.</li> <li>Output Control.</li> <li>Dead-Band Control.</li> <li>Rising Edge and Reverse Dead Band.</li> <li>Falling Edge and Forward Dead Band.</li> <li>Dead-Band Jitter.</li> <li>Auto-Shutdown.</li> <li>Operation During Sleep.</li> <li>Configuring the CWG.</li> <li>Register Summary - CWG Control.</li> <li>Register Definitions: CWG Control.</li> <li>M) Data Signal Modulator Module.</li> <li>DSM Operation.</li> <li>Modulator Signal Sources.</li> <li>Carrier Signal Sources.</li> <li>Carrier Synchronization.</li> </ul> | 456<br>456<br>457<br>457<br>457<br>457<br>458<br>459<br>459<br>462<br>462<br>464<br>464<br>475<br>476<br>476<br>479<br>479<br>481 |

#### 9.6.1 OSCCON1

| Name:    | OSCCON1 |

|----------|---------|

| Address: | 0x88D   |

Oscillator Control Register1

| Bit    | 7 | 6   | 5         | 4   | 3   | 2   | 1      | 0   |

|--------|---|-----|-----------|-----|-----|-----|--------|-----|

|        |   |     | NOSC[2:0] |     |     | NDI | /[3:0] |     |

| Access |   | R/W | R/W       | R/W | R/W | R/W | R/W    | R/W |

| Reset  |   | f   | f         | f   | q   | q   | q      | q   |

#### **Bits 6:4 – NOSC[2:0]** New Oscillator Source Request bits<sup>(1,2,3)</sup>

The setting requests a source oscillator and PLL combination per Table 9-1.

#### Table 9-1. NOSC Bit Settings

| NOSC<2:0> | Clock Source                     |

|-----------|----------------------------------|

| 111       | EXTOSC <sup>(5)</sup>            |

| 110       | HFINTOSC <sup>(6)</sup>          |

| 101       | LFINTOSC                         |

| 100       | SOSC                             |

| 011       | Reserved                         |

| 010       | EXTOSC + 4x PLL <sup>(5)</sup>   |

| 001       | HFINTOSC + 2x PLL <sup>(6)</sup> |

| 000       | Reserved                         |

# Bits 3:0 – NDIV[3:0] New Divider Selection Request bits<sup>(2,3,4)</sup>

The setting determines the new postscaler division ratio per Table 9-2.

#### Table 9-2. NDIV Bit Settings

| NDIV<3:0> | Clock Divider |

|-----------|---------------|

| 1111-1010 | Reserved      |

| 1001      | 512           |

| 1000      | 256           |

| 0111      | 128           |

| 0110      | 64            |

| 0101      | 32            |

| 0100      | 16            |

| 0011      | 8             |

| 0010      | 4             |

#### 11.2.3.1 Sleep Current vs. Wake-up Time

In the default operating mode, the LDO and reference circuitry remain in the normal configuration while in Sleep. The device is able to exit Sleep mode quickly since all circuits remain active. In Low-Power Sleep mode, when waking-up from Sleep, an extra delay time is required for these circuits to return to the normal configuration and stabilize.

The Low-Power Sleep mode is beneficial for applications that stay in Sleep mode for long periods of time. The Normal mode is beneficial for applications that need to wake from Sleep quickly and frequently.

#### 11.2.3.2 Peripheral Usage in Sleep

Some peripherals that can operate in Sleep mode will not operate properly with the Low-Power Sleep mode selected. The Low-Power Sleep mode is intended for use with these peripherals:

- Brown-out Reset (BOR)

- Windowed Watchdog Timer (WWDT)

- External interrupt pin/Interrupt-On-Change pins

- Timer1 (with external clock source)

It is the responsibility of the end user to determine what is acceptable for their application when setting the VREGPM settings in order to ensure operation in Sleep.

**Important:** The LF devices do not have a configurable Low-Power Sleep mode. LFs are unregulated devices and are always in the lowest power state when in Sleep, with no wake-up time penalty. These devices have a lower maximum  $V_{DD}$  and I/O voltage than the F devices.

#### 11.3 Idle Mode

When the Idle Enable (IDLEN) bit is clear (IDLEN = 0), the SLEEP instruction will put the device into full Sleep mode. When IDLEN is set (IDLEN = 1), the SLEEP instruction will put the device into IDLE mode. In IDLE mode, the CPU and memory operations are halted, but the peripheral clocks continue to run. This mode is similar to DOZE mode, except that in IDLE both the CPU and program memory are shut off.

**Important:** Peripherals using F<sub>OSC</sub> will continue running while in Idle (but not in Sleep). Peripherals using HFINTOSC:LFINTOSC will continue running in both Idle and Sleep.

**Important:** If  $\overline{CLKOUTEN}$  is enabled ( $\overline{CLKOUTEN} = 0$ , Configuration Word 1), the output will continue operating while in Idle.

#### 11.3.1 Idle and Interrupts

IDLE mode ends when an interrupt occurs (even if GIE = 0), but IDLEN is not changed. The device can re-enter IDLE by executing the SLEEP instruction.

If Recover-on-Interrupt is enabled (ROI = 1), the interrupt that brings the device out of Idle also restores full-speed CPU execution when doze is also enabled.

# 12.8.2 WDTCON1

| Name:    | WDTCON1 |

|----------|---------|

| Address: | 0x80D   |

#### Watchdog Timer Control Register 1

| Bit    | 7 | 6   | 5          | 4   | 3 | 2   | 1           | 0   |

|--------|---|-----|------------|-----|---|-----|-------------|-----|

|        |   |     | WDTCS[2:0] |     |   |     | WINDOW[2:0] |     |

| Access |   | R/W | R/W        | R/W |   | R/W | R/W         | R/W |

| Reset  |   | q   | q          | q   |   | q   | q           | q   |

#### Bits 6:4 – WDTCS[2:0] Watchdog Timer Clock Select bits

| Value  | Description        |

|--------|--------------------|

| 111 to | Reserved           |

| 010    |                    |

| 001    | MFINTOSC 31.25 kHz |

| 000    | LFINTOSC 31 kHz    |

# Bits 2:0 - WINDOW[2:0] Watchdog Timer Window Select bits

| WINDOW | Window delay Percent of time | Window opening Percent of time |

|--------|------------------------------|--------------------------------|

| 111    | N/A                          | 100                            |

| 110    | 12.5                         | 87.5                           |

| 101    | 25                           | 75                             |

| 100    | 37.5                         | 62.5                           |

| 011    | 50                           | 50                             |

| 010    | 62.5                         | 37.5                           |

| 001    | 75                           | 25                             |

| 000    | 87.5                         | 12.5                           |

#### Note:

- 1. If WDTCCS in CONFIG3 = 111, the Reset value of WDTCS is '000'.

- 2. The Reset value (q) of WINDOW is determined by the value of WDTCWS in the CONFIG3 register.

- 3. If WDTCCS in CONFIG3  $\neq$  111, these bits are read-only.

- 4. If WDTCWS in CONFIG3  $\neq$  111, these bits are read-only.

# 14.7.1 PORTA

Name:PORTAAddress:0x00C

# **PORTA Register**

**Note:** Writes to PORTA are actually written to the corresponding LATA register. Reads from PORTA register return actual I/O pin values.

| Bit    | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

|        | RA7 | RA6 | RA5 | RA4 | RA3 | RA2 | RA1 | RA0 |

| Access | R/W |

| Reset  | x   | x   | x   | x   | x   | х   | x   | x   |

Bits 0, 1, 2, 3, 4, 5, 6, 7 – RAn Port I/O Value bits Reset States: POR/BOR = xxxxxxx

All Other Resets = uuuuuuuu

| Value | Description                   |

|-------|-------------------------------|

| 1     | Port pin is ≥ V <sub>IH</sub> |

| 0     | Port pin is ≤ V <sub>IL</sub> |

# 16.4 Register Summary - PMD

| Address | Name | Bit Pos. |        |        |         |         |        |        |         |         |

|---------|------|----------|--------|--------|---------|---------|--------|--------|---------|---------|

| 0x0796  | PMD0 | 7:0      | SYSCMD | FVRMD  |         |         |        | NVMMD  | CLKRMD  | IOCMD   |

| 0x0797  | PMD1 | 7:0      |        | TMR6MD | TMR5MD  | TMR4MD  | TMR3MD | TMR2MD | TMR1MD  | TMR0MD  |

| 0x0798  | PMD2 | 7:0      | NCO1MD |        |         |         |        |        |         |         |

| 0x0799  | PMD3 | 7:0      |        | DAC1MD | ADCMD   |         |        | C2MD   | C1MD    | ZCDMD   |

| 0x079A  | PMD4 | 7:0      |        | PWM7MD | PWM6MD  | CCP5MD  | CCP4MD | CCP3MD | CCP2MD  | CCP1MD  |

| 0x079B  | PMD5 | 7:0      | CWG3MD | CWG2MD | CWG1MD  |         |        |        |         |         |

| 0x079C  | PMD6 | 7:0      |        |        | UART2MD | UART1MD |        |        | MSSP2MD | MSSP1MD |

| 0x079D  | PMD7 | 7:0      |        | SMT2MD | SMT1MD  | CLC4MD  | CLC3MD | CLC2MD | CLC1MD  | DSM1MD  |

# **16.5** Register Definitions: Peripheral Module Disable

# PIC16(L)F18455/56

(PMD) Peripheral Module Disable

| Value | Description          |

|-------|----------------------|

| 1     | CCP1 module disabled |

|       | CCP1 module enabled  |

#### 20.8.16 ADPREV

Name:ADPREVAddress:0x09B

#### ADC Previous Result Register

| Bit    | 15         | 14 | 13 | 12   | 11      | 10 | 9  | 8  |

|--------|------------|----|----|------|---------|----|----|----|

|        |            |    |    | PREV | 'H[7:0] |    |    |    |

| Access | RO         | RO | RO | RO   | RO      | RO | RO | RO |

| Reset  | х          | x  | x  | x    | х       | х  | х  | x  |

|        |            |    |    |      |         |    |    |    |

| Bit    | 7          | 6  | 5  | 4    | 3       | 2  | 1  | 0  |

|        | PREVL[7:0] |    |    |      |         |    |    |    |

| Access | RO         | RO | RO | RO   | RO      | RO | RO | RO |

| Reset  | х          | x  | х  | x    | х       | х  | х  | x  |

Bits 15:8 - PREVH[7:0] Previous ADC Result Most Significant bits

| Value  | Condition       | Description                                                               |

|--------|-----------------|---------------------------------------------------------------------------|

| 0 to   | <b>PSIS =</b> 1 | Upper byte of ADFLTR at the start of current ADC conversion               |

| OxFF   |                 |                                                                           |

| varies | <b>PSIS =</b> 0 | Upper bits of ADRES at the start of current ADC conversion <sup>(1)</sup> |

Bits 7:0 - PREVL[7:0] Previous ADC Result Least Significant bits

| Value  | Condition       | Description                                                               |

|--------|-----------------|---------------------------------------------------------------------------|

| 0 to   | <b>PSIS =</b> 1 | Lower byte of ADFLTR at the start of current ADC conversion               |

| OxFF   |                 |                                                                           |

| varies | <b>PSIS =</b> 0 | Lower bits of ADRES at the start of current ADC conversion <sup>(1)</sup> |

**Note:** If PSIS = 0, PREVH and PREVL are formatted the same way as ADRES is, depending on the FRM bit.

# 20.8.18 ADSTPT

Name:ADSTPTAddress:0x092

#### ADC Threshold Setpoint Register

Depending on the CALC bits, it may be used to determine ADERR. See ADC Error Calculation Mode for more details.

| Bit    | 15         | 14  | 13  | 12   | 11     | 10  | 9   | 8   |

|--------|------------|-----|-----|------|--------|-----|-----|-----|

|        |            |     |     | STPT | H[7:0] |     |     |     |

| Access | R/W        | R/W | R/W | R/W  | R/W    | R/W | R/W | R/W |

| Reset  | 0          | 0   | 0   | 0    | 0      | 0   | 0   | 0   |

|        |            |     |     |      |        |     |     |     |

| Bit    | 7          | 6   | 5   | 4    | 3      | 2   | 1   | 0   |

|        | STPTL[7:0] |     |     |      |        |     |     |     |

| Access | R/W        | R/W | R/W | R/W  | R/W    | R/W | R/W | R/W |

| Reset  | 0          | 0   | 0   | 0    | 0      | 0   | 0   | 0   |

# Bits 15:8 - STPTH[7:0]

ADC Threshold Setpoint Most Significant Byte.

# Bits 7:0 - STPTL[7:0]

ADC Threshold Setpoint Least Significant Byte.

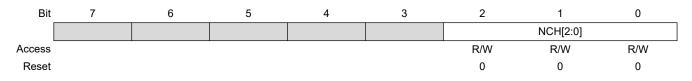

# 23.15.3 CMxNCH

Name:CMxNCHAddress:0x992,0x996

Comparator x Inverting Channel Select Register

# Bits 2:0 - NCH[2:0] Comparator Inverting Input Channel Select bits

| NCH | Negative Input Sources                    |

|-----|-------------------------------------------|

| 111 | $CxV_N$ connects to $AV_{SS}$             |

| 110 | CxV <sub>N</sub> connects to FVR Buffer 2 |

| 101 | CxV <sub>N</sub> not connected            |

| 100 | CxV <sub>N</sub> not connected            |

| 011 | CxV <sub>N</sub> connects to CxIN3- pin   |

| 010 | CxV <sub>N</sub> connects to CxIN2- pin   |

| 001 | CxV <sub>N</sub> connects to CxIN1- pin   |

| 000 | CxV <sub>N</sub> connects to CxIN0- pin   |

#### 25.2.2 Synchronous Mode

When the TOASYNC bit is clear, Timer0 clock is synchronized to the system clock ( $F_{OSC}/4$ ). When operating in Synchronous mode, Timer0 clock frequency cannot exceed  $F_{OSC}/4$ . During Sleep mode system clock is not available and Timer0 cannot operate.

#### 25.2.3 Asynchronous Mode

When the TOASYNC bit is set, Timer0 increments with each rising edge of the input source (or output of the prescaler, if used). Asynchronous mode allows Timer0 to continue operation during Sleep mode provided the selected clock source is available.

#### 25.2.4 Programmable Prescaler

Timer0 has 16 programmable input prescaler options ranging from 1:1 to 1:32768. The prescaler values are selected using the TOCKPS bits.

The prescaler counter is not directly readable or writable. The prescaler counter is cleared on the following events:

- A write to the TMR0L register

- A write to either the T0CON0 or T0CON1 registers

- Any device Reset

#### **Related Links**

8. Resets

# 25.3 Timer0 Output and Interrupt

#### 25.3.1 Programmable Postscaler

Timer0 has 16 programmable output postscaler options ranging from 1:1 to 1:16. The postscaler values are selected using the TOOUTPS bits. The postscaler divides the output of Timer0 by the selected ratio.

The postscaler counter is not directly readable or writable. The postscaler counter is cleared on the following events:

- A write to the TMR0L register

- A write to either the T0CON0 or T0CON1 registers

- Any device Reset

#### 25.3.2 Timer0 Output

TMR0\_out is the output of the postscaler. TMR0\_out toggles on every match between TMR0L and TMR0H in 8-bit mode, or when TMR0H:TMR0L rolls over in 16-bit mode. If the output postscaler is used, the output is scaled by the ratio selected.

The Timer0 output can be routed to an I/O pin via the RxyPPS output selection register. The Timer0 output can be monitored through software via the T0OUT output bit.

#### **Related Links**

15.2 PPS Outputs

#### 25.3.3 Timer0 Interrupt

The Timer0 Interrupt Flag bit (TMR0IF) is set when the TMR0\_out toggles. If the Timer0 interrupt is enabled (TMR0IE), the CPU will be interrupted when the TMR0IF bit is set.

When the postscaler bits (T0OUTPS) are set to 1:1 operation (no division), the T0IF flag bit will be set with every TMR0 match or rollover. In general, the TMR0IF flag bit will be set every T0OUTPS +1 matches or rollovers.

# 25.3.4 Timer0 Example

Timer0 Configuration:

- Timer0 mode = 16-bit

- Clock Source = F<sub>OSC</sub>/4 (250 kHz)

- Synchronous operation

- Prescaler = 1:1

- Postscaler = 1:2 (T0OUTPS = 1)

In this case the TMR0\_out toggles every two rollovers of TMR0H:TMR0L. i.e.,  $(0xFFFF)^{2*}(1/250kHz) = 524.28 \text{ ms}$

# 25.4 Operation During Sleep

When operating synchronously, Timer0 will halt when the device enters Sleep mode.

When operating asynchronously and selected clock source is active, Timer0 will continue to increment and wake the device from Sleep mode if Timer0 interrupt is enabled.

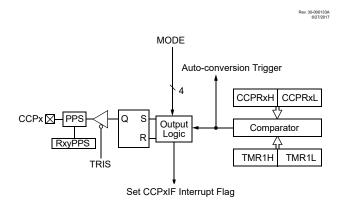

#### Figure 29-2. Compare Mode Operation Block Diagram

#### 29.3.1 CCPx Pin Configuration

The software must configure the CCPx pin as an output by clearing the associated TRIS bit and defining the appropriate output pin through the RxyPPS registers. See section *"Peripheral Pin Select (PPS) Module"* for more details.

The CCP output can also be used as an input for other peripherals.

**Important:** Clearing the CCPxCON register will force the CCPx compare output latch to the default low level. This is not the PORT I/O data latch.

#### **Related Links**

15. (PPS) Peripheral Pin Select Module

#### 29.3.2 Timer1 Mode Resource

In Compare mode, Timer1 must be running in either Timer mode or Synchronized Counter mode. The compare operation may not work in Asynchronous Counter mode.

See Section "Timer1 Module with Gate Control" for more information on configuring Timer1.

**Important:** Clocking Timer1 from the system clock ( $F_{OSC}$ ) should not be used in Compare mode. In order for Compare mode to recognize the trigger event on the CCPx pin, Timer1 must be clocked from the instruction clock ( $F_{OSC}$ /4) or from an external clock source.

#### 29.3.3 Auto-Conversion Trigger

All CCPx modes set the CCP Interrupt Flag (CCPxIF). When this flag is set and a match occurs, an autoconversion trigger can take place if the CCP module is selected as the conversion trigger source.

Refer to Section "Auto-Conversion Trigger" for more information.

**Important:** Removing the match condition by changing the contents of the CCPRxH and CCPRxL register pair, between the clock edge that generates the Auto-conversion Trigger and the clock edge that generates the Timer1 Reset, will preclude the Reset from occurring.

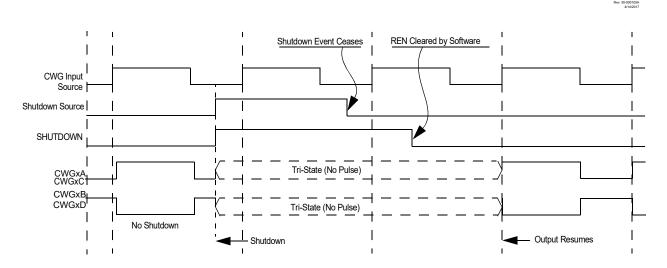

In either case, the shutdown source must be cleared before the restart can take place. That is, either the shutdown condition must be removed, or the corresponding ASyE bit must be cleared.

#### 31.11.2.1 Software-Controlled Restart

When the **REN** bit is clear (**REN** = 0), the CWG module must be restarted after an auto-shutdown event through software.

Once all auto-shutdown sources are removed, the software must clear SHUTDOWN. Once SHUTDOWN is cleared, the CWG module will resume operation upon the first rising edge of the CWG data input.

**Important:** The SHUTDOWN bit cannot be cleared in software if the auto-shutdown condition is still present.

# Figure 31-15. SHUTDOWN FUNCTIONALITY, AUTO-RESTART DISABLED (REN = 0, LSAC = 01, LSBD = 01)

#### 31.11.2.2 Auto-Restart

When the REN bit is set (REN = 1), the CWG module will restart from the shutdown state automatically.

Once all auto-shutdown conditions are removed, the hardware will automatically clear SHUTDOWN. Once SHUTDOWN is cleared, the CWG module will resume operation upon the first rising edge of the CWG data input.

**Important:** The SHUTDOWN bit cannot be cleared in software if the auto-shutdown condition is still present.

There are two signal lines in Synchronous mode: a bidirectional data line and a clock line. Slaves use the external clock supplied by the master to shift the serial data into and out of their respective receive and transmit shift registers. Since the data line is bidirectional, synchronous operation is half-duplex only. Half-duplex refers to the fact that master and slave devices can receive and transmit data but not both simultaneously. The EUSART can operate as either a master or slave device.

Start and Stop bits are not used in synchronous transmissions.

#### 36.3.1 Synchronous Master Mode

The following bits are used to configure the EUSART for synchronous master operation:

- SYNC = 1 (configures the EUSART for synchronous operation)

- CSRC = 1 (configures the EUSART as the master)

- SREN = 0 (for transmit); SREN = 1 (recommended setting to receive 1 byte)

- CREN = 0 (for transmit); CREN = 1 (to receive continuously)

- SPEN = 1 (enables the EUSART)

**Important:** Clearing the SREN and CREN bits of the RCxSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive.

#### 36.3.1.1 Master Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a master transmits the clock on the TX/CK line. The TXx/CKx pin output driver is automatically enabled when the EUSART is configured for synchronous transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One clock cycle is generated for each data bit. Only as many clock cycles are generated as there are data bits.

#### 36.3.1.2 Clock Polarity

A clock polarity option is provided for Microwire compatibility. Clock polarity is selected with the SCKP bit of the BAUDxCON register. Setting the SCKP bit sets the clock Idle state as high. When the SCKP bit is set, the data changes on the falling edge of each clock. Clearing the SCKP bit sets the Idle state as low. When the SCKP bit is cleared, the data changes on the rising edge of each clock.

#### 36.3.1.3 Synchronous Master Transmission

Data is transferred out of the device on the RXx/DTx pin. The RXx/DTx and TXx/CKx pin output drivers are automatically enabled when the EUSART is configured for synchronous master transmit operation.

A transmission is initiated by writing a character to the TXxREG register. If the TSR still contains all or part of a previous character the new character data is held in the TXxREG until the last bit of the previous character has been transmitted. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXxREG is immediately transferred to the TSR. The transmission of the character commences immediately following the transfer of the data to the TSR from the TXxREG.

Each data bit changes on the leading edge of the master clock and remains valid until the subsequent leading clock edge.

Note: The TSR register is not mapped in data memory, so it is not available to the user.

- 6. If 9-bit reception is desired, set the RX9 bit.

- 7. Set the CREN bit to enable reception.

- 8. The RCxIF bit will be set when reception is complete. An interrupt will be generated if the RCxIE bit was set.

- 9. If 9-bit mode is enabled, retrieve the Most Significant bit from the RX9D bit of the RCxSTA register.

- 10. Retrieve the eight Least Significant bits from the receive FIFO by reading the RCxREG register.

- 11. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCxSTA register or by clearing the SPEN bit which resets the EUSART.

# 36.4 EUSART Operation During Sleep

The EUSART will remain active during Sleep only in the Synchronous Slave mode. All other modes require the system clock and therefore cannot generate the necessary signals to run the Transmit or Receive Shift registers during Sleep.

Synchronous Slave mode uses an externally generated clock to run the Transmit and Receive Shift registers.

#### 36.4.1 Synchronous Receive During Sleep

To receive during Sleep, all the following conditions must be met before entering Sleep mode:

- RCxSTA and TXxSTA Control registers must be configured for Synchronous Slave Reception (see 36.3.2.5 Synchronous Slave Reception Setup:).

- If interrupts are desired, set the RCxIE bit of the PIEx register and the GIE and PEIE bits of the INTCON register.

- The RCxIF interrupt flag must be cleared by reading RCxREG to unload any pending characters in the receive buffer.

Upon entering Sleep mode, the device will be ready to accept data and clocks on the RXx/DTx and TXx/CKx pins, respectively. When the data word has been completely clocked in by the external device, the RCxIF interrupt flag bit of the PIRx register will be set. Thereby, waking the processor from Sleep.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the Global Interrupt Enable (GIE) bit of the INTCON register is also set, then the Interrupt Service Routine at address 004h will be called.

#### 36.4.2 Synchronous Transmit During Sleep

To transmit during Sleep, all the following conditions must be met before entering Sleep mode:

- The RCxSTA and TXxSTA Control registers must be configured for synchronous slave transmission (see 36.3.2.3 Synchronous Slave Transmission Setup).

- The TXxIF interrupt flag must be cleared by writing the output data to the TXxREG, thereby filling the TSR and transmit buffer.

- Interrupt enable bits TXxIE of the PIEx register and PEIE of the INTCON register must set.

- If interrupts are desired, set the GIEx bit of the INTCON register.

Upon entering Sleep mode, the device will be ready to accept clocks on the TXx/CKx pin and transmit data on the RXx/DTx pin. When the data word in the TSR has been completely clocked out by the external device, the pending byte in the TXxREG will transfer to the TSR and the TXxIF flag will be set. Thereby, waking the processor from Sleep. At this point, the TXxREG is available to accept another character for transmission. Writing TXxREG will clear the TXxIF flag.

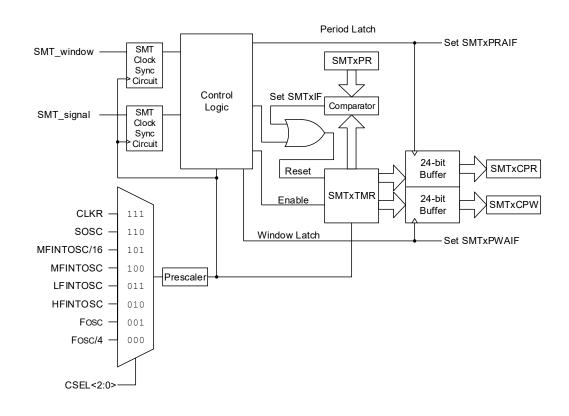

# 37. (SMT) Signal Measurement Timer

The SMT is a 24-bit counter with advanced clock and gating logic, which can be configured for measuring a variety of digital signal parameters such as pulse width, frequency and duty cycle, and the time difference between edges on two signals.

Features of the SMT include:

- 24-bit timer/counter

- Two 24-bit measurement capture registers

- One 24-bit period match register

- Multi-mode operation, including relative timing measurement

- Interrupt on period match and acquisition complete

- Multiple clock, signal and window sources

Below is the block diagram for the SMT module.

# Figure 37-1. Signal Measurement Timer Block Diagram

Rev. 10-000161E 10/12/2016

# 37.1 SMT Operation

#### 37.1.1 Clock Source Selection

The SMT clock source is selected by configuring the CSEL bits in the SMTxCLK register. The clock source can be prescaled using the PS bits of the SMTxCON0 register. The prescaled clock source is

# PIC16(L)F18455/56

# **Electrical Specifications**

| Standard Operating Conditions (unless otherwise stated) |                 |                                       |                      |                                                  |      |             |                                                                                                                                                                                                       |

|---------------------------------------------------------|-----------------|---------------------------------------|----------------------|--------------------------------------------------|------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param.<br>No.                                           | Sym.            | Device<br>Characteristics             | Min.                 | Тур.†                                            | Max. | Units       | Conditions                                                                                                                                                                                            |

| Output High Voltage                                     |                 |                                       |                      |                                                  |      |             |                                                                                                                                                                                                       |

| D370                                                    | V <sub>OH</sub> | Standard I/O PORTS                    | V <sub>DD</sub> -0.7 |                                                  |      | V           | $I_{OH} = 3.5 \text{ mA}, V_{DD} =$<br>5.0V<br>$I_{OH} = 3 \text{ mA}, V_{DD} = 3.3 \text{V}$<br>$I_{OH} = 1 \text{ mA}, V_{DD} = 1.8 \text{V}$                                                       |

| D370A                                                   |                 | High-Drive I/O<br>PORTS               | V <sub>DD</sub> -0.7 | <br>V <sub>DD</sub> -0.7<br>V <sub>DD</sub> -0.7 |      | V<br>V<br>V | $I_{OH} = 10 \text{ mA}, V_{DD} = 2.3 \text{V}, \text{HIDCx} = 1$ $I_{OH} = 37 \text{ mA}, V_{DD} = 3.0 \text{V}, \text{HIDCx} = 1$ $I_{OH} = 54 \text{ mA}, V_{DD} = 5.0 \text{V}, \text{HIDCx} = 1$ |

| All I/O Pii                                             | าร              | · · · · · · · · · · · · · · · · · · · |                      |                                                  |      |             |                                                                                                                                                                                                       |

| D380                                                    | C <sub>IO</sub> |                                       |                      | 5                                                | 50   | pF          |                                                                                                                                                                                                       |

† - Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# Note:

- 1. Negative current is defined as current sourced by the pin.