Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusActiveCore ProcessorARM® Cortex®-M0+Core Size32-Bit Single-CoreSpeed48MHz |                                         |

|-----------------------------------------------------------------------------------------|-----------------------------------------|

| Core Size 32-Bit Single-Core                                                            |                                         |

|                                                                                         |                                         |

| Speed 48MHz                                                                             |                                         |

|                                                                                         |                                         |

| Connectivity I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |                                         |

| Peripherals Brown-out Detect/Reset, DMA, I                                              | I <sup>2</sup> S, LVD, POR, PWM, WDT    |

| Number of I/O 54                                                                        |                                         |

| Program Memory Size 128KB (128K x 8)                                                    |                                         |

| Program Memory Type FLASH                                                               |                                         |

| EEPROM Size -                                                                           |                                         |

| RAM Size 32K x 8                                                                        |                                         |

| Voltage - Supply (Vcc/Vdd) 1.71V ~ 3.6V                                                 |                                         |

| Data ConvertersA/D 20x16b; D/A 1x12b                                                    |                                         |

| Oscillator Type Internal                                                                |                                         |

| Operating Temperature -40°C ~ 105°C (TA)                                                |                                         |

| Mounting Type Surface Mount                                                             |                                         |

| Package / Case 64-LFBGA                                                                 |                                         |

| Supplier Device Package 64-MAPBGA (5x5)                                                 |                                         |

| Purchase URL https://www.e-xfl.com/product-o                                            | detail/nxp-semiconductors/mkl17z128vmp4 |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Related Resources (continued)**

| Туре               | Description                                          | Resource                                                                                                                                                                                     |

|--------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Package<br>drawing | Package dimensions are provided in package drawings. | 64-LQFP: 98ASS23234W <sup>1</sup> 64-<br>MAPBGA: 98ASA00420D <sup>, 1</sup> 32-<br>QFN: 98ASA00615D <sup>1</sup> 48-QFN:<br>98ASA00616D <sup>, 1</sup> 36-WLCSP:<br>98ASA00949D <sup>1</sup> |

1. To find the associated resource, go to http://www.nxp.com and perform a search using this term.

| Symbol | Description                    | Min. | Тур. | Max. | Unit | Notes |

|--------|--------------------------------|------|------|------|------|-------|

|        | <ul> <li>VLPS → RUN</li> </ul> |      |      |      |      |       |

|        |                                | —    | 7.5  | 8    | μs   |       |

|        | • STOP → RUN                   |      |      |      |      |       |

|        |                                | _    | 7.5  | 8    | μs   |       |

Table 8. Power mode transition operating behaviors (continued)

1. Normal boot (FTFA\_FOPT[LPBOOT]=11)

### 2.2.5 Power consumption operating behaviors

The maximum values stated in the following table represent characterized results equivalent to the mean plus three times the standard deviation (mean + 3 sigma).

### NOTE

The while (1) test is executed with flash cache enabled.

### NOTE

The data at 105 °C are for QFN, LQFP and MAPBGA packages only.

Table 9. Power consumption operating behaviors

| Symbol                | Description                                                                                                                                     | Min. | Тур. | Max.     | Unit | Notes |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------|------|----------|------|-------|

| I <sub>DDA</sub>      | Analog supply current                                                                                                                           |      | _    | See note | mA   | 1     |

| I <sub>DD_RUNCO</sub> | Running CoreMark in flash in compute operation mode—48M HIRC mode, 48 MHz core / 24 MHz flash, $V_{DD}$ = 3.0 V                                 |      |      |          |      | 2     |

|                       | • at 25 °C                                                                                                                                      | —    | 5.76 | 6.40     | mA   |       |

|                       | • at 105 °C                                                                                                                                     | _    | 6.04 | 6.68     |      |       |

| I <sub>DD_RUNCO</sub> | Running While(1) loop in flash in compute<br>operation mode—48M HIRC mode, 48 MHz<br>core / 24 MHz flash, V <sub>DD</sub> = 3.0 V               |      |      |          |      |       |

|                       | • at 25 °C                                                                                                                                      | _    | 3.21 | 3.85     | mA   |       |

|                       | • at 105 °C                                                                                                                                     | —    | 3.49 | 4.13     |      |       |

| I <sub>DD_RUN</sub>   | Run mode current—48M HIRC mode, running<br>CoreMark in Flash all peripheral clock disable 48<br>MHz core/24 MHz flash, $V_{DD}$ = 3.0 V         |      |      |          |      | 2     |

|                       | • at 25 °C                                                                                                                                      | _    | 6.45 | 7.09     | mA   |       |

|                       | • at 105 °C                                                                                                                                     | —    | 6.75 | 7.39     |      |       |

| I <sub>DD_RUN</sub>   | Run mode current—48M HIRC mode, running<br>CoreMark in flash all peripheral clock disable, 24<br>MHz core/12 MHz flash, V <sub>DD</sub> = 3.0 V |      |      |          |      | 2     |

Table continues on the next page...

10

| Symbol              | Description                                                                                                                                                        | Min. | Тур. | Max. | Unit | Notes |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|-------|

|                     | • at 25 °C                                                                                                                                                         |      | 3.95 | 4.59 |      |       |

|                     | • at 105 °C                                                                                                                                                        | _    | 4.23 | 4.87 | mA   |       |

| I <sub>DD_RUN</sub> | Run mode current—48M HIRC mode, running<br>CoreMark in Flash all peripheral clock disable 12<br>MHz core/6 MHz flash, V <sub>DD</sub> = 3.0 V                      |      |      |      |      | 2     |

|                     | • at 25 °C                                                                                                                                                         | —    | 2.68 | 3.32 | mA   |       |

|                     | • at 105 °C                                                                                                                                                        | —    | 2.96 | 3.60 |      |       |

| I <sub>DD_RUN</sub> | Run mode current—48M HIRC mode, running<br>CoreMark in Flash all peripheral clock enable 48<br>MHz core/24 MHz flash, V <sub>DD</sub> = 3.0 V<br>• at 25 °C        |      | 8.08 | 8.72 | mA   | 2     |

|                     |                                                                                                                                                                    |      |      |      |      |       |

|                     | • at 105 °C                                                                                                                                                        | _    | 8.39 | 9.03 |      |       |

| I <sub>DD_RUN</sub> | Run mode current—48M HIRC mode, running<br>While(1) loop in flash all peripheral clock disable,<br>48 MHz core/24 MHz flash, V <sub>DD</sub> = 3.0 V<br>• at 25 °C | _    | 3.90 | 4.54 | mA   |       |

|                     | • at 105 °C                                                                                                                                                        | —    | 4.21 | 4.85 |      |       |

| I <sub>DD_RUN</sub> | Run mode current—48M HIRC mode, running<br>While(1) loop in Flash all peripheral clock disable,<br>24 MHz core/12 MHz flash, V <sub>DD</sub> = 3.0 V<br>• at 25 °C |      | 2.66 | 3.30 | mA   |       |

|                     |                                                                                                                                                                    |      |      |      |      |       |

|                     | • at 105 °C                                                                                                                                                        | —    | 2.94 | 3.58 |      |       |

| I <sub>DD_RUN</sub> | Run mode current—48M HIRC mode, Running<br>While(1) loop in Flash all peripheral clock disable,<br>12 MHz core/6 MHz flash, V <sub>DD</sub> = 3.0 V<br>• at 25 °C  | _    | 2.03 | 2.67 | mA   |       |

|                     |                                                                                                                                                                    | —    |      |      |      |       |

|                     | • at 105 °C                                                                                                                                                        |      | 2.31 | 2.95 |      |       |

| I <sub>DD_RUN</sub> | Run mode current—48M HIRC mode, Running<br>While(1) loop in Flash all peripheral clock enable,<br>48 MHz core/24 MHz flash, V <sub>DD</sub> = 3.0 V<br>• at 25 °C  | _    | 5.52 | 6.16 | mA   |       |

|                     | • at 105 °C                                                                                                                                                        |      | 5.83 | 6.47 |      |       |

|                     | • at 105 C                                                                                                                                                         |      | 5.65 | 0.47 |      |       |

| I <sub>DD_RUN</sub> | Run mode current—48M HIRC mode, running<br>While(1) loop in SRAM all peripheral clock<br>disable, 48 MHz core/24 MHz flash, V <sub>DD</sub> = 3.0 V                |      | 5.00 | 5.00 |      |       |

|                     | • at 25 °C                                                                                                                                                         | —    | 5.29 | 5.93 | mA   |       |

|                     | • at 105 °C                                                                                                                                                        | —    | 5.56 | 6.20 |      |       |

| I <sub>DD_RUN</sub> | Run mode current—48M HIRC mode, running<br>While(1) loop in SRAM all peripheral clock<br>enable, 48 MHz core/24 MHz flash, $V_{DD}$ = 3.0 V                        |      | 0.04 | 7 55 |      |       |

|                     |                                                                                                                                                                    | —    | 6.91 | 7.55 | mA   |       |

|                     |                                                                                                                                                                    | —    | 7.19 | 7.91 |      |       |

| Table 9. Power consumption operating behaviors (continued) |

|------------------------------------------------------------|

|------------------------------------------------------------|

Table continues on the next page...

| Table 9. | Power consumption operating behaviors (continued) |

|----------|---------------------------------------------------|

|----------|---------------------------------------------------|

| Symbol                 | Description                                                                                                                                                                                | Min. | Тур.   | Max.   | Unit | Notes |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|--------|------|-------|

|                        | disable, 125 kHz core / 31.25 kHz flash, V <sub>DD</sub> =<br>3.0 V<br>• at 25 °C                                                                                                          | _    | 50     | 131    | μA   |       |

| I <sub>DD_VLPR</sub>   | Very-low-power run mode current—2 MHz LIRC<br>mode, While(1) loop in SRAM all peripheral clock<br>enable, 2 MHz core / 0.5 MHz flash, V <sub>DD</sub> = 3.0 V<br>• at 25 °C                |      | 208    | 289    | μA   |       |

| I <sub>DD_WAIT</sub>   | Wait mode current—core disabled, 48 MHz<br>system/24 MHz bus, flash disabled (flash doze<br>enabled), all peripheral clocks disabled,<br>MCG_Lite under HIRC mode, V <sub>DD</sub> = 3.0 V | _    | 1.81   | 1.89   | mA   |       |

| I <sub>DD_WAIT</sub>   | Wait mode current—core disabled, 24 MHz<br>system/12 MHz bus, flash disabled (flash doze<br>enabled), all peripheral clocks disabled,<br>MCG_Lite under HIRC mode, V <sub>DD</sub> = 3.0 V |      | 1.22   | 1.39   | mA   |       |

| I <sub>DD_VLPW</sub>   | Very-low-power wait mode current, core disabled, 4 MHz system/ 1 MHz bus and flash, all peripheral clocks disabled, $V_{DD} = 3.0$ V                                                       | —    | 172    | 182    | μA   |       |

| I <sub>DD_VLPW</sub>   | Very-low-power wait mode current, core disabled, 2 MHz system/ 0.5 MHz bus and flash, all peripheral clocks disabled, $V_{DD} = 3.0$ V                                                     | _    | 69     | 76     | μA   |       |

| I <sub>DD_VLPW</sub>   | Very-low-power wait mode current, core disabled, 125 kHz system/ 31.25 kHz bus and flash, all peripheral clocks disabled, $V_{DD} = 3.0$ V                                                 | _    | 36     | 40     | μA   |       |

| DD_PSTOP2              | Partial Stop 2, core and system clock disabled, 12 MHz bus and flash, $V_{DD}$ = 3.0 V                                                                                                     |      |        |        |      |       |

|                        |                                                                                                                                                                                            |      | 1.81   | 2.06   | mA   |       |

| I <sub>DD_PSTOP2</sub> | Partial Stop 2, core and system clock disabled, flash doze enabled, 12 MHz bus, $V_{DD} = 3.0 V$                                                                                           |      |        |        |      |       |

|                        |                                                                                                                                                                                            | _    | 1.00   | 1.25   | mA   |       |

| I <sub>DD_STOP</sub>   | Stop mode current at 3.0 V<br>• at 25 °C and below                                                                                                                                         | _    | 161.93 | 171.82 |      |       |

|                        | • at 50 °C                                                                                                                                                                                 | _    | 181.45 | 191.96 |      |       |

|                        | • at 85 °C                                                                                                                                                                                 |      | 236.29 | 271.17 | μA   |       |

|                        | • at 105 °C                                                                                                                                                                                |      | 390.33 | 465.58 |      |       |

| I <sub>DD_VLPS</sub>   | Very-low-power stop mode current at 3.0 V<br>• at 25 °C and below                                                                                                                          | _    | 3.31   | 5.14   |      |       |

|                        | • at 50 °C                                                                                                                                                                                 | _    | 10.43  | 17.68  |      |       |

|                        | • at 85 °C                                                                                                                                                                                 | _    | 34.14  | 61.06  | μA   |       |

|                        | • at 105 °C                                                                                                                                                                                |      | 104.38 | 164.44 |      |       |

| I <sub>DD_VLPS</sub>   | Very-low-power stop mode current at 1.8 V<br>• at 25 °C and below                                                                                                                          | _    | 3.21   | 5.22   |      |       |

Table continues on the next page...

| Symbol                | Description                                                                                         | Min. | Тур.  | Max.  | Unit | Notes |

|-----------------------|-----------------------------------------------------------------------------------------------------|------|-------|-------|------|-------|

| I <sub>DD_VLLS3</sub> | Very-low-leakage stop mode 3 current with RTC                                                       |      |       |       |      | 3     |

|                       | current, at 1.8 V<br>• at 25 °C and below                                                           | —    | 1.96  | 2.36  | μA   |       |

|                       | • at 50 °C                                                                                          | —    | 3.86  | 5.67  |      |       |

|                       | • at 70 °C                                                                                          | —    | 6.23  | 8.53  |      |       |

|                       | • at 85 °C                                                                                          | —    | 10.21 | 13.37 |      |       |

|                       | • at 105 °C                                                                                         | —    | 30.25 | 37.02 |      |       |

|                       |                                                                                                     |      |       |       |      |       |

| I <sub>DD_VLLS1</sub> | Very-low-leakage stop mode 1 current all<br>peripheral disabled at 3.0 V                            |      |       |       |      |       |

|                       | • at 25 °C and below                                                                                | —    | 0.66  | 0.80  |      |       |

|                       | • at 50°C                                                                                           | —    | 1.78  | 3.87  |      |       |

|                       | • at 70°C                                                                                           | —    | 2.55  | 4.26  | μΑ   |       |

|                       | • at 85°C                                                                                           | —    | 4.83  | 6.64  |      |       |

|                       | ● at 105 °C                                                                                         | —    | 16.42 | 20.49 |      |       |

|                       | Very-low-leakage stop mode 1 current RTC                                                            |      |       |       |      | 3     |

| I <sub>DD_VLLS1</sub> | enabled at 3.0 V                                                                                    |      | 1.26  | 1.40  |      |       |

|                       | <ul> <li>at 25 °C and below</li> </ul>                                                              | _    |       |       |      |       |

|                       | • at 50°C                                                                                           |      | 2.38  | 4.47  |      |       |

|                       | • at 70°C                                                                                           | _    | 3.15  | 4.86  | μA   |       |

|                       | • at 85°C                                                                                           | _    | 5.43  | 7.24  |      |       |

|                       | • at 105 °C                                                                                         | _    | 17.02 | 21.09 |      |       |

| I <sub>DD_VLLS1</sub> | Very-low-leakage stop mode 1 current RTC                                                            |      |       |       |      | 3     |

|                       | enabled at 1.8 V                                                                                    | _    | 1.16  | 1.30  |      |       |

|                       | • at 25 °C and below                                                                                | _    | 1.96  | 2.28  |      |       |

|                       | • at 50°C                                                                                           | _    | 2.78  | 3.37  | μA   |       |

|                       | • at 70°C                                                                                           | _    | 4.85  | 6.88  |      |       |

|                       | • at 85°C                                                                                           | _    | 15.78 | 18.81 |      |       |

|                       | • at 105 °C                                                                                         |      |       |       |      |       |

| I <sub>DD_VLLS0</sub> | Very-low-leakage stop mode 0 current all                                                            |      |       |       |      |       |

|                       | peripheral disabled (SMC_STOPCTRL[PORPO]<br>= 0) at 3.0 V                                           |      |       |       |      |       |

|                       | <ul> <li>at 25 °C and below</li> </ul>                                                              | —    | 0.35  | 0.47  | μA   |       |

|                       | • at 50 °C                                                                                          | —    | 1.25  | 1.44  |      |       |

|                       | • at 70 °C                                                                                          | —    | 2.53  | 3.24  |      |       |

|                       | • at 85 °C                                                                                          | —    | 4.40  | 5.24  |      |       |

|                       | • at 105 °C                                                                                         | —    | 16.09 | 19.29 |      |       |

| I <sub>DD_VLLS0</sub> | Very-low-leakage stop mode 0 current all<br>peripheral disabled (SMC_STOPCTRL[PORPO]<br>= 1) at 3 V |      |       |       |      |       |

| Symbol           | Description                                                                                                                                                                                                                                                                                                                                                                                                |           | ٦         | Tempera   | ature (°0 | C)        |           | Unit |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|------|

|                  |                                                                                                                                                                                                                                                                                                                                                                                                            | -40       | 25        | 50        | 70        | 85        | 105       |      |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                            |           |           |           |           |           |           | nA   |

| I <sub>CMP</sub> | CMP peripheral adder measured by<br>placing the device in VLLS1 mode with<br>CMP enabled using the 6-bit DAC and a<br>single external input for compare. Includes<br>6-bit DAC power consumption.                                                                                                                                                                                                          | 22        | 22        | 22        | 22        | 22        | 22        | μΑ   |

| IUART            | <ul> <li>UART peripheral adder measured by placing the device in STOP or VLPS mode with selected clock source waiting for RX data at 115200 baud rate. Includes selected clock source power consumption.</li> <li>IRC8M (8 MHz internal reference clock)</li> <li>IRC2M (2 MHz internal reference clock)</li> </ul>                                                                                        | 114<br>34 | 114<br>34 | 114<br>34 | 114<br>34 | 114<br>34 | 114<br>34 | μA   |

| ITPM             | <ul> <li>TPM peripheral adder measured by placing the device in STOP or VLPS mode with selected clock source configured for output compare generating 100 Hz clock signal. No load is placed on the I/O generating the clock signal. Includes selected clock source and I/O switching currents.</li> <li>IRC8M (8 MHz internal reference clock)</li> <li>IRC2M (2 MHz internal reference clock)</li> </ul> | 147<br>42 | 147<br>42 | 147<br>42 | 147<br>42 | 147<br>42 | 147<br>42 | μΑ   |

| I <sub>BG</sub>  | Bandgap adder when BGEN bit is set and device is placed in VLPx or VLLSx mode.                                                                                                                                                                                                                                                                                                                             | 45        | 45        | 45        | 45        | 45        | 45        | μA   |

| IADC             | ADC peripheral adder combining the measured values at $V_{DD}$ and $V_{DDA}$ by placing the device in STOP or VLPS mode. ADC is configured for low power mode using the internal clock and continuous conversions.                                                                                                                                                                                         | 330       | 330       | 330       | 330       | 330       | 330       | μA   |

### Table 10. Low power mode peripheral adders — typical value (continued)

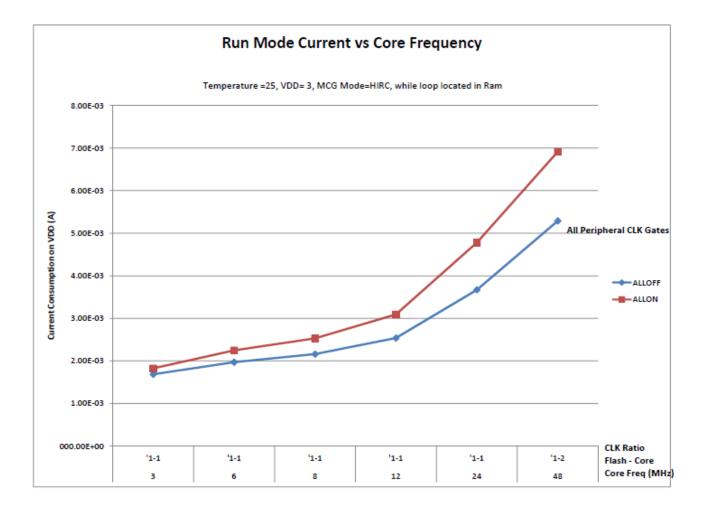

### 2.2.5.1 Diagram: Typical IDD\_RUN operating behavior

The following data was measured under these conditions:

- MCG-Lite in HIRC for run mode, and LIRC for VLPR mode

- No GPIOs toggled

- Code execution from flash

- For the ALLOFF curve, all peripheral clocks are disabled except FTFA

#### General

1. Maximum  $T_A$  can be exceeded only if the user ensures that  $T_J$  does not exceed the maximum. The simplest method to determine  $T_J$  is:  $T_J = T_A + R_{\theta JA} \times chip$  power dissipation.

Table 16. Thermal operating requirements for other packages

| Symbol         | Description              | Min. | Max. | Unit | Notes |

|----------------|--------------------------|------|------|------|-------|

| TJ             | Die junction temperature | -40  | 125  | °C   |       |

| T <sub>A</sub> | Ambient temperature      | -40  | 105  | °C   | 1     |

1. Maximum  $T_A$  can be exceeded only if the user ensures that  $T_J$  does not exceed the maximum. The simplest method to determine  $T_J$  is:  $T_J = T_A + R_{\theta JA} \times$  chip power dissipation.

### 2.4.2 Thermal attributes

Table 17. Thermal attributes

| Board type        | Symbo<br>I        | Description                                                                                              | 48<br>QFN | 32<br>QFN | 64<br>LQFP | 64<br>MAPB<br>GA | 36<br>WLCS<br>P | Unit | Notes |

|-------------------|-------------------|----------------------------------------------------------------------------------------------------------|-----------|-----------|------------|------------------|-----------------|------|-------|

| Single-layer (1S) | R <sub>θJA</sub>  | Thermal resistance,<br>junction to ambient<br>(natural convection)                                       | 86        | 101       | 70         | 50.3             | 77.6            | °C/W | 1     |

| Four-layer (2s2p) | R <sub>θJA</sub>  | Thermal resistance,<br>junction to ambient<br>(natural convection)                                       | 29        | 33        | 51         | 42.9             | 38.9            | °C/W |       |

| Single-layer (1S) | R <sub>θJMA</sub> | Thermal resistance,<br>junction to ambient (200<br>ft./min. air speed)                                   | 71        | 84        | 58         | 41.4             | 69.6            | °C/W |       |

| Four-layer (2s2p) | R <sub>θJMA</sub> | Thermal resistance,<br>junction to ambient (200<br>ft./min. air speed)                                   | 24        | 28        | 45         | 38.0             | 35.6            | °C/W |       |

|                   | R <sub>θJB</sub>  | Thermal resistance, junction to board                                                                    | 12        | 13        | 33         | 39.6             | 34.8            | °C/W | 2     |

|                   | R <sub>θJC</sub>  | Thermal resistance, junction to case                                                                     | 1.7       | 1.7       | 20         | 27.3             | 0.37            | °C/W | 3     |

|                   | $\Psi_{JT}$       | Thermal characterization<br>parameter, junction to<br>package top outside<br>center (natural convection) | 2         | 3         | 4          | 0.4              | 0.2             | °C/W | 4     |

| _                 | $\Psi_{JB}$       | Thermal characterization<br>parameter, junction to<br>package bottom (natural<br>convection)             | -         | -         | -          | 12.6             | -               | °C/W | 5     |

1. Determined according to JEDEC Standard JESD51-2, Integrated Circuits Thermal Test Method Environmental Conditions—Natural Convection (Still Air), or EIA/JEDEC Standard JESD51-6, Integrated Circuit Thermal Test Method Environmental Conditions—Forced Convection (Moving Air).

2. Determined according to JEDEC Standard JESD51-8, Integrated Circuit Thermal Test Method Environmental Conditions—Junction-to-Board.

| Symbol          | Description         | Min. | Тур. | Max. | Unit | Notes |

|-----------------|---------------------|------|------|------|------|-------|

| Tj              | Period jitter (RMS) | —    | 35   | 150  | ps   | _     |

| T <sub>su</sub> | Startup time        | —    | 2    | 3    | μs   |       |

Table 19. IRC48M specification (continued)

1. The maximum value represents characterized results equivalent to mean plus or minus three times the standard deviation (mean +/-3sigma).

| Symbol                | Description                      | Min. | Тур. | Max. | Unit              | Notes |

|-----------------------|----------------------------------|------|------|------|-------------------|-------|

| I <sub>DD_2M</sub>    | Supply current in 2 MHz mode     | _    | 14   | 17   | μA                | —     |

| I <sub>DD_8M</sub>    | Supply current in 8 MHz mode     | —    | 30   | 35   | μA                | —     |

| f <sub>IRC_2M</sub>   | Output frequency                 | —    | 2    | —    | MHz               | —     |

| f <sub>IRC_8M</sub>   | Output frequency                 | —    | 8    | —    | MHz               | —     |

| f <sub>IRC_T_2M</sub> | Output frequency range (trimmed) | —    | —    | ±3   | %f <sub>IRC</sub> | _     |

| f <sub>IRC_T_8M</sub> | Output frequency range (trimmed) | —    | —    | ±3   | %f <sub>IRC</sub> | —     |

| T <sub>su_2M</sub>    | Startup time                     | _    | —    | 12.5 | μs                | —     |

| T <sub>su_8M</sub>    | Startup time                     | _    | —    | 12.5 | μs                | —     |

#### Table 20. IRC8M/2M specification

#### Flash timing specifications — program and erase 3.4.1.1

The following specifications represent the amount of time the internal charge pumps are active and do not include command overhead.

| Symbol                | Description                        | Min. | Тур. | Max. | Unit | Notes |

|-----------------------|------------------------------------|------|------|------|------|-------|

| t <sub>hvpgm4</sub>   | Longword Program high-voltage time | —    | 7.5  | 18   | μs   | —     |

| t <sub>hversscr</sub> | Sector Erase high-voltage time     | —    | 13   | 113  | ms   | 1     |

52

452

ms

Table 23. NVM program/erase timing specifications

1. Maximum time based on expectations at cycling end-of-life.

t<sub>hversblk128k</sub>

Erase Block high-voltage time for 128 KB

#### Flash timing specifications — commands 3.4.1.2 Table 24. Flash command timing specifications

| Symbol                  | Description                                   | Min. | Тур. | Max. | Unit | Notes |

|-------------------------|-----------------------------------------------|------|------|------|------|-------|

|                         | Read 1s Block execution time                  |      |      |      |      | 1     |

| t <sub>rd1blk128k</sub> | 128 KB program flash                          | _    | _    | 1.7  | ms   |       |

| t <sub>rd1sec1k</sub>   | Read 1s Section execution time (flash sector) | _    | —    | 60   | μs   | 1     |

| t <sub>pgmchk</sub>     | Program Check execution time                  | _    | _    | 45   | μs   | 1     |

| t <sub>rdrsrc</sub>     | Read Resource execution time                  | _    | —    | 30   | μs   | 1     |

| t <sub>pgm4</sub>       | Program Longword execution time               | _    | 65   | 145  | μs   | _     |

|                         | Erase Flash Block execution time              |      |      |      |      | 2     |

| t <sub>ersblk128k</sub> | 128 KB program flash                          | -    | 88   | 600  | ms   |       |

| t <sub>ersscr</sub>     | Erase Flash Sector execution time             | _    | 14   | 114  | ms   | 2     |

| t <sub>rd1all</sub>     | Read 1s All Blocks execution time             | _    | _    | 1.8  | ms   | 1     |

| t <sub>rdonce</sub>     | Read Once execution time                      | _    | _    | 25   | μs   | 1     |

| t <sub>pgmonce</sub>    | Program Once execution time                   | _    | 65   | —    | μs   | _     |

| t <sub>ersall</sub>     | Erase All Blocks execution time               | _    | 175  | 1300 | ms   | 2     |

| t <sub>vfykey</sub>     | Verify Backdoor Access Key execution time     | -    | _    | 30   | μs   | 1     |

| t <sub>ersallu</sub>    | Erase All Blocks Unsecure execution time      | _    | 175  | 1300 | ms   | 2     |

1. Assumes 25 MHz flash clock frequency.

2. Maximum times for erase parameters based on expectations at cycling end-of-life.

1

### 3.4.1.3 Flash high voltage current behaviors Table 25. Flash high voltage current behaviors

| Symbol              | Description                                                           | Min. | Тур. | Max. | Unit |

|---------------------|-----------------------------------------------------------------------|------|------|------|------|

| I <sub>DD_PGM</sub> | Average current adder during high voltage flash programming operation |      | 2.5  | 6.0  | mA   |

| I <sub>DD_ERS</sub> | Average current adder during high voltage flash erase operation       |      | 1.5  | 4.0  | mA   |

## 3.4.1.4 Reliability specifications

### Table 26. NVM reliability specifications

| Symbol                  | Description                            | Min.    | Typ. <sup>1</sup> | Max. | Unit   | Notes |

|-------------------------|----------------------------------------|---------|-------------------|------|--------|-------|

|                         | Program                                | n Flash | -                 | -    |        |       |

| t <sub>nvmretp10k</sub> | Data retention after up to 10 K cycles | 5       | 50                | _    | years  | _     |

| t <sub>nvmretp1k</sub>  | Data retention after up to 1 K cycles  | 20      | 100               | _    | years  | _     |

| n <sub>nvmcycp</sub>    | Cycling endurance                      | 10 K    | 50 K              |      | cycles | 2     |

1. Typical data retention values are based on measured response accelerated at high temperature and derated to a constant 25 °C use profile. Engineering Bulletin EB618 does not apply to this technology. Typical endurance defined in Engineering Bulletin EB619.

2. Cycling endurance represents number of program/erase cycles at -40 °C  $\leq$  T<sub>j</sub>  $\leq$  125 °C.

# 3.5 Security and integrity modules

There are no specifications necessary for the device's security and integrity modules.

# 3.6 Analog

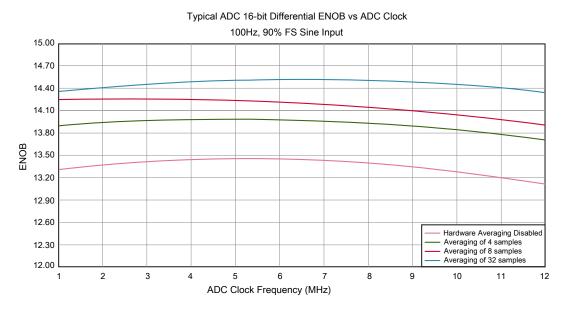

### 3.6.1 ADC electrical specifications

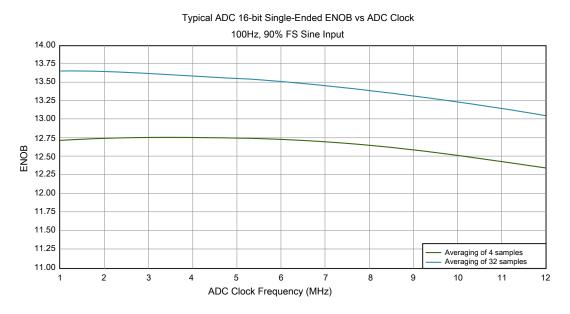

Using differential inputs can achieve better system accuracy than using single-end inputs.

- The ADC supply current depends on the ADC conversion clock speed, conversion rate and ADC\_CFG1[ADLPC] (low power). For lowest power operation, ADC\_CFG1[ADLPC] must be set, the ADC\_CFG2[ADHSC] bit must be clear with 1 MHz ADC conversion clock speed.

- 4. 1 LSB =  $(V_{REFH} V_{REFL})/2^N$

- 5. ADC conversion clock < 16 MHz, Max hardware averaging (AVGE = %1, AVGS = %11)

- 6. Input data is 100 Hz sine wave. ADC conversion clock < 12 MHz.

- 7. Input data is 1 kHz sine wave. ADC conversion clock < 12 MHz.

- 8. ADC conversion clock < 3 MHz

Figure 9. Typical ENOB vs. ADC\_CLK for 16-bit single-ended mode

## 3.6.2 Voltage reference electrical specifications

| Table 29. | <b>VREF full-range</b> | operating | requirements |

|-----------|------------------------|-----------|--------------|

|-----------|------------------------|-----------|--------------|

| Symbol           | Description             | Min.                      | Max. | Unit | Notes |

|------------------|-------------------------|---------------------------|------|------|-------|

| V <sub>DDA</sub> | Supply voltage          |                           | 3.6  | V    |       |

| T <sub>A</sub>   | Temperature             | Operating t<br>range of t |      | °C   |       |

| CL               | Output load capacitance | 1(                        | 00   | nF   | 1, 2  |

- 1. C<sub>L</sub> must be connected to VREF\_OUT if the VREF\_OUT functionality is being used for either an internal or external reference.

- The load capacitance should not exceed +/-25% of the nominal specified C<sub>L</sub> value over the operating temperature range of the device.

# Table 30 is tested under the condition of setting VREF\_TRM[CHOPEN], VREF\_SC[REGEN] and VREF\_SC[ICOMPEN] bits to 1.

| Symbol                   | Description                                                                                | Min.   | Тур.  | Max.   | Unit | Notes |

|--------------------------|--------------------------------------------------------------------------------------------|--------|-------|--------|------|-------|

| V <sub>out</sub>         | Voltage reference output with factory trim at nominal $V_{\text{DDA}}$ and temperature=25C | 1.1915 | 1.195 | 1.1977 | V    | 1     |

| V <sub>out</sub>         | Voltage reference output — factory trim                                                    | 1.1584 | —     | 1.2376 | V    | 1     |

| V <sub>out</sub>         | Voltage reference output — user trim                                                       | 1.193  | —     | 1.197  | V    | 1     |

| V <sub>step</sub>        | Voltage reference trim step                                                                | _      | 0.5   | —      | mV   | 1     |

| V <sub>tdrift</sub>      | Temperature drift (Vmax -Vmin across the full temperature range: 0 to 70°C)                | _      |       | 50     | mV   | 1     |

| I <sub>bg</sub>          | Bandgap only current                                                                       | _      | —     | 80     | μA   | 1     |

| I <sub>lp</sub>          | Low-power buffer current                                                                   |        | _     | 360    | uA   | 1     |

| I <sub>hp</sub>          | High-power buffer current                                                                  | _      | —     | 1      | mA   | 1     |

| $\Delta V_{LOAD}$        | Load regulation                                                                            |        |       |        | μV   | 1, 2  |

|                          | • current = ± 1.0 mA                                                                       | —      | 200   | _      |      |       |

| T <sub>stup</sub>        | Buffer startup time                                                                        | _      | _     | 100    | μs   |       |

| T <sub>chop_osc_st</sub> | Internal bandgap start-up delay with chop oscillator enabled                               | —      | —     | 35     | ms   | -     |

| V <sub>vdrift</sub>      | Voltage drift (Vmax -Vmin across the full voltage range)                                   | _      | 2     | —      | mV   | 1     |

Table 30. VREF full-range operating behaviors

1. See the chip's Reference Manual for the appropriate settings of the VREF Status and Control register.

2. Load regulation voltage is the difference between the VREF\_OUT voltage with no load vs. voltage with defined load

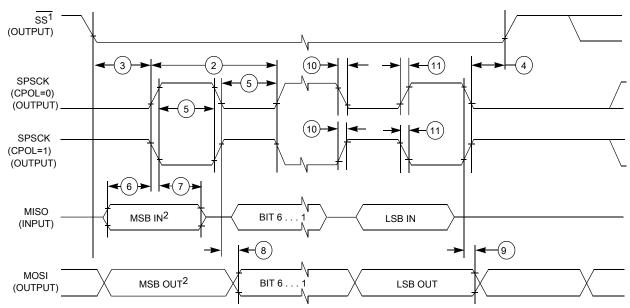

| Num. | Symbol          | Description                   | Min. | Max.                     | Unit | Note |

|------|-----------------|-------------------------------|------|--------------------------|------|------|

| 8    | t <sub>v</sub>  | Data valid (after SPSCK edge) | —    | 52                       | ns   | —    |

| 9    | t <sub>HO</sub> | Data hold time (outputs)      | 0    | —                        | ns   | —    |

| 10   | t <sub>RI</sub> | Rise time input               | —    | t <sub>periph</sub> - 25 | ns   | —    |

|      | t <sub>FI</sub> | Fall time input               |      |                          |      |      |

| 11   | t <sub>RO</sub> | Rise time output              | _    | 36                       | ns   | —    |

|      | t <sub>FO</sub> | Fall time output              |      |                          |      |      |

Table 37. SPI master mode timing on slew rate enabled pads (continued)

1. For SPI0  $f_{periph}$  is the bus clock ( $f_{BUS}$ ). For SPI1  $f_{periph}$  is the system clock ( $f_{SYS}$ ).

2.  $t_{periph} = 1/f_{periph}$

1. If configured as an output.

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

#### Figure 14. SPI master mode timing (CPHA = 0)

#### Peripheral operating requirements and behaviors

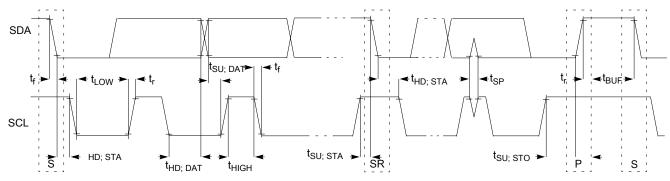

- 1. The maximum SCL Clock Frequency in Fast mode with maximum bus loading can be achieved only when using the high drive pins across the full voltage range and when using the normal drive pins and VDD ≥ 2.7 V.

- The master mode I<sup>2</sup>C deasserts ACK of an address byte simultaneously with the falling edge of SCL. If no slaves

acknowledge this address byte, then a negative hold time can result, depending on the edge rates of the SDA and SCL

lines.

- 3. The maximum tHD; DAT must be met only if the device does not stretch the LOW period (tLOW) of the SCL signal.

- 4. Input signal Slew = 10 ns and Output Load = 50 pF

- 5. Set-up time in slave-transmitter mode is 1 IPBus clock period, if the TX FIFO is empty.

- 6. A Fast mode I<sup>2</sup>C bus device can be used in a Standard mode I2C bus system, but the requirement t<sub>SU; DAT</sub> ≥ 250 ns must then be met. This is automatically the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, then it must output the next data bit to the SDA line t<sub>rmax</sub> + t<sub>SU; DAT</sub> = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification) before the SCL line is released.

- 7.  $C_b$  = total capacitance of the one bus line in pF.

| Characteristic                                                                               | Symbol                | Minimum                            | Maximum        | Unit |

|----------------------------------------------------------------------------------------------|-----------------------|------------------------------------|----------------|------|

| SCL Clock Frequency                                                                          | f <sub>SCL</sub>      | 0                                  | 1 <sup>1</sup> | MHz  |

| Hold time (repeated) START condition. After this period, the first clock pulse is generated. | t <sub>HD</sub> ; STA | 0.26                               | _              | μs   |

| LOW period of the SCL clock                                                                  | t <sub>LOW</sub>      | 0.5                                | —              | μs   |

| HIGH period of the SCL clock                                                                 | t <sub>HIGH</sub>     | 0.26                               | —              | μs   |

| Set-up time for a repeated START condition                                                   | t <sub>SU</sub> ; STA | 0.26                               | —              | μs   |

| Data hold time for $I_2C$ bus devices                                                        | t <sub>HD</sub> ; DAT | 0                                  | —              | μs   |

| Data set-up time                                                                             | t <sub>SU</sub> ; DAT | 50                                 | _              | ns   |

| Rise time of SDA and SCL signals                                                             | tr                    | 20 +0.1C <sub>b</sub>              | 120            | ns   |

| Fall time of SDA and SCL signals                                                             | t <sub>f</sub>        | 20 +0.1C <sub>b</sub> <sup>2</sup> | 120            | ns   |

| Set-up time for STOP condition                                                               | t <sub>SU</sub> ; STO | 0.26                               | —              | μs   |

| Bus free time between STOP and START condition                                               | t <sub>BUF</sub>      | 0.5                                | —              | μs   |

| Pulse width of spikes that must be suppressed by the input filter                            | t <sub>SP</sub>       | 0                                  | 50             | ns   |

Table 41. I<sup>2</sup>C 1Mbit/s timing

- 1. The maximum SCL clock frequency of 1 Mbit/s can support maximum bus loading when using the high drive pins across the full voltage range.

- 2. C<sub>b</sub> = total capacitance of the one bus line in pF.

Figure 18. Timing definition for devices on the I<sup>2</sup>C bus

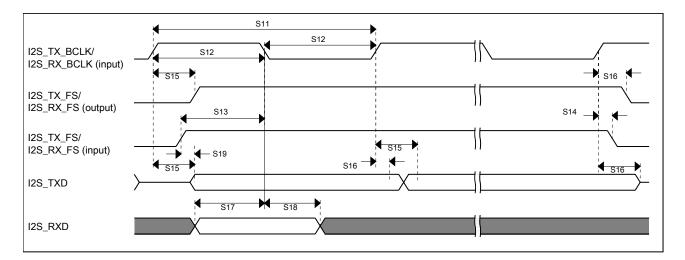

Figure 22. I2S/SAI timing — slave modes

# 4 Dimensions

### 4.1 Obtaining package dimensions

Package dimensions are provided in package drawings.

To find a package drawing, go to freescale.com and perform a keyword search for the drawing's document number:

| If you want the drawing for this package | Then use this document number |

|------------------------------------------|-------------------------------|

| 32-pin QFN                               | 98ASA00615D                   |

| 36-pin WLCSP                             | 98ASA00949D                   |

| 48-pin QFN                               | 98ASA00616D                   |

| 64-pin LQFP                              | 98ASS23234W                   |

| 64-pin MAPBGA                            | 98ASA00420D                   |

#### **Pinouts and Packaging**

| 64<br>MAP<br>BGA | 64<br>LQFP | 48<br>QFN | 36<br>WLC<br>SP | 32<br>QFN | Pin Name                       | Default   | ALT0      | ALT1                           | ALT2      | ALT3                 | ALT4                 | ALT5      | ALT6             | ALT7 |

|------------------|------------|-----------|-----------------|-----------|--------------------------------|-----------|-----------|--------------------------------|-----------|----------------------|----------------------|-----------|------------------|------|

| E8               | 38         | 30        | - 3P            | _         | PTB3                           | ADC0_SE13 | ADC0_SE13 | PTB3                           | I2C0_SDA  | TPM2_CH1             |                      |           |                  |      |

| E6               | 39         | 31        | -               | _         | PTB16                          | DISABLED  | _         | PTB16                          | SPI1_MOSI | LPUARTO_<br>RX       | TPM_<br>CLKIN0       | SPI1_MISO |                  |      |

| D7               | 40         | 32        | -               | _         | PTB17                          | DISABLED  |           | PTB17                          | SPI1_MISO | LPUART0_<br>TX       | TPM_<br>CLKIN1       | SPI1_MOSI |                  |      |

| D6               | 41         | -         | -               | -         | PTB18                          | DISABLED  |           | PTB18                          |           | TPM2_CH0             | I2S0_TX_<br>BCLK     |           |                  |      |

| C7               | 42         | -         | -               | _         | PTB19                          | DISABLED  |           | PTB19                          |           | TPM2_CH1             | I2S0_TX_<br>FS       |           |                  |      |

| D8               | 43         | 33        | -               | -         | PTC0                           | ADC0_SE14 | ADC0_SE14 | PTC0                           |           | EXTRG_IN             | audioUSB_<br>SOF_OUT | CMP0_OUT  | I2S0_TXD0        |      |

| C6               | 44         | 34        | B1              | 22        | PTC1/<br>LLWU_P6/<br>RTC_CLKIN | ADC0_SE15 | ADC0_SE15 | PTC1/<br>LLWU_P6/<br>RTC_CLKIN | I2C1_SCL  |                      | TPM0_CH0             |           | I2S0_TXD0        |      |

| B7               | 45         | 35        | B2              | 23        | PTC2                           | ADC0_SE11 | ADC0_SE11 | PTC2                           | I2C1_SDA  |                      | TPM0_CH1             |           | I2S0_TX_<br>FS   |      |

| C8               | 46         | 36        | A1              | 24        | PTC3/<br>LLWU_P7               | DISABLED  |           | PTC3/<br>LLWU_P7               | SPI1_SCK  | LPUART1_<br>RX       | TPM0_CH2             | CLKOUT    | I2S0_TX_<br>BCLK |      |

| E3               | 47         | _         | C4              | -         | VSS                            | VSS       | VSS       |                                |           |                      |                      |           |                  |      |

| E4               | 48         | _         | B3              | _         | VDD                            | VDD       | VDD       |                                |           |                      |                      |           |                  |      |

| B8               | 49         | 37        | A2              | 25        | PTC4/<br>LLWU_P8               | DISABLED  |           | PTC4/<br>LLWU_P8               | SPI0_PCS0 | LPUART1_<br>TX       | TPM0_CH3             | I2S0_MCLK |                  |      |

| A8               | 50         | 38        | A3              | 26        | PTC5/<br>LLWU_P9               | DISABLED  |           | PTC5/<br>LLWU_P9               | SPI0_SCK  | LPTMR0_<br>ALT2      | I2S0_RXD0            |           | CMP0_OUT         |      |

| A7               | 51         | 39        | B4              | 27        | PTC6/<br>LLWU_P10              | CMP0_IN0  | CMP0_IN0  | PTC6/<br>LLWU_P10              | SPI0_MOSI | EXTRG_IN             | I2S0_RX_<br>BCLK     | SPI0_MISO | I2S0_MCLK        |      |

| B6               | 52         | 40        | A4              | 28        | PTC7                           | CMP0_IN1  | CMP0_IN1  | PTC7                           | SPI0_MISO | audioUSB_<br>SOF_OUT | I2S0_RX_<br>FS       | SPI0_MOSI |                  |      |

| A6               | 53         | -         | _               | _         | PTC8                           | CMP0_IN2  | CMP0_IN2  | PTC8                           | I2C0_SCL  | TPM0_CH4             | I2S0_MCLK            |           |                  |      |

| B5               | 54         | _         | _               | _         | PTC9                           | CMP0_IN3  | CMP0_IN3  | PTC9                           | I2C0_SDA  | TPM0_CH5             | I2S0_RX_<br>BCLK     |           |                  |      |

| B4               | 55         | -         | -               | _         | PTC10                          | DISABLED  |           | PTC10                          | I2C1_SCL  |                      | I2S0_RX_<br>FS       |           |                  |      |

| A5               | 56         | -         | -               | _         | PTC11                          | DISABLED  |           | PTC11                          | I2C1_SDA  |                      | I2S0_RXD0            |           |                  |      |

| C3               | 57         | 41        | -               | -         | PTD0                           | DISABLED  |           | PTD0                           | SPI0_PCS0 |                      | TPM0_CH0             |           | FXI00_D0         |      |

| A4               | 58         | 42        | -               | _         | PTD1                           | ADC0_SE5b | ADC0_SE5b | PTD1                           | SPI0_SCK  |                      | TPM0_CH1             |           | FXIO0_D1         |      |

| C2               | 59         | 43        | -               | _         | PTD2                           | DISABLED  |           | PTD2                           | SPI0_MOSI | UART2_RX             | TPM0_CH2             | SPI0_MISO | FXIO0_D2         |      |

| B3               | 60         | 44        | -               | _         | PTD3                           | DISABLED  |           | PTD3                           | SPI0_MISO | UART2_TX             | TPM0_CH3             | SPI0_MOSI | FXIO0_D3         |      |

| A3               | 61         | 45        | A5              | 29        | PTD4/<br>LLWU_P14              | DISABLED  |           | PTD4/<br>LLWU_P14              | SPI1_PCS0 | UART2_RX             | TPM0_CH4             |           | FXI00_D4         |      |

| C1               | 62         | 46        | B5              | 30        | PTD5                           | ADC0_SE6b | ADC0_SE6b | PTD5                           | SPI1_SCK  | UART2_TX             | TPM0_CH5             |           | FXIO0_D5         |      |

| B2               | 63         | 47        | A6              | 31        | PTD6/<br>LLWU_P15              | ADC0_SE7b | ADC0_SE7b | PTD6/<br>LLWU_P15              | SPI1_MOSI | LPUART0_<br>RX       |                      | SPI1_MISO | FXIO0_D6         |      |

# 7.1 Description

Part numbers for the chip have fields that identify the specific part. You can use the values of these fields to determine the specific part you have received.

# 7.2 Format

Part numbers for this device have the following format:

Q KL## A FFF R T PP CC N

# 7.3 Fields

This table lists the possible values for each field in the part number (not all combinations are valid):

| Field | Description                 | Values                                                                                                                                                                                                |

|-------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Q     | Qualification status        | <ul> <li>M = Fully qualified, general market flow</li> <li>P = Prequalification</li> </ul>                                                                                                            |

| KL##  | Kinetis family              | • KL17                                                                                                                                                                                                |

| A     | Key attribute               | • Z = Cortex-M0+                                                                                                                                                                                      |

| FFF   | Program flash memory size   | <ul> <li>128 = 128 KB</li> <li>256 = 256 KB</li> </ul>                                                                                                                                                |

| R     | Silicon revision            | <ul> <li>(Blank) = Main</li> <li>A = Revision after main</li> </ul>                                                                                                                                   |

| Т     | Temperature range (°C)      | <ul> <li>V = -40 to 105</li> <li>C = -40 to 85</li> </ul>                                                                                                                                             |

| PP    | Package identifier          | <ul> <li>FM = 32 QFN (5 mm x 5 mm)</li> <li>AL = 36 WLCSP (2.8 mm x 2.7 mm)</li> <li>FT = 48 QFN (7 mm x 7 mm)</li> <li>LH = 64 LQFP (10 mm x 10 mm)</li> <li>MP = 64 MAPBGA (5 mm x 5 mm)</li> </ul> |

| CC    | Maximum CPU frequency (MHz) | • 4 = 48 MHz                                                                                                                                                                                          |

| N     | Packaging type              | R = Tape and reel                                                                                                                                                                                     |

Table 47. Part number fields descriptions

# 7.4 Example

This is an example part number:

# 8.2 Examples

#### Operating rating:

| Symbol          | Description                  | Min. | Max. | Unit |  |  |

|-----------------|------------------------------|------|------|------|--|--|

| V <sub>DD</sub> | 1.0 V core supply<br>voltage | -0.3 | 1.2  | V    |  |  |

|                 |                              |      |      |      |  |  |

#### Operating requirement:

| Symbol          | Description                  | Min. | Max. | Unit |

|-----------------|------------------------------|------|------|------|

| V <sub>DD</sub> | 1.0 V core supply<br>voltage | 0.9  | 1.1  | V    |

4.

### Operating behavior that includes a typical value:

| Symbol | Description                                    | Min.  | Тур. | Max. | Unit |

|--------|------------------------------------------------|-------|------|------|------|

|        | Digital I/O weak<br>pullup/pulldown<br>current | 10 AM | 70   | 130  | μA   |

## 8.3 Typical-value conditions

Typical values assume you meet the following conditions (or other conditions as specified):

| Symbol          | Description         | Value | Unit |

|-----------------|---------------------|-------|------|

| T <sub>A</sub>  | Ambient temperature | 25    | ٥C   |

| V <sub>DD</sub> | Supply voltage      | 3.3   | V    |

#### How to Reach Us:

Home Page: freescale.com

Web Support: freescale.com/support Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. Freescale reserves the right to make changes without further notice to any products herein.

Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: freescale.com/SalesTermsandConditions.

Freescale, the Freescale logo, the Energy Efficient Solutions logo, and Kinetis are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. All other product or service names are the property of their respective owners. ARM, the ARM powered logo, and Cortex are registered trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved.

©2014-2016 Freescale Semiconductor, Inc.

Document Number KL17P64M48SF6 Revision 6, 02/2016