# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | AVR                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                        |

| Number of I/O              | 22                                                                      |

| Program Memory Size        | 8KB (8K x 8)                                                            |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 128 x 8                                                                 |

| RAM Size                   | 512 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                             |

| Data Converters            | A/D 12x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 24-VFQFN Exposed Pad                                                    |

| Supplier Device Package    | 24-VQFN (4x4)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/attiny807-mnr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 28.3. Functional Description                                                                                                                    |                                                                                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28.4. Register Summary - AC                                                                                                                     | 411                                                                                                                                                                                                            |

| 28.5. Register Description                                                                                                                      |                                                                                                                                                                                                                |

|                                                                                                                                                 | 110                                                                                                                                                                                                            |

| 29. ADC - Analog-to-Digital Converter                                                                                                           |                                                                                                                                                                                                                |

| 29.1. Features                                                                                                                                  |                                                                                                                                                                                                                |

| 29.2. Overview                                                                                                                                  |                                                                                                                                                                                                                |

| 29.3. Functional Description                                                                                                                    |                                                                                                                                                                                                                |

| 29.4. Register Summary - ADCn                                                                                                                   |                                                                                                                                                                                                                |

| 29.5. Register Description                                                                                                                      |                                                                                                                                                                                                                |

| 30. UPDI - Unified Program and Debug Interface                                                                                                  |                                                                                                                                                                                                                |

| 30.1. Features                                                                                                                                  |                                                                                                                                                                                                                |

| 30.2. Overview                                                                                                                                  |                                                                                                                                                                                                                |

| 30.3. Functional Description                                                                                                                    |                                                                                                                                                                                                                |

| 30.4. Register Summary - UPDI                                                                                                                   |                                                                                                                                                                                                                |

| 30.5. Register Description                                                                                                                      |                                                                                                                                                                                                                |

| 31. Electrical Characteristics                                                                                                                  |                                                                                                                                                                                                                |

| 31.1. Disclaimer                                                                                                                                | 480                                                                                                                                                                                                            |

| 31.2. Absolute Maximum Ratings                                                                                                                  |                                                                                                                                                                                                                |

| 31.3. General Operating Ratings                                                                                                                 |                                                                                                                                                                                                                |

| 31.4. Power Consumption                                                                                                                         |                                                                                                                                                                                                                |

| 31.5. Wake-Up Time                                                                                                                              |                                                                                                                                                                                                                |

|                                                                                                                                                 |                                                                                                                                                                                                                |

| -                                                                                                                                               |                                                                                                                                                                                                                |

| 31.6. Power Consumption of Peripherals                                                                                                          |                                                                                                                                                                                                                |

| 31.6.Power Consumption of Peripherals31.7.BOD and POR Characteristics                                                                           |                                                                                                                                                                                                                |

| <ul><li>31.6. Power Consumption of Peripherals</li><li>31.7. BOD and POR Characteristics</li><li>31.8. External Reset Characteristics</li></ul> |                                                                                                                                                                                                                |

| <ul> <li>31.6. Power Consumption of Peripherals</li> <li>31.7. BOD and POR Characteristics</li></ul>                                            |                                                                                                                                                                                                                |

| <ul> <li>31.6. Power Consumption of Peripherals</li> <li>31.7. BOD and POR Characteristics</li></ul>                                            |                                                                                                                                                                                                                |

| <ul> <li>31.6. Power Consumption of Peripherals</li></ul>                                                                                       | 484<br>485<br>486<br>486<br>487<br>489                                                                                                                                                                         |

| <ul> <li>31.6. Power Consumption of Peripherals</li></ul>                                                                                       |                                                                                                                                                                                                                |

| <ul> <li>31.6. Power Consumption of Peripherals</li></ul>                                                                                       |                                                                                                                                                                                                                |

| <ul> <li>31.6. Power Consumption of Peripherals</li></ul>                                                                                       |                                                                                                                                                                                                                |

| <ul> <li>31.6. Power Consumption of Peripherals</li></ul>                                                                                       | 484<br>485<br>486<br>486<br>487<br>487<br>489<br>490<br>490<br>491<br>493<br>494                                                                                                                               |

| <ul> <li>31.6. Power Consumption of Peripherals</li></ul>                                                                                       | 484<br>485<br>486<br>486<br>487<br>487<br>489<br>490<br>490<br>491<br>493<br>493<br>494                                                                                                                        |

| <ul> <li>31.6. Power Consumption of Peripherals</li></ul>                                                                                       | 484<br>485<br>486<br>486<br>487<br>487<br>489<br>490<br>490<br>491<br>493<br>493<br>494<br>497                                                                                                                 |

| <ul> <li>31.6. Power Consumption of Peripherals</li></ul>                                                                                       | 484<br>485<br>486<br>486<br>487<br>487<br>489<br>490<br>490<br>491<br>493<br>493<br>494<br>497                                                                                                                 |

| <ul> <li>31.6. Power Consumption of Peripherals</li></ul>                                                                                       | 484<br>485<br>486<br>486<br>487<br>487<br>489<br>490<br>490<br>491<br>491<br>493<br>493<br>494<br>497<br>497                                                                                                   |

| <ul> <li>31.6. Power Consumption of Peripherals</li></ul>                                                                                       | 484<br>485<br>486<br>486<br>487<br>487<br>489<br>490<br>490<br>491<br>493<br>493<br>494<br>493<br>494<br>497<br>497<br>497<br>498                                                                              |

| <ul> <li>31.6. Power Consumption of Peripherals</li></ul>                                                                                       | 484<br>485<br>486<br>486<br>487<br>489<br>490<br>491<br>491<br>493<br>493<br>493<br>494<br>497<br>497<br>497<br>497<br>499<br>506                                                                              |

| <ul> <li>31.6. Power Consumption of Peripherals</li></ul>                                                                                       | 484<br>485<br>486<br>486<br>487<br>489<br>490<br>491<br>491<br>493<br>493<br>493<br>494<br>497<br>497<br>497<br>497<br>499<br>506                                                                              |

| <ul> <li>31.6. Power Consumption of Peripherals</li></ul>                                                                                       | 484<br>485<br>486<br>486<br>487<br>487<br>489<br>490<br>490<br>491<br>493<br>493<br>494<br>493<br>494<br>497<br>497<br>497<br>497<br>497<br>498<br>499<br>506<br>513                                           |

| <ul> <li>31.6. Power Consumption of Peripherals</li></ul>                                                                                       | 484<br>485<br>486<br>486<br>486<br>487<br>489<br>490<br>491<br>491<br>493<br>493<br>494<br>493<br>494<br>497<br>497<br>497<br>498<br>499<br>506<br>513                                                         |

| <ul> <li>31.6. Power Consumption of Peripherals</li></ul>                                                                                       | 484<br>485<br>486<br>486<br>487<br>489<br>490<br>490<br>491<br>491<br>493<br>493<br>494<br>493<br>494<br>497<br>497<br>497<br>497<br>498<br>499<br>506<br>513<br>515                                           |

| <ul> <li>31.6. Power Consumption of Peripherals</li></ul>                                                                                       | 484<br>485<br>486<br>486<br>487<br>487<br>489<br>490<br>490<br>491<br>493<br>493<br>493<br>494<br>493<br>494<br>497<br>497<br>497<br>497<br>497<br>497<br>506<br>513<br>513<br>515<br>518<br>518<br>523<br>526 |

#### 6.10.4.3 Oscillator Configuration

|        | Name:<br>Offset:<br>Reset:<br>Property: | OSCCFG<br>0x02<br>-<br>- |   |   |   |               |       |          |

|--------|-----------------------------------------|--------------------------|---|---|---|---------------|-------|----------|

| Bit    | 7                                       | 6                        | 5 | 4 | 3 | 2             | 1     | 0        |

|        | OSCLOCK                                 |                          |   |   |   |               | FREQS | SEL[1:0] |

| Access | R                                       |                          |   | • | • | · · · · · · · | R     | R        |

| Reset  | 0                                       |                          |   |   |   |               | 1     | 0        |

#### Bit 7 – OSCLOCK Oscillator Lock

This fuse bit is loaded to LOCK in CLKCTRL.OSC20MCALIBB during Reset.

| Value | Description                                                   |

|-------|---------------------------------------------------------------|

| 0     | Calibration registers of the 20 MHz oscillator are accessible |

| 1     | Calibration registers of the 20 MHz oscillator are locked     |

#### Bits 1:0 – FREQSEL[1:0] Frequency Select

These bits select the operation frequency of the 16/20 MHz internal oscillator (OSC20M) and determine the respective factory calibration values to be written to CAL20M in CLKCTRL.OSC20MCALIBA and TEMPCAL20M in CLKCTRL.OSC20MCALIBB.

| Value | Description                                          |

|-------|------------------------------------------------------|

| 0x1   | Run at 16 MHz with corresponding factory calibration |

| 0x2   | Run at 20 MHz with corresponding factory calibration |

| Other | Reserved                                             |

#### **Related Links**

10.4 Register Summary - CLKCTRL

12. RSTCTRL - Reset Controller

- Event 3: Clock period = 1024 RTC clock cycles

- Event 4: Clock period = 512 RTC clock cycles

- Event 5: Clock period = 256 RTC clock cycles

- Event 6: Clock period = 128 RTC clock cycles

- Event 7: Clock period = 64 RTC clock cycles

The event users are configured by the Event System (EVSYS).

#### **Related Links**

14. EVSYS - Event System

## 22.6 Interrupts

#### Table 22-2. Available Interrupt Vectors and Sources For Devices With Up to 8 KB Flash

| Offset | Name | Vector Description                                           | Conditions                                                                                                                                                                       |  |  |  |

|--------|------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0x00   | RTC  | Real-time counter<br>overflow and compare<br>match interrupt | <ul> <li>Overflow (OVF): The counter has reached its top value and wrapped to zero.</li> <li>Compare (CMP): Match between the counter value and the compare register.</li> </ul> |  |  |  |

| 0x02   | PIT  | Periodic Interrupt Timer interrupt                           | A time period has passed, as configured in RTC_PITCTRLA.PERIOD.                                                                                                                  |  |  |  |

#### Table 22-3. Available Interrupt Vectors and Sources For Devices With More Than 8 KB Flash

| Offset | Name | Vector Description                                           | Conditions                                                                                                                                                                       |

|--------|------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00   | RTC  | Real-time counter<br>overflow and compare<br>match interrupt | <ul> <li>Overflow (OVF): The counter has reached its top value and wrapped to zero.</li> <li>Compare (CMP): Match between the counter value and the compare register.</li> </ul> |

| 0x04   | PIT  | Periodic Interrupt Timer interrupt                           | A time period has passed, as configured in RTC_PITCTRLA.PERIOD.                                                                                                                  |

When an interrupt condition occurs, the corresponding interrupt flag is set in the Interrupt Flags register of the peripheral (*peripheral*.INTFLAGS).

An interrupt source is enabled or disabled by writing to the corresponding enable bit in the peripheral's Interrupt Control register (*peripheral*.INTCTRL).

An interrupt request is generated when the corresponding interrupt source is enabled and the interrupt flag is set. The interrupt request remains active until the interrupt flag is cleared. See the peripheral's INTFLAGS register for details on how to clear interrupt flags.

#### **Related Links**

CPUINT - CPU Interrupt Controller

INTCTRL

INTCTRL

PITINTCTRL

#### 22.11.9 Period

| Name:     | PER  |

|-----------|------|

| Offset:   | 0x0A |

| Reset:    | 0xFF |

| Property: | -    |

The RTC.PERL and RTC.PERH register pair represents the 16-bit value, PER. The low byte [7:0] (suffix L) is accessible at the original offset. The high byte [15:8] (suffix H) can be accessed at offset + 0x01. For more details on reading and writing 16-bit registers, refer to Accessing 16-bit Registers in the CPU chapter.

Due to synchronization between the RTC clock and system clock domains, there is a latency of two RTC clock cycles from updating the register until this has an effect. Application software needs to check that the PERBUSY flag in RTC.STATUS is cleared before writing to this register.

| Bit    | 15        | 14  | 13  | 12  | 11  | 10  | 9   | 8   |  |

|--------|-----------|-----|-----|-----|-----|-----|-----|-----|--|

|        | PER[15:8] |     |     |     |     |     |     |     |  |

| Access | R/W       | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Reset  | 1         | 1   | 1   | 1   | 1   | 1   | 1   | 1   |  |

|        |           |     |     |     |     |     |     |     |  |

| Bit    | 7         | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|        | PER[7:0]  |     |     |     |     |     |     |     |  |

| Access | R/W       | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Reset  | 1         | 1   | 1   | 1   | 1   | 1   | 1   | 1   |  |

Bits 15:8 - PER[15:8] Period High Byte

These bits hold the MSB of the 16-bit Period register.

Bits 7:0 - PER[7:0] Period Low Byte

These bits hold the LSB of the 16-bit Period register.

# ATtiny807/1607

**USART - Universal Synchronous and Asynchrono...**

| USART | SPI  | Comment                                   |

|-------|------|-------------------------------------------|

| TxD   | MOSI | Master out only                           |

| RxD   | MISO | Master in only                            |

| ХСК   | SCK  | Functionally identical                    |

| -     | SS   | Not supported by USART in Master SPI mode |

#### Table 23-8. Comparison of USART in Master SPI Mode and SPI Pins

#### **Related Links**

23.5.9 CTRLC

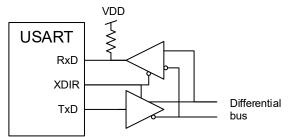

#### 23.3.2.6 RS-485 Mode of Operation

The RS-485 feature enables the support of external components to comply with the RS-485 standard.

Either an external line driver is supported as shown in the figure below (RS-485=0x1 in USARTn.CTRLA), or control of the transmitter driving the TxD pin is provided (RS-485=0x2).

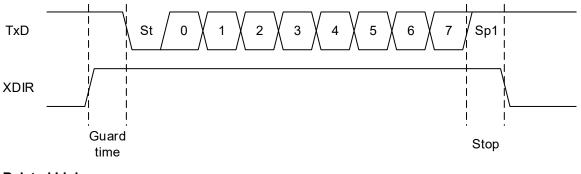

While operating in RS-485 mode, the Transmit Direction pin (XDIR) is driven high when the transmitter is active.

#### Figure 23-10. RS-485 Bus Connection

The XDIR pin goes high one baud clock cycle in advance of data being shifted out, to allow some guard time to enable the external line driver. The XDIR pin will remain high for the complete frame including Stop bit(s).

#### Related Links 23.2.1 Signal Description

#### 23.3.2.7 Start Frame Detection

The start frame detection is supported in UART mode only. The UART start frame detector is limited to Standby Sleep mode only and can wake up the system when a Start bit is detected.

#### 23.5.5 USART Status Register

| Name:     | STATUS |

|-----------|--------|

| Offset:   | 0x04   |

| Reset:    | 0x00   |

| Property: | -      |

| Bit    | 7     | 6     | 5     | 4     | 3     | 2 | 1   | 0   |

|--------|-------|-------|-------|-------|-------|---|-----|-----|

|        | RXCIF | TXCIF | DREIF | RXSIF | ISFIF |   | BDF | WFB |

| Access | R     | R/W   | R     | R/W   | R/W   |   | R/W | R/W |

| Reset  | 0     | 0     | 0     | 0     | 0     |   | 0   | 0   |

#### Bit 7 – RXCIF USART Receive Complete Interrupt Flag

This flag is set to '1' when there is unread data in the receive buffer and cleared when the receive buffer is empty (i.e. does not contain any unread data). When the receiver is disabled, the receive buffer will be flushed and consequently, the RXCIF will become '0'.

When interrupt-driven data reception is used, the receive complete interrupt routine must read the received data from RXDATA in order to clear the RXCIF. If not, a new interrupt will occur directly after the return from the current interrupt.

#### Bit 6 – TXCIF USART Transmit Complete Interrupt Flag

This flag is set when the entire frame in the Transmit Shift register has been shifted out and there are no new data in the transmit buffer (TXDATA).

This flag is automatically cleared when the transmit complete interrupt vector is executed. The flag can also be cleared by writing a '1' to its bit location.

## Bit 5 – DREIF USART Data Register Empty Flag

The DREIF indicates if the transmit buffer (TXDATA) is ready to receive new data. The flag is set to '1' when the transmit buffer is empty and is '0' when the transmit buffer contains data to be transmitted that has not yet been moved into the Shift register. DREIF is set after a Reset to indicate that the transmitter is ready. Always write this bit to '0' when writing the STATUS register.

DREIF is cleared to '0' by writing TXDATAL. When interrupt-driven data transmission is used, the Data Register Empty interrupt routine must either write new data to TXDATA in order to clear DREIF or disable the Data Register Empty interrupt. If not, a new interrupt will occur directly after the return from the current interrupt.

#### Bit 4 – RXSIF USART Receive Start Interrupt Flag

The RXSIF flag indicates a valid Start condition on RxD line. The flag is set when the system is in standby modes and a high (IDLE) to low (START) valid transition is detected on the RxD line. If the start detection is not enabled, the RXSIF will always be read as '0'. This flag can only be cleared by writing a '1' to its bit location. This flag is not used in the Master SPI mode operation.

#### Bit 3 – ISFIF Inconsistent Sync Field Interrupt Flag

This bit is set when the auto-baud is enabled and the sync field bit time is too fast or too slow to give a valid baud setting. It will also be set when USART is set to LINAUTO mode and the SYNC character differ from data value 0x55.

Writing a '1' to this bit will clear the flag and bring the USART back to Idle state.

#### 24.5.3 Interrupt Control

| Name:     | INTCTRL |

|-----------|---------|

| Offset:   | 0x02    |

| Reset:    | 0x00    |

| Property: | -       |

| Bit    | 7     | 6     | 5     | 4    | 3 | 2 | 1 | 0   |

|--------|-------|-------|-------|------|---|---|---|-----|

|        | RXCIE | TXCIE | DREIE | SSIE |   |   |   | IE  |

| Access | R/W   | R/W   | R/W   | R/W  |   |   |   | R/W |

| Reset  | 0     | 0     | 0     | 0    |   |   |   | 0   |

Bit 7 – RXCIE Receive Complete Interrupt Enable

In Buffer mode, this bit enables the receive complete interrupt. The enabled interrupt will be triggered when the RXCIF flag in the SPIn.INTFLAGS register is set. In the Non-Buffer mode this bit is zero.

#### Bit 6 - TXCIE Transfer Complete Interrupt Enable

In Buffer mode, this bit enables the transfer complete interrupt. The enabled interrupt will be triggered when the TXCIF flag in the SPIn.INTFLAGS register is set. In the Non-Buffer mode, this bit is zero.

#### Bit 5 – DREIE Data Register Empty Interrupt Enable

In Buffer mode, this bit enables the data register empty interrupt. The enabled interrupt will be triggered when the DREIF flag in the SPIn.INTFLAGS register is set. In the Non-Buffer mode, this bit is zero.

#### Bit 4 – SSIE Slave Select Trigger Interrupt Enable

In Buffer mode, this bit enables the Slave Select interrupt. The enabled interrupt will be triggered when the SSIF flag in the SPIn.INTFLAGS register is set. In the Non-Buffer mode, this bit is zero.

#### Bit 0 - IE Interrupt Enable

This bit enables the SPI interrupt when the SPI is not in Buffer mode. The enabled interrupt will be triggered when RXCIF/IF is set in the SPIn.INTFLAGS register.

Disable bit (SSD) is not '1'. The flag is cleared by writing a 1 to its bit location. In the Non-Buffer mode, this bit is always 0.

### Bit 0 – BUFOVF Buffer Overflow

This flag is only used in Buffer mode. This flag indicates data loss due to a receiver buffer full condition. This flag is set if a buffer overflow condition is detected. A buffer overflow occurs when the receive buffer is full (two characters) and a third byte has been received in the Shift register. If there is no transmit data the buffer overflow will not be set before the start of a new serial transfer. This flag is valid until the receive buffer (SPIn.DATA) is read. Always write this bit location to 0 when writing the SPIn.INTFLAGS register. In the Non-Buffer mode, this bit is always 0.

0

0

#### 24.5.5 Data

Reset

|        | Name:<br>Offset:<br>Reset:<br>Property: | DATA<br>0x04<br>0x00<br>- |     |      |                |     |     |     |  |

|--------|-----------------------------------------|---------------------------|-----|------|----------------|-----|-----|-----|--|

| Bit    | 7                                       | 6                         | 5   | 4    | 3              | 2   | 1   | 0   |  |

|        |                                         |                           |     | DATA | <b>\</b> [7:0] |     |     |     |  |

| Access | R/W                                     | R/W                       | R/W | R/W  | R/W            | R/W | R/W | R/W |  |

#### Bits 7:0 - DATA[7:0] SPI Data

0

0

0

The SPIn.DATA register is used for sending and receiving data. Writing to the register initiates the data transmission, and the byte written to the register will be shifted out on the SPI output line.

0

0

Reading this register in Buffer mode will read the second receive buffer and the contents of the first receive buffer will be moved to the second receive buffer.

0

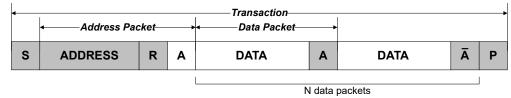

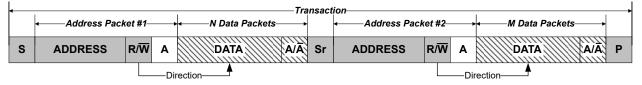

Figure 25-7 illustrates the master read transaction. The master initiates the transaction by issuing a Start condition followed by an address packet with the direction bit set to '1' (ADDRESS+R). The addressed slave must acknowledge the address for the master to be allowed to continue the transaction.

#### Figure 25-7. Master Read Transaction

Assuming the slave acknowledges the address, the master can start receiving data from the slave. There are no limitations to the number of data packets that can be transferred. The slave transmits the data while the master signals ACK or NACK after each data byte. The master terminates the transfer with a NACK before issuing a Stop condition.

Figure 25-8 illustrates a combined transaction. A combined transaction consists of several read and write transactions separated by repeated Start conditions (Sr).

#### Figure 25-8. Combined Transaction

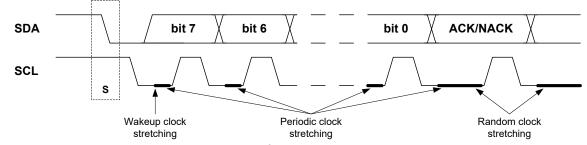

#### 25.3.2.6 Clock and Clock Stretching

All devices connected to the bus are allowed to stretch the low period of the clock to slow down the overall clock frequency or to insert Wait states while processing data. A device that needs to stretch the clock can do this by holding/forcing the SCL line low after it detects a low level on the line.

Three types of clock stretching can be defined, as shown in Figure 25-9.

#### Figure 25-9. Clock Stretching <sup>(1)</sup>

**Note:** Clock stretching is not supported by all I<sup>2</sup>C slaves and masters.

If a slave device is in Sleep mode and a Start condition is detected, the clock stretching normally works during the wake-up period. For AVR devices, the clock stretching will be either directly before or after the ACK/NACK bit, as AVR devices do not need to wake-up for transactions that are not addressed to it.

A slave device can slow down the bus frequency by stretching the clock periodically on a bit level. This allows the slave to run at a lower system clock frequency. However, the overall performance of the bus will be reduced accordingly. Both the master and slave device can randomly stretch the clock on a byte level basis before and after the ACK/NACK bit. This provides time to process incoming or prepare outgoing data or perform other time-critical tasks.

#### 26.5.1 Control A

Name:

CTRLA

Offset:

0x00

Reset:

0x00

Property:

If an NMI has been triggered, this register is not writable.

| Bit    | 7     | 6 | 5 | 4 | 3 | 2 | 1     | 0      |

|--------|-------|---|---|---|---|---|-------|--------|

|        | RESET |   |   |   |   |   | NMIEN | ENABLE |

| Access | R/W   |   |   |   |   |   | R/W   | R/W    |

| Reset  | 0     |   |   |   |   |   | 0     | 0      |

#### Bit 7 – RESET Reset CRCSCAN

Writing this bit to '1' resets the CRCSCAN peripheral: The CRCSCAN Control registers and STATUS register (CTRLA, CTRLB, STATUS) will be cleared one clock cycle after the RESET bit was written to '1'.

If NMIEN is '0', this bit is writable both when the CRCSCAN is busy (the BUSY bit in CRCSCAN.STATUS is '1') and not busy (the BUSY bit is '0'), and will take effect immediately.

If NMIEN is '1', this bit is only writable when the CRCSCAN is not busy (the BUSY bit in CRCSCAN.STATUS is '0').

The RESET bit is a strobe bit.

#### Bit 1 – NMIEN Enable NMI Trigger

When this bit is written to '1', any CRC failure will trigger an NMI.

This can only be cleared by a system Reset - it is not cleared by a write to the RESET bit.

This bit can only be written to '1' when the CRCSCAN is not busy (the BUSY bit in CRCSCAN.STATUS is '0').

#### Bit 0 – ENABLE Enable CRCSCAN

Writing this bit to '1' enables the CRCSCAN peripheral with the current settings. It will stay '1' even after a CRC check has completed, but writing it to '1' again will start a new check.

Writing the bit to '0' will disable the CRCSCAN after the ongoing check is completed (after reaching the end of the section it is set up to check). A failure in the ongoing check will still be detected and can cause an NMI if the NMIEN bit is '1'.

The CRCSCAN can be enabled during the internal Reset initialization to verify Flash sections before letting the CPU start normal code execution (see the device data sheet fuse description). If the CRCSCAN is enabled during the internal Reset initialization, the ENABLE bit will read as '1' when normal code execution starts.

To see whether the CRCSCAN peripheral is busy with an ongoing check, poll the Busy bit (BUSY) in the STATUS register (CRCSCAN.STATUS).

#### Related Links

6.10 Configuration and User Fuses (FUSE)12.3.2.2 Reset Time

## 27.5.6 TRUTHn

| Name:     | TRUTH                |

|-----------|----------------------|

| Offset:   | 0x08 + n*0x04 [n=01] |

| Reset:    | 0x00                 |

| Property: | Enable-Protected     |

| Bit    | 7   | 6   | 5   | 4    | 3      | 2   | 1   | 0   |

|--------|-----|-----|-----|------|--------|-----|-----|-----|

| Γ      |     |     |     | TRUT | H[7:0] |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W    | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0      | 0   | 0   | 0   |

## Bits 7:0 - TRUTH[7:0] Truth Table

These bits define the value of truth logic as a function of inputs IN[2:0].

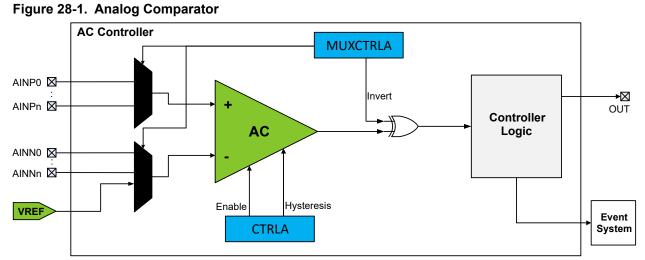

#### 28.2.1 Block Diagram

Note: Refer to 28.2.2 Signal Description for the number of AINN and AINP.

#### 28.2.2 Signal Description

| Signal | Description              | Туре    |

|--------|--------------------------|---------|

| AINN0  | Negative Input 0         | Analog  |

| AINN1  | Negative Input 1         | Analog  |

| AINP0  | Positive Input 0         | Analog  |

| AINP1  | Positive Input 1         | Analog  |

| OUT    | Comparator Output for AC | Digital |

## 28.2.3 System Dependencies

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

#### Table 28-1. AC System Dependencies

| Dependency                | Applicable | Peripheral |

|---------------------------|------------|------------|

| Clocks                    | Yes        | CLKCTRL    |

| I/O Lines and Connections | Yes        | PORT       |

| Interrupts                | Yes        | CPUINT     |

| Events                    | Yes        | EVSYS      |

| Debug                     | Yes        | UPDI       |

#### 28.2.3.1 Clocks

This peripheral depends on the peripheral clock.

#### 28.2.3.2 I/O Lines and Connections

I/O pins AINN0-AINN1 and AINP0- AINP1 are all analog inputs to the AC.

For correct operation, the pins must be configured in the port and port multiplexing peripherals.

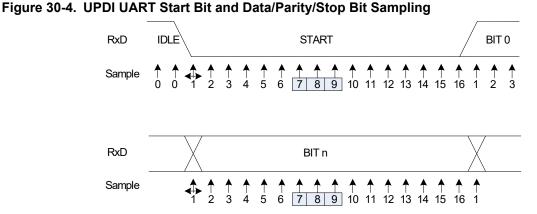

#### 30.3.1.1 UPDI UART

All transmission and reception of serial data on the UPDI is achieved using the UPDI frames presented in Figure 30-3. Communication is initiated from the master (debugger) side, and every transmission must start with a SYNCH character upon which the UPDI can recover the transmission baud rate, and store this setting for the coming data. The baud rate set by the SYNCH character will be used for both reception and transmission for the instruction byte received after the SYNCH. See 30.3.3 UPDI Instruction Set for details on when the next SYNCH character is expected in the instruction stream.

There is no writable baud rate register in the UPDI, so the baud rate sampled from the SYNCH character is used for data recovery by sampling the Start bit, and performing a majority vote on the middle samples. This process is repeated for all bits in the frame, including the parity bit and two Stop bits. The baud generator uses 16 samples, and the majority voting is done on sample 7, 8, and 9.

The transmission baud rate must be set up in relation to the selected UPDI clock, which can be adjusted by UPDICLKSEL in UPDI.ASI\_CTRLA. See Table 30-2 for recommended maximum and minimum baud rate settings.

#### Table 30-2. Recommended UART Baud Rate Based on UPDICLKSEL Setting

| UPDICLKSEL[1:0]       | MAX Recommended Baud Rate | MIN Recommended Baud Rate |

|-----------------------|---------------------------|---------------------------|

| 0x1 (16 MHz)          | 0.9 Mbps                  | 0.300 kbps                |

| 0x2 (8 MHz)           | 450 kbps                  | 0.150 kbps                |

| 0x3 (4 MHz) - Default | 225 kbps                  | 0.075 kbps                |

The UPDI Baud Rate Generator utilizes fractional baud counting to minimize the transmission error. With the fixed frame format used by the UPDI, the maximum and recommended receiver transmission error limits can be seen in the following table:

#### Table 30-3. Receiver Baud Rate Error

| Data + Parity Bits | R <sub>slow</sub> | R <sub>fast</sub> |             | Recommended<br>Max. RX Error [%] |

|--------------------|-------------------|-------------------|-------------|----------------------------------|

| 9                  | 96.39             | 104.76            | +4.76/-3.61 | +1.5/-1.5                        |

#### 30.3.1.2 BREAK Character

The BREAK character is used to reset the internal state of the UPDI to the default setting. This is useful if the UPDI enters an error state due to a communication error, or when the synchronization between the debugger and the UPDI is lost.

## ATtiny807/1607 UPDI - Unified Program and Debug Interface

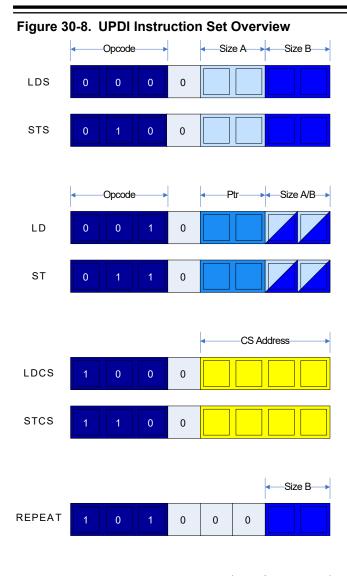

| - |    |    |                           |  |  |  |

|---|----|----|---------------------------|--|--|--|

| 0 | РC | 0[ | DE                        |  |  |  |

| 0 | 0  | 0  | LDS                       |  |  |  |

| 0 | 0  | 1  | LD                        |  |  |  |

| 0 | 1  | 0  | STS                       |  |  |  |

| 0 | 1  | 1  | ST                        |  |  |  |

| 1 | 0  | 0  | LDCS (LDS Control/Status) |  |  |  |

| 1 | 0  | 1  | REPEAT                    |  |  |  |

| 1 | 1  | 0  | STCS (STS Control/Status) |  |  |  |

| 1 | 1  | 1  | KEY                       |  |  |  |

| Si | Size A - Address size |                |  |  |  |

|----|-----------------------|----------------|--|--|--|

| 0  | 0                     | Byte           |  |  |  |

| 0  | 1                     | Word (2 Bytes) |  |  |  |

| 1  | 0                     | Reserved       |  |  |  |

| 1  | 1                     | Reserved       |  |  |  |

| Pt | Ptr - Pointer access |          |  |  |  |  |

|----|----------------------|----------|--|--|--|--|

| 0  | 0                    | *(ptr)   |  |  |  |  |

| 0  | 1                    | *(ptr++) |  |  |  |  |

| 1  | 0                    | ptr      |  |  |  |  |

| 1  | 1                    | Reserved |  |  |  |  |

| Si | Size B - Data size |                |  |  |  |  |

|----|--------------------|----------------|--|--|--|--|

| 0  | 0                  | Byte           |  |  |  |  |

| 0  | 1                  | Word (2 Bytes) |  |  |  |  |

| 1  | 0                  | Reserved       |  |  |  |  |

| 1  | 1                  | Reserved       |  |  |  |  |

| C | CS Address (CS - Control/Status reg.) |   |   |                     |  |  |  |

|---|---------------------------------------|---|---|---------------------|--|--|--|

| 0 | 0                                     | 0 | 0 | Reg 0               |  |  |  |

| 0 | 0                                     | 0 | 1 | Reg 1               |  |  |  |

| 0 | 0                                     | 1 | 0 | Reg 2               |  |  |  |

| 0 | 0                                     | 1 | 1 | Reg 3               |  |  |  |

| 0 | 1                                     | 0 | 0 | Reg 4 (ASICS space) |  |  |  |

|   |                                       |   |   |                     |  |  |  |

1 1 1 1 Reserved

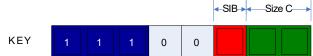

| Size C - Key size                   |   |                     |  |  |  |  |

|-------------------------------------|---|---------------------|--|--|--|--|

| 0                                   | 0 | 64 bits (8 Bytes)   |  |  |  |  |

| 0                                   | 1 | 128 bits (16 Bytes) |  |  |  |  |

| 1                                   | 0 | Reserved            |  |  |  |  |

| 1                                   | 1 | Reserved            |  |  |  |  |

|                                     |   |                     |  |  |  |  |

| SIB – System Information Block sel. |   |                     |  |  |  |  |

| SI | B – System Information Block sel. |

|----|-----------------------------------|

| 0  | Receive KEY                       |

| 1  | Send SIB                          |

| Symbol              | Description                              | Condition                               | Min | Tun  | Mox  | Unit |

|---------------------|------------------------------------------|-----------------------------------------|-----|------|------|------|

| Symbol              | Description                              | Condition                               |     | тур. | Max. | Unit |

| t <sub>wakeup</sub> | Start-up time from any Reset release     |                                         | -   | 200  | -    | μs   |

|                     | Wake-up from Idle mode                   | OSC20M @ 20 MHz;<br>V <sub>DD</sub> =5V | -   | 1    | -    |      |

|                     |                                          | OSC20M @ 10 MHz;<br>V <sub>DD</sub> =3V | -   | 2    | -    | -    |

|                     |                                          | OSC20M @ 5 MHz;<br>V <sub>DD</sub> =2V  | -   | 4    | -    |      |

|                     | Wake-up from Standby and Power-down mode |                                         | -   | 10   | -    |      |

## Table 31-6. Start-Up, Reset, and Wake-Up Time from OSC20M

## **31.6** Power Consumption of Peripherals

The table below can be used to calculate the additional current consumption for the different I/O peripherals in the various operating modes.

Operating conditions:

- V<sub>DD</sub> = 3V

- T = 25°C

- OSC20M at 1 MHz used as system clock source, except where otherwise specified

- In Idle Sleep mode, except where otherwise specified

## Table 31-7. Power Consumption of Peripherals

| Peripheral   | Conditions                    | Typ. <sup>(1)</sup> | Unit |

|--------------|-------------------------------|---------------------|------|

| BOD          | Continuous                    | 19                  | μA   |

|              | Sampling @ 1 kHz              | 1.2                 |      |

| TCA          | 16-bit count @ 1 MHz          | 12.6                | μA   |

| ТСВ          | 16-bit count @ 1 MHz          | 7.4                 | μA   |

| RTC          | 16-bit count                  | 1.2                 | μA   |

| WDT          |                               | 0.7                 | μA   |

| OSC20M       |                               | 125                 | μA   |

| AC           | Low-power mode <sup>(2)</sup> | 45                  | μA   |

| ADC          | 50 ksps                       | 325                 | μA   |

|              | 100 ksps                      | 340                 | μA   |

| USART        | Enable @ 9600 Baud            | 13                  | μA   |

| SPI (Master) | Enable @ 100 kHz              | 2.1                 | μA   |

| TWI (Master) | Enable @ 100 kHz              | 23.9                | μA   |

| Peripheral        | Conditions       | Тур. <sup>(1)</sup> | Unit |

|-------------------|------------------|---------------------|------|

| TWI (Slave)       | Enable @ 100 kHz | 17.1                | μA   |

| Flash programming | Erase Operation  | 1.5                 | mA   |

|                   | Write Operation  | 3.0                 |      |

Note:

- 1. Current consumption of the module only. To calculate the total power consumption of the system, add this value to the base power consumption as listed in *Power Consumption*.

- 2. CPU in Standby mode.

## 31.7 BOD and POR Characteristics

## Table 31-8. Power Supply Characteristics

| Symbol | Description    | Condition | Min. | Тур. | Max. | Unit |

|--------|----------------|-----------|------|------|------|------|

| SRON   | Power-on Slope |           | -    | -    | 100  | V/ms |

### Table 31-9. Power-On Reset (POR) Characteristics

| Symbol | Description                               | Condition                                         | Min. | Тур. | Max. | Unit |

|--------|-------------------------------------------|---------------------------------------------------|------|------|------|------|

| VPOR   | POR threshold voltage on $V_{DD}$ falling | V <sub>DD</sub> falls/rises at 0.5 V/ms or slower | 0.8  | -    | 1.6  | V    |

|        | POR threshold voltage on $V_{DD}$ rising  |                                                   | 1.4  | -    | 1.8  |      |

#### Table 31-10. Brown-Out Detection (BOD) Characteristics

| Symbol             | Description                           | Condition                               | Min. | Тур. | Max. | Unit |  |

|--------------------|---------------------------------------|-----------------------------------------|------|------|------|------|--|

| VBOD               | BOD triggering level (falling/rising) | BODLEVEL7                               | 3.9  | 4.2  | 4.5  | V    |  |

|                    |                                       | BODLEVEL2                               | 2.4  | 2.6  | 2.9  |      |  |

|                    |                                       | BODLEVEL0                               | 1.7  | 1.8  | 2.0  |      |  |

| VINT               | Interrupt level 0                     | Percentage above the selected BOD level | -    | 4    | -    | %    |  |

|                    | Interrupt level 1                     |                                         |      | 13   | -    |      |  |

|                    | Interrupt level 2                     |                                         |      | 25   | -    |      |  |

| VHYS               | Hysteresis                            | BODLEVEL7                               | -    | 80   | -    | mV   |  |

|                    |                                       | BODLEVEL2                               | -    | 40   | -    |      |  |

|                    |                                       | BODLEVEL0                               | -    | 25   | -    |      |  |

| TBOD               | Detection time                        | Continuous                              | -    | 7    | -    | μs   |  |

|                    |                                       | Sampled, 1 kHz                          | -    | 1    | -    | ms   |  |

|                    |                                       | Sampled, 125 Hz                         | -    | 8    | -    |      |  |

| T <sub>start</sub> | Start-up time                         | Time from enable to ready               | -    | 40   | -    | μs   |  |

# ATtiny807/1607

**Electrical Characteristics**

| Symbol | Description  | Conditions                  |                               | Min.     | Тур.        | Max. | Unit |    |     |

|--------|--------------|-----------------------------|-------------------------------|----------|-------------|------|------|----|-----|

|        |              | REFSEL =<br>INTERNAL or VDD | f <sub>ADC</sub> =77 ksps     | -        | 0.4         | 1.0  |      |    |     |

|        |              | 1.1V≤V <sub>REF</sub>       |                               |          |             |      |      |    |     |

|        |              | REFSEL =<br>INTERNAL        | f <sub>ADC</sub> =115 ksps    | -        | 0.5         | 1.6  |      |    |     |

|        |              | 1.1V≤V <sub>REF</sub>       |                               |          |             |      |      |    |     |

|        |              | REFSEL = VDD                | f <sub>ADC</sub> =115 ksps    | -        | 0.9         | 2.0  |      |    |     |

|        |              | 1.8V≤V <sub>REF</sub>       |                               |          |             |      |      |    |     |

| EABS   | Absolute     | REFSEL =                    | T=[0-105]°C                   | -        | 3           | 30   | LSB  |    |     |

|        | accuracy     |                             | V <sub>DD</sub> = [1.8V-3.6V] |          |             |      |      |    |     |

|        |              | V <sub>REF</sub> = 1.1V     | V <sub>DD</sub> = [1.8V-3.6V] | -        | 3           | 40   |      |    |     |

|        |              | REFSEL = V <sub>DD</sub>    |                               | -        | 2           | 5    |      |    |     |

|        |              | REFSEL =<br>INTERNAL        |                               | -        | -           | 65   |      |    |     |

| EGAIN  | Gain error   | Gain error                  |                               | REFSEL = | T=[0-105]°C | -25  | 3    | 25 | LSB |

|        |              | INTERNAL                    | V <sub>DD</sub> = [1.8V-3.6V] |          |             |      |      |    |     |

|        |              | V <sub>REF</sub> = 1.1V     | V <sub>DD</sub> = [1.8V-3.6V] | -35      | 3           | 35   |      |    |     |

|        |              | REFSEL = V <sub>DD</sub>    |                               | -1       | 2           | 4    |      |    |     |

|        |              | REFSEL =<br>INTERNAL        |                               | -60      | -           | 60   |      |    |     |

| EOFF   | Offset error | REFSEL =<br>INTERNAL        |                               | -5       | -0.5        | 2    | LSB  |    |     |

|        |              | V <sub>REF</sub> = 0.55V    |                               |          |             |      |      |    |     |

|        |              | REFSEL =<br>INTERNAL        |                               | -4       | -0.5        | 2    | LSB  |    |     |

|        |              | $1.1V \le V_{REF}$          |                               |          |             |      |      |    |     |

#### Note:

- 1. A DNL error of less than or equal to 1 LSB ensures a monotonic transfer function with no missing codes.

- 2. These values are based on characterization and not covered by production test limits.

- 3. Reference setting and f<sub>ADC</sub> must fulfill the specification in Clock and Timing Characteristics, and Power supply, Reference, and Input Range tables.

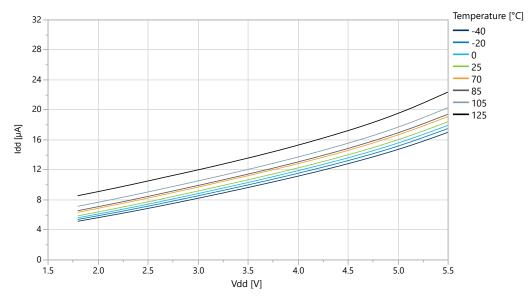

Figure 32-5. Active Supply Current vs. V<sub>DD</sub> (f=32 KHz OSCULP32K)

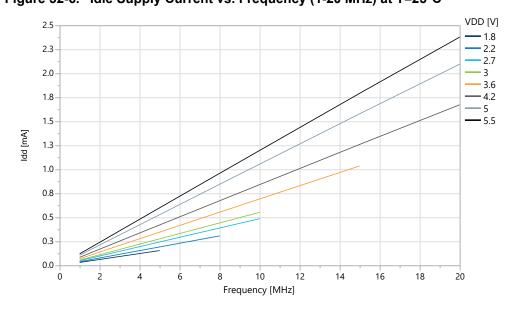

## 32.1.2 Supply Currents in Idle Mode Figure 32-6. Idle Supply Current vs. Frequency (1-20 MHz) at T=25°C

• Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

## Legal Notice

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

## Trademarks

The Microchip name and logo, the Microchip logo, AnyRate, AVR, AVR logo, AVR Freaks, BeaconThings, BitCloud, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KeeLoq, KeeLoq logo, Kleer, LANCheck, LINK MD, maXStylus, maXTouch, MediaLB, megaAVR, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, Prochip Designer, QTouch, RightTouch, SAM-BA, SpyNIC, SST, SST Logo, SuperFlash, tinyAVR, UNI/O, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, EtherSynch, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and Quiet-Wire are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, CryptoAuthentication, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet Iogo, Mindi, MiWi, motorBench, MPASM, MPF, MPLAB Certified Iogo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, QMatrix, RightTouch Iogo, REAL ICE, Ripple Blocker, SAM-ICE, Serial Quad I/O, SMART-I.S., SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.