Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | dsPIC                                                                         |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 20 MIPS                                                                       |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                     |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, QEI, POR, PWM, WDT                 |

| Number of I/O              | 52                                                                            |

| Program Memory Size        | 66KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 1K x 8                                                                        |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 16x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 64-TQFP                                                                       |

| Supplier Device Package    | 64-TQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f5015-20e-pt |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Special Microcontroller Features:**

- Enhanced Flash program memory:

- 10,000 erase/write cycle (minimum) for industrial temperature range, 100K (typical)

- Data EEPROM memory:

- 100,000 erase/write cycle (minimum) for industrial temperature range, 1M (typical)

- Self-reprogrammable under software control

- Power-on Reset (POR), Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Flexible Watchdog Timer (WDT) with on-chip, low-power RC oscillator for reliable operation

- Fail-Safe Clock Monitor operation detects clock failure and switches to on-chip, low-power RC oscillator

- Programmable code protection

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) programming capability

- Selectable Power Management modes:

- Sleep, Idle and Alternate Clock modes

### **CMOS Technology:**

- · Low-power, high-speed Flash technology

- Wide operating voltage range (2.5V to 5.5V)

- Industrial and Extended temperature ranges

- Low power consumption

### dsPIC30F Motor Control and Power Conversion Family

| Device       | Pins | Program<br>Mem. Bytes/<br>Instructions | SRAM<br>Bytes | EEPROM<br>Bytes | Timer<br>16-bit |   | Output<br>Comp/Std<br>PWM | Motor<br>Control<br>PWM | A/D 10-bit<br>1 Msps | Quad<br>Enc | UART | IdS | I²C <sup>TM</sup> | CAN |

|--------------|------|----------------------------------------|---------------|-----------------|-----------------|---|---------------------------|-------------------------|----------------------|-------------|------|-----|-------------------|-----|

| dsPIC30F5015 | 64   | 66K/22K                                | 2048          | 1024            | 5               | 4 | 4                         | 8 ch                    | 16 ch                | Yes         | 1    | 2   | 1                 | 1   |

| dsPIC30F5016 | 80   | 66K/22K                                | 2048          | 1024            | 5               | 4 | 4                         | 8 ch                    | 16 ch                | Yes         | 1    | 2   | 1                 | 1   |

### **Table of Contents**

| 1.0   | Device Overview                                            | 9     |

|-------|------------------------------------------------------------|-------|

| 2.0   | CPU Architecture Overview                                  | 17    |

| 3.0   | Memory Organization                                        | 25    |

| 4.0   | Address Generator Units                                    | 37    |

| 5.0   | Interrupts                                                 | 43    |

| 6.0   | Flash Program Memory                                       | 51    |

| 7.0   | Data EEPROM Memory                                         | 57    |

| 8.0   | I/O Ports                                                  | 61    |

| 9.0   | Timer1 Module                                              | 67    |

| 10.0  | Timer2/3 Module                                            | 71    |

| 11.0  | Timer4/5 Module                                            | 77    |

| 12.0  | Input Capture Module                                       |       |

| 13.0  | Output Compare Module                                      |       |

| 14.0  | Quadrature Encoder Interface (QEI) Module                  |       |

| 15.0  | Motor Control PWM Module                                   |       |

| 16.0  | SPI Module                                                 |       |

| 17.0  | I2C™ Module                                                |       |

| 18.0  | Universal Asynchronous Receiver Transmitter (UART) Module  |       |

| 19.0  | CAN Module                                                 |       |

| 20.0  | 10-bit High-Speed Analog-to-Digital Converter (ADC) Module |       |

| 21.0  | System Integration                                         |       |

| 22.0  | Instruction Set Summary                                    |       |

| 23.0  | Development Support                                        |       |

| 24.0  | Electrical Characteristics                                 |       |

|       | Packaging Information                                      |       |

|       | ndix A: Revision History                                   |       |

|       | ۲                                                          | -     |

| The N | Aicrochip Web Site                                         | . 231 |

|       | omer Change Notification Service                           |       |

| Custo | omer Support                                               | . 231 |

|       | er Response                                                |       |

| Produ | uct Identification System                                  | . 233 |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

| Pin Name              | Pin<br>Type | Buffer<br>Type | Description                                                                                                                              |  |  |  |  |  |  |

|-----------------------|-------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| MCLR                  | I/P         | ST             | Master Clear (Reset) input or programming voltage input. This pin is an active-low Reset to the device.                                  |  |  |  |  |  |  |

| OCFA                  | I           | ST             | ompare Fault A input (for Compare channels 1, 2, 3 and 4).                                                                               |  |  |  |  |  |  |

| OC1-OC4               | 0           | —              | Compare outputs 1 through 4.                                                                                                             |  |  |  |  |  |  |

| OSC1                  | I           | ST/CMOS        | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                          |  |  |  |  |  |  |

| OSC2                  | I/O         | —              | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. |  |  |  |  |  |  |

| PGD                   | I/O         | ST             | In-Circuit Serial Programming™ data input/output pin.                                                                                    |  |  |  |  |  |  |

| PGC                   | I I         | ST             | In-Circuit Serial Programming clock input pin.                                                                                           |  |  |  |  |  |  |

| RB0-RB15              | I/O         | ST             | PORTB is a bidirectional I/O port.                                                                                                       |  |  |  |  |  |  |

| RC13-RC15             | I/O         | ST             | PORTC is a bidirectional I/O port.                                                                                                       |  |  |  |  |  |  |

| RD0-RD11              | I/O         | ST             | PORTD is a bidirectional I/O port.                                                                                                       |  |  |  |  |  |  |

| RE0-RE7               | I/O         | ST             | PORTE is a bidirectional I/O port.                                                                                                       |  |  |  |  |  |  |

| RF0-RF6               | I/O         | ST             | PORTF is a bidirectional I/O port.                                                                                                       |  |  |  |  |  |  |

| RG2-RG3               | I/O         | ST             | PORTG is a bidirectional I/O port.                                                                                                       |  |  |  |  |  |  |

| RG6-RG9               | I/O         | ST             | ·                                                                                                                                        |  |  |  |  |  |  |

| SCK1                  | I/O         | ST             | Synchronous serial clock input/output for SPI1.                                                                                          |  |  |  |  |  |  |

| SDI1                  | 1           | ST             | SPI1 Data In.                                                                                                                            |  |  |  |  |  |  |

| SDO1                  | 0           | _              | SPI1 Data Out.                                                                                                                           |  |  |  |  |  |  |

| SS1                   |             | ST             | SPI1 Slave Synchronization.                                                                                                              |  |  |  |  |  |  |

| SCK2                  | I/O         | ST             | Synchronous serial clock input/output for SPI2.                                                                                          |  |  |  |  |  |  |

| SDI2                  |             | ST             | SPI2 Data In.                                                                                                                            |  |  |  |  |  |  |

| SDO2<br>SS2           | 0           |                | SPI2 Data Out.                                                                                                                           |  |  |  |  |  |  |

|                       |             | ST             | SPI2 Slave Synchronization.                                                                                                              |  |  |  |  |  |  |

| SCL                   | I/O         | ST             | Synchronous serial clock input/output for I <sup>2</sup> C™.                                                                             |  |  |  |  |  |  |

| SDA                   | I/O         | ST             | Synchronous serial data input/output for I <sup>2</sup> C.                                                                               |  |  |  |  |  |  |

| SOSCO                 | 0           |                | 32 kHz low-power oscillator crystal output.                                                                                              |  |  |  |  |  |  |

| SOSCI                 | I           | ST/CMOS        | 32 kHz low-power oscillator crystal input. ST buffer when configured in RC                                                               |  |  |  |  |  |  |

|                       |             |                | mode; CMOS otherwise.                                                                                                                    |  |  |  |  |  |  |

| T1CK                  |             | ST             | Timer1 external clock input.                                                                                                             |  |  |  |  |  |  |

| T4CK                  | I           | ST             | Timer4 external clock input.                                                                                                             |  |  |  |  |  |  |

| U1RX                  |             | ST             | UART1 Receive.                                                                                                                           |  |  |  |  |  |  |

| U1TX                  | 0           |                | UART1 Transmit.                                                                                                                          |  |  |  |  |  |  |

| Vdd                   | Р           |                | Positive supply for logic and I/O pins.                                                                                                  |  |  |  |  |  |  |

| Vss                   | Р           | —              | Ground reference for logic and I/O pins.                                                                                                 |  |  |  |  |  |  |

| Vref+                 | I           | Analog         | Analog Voltage Reference (High) input.                                                                                                   |  |  |  |  |  |  |

| Vref-                 | I           | Analog         | Analog Voltage Reference (Low) input.                                                                                                    |  |  |  |  |  |  |

| Legend: CM<br>ST<br>I |             | hmitt Trigge   | ible input or output Analog = Analog input<br>r input with CMOS levels O = Output<br>P = Power                                           |  |  |  |  |  |  |

#### TABLE 1-1: I/O PIN DESCRIPTIONS FOR dsPIC30F5015 (CONTINUED)

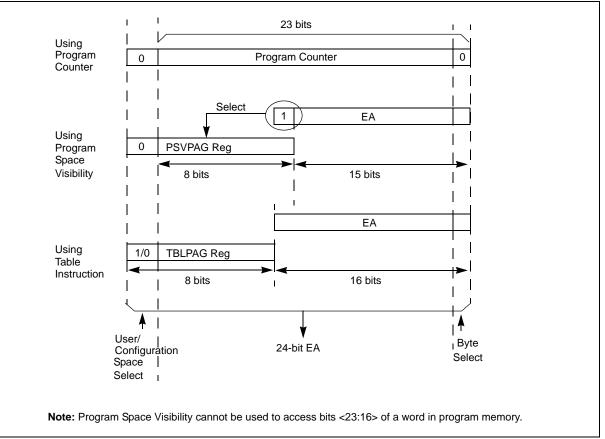

#### TABLE 3-1: PROGRAM SPACE ADDRESS CONSTRUCTION

|                          | Access                           | Program Space Address |                           |               |               |  |  |  |  |

|--------------------------|----------------------------------|-----------------------|---------------------------|---------------|---------------|--|--|--|--|

| Access Type              | Space                            | <23> <22:16> <15      |                           | <15>          | 5> <14:1>     |  |  |  |  |

| Instruction Access       | User                             | 0                     |                           | PC<22:1> 0    |               |  |  |  |  |

| TBLRD/TBLWT              | User<br>(TBLPAG<7> = 0)          | TBL                   | PAG<7:0>                  |               | Data EA<15:0> |  |  |  |  |

| TBLRD/TBLWT              | Configuration<br>(TBLPAG<7> = 1) | TBL                   | PAG<7:0>                  | Data EA<15:0> |               |  |  |  |  |

| Program Space Visibility | User                             | 0                     | PSVPAG<7:0> Data EA<14:0> |               |               |  |  |  |  |

#### FIGURE 3-2: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

# dsPIC30F5015/5016

## 7.0 DATA EEPROM MEMORY

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

The data EEPROM memory is readable and writable during normal operation over the entire VDD range. The data EEPROM memory is directly mapped in the program memory address space.

The four SFRs used to read and write the program Flash memory are used to access data EEPROM memory, as well. As described in **Section 4.0 "Address Generator Units"**, these registers are:

- NVMCON

- NVMADR

- NVMADRU

- NVMKEY

The EEPROM data memory allows read and write of single words and 16-word blocks. When interfacing to data memory, NVMADR, in conjunction with the NVMADRU register, is used to address the EEPROM location being accessed. TBLRDL and TBLWTL instructions are used to read and write data EEPROM.

A word write operation should be preceded by an erase of the corresponding memory location(s). The write typically requires 2 ms to complete, but the write time will vary with voltage and temperature. A program or erase operation on the data EEPROM does not stop the instruction flow. The user is responsible for waiting for the appropriate duration of time before initiating another data EEPROM write/erase operation. Attempting to read the data EEPROM while a programming or erase operation is in progress results in unspecified data.

Control bit WR initiates write operations, similar to program Flash writes. This bit cannot be cleared, only set, in software. This bit is cleared in hardware at the completion of the write operation. The inability to clear the WR bit in software prevents the accidental or premature termination of a write operation.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a  $\overline{\text{MCLR}}$  Reset, or a WDT Time-out Reset, during normal operation. In these situations, following Reset, the user can check the WRERR bit and rewrite the location. The address register NVMADR remains unchanged.

Note: Interrupt flag bit NVMIF in the IFS0 register is set when write is complete. It must be cleared in software.

## 7.1 Reading the Data EEPROM

A TBLRD instruction reads a word at the current program word address. This example uses W0 as a pointer to data EEPROM. The result is placed in register W4, as shown in Example 7-1.

#### EXAMPLE 7-1: DATA EEPROM READ

| MOV    | #LOW_ADDR_WORD,W0  | ; Init Pointer     |

|--------|--------------------|--------------------|

| MOV    | #HIGH_ADDR_WORD,W1 |                    |

| MOV    | W1 TBLPAG          |                    |

| TBLRDL | [ w0 ], w4         | ; read data EEPROM |

### 12.1.2 CAPTURE BUFFER OPERATION

Each capture channel has an associated FIFO buffer, which is four 16-bit words deep. There are two status flags, which provide status on the FIFO buffer:

- ICBFNE Input Capture Buffer Not Empty

- ICOV Input Capture Overflow

The ICBFNE will be set on the first input capture event and remain set until all capture events have been read from the FIFO. As each word is read from the FIFO, the remaining words are advanced by one position within the buffer.

In the event that the FIFO is full with four capture events and a fifth capture event occurs prior to a read of the FIFO, an overflow condition will occur and the ICOV bit will be set to a logic '1'. The fifth capture event is lost and is not stored in the FIFO. No additional events will be captured till all four events have been read from the buffer.

If a FIFO read is performed after the last read and no new capture event has been received, the read will yield indeterminate results.

# 12.1.3 TIMER2 AND TIMER3 SELECTION MODE

Each capture channel can select between one of two timers for the time base, Timer2 or Timer3.

Selection of the timer resource is accomplished through SFR bit ICTMR (ICxCON<7>). Timer3 is the default timer resource available for the input capture module.

#### 12.1.4 HALL SENSOR MODE

When the input capture module is set for capture on every edge, rising and falling, ICM<2:0> = 001, the following operations are performed by the input capture logic:

- The input capture interrupt flag is set on every edge, rising and falling

- The interrupt on Capture mode setting bits, ICI<1:0>, is ignored, since every capture generates an interrupt

- A capture overflow condition is not generated in this mode

### 12.2 Input Capture Operation During Sleep and Idle Modes

An input capture event will generate a device wake-up or interrupt, if enabled, if the device is in CPU Idle or Sleep mode.

Independent of the timer being enabled, the input capture module will wake-up from the CPU Sleep or Idle mode when a capture event occurs, if ICM<2:0> = 111 and the interrupt enable bit is asserted. The same wake-up can generate an interrupt if the conditions for processing the interrupt have been satisfied. The wake-up feature is useful as a method of adding extra external pin interrupts.

#### 12.2.1 INPUT CAPTURE IN CPU SLEEP MODE

CPU Sleep mode allows input capture module operation with reduced functionality. In the CPU Sleep mode, the ICI<1:0> bits are not applicable, and the input capture module can only function as an external interrupt source.

The capture module must be configured for interrupt only on the rising edge (ICM<2:0> = 111) in order for the input capture module to be used while the device is in Sleep mode. The prescale settings of 4:1 or 16:1 are not applicable in this mode.

# 12.2.2 INPUT CAPTURE IN CPU IDLE MODE

CPU Idle mode allows input capture module operation with full functionality. In the CPU Idle mode, the Interrupt mode selected by the ICI<1:0> bits is applicable, as well as the 4:1 and 16:1 capture prescale settings, which are defined by control bits ICM<2:0>. This mode requires the selected timer to be enabled. Moreover, the ICSIDL bit must be asserted to a logic '0'.

If the input capture module is defined as ICM<2:0> = 111 in CPU Idle mode, the input capture pin will serve only as an external interrupt pin.

### 12.3 Input Capture Interrupts

The input capture channels have the ability to generate an interrupt, based upon the selected number of capture events. The selection number is set by control bits ICI<1:0> (ICxCON<6:5>).

Each channel provides an interrupt flag bit (ICxIF). The respective capture channel interrupt flag is located in the corresponding IFSx Status register.

Enabling an interrupt is accomplished via the respective Capture Channel Interrupt Enable bit (ICxIE). The Capture Interrupt Enable bit is located in the corresponding IEC Control register.

# dsPIC30F5015/5016

NOTES:

## 19.0 CAN MODULE

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

#### 19.1 Overview

The Controller Area Network (CAN) module is a serial interface, useful for communicating with other CAN modules or microcontroller devices. This interface/ protocol was designed to allow communications within noisy environments. Only one CAN module is available.

The CAN module is a communication controller implementing the CAN 2.0 A/B protocol, as defined in the BOSCH specification. The module will support CAN 1.2, CAN 2.0A, CAN 2.0B Passive and CAN 2.0B Active versions of the protocol. The module implementation is a full CAN system. The CAN specification is not covered within this data sheet. The reader may refer to the BOSCH CAN specification for further details.

The module features are as follows:

- Implementation of the CAN protocol CAN 1.2, CAN 2.0A and CAN 2.0B

- Standard and extended data frames

- 0-8 bytes data length

- · Programmable bit rate up to 1 Mbit/sec

- Support for remote frames

- Double-buffered receiver with two prioritized received message storage buffers (each buffer may contain up to 8 bytes of data)

- Six full (standard/extended identifier) acceptance filters, two associated with the high priority receive buffer, and four associated with the low priority receive buffer

- Two full acceptance filter masks, one each associated with the high and low priority receive buffers

- Three transmit buffers with application specified prioritization and abort capability (each buffer may contain up to 8 bytes of data)

- Programmable wake-up functionality with integrated low pass filter

- Programmable Loopback mode supports self-test operation

- Signaling via interrupt capabilities for all CAN receiver and transmitter error states

- Programmable clock source

- Programmable link to timer module for time-stamping and network synchronization

- Low-power Sleep and Idle mode

The CAN bus module consists of a protocol engine, and message buffering/control. The CAN protocol engine handles all functions for receiving and transmitting messages on the CAN bus. Messages are transmitted by first loading the appropriate data registers. Status and errors can be checked by reading the appropriate registers. Any message detected on the CAN bus is checked for errors and then matched against filters to see if it should be received and stored in one of the receive registers.

## 19.2 Frame Types

The CAN module transmits various types of frames, which include data messages or remote transmission requests initiated by the user as other frames that are automatically generated for control purposes. The following frame types are supported:

Standard Data Frame

A Standard Data Frame is generated by a node when the node wishes to transmit data. It includes an 11-bit Standard Identifier (SID) but not an 18-bit Extended Identifier (EID).

Extended Data Frame

An Extended Data Frame is similar to a Standard Data Frame, but includes an Extended Identifier as well.

Remote Frame

It is possible for a destination node to request the data from the source. For this purpose, the destination node sends a Remote Frame with an identifier that matches the identifier of the required Data Frame. The appropriate data source node will then send a Data Frame as a response to this remote request.

Error Frame

An Error Frame is generated by any node that detects a bus error. An error frame consists of two fields: an Error Flag field and an Error Delimiter field.

Overload Frame

An Overload Frame can be generated by a node as a result of 2 conditions. First, the node detects a dominant bit during Interframe Space, which is an illegal condition. Second, due to internal conditions, the node is not yet able to start reception of the next message. A node may generate a maximum of two sequential Overload Frames to delay the start of the next message.

• Interframe Space

Interframe Space separates a proceeding frame (of whatever type) from a following Data or Remote Frame.

## 20.8 ADC Acquisition Requirements

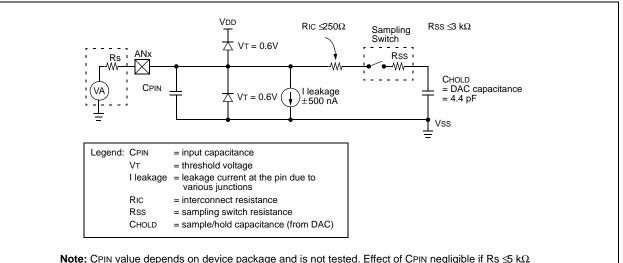

The analog input model of the 10-bit ADC is shown in Figure 20-3. The total sampling time for the ADC is a function of the internal amplifier settling time, device VDD and the holding capacitor charge time.

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the voltage level on the analog input pin. The analog output source impedance (Rs), the interconnect impedance (RIC), and the internal sampling switch (Rss) impedance combine to directly affect the time required to charge the capacitor CHOLD. The combined impedance must therefore be small enough to fully charge the holding capacitor within the chosen sample time. To minimize the effects of pin leakage currents on the accuracy of the ADC, the maximum recommended source impedance, Rs, is 5 k $\Omega$  for conversion rates up to 500 ksps and a maximum of  $500\Omega$  for conversion rates up to 1 Msps. After the analog input channel is selected (changed), this sampling function must be completed prior to starting the conversion. The internal holding capacitor will be in a discharged state prior to each sample operation.

The user must allow at least 1 TAD period of sampling time, TSAMP, between conversions to allow each sample to be acquired. This sample time may be controlled manually in software by setting/clearing the SAMP bit, or it may be automatically controlled by the ADC. In an automatic configuration, the user must allow enough time between conversion triggers so that the minimum sample time can be satisfied. Refer to Table 24-40 for TAD and sample time requirements.

#### FIGURE 20-3: ADC CONVERTER ANALOG INPUT MODEL

# 21.3.1.1 POR with Long Crystal Start-up Time (with FSCM Enabled)

The oscillator start-up circuitry is not linked to the POR circuitry. Some crystal circuits (especially low frequency crystals) will have a relatively long start-up time. Therefore, one or more of the following conditions is possible after the POR timer and the PWRT have expired:

- The oscillator circuit has not begun to oscillate.

- The Oscillator Start-up Timer has NOT expired (if a crystal oscillator is used).

- The PLL has not achieved a LOCK (if PLL is used).

If the FSCM is enabled and one of the above conditions is true, then a clock failure trap will occur. The device will automatically switch to the FRC oscillator and the user can switch to the desired crystal oscillator in the trap, ISR.

#### 21.3.1.2 Operating without FSCM and PWRT

If the FSCM is disabled and the Power-up Timer (PWRT) is also disabled, then the device will exit rapidly from Reset on power-up. If the clock source is FRC, LPRC, EXTRC or EC, it will be active immediately.

If the FSCM is disabled and the system clock has not started, the device will be in a frozen state at the Reset vector until the system clock starts. From the user's perspective, the device will appear to be in Reset until a system clock is available.

#### 21.3.2 BOR: PROGRAMMABLE BROWN-OUT RESET

The BOR (Brown-out Reset) module is based on an internal voltage reference circuit. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (i.e., missing portions of the AC cycle waveform due to bad power transmission lines or voltage sags due to excessive current draw when a large inductive load is turned on).

The BOR module allows selection of one of the following voltage trip points:

- 2.6V-2.71V

- 4.1V-4,4V

- 4.58V-4.73V

**Note:** The BOR voltage trip points indicated here are nominal values provided for design guidance only.

A BOR will generate a Reset pulse which will reset the device. The BOR will select the clock source, based on the Configuration bit values (FOS<2:0> and FPR<4:0>). Furthermore, if an oscillator mode is selected, the BOR will activate the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, then the clock will be held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the POR time-out (TPOR) and the PWRT time-out (TPWRT) will be applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, then a nominal delay of TFSCM =  $100 \ \mu s$  is applied. The total delay in this case is (TPOR + TFSCM).

The BOR Status bit (RCON<1>) will be set to indicate that a BOR has occurred. The BOR circuit, if enabled, will continue to operate while in Sleep or Idle modes and will reset the device should VDD fall below the BOR threshold voltage.

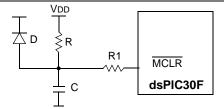

FIGURE 21-6:

#### EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: External Power-on Reset circuit is required only if the VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- 2: R should be suitably chosen so as to make sure that the voltage drop across R does not violate the device's electrical specification.

- 3: R1 should be suitably chosen so as to limit any current flowing into MCLR from external capacitor C, in the event of MCLR/VPP pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

Note: Dedicated supervisory devices, such as the MCP1XX and MCP8XX, may also be used as an external Power-on Reset circuit. Table 21-5 shows the Reset conditions for the RCON register. Since the control bits within the RCON register are R/W, the information in the table implies that all the bits are negated prior to the action specified in the condition column.

|                                        | 1                     |       | 1      |      |     |      |      |       |     |     |

|----------------------------------------|-----------------------|-------|--------|------|-----|------|------|-------|-----|-----|

| Condition                              | Program<br>Counter    | TRAPR | IOPUWR | EXTR | SWR | WDTO | IDLE | SLEEP | POR | BOR |

| Power-on Reset                         | 0x000000              | 0     | 0      | 0    | 0   | 0    | 0    | 0     | 1   | 1   |

| Brown-out Reset                        | 0x000000              | 0     | 0      | 0    | 0   | 0    | 0    | 0     | 0   | 1   |

| MCLR Reset during normal operation     | 0x000000              | 0     | 0      | 1    | 0   | 0    | 0    | 0     | 0   | 0   |

| Software Reset during normal operation | 0x000000              | 0     | 0      | 0    | 1   | 0    | 0    | 0     | 0   | 0   |

| MCLR Reset during Sleep                | 0x000000              | 0     | 0      | 1    | 0   | 0    | 0    | 1     | 0   | 0   |

| MCLR Reset during Idle                 | 0x000000              | 0     | 0      | 1    | 0   | 0    | 1    | 0     | 0   | 0   |

| WDT Time-out Reset                     | 0x000000              | 0     | 0      | 0    | 0   | 1    | 0    | 0     | 0   | 0   |

| WDT Wake-up                            | PC + 2                | 0     | 0      | 0    | 0   | 1    | 0    | 1     | 0   | 0   |

| Interrupt Wake-up from Sleep           | PC + 2 <sup>(1)</sup> | 0     | 0      | 0    | 0   | 0    | 0    | 1     | 0   | 0   |

| Clock Failure Trap                     | 0x000004              | 0     | 0      | 0    | 0   | 0    | 0    | 0     | 0   | 0   |

| Trap Reset                             | 0x000000              | 1     | 0      | 0    | 0   | 0    | 0    | 0     | 0   | 0   |

| Illegal Operation Trap                 | 0x000000              | 0     | 1      | 0    | 0   | 0    | 0    | 0     | 0   | 0   |

### TABLE 21-5: INITIALIZATION CONDITION FOR RCON REGISTER CASE 1

**Note 1:** When the wake-up is due to an enabled interrupt, the PC is loaded with the corresponding interrupt vector.

Table 21-6 shows a second example of the bit conditions for the RCON register. In this case, it is not assumed the user has set/cleared specific bits prior to action specified in the condition column.

#### TABLE 21-6: INITIALIZATION CONDITION FOR RCON REGISTER CASE 2

| Condition                              | Program<br>Counter    | TRAPR | IOPUWR | EXTR | SWR | WDTO | IDLE | SLEEP | POR | BOR |

|----------------------------------------|-----------------------|-------|--------|------|-----|------|------|-------|-----|-----|

| Power-on Reset                         | 0x000000              | 0     | 0      | 0    | 0   | 0    | 0    | 0     | 1   | 1   |

| Brown-out Reset                        | 0x000000              | u     | u      | u    | u   | u    | u    | u     | 0   | 1   |

| MCLR Reset during normal operation     | 0x000000              | u     | u      | 1    | 0   | 0    | 0    | 0     | u   | u   |

| Software Reset during normal operation | 0x000000              | u     | u      | 0    | 1   | 0    | 0    | 0     | u   | u   |

| MCLR Reset during Sleep                | 0x000000              | u     | u      | 1    | u   | 0    | 0    | 1     | u   | u   |

| MCLR Reset during Idle                 | 0x000000              | u     | u      | 1    | u   | 0    | 1    | 0     | u   | u   |

| WDT Time-out Reset                     | 0x000000              | u     | u      | 0    | 0   | 1    | 0    | 0     | u   | u   |

| WDT Wake-up                            | PC + 2                | u     | u      | u    | u   | 1    | u    | 1     | u   | u   |

| Interrupt Wake-up from<br>Sleep        | PC + 2 <sup>(1)</sup> | u     | u      | u    | u   | u    | u    | 1     | u   | u   |

| Clock Failure Trap                     | 0x000004              | u     | u      | u    | u   | u    | u    | u     | u   | u   |

| Trap Reset                             | 0x000000              | 1     | u      | u    | u   | u    | u    | u     | u   | u   |

| Illegal Operation Reset                | 0x000000              | u     | 1      | u    | u   | u    | u    | u     | u   | u   |

**Legend:** u = unchanged

**Note** 1: When the wake-up is due to an enabled interrupt, the PC is loaded with the corresponding interrupt vector.

#### 21.7 Peripheral Module Disable (PMD) Registers

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled via the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral will also be disabled so writes to those registers will have no effect and read values will be invalid.

A peripheral module will only be enabled if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

| Note: | If a PMD bit is set, the corresponding<br>module is disabled after a delay of 1<br>instruction cycle. Similarly, if a PMD bit is<br>cleared, the corresponding module is<br>enabled after a delay of 1 instruction cycle<br>(assuming the module control registers<br>are already configured to capable module |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | are already configured to enable module operation).                                                                                                                                                                                                                                                            |

## 21.8 In-Circuit Debugger

When MPLAB ICD 2 is selected as a debugger, the In-Circuit Debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. When the device has this feature enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins.

One of four pairs of Debug I/O pins may be selected by the user using configuration options in MPLAB IDE. These pin pairs are named EMUD/EMUC, EMUD1/ EMUC1, EMUD2/EMUC2 and EMUD3/EMUC3.

In each case, the selected EMUD pin is the Emulation/ Debug Data line, and the EMUC pin is the Emulation/ Debug Clock line. These pins will interface to the MPLAB ICD 2 module available from Microchip. The selected pair of Debug I/O pins is used by MPLAB ICD 2 to send commands and receive responses, as well as to send and receive data. To use the In-Circuit Debugger function of the device, the design must implement ICSP connections to MCLR, VDD, Vss, PGC, PGD and the selected EMUDx/EMUCx pin pair.

This gives rise to two possibilities:

- If EMUD/EMUC is selected as the debug I/O pin pair, then only a 5-pin interface is required, as the EMUD and EMUC pin functions are multiplexed with the PGD and PGC pin functions in all dsPIC30F devices.

- If EMUD1/EMUC1, EMUD2/EMUC2 or EMUD3/ EMUC3 is selected as the debug I/O pin pair, then a 7-pin interface is required, as the EMUDx/EMUCx pin functions (x = 1, 2 or 3) are not multiplexed with the PGD and PGC pin functions.

# dsPIC30F5015/5016

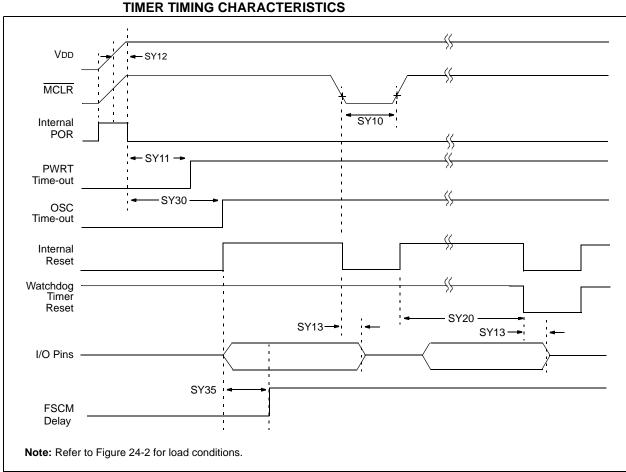

# FIGURE 24-5: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING CHARACTERISTICS

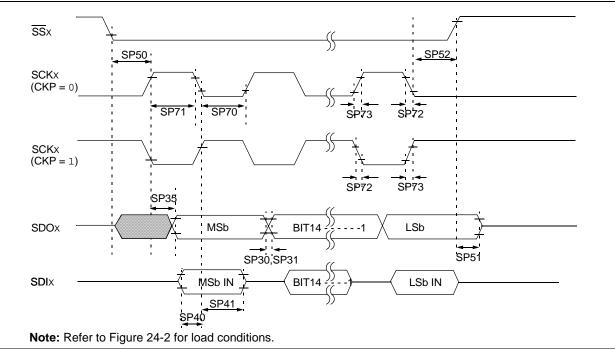

#### FIGURE 24-18: SPI MODULE SLAVE MODE (CKE = 0) TIMING CHARACTERISTICS

#### TABLE 24-35: SPI MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| АС СНА       | ARACTERIS                            | TICS                                                 | Standard Operating Conditions: 2.5V to 5.5V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |                    |     |       |                    |  |  |  |

|--------------|--------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|--------------------|--|--|--|

| Param<br>No. | Symbol Characteristic <sup>(1)</sup> |                                                      | Min                                                                                                                                                                                      | Тур <sup>(2)</sup> | Max | Units | Conditions         |  |  |  |

| SP70         | TscL                                 | SCKx Input Low Time                                  | 30                                                                                                                                                                                       | —                  |     | ns    | —                  |  |  |  |

| SP71         | TscH                                 | SCKx Input High Time                                 | 30                                                                                                                                                                                       | —                  |     | ns    | —                  |  |  |  |

| SP72         | TscF                                 | SCKx Input Fall Time <sup>(3)</sup>                  |                                                                                                                                                                                          | 10                 | 25  | ns    | —                  |  |  |  |

| SP73         | TscR                                 | SCKx Input Rise Time <sup>(3)</sup>                  |                                                                                                                                                                                          | 10                 | 25  | ns    | —                  |  |  |  |

| SP30         | TdoF                                 | SDOx Data Output Fall Time <sup>(3)</sup>            | —                                                                                                                                                                                        | —                  | _   | ns    | See parameter DO32 |  |  |  |

| SP31         | TdoR                                 | SDOx Data Output Rise Time <sup>(3)</sup>            | —                                                                                                                                                                                        | —                  | _   | ns    | See parameter DO31 |  |  |  |

| SP35         | TscH2doV,<br>TscL2doV                | SDOx Data Output Valid after<br>SCKx Edge            | —                                                                                                                                                                                        | —                  | 30  | ns    | —                  |  |  |  |

| SP40         | TdiV2scH,<br>TdiV2scL                | Setup Time of SDIx Data Input to SCKx Edge           | 20                                                                                                                                                                                       | —                  |     | ns    | —                  |  |  |  |

| SP41         | TscH2diL,<br>TscL2diL                | Hold Time of SDIx Data Input to SCKx Edge            | 20                                                                                                                                                                                       | _                  |     | ns    | —                  |  |  |  |

| SP50         | TssL2scH,<br>TssL2scL                | SSx↓to SCKx↑ or SCKx↓Input                           | 120                                                                                                                                                                                      | —                  |     | ns    | —                  |  |  |  |

| SP51         | TssH2doZ                             | SSx↑ to SDOx Output<br>High-Impedance <sup>(3)</sup> | 10                                                                                                                                                                                       | —                  | 50  | ns    | —                  |  |  |  |

| SP52         | TscH2ssH<br>TscL2ssH                 | SSx after SCK Edge                                   | 1.5 Tcy +40                                                                                                                                                                              | —                  | _   | ns    | —                  |  |  |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

3: Assumes 50 pF load on all SPI pins.

## TABLE 24-38: I<sup>2</sup>C<sup>™</sup> BUS DATA TIMING REQUIREMENTS (SLAVE MODE)

| AC CHA       | AC CHARACTERISTICS Standard Operating Conditions: 2.5V to 5.5V<br>(unless otherwise stated)<br>Operating temperature -40°C ≤TA ≤+85°C for Industrial<br>-40°C ≤TA ≤+125°C for Extended |                 |                           |             |      |       |                                             |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------------|-------------|------|-------|---------------------------------------------|--|--|--|

| Param<br>No. | Symbol Charac                                                                                                                                                                          |                 | teristic                  | Min         | Max  | Units | Conditions                                  |  |  |  |

| IS10         | TLO:SCL                                                                                                                                                                                | Clock Low Time  | 100 kHz mode              | 4.7         | —    | μs    | Device must operate at a minimum of 1.5 MHz |  |  |  |

|              |                                                                                                                                                                                        |                 | 400 kHz mode              | 1.3         | _    | μs    | Device must operate at a minimum of 10 MHz  |  |  |  |

|              |                                                                                                                                                                                        |                 | 1 MHz mode <sup>(1)</sup> | 0.5         | —    | μs    | —                                           |  |  |  |

| IS11         | THI:SCL                                                                                                                                                                                | Clock High Time | 100 kHz mode              | 4.0         | —    | μs    | Device must operate at a minimum of 1.5 MHz |  |  |  |

|              |                                                                                                                                                                                        |                 | 400 kHz mode              | 0.6         | —    | μs    | Device must operate at a minimum of 10 MHz  |  |  |  |

|              |                                                                                                                                                                                        |                 | 1 MHz mode <sup>(1)</sup> | 0.5         | —    | μs    | _                                           |  |  |  |

| IS20         | TF:SCL                                                                                                                                                                                 | SDA and SCL     | 100 kHz mode              |             | 300  | ns    | CB is specified to be from                  |  |  |  |

|              |                                                                                                                                                                                        | Fall Time       | 400 kHz mode              | 20 + 0.1 Св | 300  | ns    | 10 to 400 pF                                |  |  |  |

|              |                                                                                                                                                                                        |                 | 1 MHz mode <sup>(1)</sup> |             | 100  | ns    |                                             |  |  |  |

| IS21         | TR:SCL                                                                                                                                                                                 | SDA and SCL     | 100 kHz mode              | _           | 1000 | ns    | CB is specified to be from                  |  |  |  |

|              |                                                                                                                                                                                        | Rise Time       | 400 kHz mode              | 20 + 0.1 Св | 300  | ns    | 10 to 400 pF                                |  |  |  |

|              |                                                                                                                                                                                        |                 | 1 MHz mode <sup>(1)</sup> | _           | 300  | ns    |                                             |  |  |  |

| IS25         | TSU:DAT                                                                                                                                                                                | Data Input      | 100 kHz mode              | 250         |      | ns    | —                                           |  |  |  |

|              |                                                                                                                                                                                        | Setup Time      | 400 kHz mode              | 100         | —    | ns    |                                             |  |  |  |

|              |                                                                                                                                                                                        |                 | 1 MHz mode <sup>(1)</sup> | 100         | —    | ns    |                                             |  |  |  |

| IS26         | THD:DAT                                                                                                                                                                                | Data Input      | 100 kHz mode              | 0           | —    | ns    | —                                           |  |  |  |

|              |                                                                                                                                                                                        | Hold Time       | 400 kHz mode              | 0           | 0.9  | μs    |                                             |  |  |  |

|              |                                                                                                                                                                                        |                 | 1 MHz mode <sup>(1)</sup> | 0           | 0.3  | μs    |                                             |  |  |  |

| IS30         | TSU:STA                                                                                                                                                                                | Start Condition | 100 kHz mode              | 4.7         | —    | μs    | Only relevant for repeated                  |  |  |  |

|              |                                                                                                                                                                                        | Setup Time      | 400 kHz mode              | 0.6         | —    | μs    | Start condition                             |  |  |  |

|              |                                                                                                                                                                                        |                 | 1 MHz mode <sup>(1)</sup> | 0.25        | —    | μs    |                                             |  |  |  |

| IS31         | THD:STA                                                                                                                                                                                | Start Condition | 100 kHz mode              | 4.0         | —    | μs    | After this period, the first                |  |  |  |

|              |                                                                                                                                                                                        | Hold Time       | 400 kHz mode              | 0.6         | —    | μs    | clock pulse is generated                    |  |  |  |

|              |                                                                                                                                                                                        |                 | 1 MHz mode <sup>(1)</sup> | 0.25        | —    | μs    |                                             |  |  |  |

| IS33         | TSU:STO                                                                                                                                                                                | Stop Condition  | 100 kHz mode              | 4.7         | —    | μs    | —                                           |  |  |  |

|              |                                                                                                                                                                                        | Setup Time      | 400 kHz mode              | 0.6         | —    | μs    |                                             |  |  |  |

|              |                                                                                                                                                                                        |                 | 1 MHz mode <sup>(1)</sup> | 0.6         |      | μs    |                                             |  |  |  |

| IS34         | THD:STO                                                                                                                                                                                | Stop Condition  | 100 kHz mode              | 4000        | —    | ns    |                                             |  |  |  |

|              |                                                                                                                                                                                        | Hold Time       | 400 kHz mode              | 600         | —    | ns    |                                             |  |  |  |

|              |                                                                                                                                                                                        |                 | 1 MHz mode <sup>(1)</sup> | 250         |      | ns    |                                             |  |  |  |

| IS40         | TAA:SCL                                                                                                                                                                                | Output Valid    | 100 kHz mode              | 0           | 3500 | ns    |                                             |  |  |  |

|              |                                                                                                                                                                                        | From Clock      | 400 kHz mode              | 0           | 1000 | ns    |                                             |  |  |  |

|              |                                                                                                                                                                                        |                 | 1 MHz mode <sup>(1)</sup> | 0           | 350  | ns    |                                             |  |  |  |

| IS45         | TBF:SDA                                                                                                                                                                                | Bus Free Time   | 100 kHz mode              | 4.7         |      | μs    | Time the bus must be free                   |  |  |  |

|              |                                                                                                                                                                                        |                 | 400 kHz mode              | 1.3         |      | μs    | before a new transmissior                   |  |  |  |

|              |                                                                                                                                                                                        |                 | 1 MHz mode <sup>(1)</sup> | 0.5         | _    | μs    | can start                                   |  |  |  |

**Note 1:** Maximum pin capacitance = 10 pF for all I<sup>2</sup>C pins (for 1 MHz mode only).

| АС СНА           |               | STICS                                             | Standard Operating Conditions: 2.7V to 5.5V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |             |                                  |          |                                                                                   |  |  |  |

|------------------|---------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------------------|----------|-----------------------------------------------------------------------------------|--|--|--|

| Param<br>No.     | Symbol        | Characteristic                                    | Min.                                                                                                                                                                                     | Тур         | Max.                             | Units    | Conditions                                                                        |  |  |  |

|                  | Device Supply |                                                   |                                                                                                                                                                                          |             |                                  |          |                                                                                   |  |  |  |

| AD01             | AVdd          | Module VDD Supply                                 | Greater of<br>VDD – 0.3<br>or 2.7                                                                                                                                                        | _           | Lesser of<br>VDD + 0.3<br>or 5.5 | V        |                                                                                   |  |  |  |

| AD02             | AVss          | Module Vss Supply                                 | Vss - 0.3                                                                                                                                                                                |             | Vss + 0.3                        | V        |                                                                                   |  |  |  |

| Reference Inputs |               |                                                   |                                                                                                                                                                                          |             |                                  |          |                                                                                   |  |  |  |

| AD05             | Vrefh         | Reference Voltage High                            | AVss + 2.7                                                                                                                                                                               | _           | AVdd                             | V        |                                                                                   |  |  |  |

| AD06             | Vrefl         | Reference Voltage Low                             | AVss                                                                                                                                                                                     |             | AVDD - 2.7                       | V        |                                                                                   |  |  |  |

| AD07             | Vref          | Absolute Reference Voltage                        | AVss - 0.3                                                                                                                                                                               |             | AVDD + 0.3                       | V        |                                                                                   |  |  |  |

| AD08             | IREF          | Current Drain                                     | —                                                                                                                                                                                        | 200<br>.001 | 300<br>3                         | μΑ<br>μΑ | A/D operating<br>A/D off                                                          |  |  |  |

|                  |               |                                                   | Analog Ir                                                                                                                                                                                | nput        |                                  |          |                                                                                   |  |  |  |

| AD10             | VINH-VINL     | Full-Scale Input Span                             | Vrefl                                                                                                                                                                                    | _           | Vrefh                            | V        |                                                                                   |  |  |  |

| AD12             | —             | Leakage Current                                   | —                                                                                                                                                                                        | ±0.001      | ±0.244                           | μA       | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 5V<br>Source Impedance = 5 k $\Omega$ |  |  |  |

| AD13             | —             | Leakage Current                                   | _                                                                                                                                                                                        | ±0.001      | ±0.244                           | μA       | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3V<br>Source Impedance = 5 k $\Omega$ |  |  |  |

| AD17             | Rin           | Recommended Impedance<br>of Analog Voltage Source | —                                                                                                                                                                                        | _           | —                                | Ω        | See Table 20-2                                                                    |  |  |  |

|                  | 1             | 1                                                 | DC Accu                                                                                                                                                                                  |             |                                  |          |                                                                                   |  |  |  |

| AD20             | Nr            | Resolution                                        | 1                                                                                                                                                                                        | 0 data bi   | its                              | bits     | —                                                                                 |  |  |  |

| AD21             | INL           | Integral Nonlinearity <sup>(2)</sup>              | —                                                                                                                                                                                        | ±1          | ±1                               | LSb      | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 5V                                    |  |  |  |

| AD21A            | INL           | Integral Nonlinearity <sup>(2)</sup>              | —                                                                                                                                                                                        | ±1          | ±1                               | LSb      | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 3V                                    |  |  |  |

| AD22             | DNL           | Differential Nonlinearity <sup>(2)</sup>          | _                                                                                                                                                                                        | ±1          | ±1                               | LSb      | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 5V                                    |  |  |  |

| AD22A            | DNL           | Differential Nonlinearity <sup>(2)</sup>          | _                                                                                                                                                                                        | ±1          | ±1                               | LSb      | Vinl = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3V                                    |  |  |  |

| AD23             | Gerr          | Gain Error <sup>(2)</sup>                         | —                                                                                                                                                                                        | ±5          | ±6                               | LSb      | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 5V                                    |  |  |  |

| AD23A            | Gerr          | Gain Error <sup>(2)</sup>                         | —                                                                                                                                                                                        | ±5          | ±6                               | LSb      | Vinl = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3V                                    |  |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Measurements taken with external VREF+ and VREF- used as the ADC voltage references.

**3:** The A/D conversion result never decreases with an increase in the input voltage, and has no missing codes.

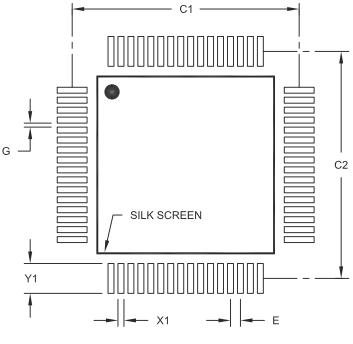

## 64-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                          | MILLIMETERS |          |       |      |  |

|--------------------------|-------------|----------|-------|------|--|

| Dimension                | MIN         | NOM      | MAX   |      |  |

| Contact Pitch            | E           | 0.50 BSC |       |      |  |

| Contact Pad Spacing      | C1          |          | 11.40 |      |  |

| Contact Pad Spacing      | C2          |          | 11.40 |      |  |

| Contact Pad Width (X64)  | X1          |          |       | 0.30 |  |

| Contact Pad Length (X64) | Y1          |          |       | 1.50 |  |

| Distance Between Pads    | G           | 0.20     |       |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2085A

## APPENDIX A: REVISION HISTORY

## Revision A (July 2005)

Original data sheet for dsPIC30F5015/5016 devices.

### **Revision B (September 2006)**

Revision B of this data sheet reflects these changes:

- Base instruction CP1 removed (see Table 22-2)

- Supported I<sup>2</sup>C Slave Addresses (see Table 17-1)

- ADC Conversion Clock selection (see Section 20.0 "10-bit High-Speed Analog-to-Digital Converter (ADC) Module")

- Revised Electrical Characteristics

- Operating current (IDD) specifications (see Table 24-6)

- Idle current (IIDLE) specifications (see Table 24-7)

- Power-down current (IPD) specifications (see Table 24-8)

- I/O Pin input specifications (see Table 24-9)

- BOR voltage limits (see Table 24-11)

- Watchdog Timer limits (see Table 24-21)

## **Revision C (January 2007)**

This revision includes updates to the packaging diagram.

#### **Revision D (March 2008)**

This revision reflects these updates:

- Changed the location of the input reference in the 10-bit High-Speed ADC Functional Block Diagram (see Figure 20-1)

- Added FUSE Configuration Register (FICD) details (see Section 21.6 "Device Configuration Registers" and Table 21-8)

- Added Note 2 in Device Configuration Registers table (Table 21-8)

- Removed erroneous statement regarding generation of CAN receive errors (see Section 19.4.5 "Receive Errors")

- Electrical Specifications:

- Resolved TBD values for parameters DO10, DO16, DO20, and DO26 (see Table 24-10)

- 10-bit High-Speed ADC tPDU timing parameter (time to stabilize) has been updated from 20 µs typical to 20 µs maximum (see Table 24-41)

- Parameter OS65 (Internal RC Accuracy) has been expanded to reflect multiple Min and Max values for different temperatures (see Table 24-19)

- Parameter DC12 (RAM Data Retention Voltage) Min and Max values have been updated (see Table 24-5)

- Parameter D134 (Erase/Write Cycle Time) has been updated to include Min and Max values and the Typ value has been removed (see Table 24-12)

- Removed parameters OS62 (Internal FRC Jitter) and OS64 (Internal FRC Drift) and Note 2 from AC Characteristics (see Table 24-18)

- Parameter OS63 (Internal FRC Accuracy) has been expanded to reflect multiple Min and Max values for different temperatures (see Table 24-18)

- Updated Min and Max values and Conditions for parameter SY11 and updated Min, Typ, and Max values and Conditions for parameter SY20 (see Table 24-21)

- Removed dsPIC30F6010 device reference from the third paragraph of **Section 7.0 "Data EEPROM Memory"**

- Removed IC5 and IC6 pin references from the 64-pin TQFP pin diagram (see "Pin Diagram") and Figure 1-1

- Changed Interrupt Vectors 40-43 to Reserved (see Table 5-1)

- Updated PMD2 SFR bits 15-12 and 7-4 are unimplemented (see Table 21-7)

- Additional minor corrections throughout the document

## **READER RESPONSE**