Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFL

| Detalls                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | C1665V2                                                                          |

| Core Size                  | 16/32-Bit                                                                        |

| Speed                      | 80MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI             |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                  |

| Number of I/O              | 75                                                                               |

| Program Memory Size        | 448KB (448K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 50K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                        |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-LQFP Exposed Pad                                                             |

| Supplier Device Package    | PG-LQFP-100-8                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc2361a56f80laakxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Edition 2014-06 Published by Infineon Technologies AG 81726 Munich, Germany © 2014 Infineon Technologies AG All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

| XC236xA                    |                                                        |  |  |  |  |

|----------------------------|--------------------------------------------------------|--|--|--|--|

| -                          | listory: V2.12, 2014-06                                |  |  |  |  |

|                            | Previous Version(s):                                   |  |  |  |  |

| V2.11, 201                 |                                                        |  |  |  |  |

| V2.1, 2011-                |                                                        |  |  |  |  |

| V2.0, 2009-                |                                                        |  |  |  |  |

| V1.31, 2008<br>V1.3, 2008- |                                                        |  |  |  |  |

| V1.3, 2008-<br>V1.2, 2008- |                                                        |  |  |  |  |

| ,                          | 09<br>06 Preliminary                                   |  |  |  |  |

|                            | 06 (Intermediate version)                              |  |  |  |  |

| Page                       | Subjects (major changes since last revisions)          |  |  |  |  |

| V2.0 to V2.                | 1                                                      |  |  |  |  |

| 38                         | ID registers added                                     |  |  |  |  |

| 85                         | ADC capacitances corrected (typ. vs. max.)             |  |  |  |  |

| 89                         | Conditions relaxed for $\Delta f_{INT}$                |  |  |  |  |

|                            | Range for $f_{WU}$ adapted according to PCN 2010-013-A |  |  |  |  |

|                            | Added startup time from power-on $t_{SPO}$             |  |  |  |  |

| 126                        | Quality declarations added                             |  |  |  |  |

| V2.1 to V2.                | 11                                                     |  |  |  |  |

| 14f, 123f                  | 14f, 123f Wrong package information (LQFP-144) removed |  |  |  |  |

| V2.11 to V2.12             |                                                        |  |  |  |  |

| 9                          | Basic device types replaced                            |  |  |  |  |

| 10                         | Special device types added                             |  |  |  |  |

| 14                         | Logic symbol corrected                                 |  |  |  |  |

| 123                        | Package type added                                     |  |  |  |  |

### Trademarks

C166<sup>™</sup>, TriCore<sup>™</sup>, and DAVE<sup>™</sup> are trademarks of Infineon Technologies AG.

### We Listen to Your Comments

Is there any information in this document that you feel is wrong, unclear or missing? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

### **Table of Contents**

| Flash Memory Parameters       92         AC Parameters       94         Testing Waveforms       94         Definition of Internal Timing       95         Phase Locked Loop (PLL)       96         Wakeup Clock       99         Selecting and Changing the Operating Frequency       99         External Clock Input Parameters       100         Pad Properties       102         External Bus Timing       105         Bus Cycle Control with the READY Input       111         Synchronous Serial Interface Timing       113 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Debug Interface Timing 117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Package and Reliability123Packaging123Thermal Considerations125Quality Declarations126                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

#### **General Device Information**

## 2.1 Pin Configuration and Definition

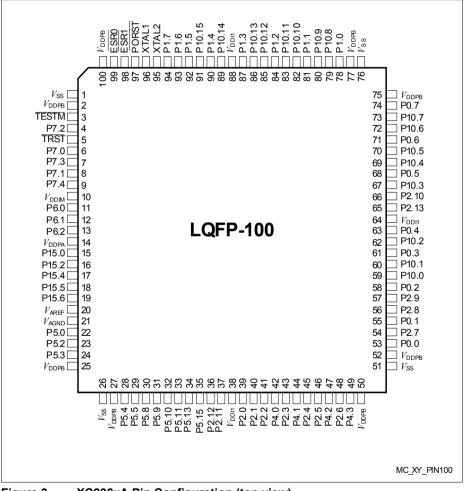

The pins of the XC236xA are described in detail in **Table 6**, which includes all alternate functions. For further explanations please refer to the footnotes at the end of the table. The following figure summarizes all pins, showing their locations on the four sides of the package.

Figure 3 XC236xA Pin Configuration (top view)

### **General Device Information**

| Table 6         Pin Definitions and Functions (cont'd) |                   |       |      |                                                   |  |  |

|--------------------------------------------------------|-------------------|-------|------|---------------------------------------------------|--|--|

| Pin                                                    | Symbol            | Ctrl. | Туре | Function                                          |  |  |

| 18                                                     | P15.5             | I     | In/A | Bit 5 of Port 15, General Purpose Input           |  |  |

|                                                        | ADC1_CH5          | I     | In/A | Analog Input Channel 5 for ADC1                   |  |  |

|                                                        | T6EUDA            | I     | In/A | GPT12E Timer T6 External Up/Down Control<br>Input |  |  |

| 19                                                     | P15.6             | I     | In/A | Bit 6 of Port 15, General Purpose Input           |  |  |

|                                                        | ADC1_CH6          | I     | In/A | Analog Input Channel 6 for ADC1                   |  |  |

| 20                                                     | V <sub>AREF</sub> | -     | PS/A | Reference Voltage for A/D Converters ADC0/1       |  |  |

| 21                                                     | V <sub>AGND</sub> | -     | PS/A | Reference Ground for A/D Converters ADC0/1        |  |  |

| 22                                                     | P5.0              | I     | In/A | Bit 0 of Port 5, General Purpose Input            |  |  |

|                                                        | ADC0_CH0          | I     | In/A | Analog Input Channel 0 for ADC0                   |  |  |

| 23                                                     | P5.2              | I     | In/A | Bit 2 of Port 5, General Purpose Input            |  |  |

|                                                        | ADC0_CH2          | I     | In/A | Analog Input Channel 2 for ADC0                   |  |  |

|                                                        | TDI_A             | I     | In/A | JTAG Test Data Input                              |  |  |

| 24                                                     | P5.3              | I     | In/A | Bit 3 of Port 5, General Purpose Input            |  |  |

|                                                        | ADC0_CH3          | I     | In/A | Analog Input Channel 3 for ADC0                   |  |  |

|                                                        | T3INA             | I     | In/A | GPT12E Timer T3 Count/Gate Input                  |  |  |

| 28                                                     | P5.4              | I     | In/A | Bit 4 of Port 5, General Purpose Input            |  |  |

|                                                        | ADC0_CH4          | I     | In/A | Analog Input Channel 4 for ADC0                   |  |  |

|                                                        | T3EUDA            | I     | In/A | GPT12E Timer T3 External Up/Down Control<br>Input |  |  |

|                                                        | TMS_A             | I     | In/A | JTAG Test Mode Selection Input                    |  |  |

| 29                                                     | P5.5              | I     | In/A | Bit 5 of Port 5, General Purpose Input            |  |  |

|                                                        | ADC0_CH5          | I     | In/A | Analog Input Channel 5 for ADC0                   |  |  |

|                                                        | CCU60_T12<br>HRB  | I     | In/A | External Run Control Input for T12 of CCU60       |  |  |

### XC2361A, XC2363A, XC2364A, XC2365A XC2000 Family / Base Line

### **General Device Information**

| Table            | Table 6Pin Definitions and Functions (cont'd) |        |      |                                                                                                                                                                                                                                                                                   |  |  |  |

|------------------|-----------------------------------------------|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin              | Symbol                                        | Ctrl.  | Туре | Function                                                                                                                                                                                                                                                                          |  |  |  |

| 98               | ESR1                                          | 00 / I | St/B | External Service Request 1<br>After power-up, an internal weak pull-up device<br>holds this pin high when nothing is driving it.                                                                                                                                                  |  |  |  |

|                  | RxDC0E                                        | I      | St/B | CAN Node 0 Receive Data Input                                                                                                                                                                                                                                                     |  |  |  |

|                  | U1C0_DX0F                                     | I      | St/B | USIC1 Channel 0 Shift Data Input                                                                                                                                                                                                                                                  |  |  |  |

|                  | U1C0_DX2C                                     | I      | St/B | USIC1 Channel 0 Shift Control Input                                                                                                                                                                                                                                               |  |  |  |

|                  | U1C1_DX0C                                     | I      | St/B | USIC1 Channel 1 Shift Data Input                                                                                                                                                                                                                                                  |  |  |  |

|                  | U1C1_DX2B                                     | I      | St/B | USIC1 Channel 1 Shift Control Input                                                                                                                                                                                                                                               |  |  |  |

|                  | U2C1_DX2C                                     | I      | St/B | USIC2 Channel 1 Shift Control Input                                                                                                                                                                                                                                               |  |  |  |

| 99               | ESR0                                          | O0 / I | St/B | <b>External Service Request 0</b><br>After power-up, ESR0 operates as open-drain<br>bidirectional reset with a weak pull-up.                                                                                                                                                      |  |  |  |

|                  | U1C0_DX0E                                     | I      | St/B | USIC1 Channel 0 Shift Data Input                                                                                                                                                                                                                                                  |  |  |  |

|                  | U1C0_DX2B                                     | I      | St/B | USIC1 Channel 0 Shift Control Input                                                                                                                                                                                                                                               |  |  |  |

| 10               | V <sub>DDIM</sub>                             | -      | PS/M | <b>Digital Core Supply Voltage for Domain M</b><br>Decouple with a ceramic capacitor, see Data<br>Sheet for details.                                                                                                                                                              |  |  |  |

| 38,<br>64,<br>88 | V <sub>DDI1</sub>                             | -      | PS/1 | <b>Digital Core Supply Voltage for Domain 1</b><br>Decouple with a ceramic capacitor, see Data<br>Sheet for details.<br>All $V_{\text{DDI1}}$ pins must be connected to each other.                                                                                               |  |  |  |

| 14               | V <sub>DDPA</sub>                             | -      | PS/A | <b>Digital Pad Supply Voltage for Domain A</b><br>Connect decoupling capacitors to adjacent<br>$V_{\text{DDP}}/V_{\text{SS}}$ pin pairs as close as possible to the pins.<br>Note: The A/D_Converters and ports P5, P6 and<br>P15 are fed from supply voltage $V_{\text{DDPA}}$ . |  |  |  |

With this hardware most XC236xA instructions are executed in a single machine cycle of 12.5 ns with an 80-MHz CPU clock. For example, shift and rotate instructions are always processed during one machine cycle, no matter how many bits are shifted. Also, multiplication and most MAC instructions execute in one cycle. All multiple-cycle instructions have been optimized so that they can be executed very fast; for example, a 32-/16-bit division is started within 4 cycles while the remaining cycles are executed in the background. Another pipeline optimization, the branch target prediction, eliminates the execution time of branch instructions if the prediction was correct.

The CPU has a register context consisting of up to three register banks with 16 wordwide GPRs each at its disposal. One of these register banks is physically allocated within the on-chip DPRAM area. A Context Pointer (CP) register determines the base address of the active register bank accessed by the CPU at any time. The number of these register bank copies is only restricted by the available internal RAM space. For easy parameter passing, a register bank may overlap others.

A system stack of up to 32 Kwords is provided for storage of temporary data. The system stack can be allocated to any location within the address space (preferably in the on-chip RAM area); it is accessed by the CPU with the stack pointer (SP) register. Two separate SFRs, STKOV and STKUN, are implicitly compared with the stack pointer value during each stack access to detect stack overflow or underflow.

The high performance of the CPU hardware implementation can be best utilized by the programmer with the highly efficient XC236xA instruction set. This includes the following instruction classes:

- Standard Arithmetic Instructions

- DSP-Oriented Arithmetic Instructions

- Logical Instructions

- Boolean Bit Manipulation Instructions

- Compare and Loop Control Instructions

- Shift and Rotate Instructions

- Prioritize Instruction

- Data Movement Instructions

- System Stack Instructions

- Jump and Call Instructions

- Return Instructions

- System Control Instructions

- Miscellaneous Instructions

The basic instruction length is either 2 or 4 bytes. Possible operand types are bits, bytes and words. A variety of direct, indirect or immediate addressing modes are provided to specify the required operands.

## 3.8 Capture/Compare Unit (CAPCOM2)

The CAPCOM2 unit supports generation and control of timing sequences on up to 16 channels with a maximum resolution of one system clock cycle (eight cycles in staggered mode). The CAPCOM2 unit is typically used to handle high-speed I/O tasks such as pulse and waveform generation, pulse width modulation (PWM), digital to analog (D/A) conversion, software timing, or time recording with respect to external events.

Two 16-bit timers (T7/T8) with reload registers provide two independent time bases for the capture/compare register array.

The input clock for the timers is programmable to several prescaled values of the internal system clock, or may be derived from an overflow/underflow of timer T6 in module GPT2. This provides a wide range or variation for the timer period and resolution and allows precise adjustments to the application-specific requirements. In addition, an external count input allows event scheduling for the capture/compare registers relative to external events.

The capture/compare register array contains 16 dual purpose capture/compare registers, each of which may be individually allocated to either CAPCOM timer and programmed for capture or compare function.

All registers have each one port pin associated with it which serves as an input pin for triggering the capture function, or as an output pin to indicate the occurrence of a compare event.

When a capture/compare register has been selected for capture mode, the current contents of the allocated timer will be latched ('captured') into the capture/compare register in response to an external event at the port pin which is associated with this register. In addition, a specific interrupt request for this capture/compare register is generated. Either a positive, a negative, or both a positive and a negative external signal transition at the pin can be selected as the triggering event.

The contents of all registers which have been selected for one of the five compare modes are continuously compared with the contents of the allocated timers.

When a match occurs between the timer value and the value in a capture/compare register, specific actions will be taken based on the selected compare mode.

| Compare Modes | Function                                                                                   |

|---------------|--------------------------------------------------------------------------------------------|

| Mode 0        | Interrupt-only compare mode;<br>Several compare interrupts per timer period are possible   |

| Mode 1        | Pin toggles on each compare match;<br>Several compare events per timer period are possible |

Table 9 Compare Modes

| Compare Modes           | Function                                                                                                                        |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Mode 2                  | Interrupt-only compare mode;<br>Only one compare interrupt per timer period is generated                                        |

| Mode 3                  | Pin set '1' on match; pin reset '0' on compare timer overflow;<br>Only one compare event per timer period is generated          |

| Double Register<br>Mode | Two registers operate on one pin;<br>Pin toggles on each compare match;<br>Several compare events per timer period are possible |

| Single Event Mode       | Generates single edges or pulses;<br>Can be used with any compare mode                                                          |

### Table 9 Compare Modes (cont'd)

With its maximum resolution of 2 system clock cycles, the **GPT2 module** provides precise event control and time measurement. It includes two timers (T5, T6) and a capture/reload register (CAPREL). Both timers can be clocked with an input clock which is derived from the CPU clock via a programmable prescaler or with external signals. The counting direction (up/down) for each timer can be programmed by software or altered dynamically with an external signal on a port pin (TxEUD<sup>1</sup>). Concatenation of the timers is supported with the output toggle latch (T6OTL) of timer T6, which changes its state on each timer overflow/underflow.

The state of this latch may be used to clock timer T5, and/or it may be output on pin T6OUT. The overflows/underflows of timer T6 can also be used to clock the CAPCOM2 timers and to initiate a reload from the CAPREL register.

The CAPREL register can capture the contents of timer T5 based on an external signal transition on the corresponding port pin (CAPIN); timer T5 may optionally be cleared after the capture procedure. This allows the XC236xA to measure absolute time differences or to perform pulse multiplication without software overhead.

The capture trigger (timer T5 to CAPREL) can also be generated upon transitions of GPT1 timer T3 inputs T3IN and/or T3EUD. This is especially advantageous when T3 operates in Incremental Interface Mode.

<sup>1)</sup> Exception: T5EUD is not connected to a pin.

### 4.1.3 Pad Timing Definition

If not otherwise noted, all timing parameters are tested and are valid for the corresponding output pins operating in strong driver, fast edge mode. See also "Pad Properties" on Page 102.

### 4.1.4 Parameter Interpretation

The parameters listed in the following include both the characteristics of the XC236xA and its demands on the system. To aid in correctly interpreting the parameters when evaluating them for a design, they are marked accordingly in the column "Symbol":

**CC** (Controller Characteristics):

The logic of the XC236xA provides signals with the specified characteristics.

#### SR (System Requirement):

The external system must provide signals with the specified characteristics to the XC236xA.

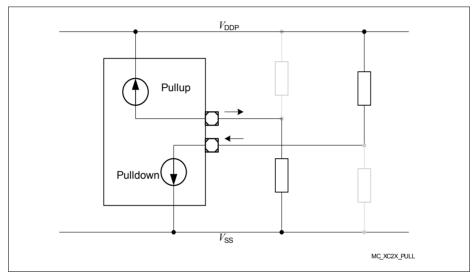

#### Pullup/Pulldown Device Behavior

Most pins of the XC236xA feature pullup or pulldown devices. For some special pins these are fixed; for the port pins they can be selected by the application.

The specified current values indicate how to load the respective pin depending on the intended signal level. **Figure 13** shows the current paths.

The shaded resistors shown in the figure may be required to compensate system pull currents that do not match the given limit values.

Figure 13 Pullup/Pulldown Current Definition

### XC2361A, XC2363A, XC2364A, XC2365A XC2000 Family / Base Line

#### **Electrical Parameters**

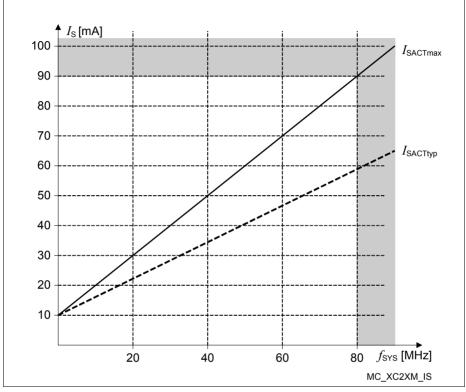

Figure 14Supply Current in Active Mode as a Function of FrequencyNote: Operating Conditions apply.

### 4.4 System Parameters

The following parameters specify several aspects which are important when integrating the XC236xA into an application system.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

| Parameter                                                             | Symbol                 | Values                                  |                 |                                            | Unit | Note /                               |

|-----------------------------------------------------------------------|------------------------|-----------------------------------------|-----------------|--------------------------------------------|------|--------------------------------------|

|                                                                       |                        | Min.                                    | Тур.            | Max.                                       | 1    | Test Condition                       |

| Short-term deviation of internal clock source frequency <sup>1)</sup> | ∆f <sub>INT</sub> CC   | -1                                      | _               | 1                                          | %    | ⊿ <i>T</i> <sub>J</sub> ≤ 10 °C      |

| Internal clock source frequency                                       | $f_{\rm INT}$ CC       | 4.8                                     | 5.0             | 5.2                                        | MHz  |                                      |

| Wakeup clock source                                                   | $f_{\rm WU}$ CC        | 400                                     | -               | 700                                        | kHz  | FREQSEL= 00                          |

| frequency <sup>2)</sup>                                               |                        | 210                                     | -               | 390                                        | kHz  | FREQSEL= 01                          |

|                                                                       |                        | 140                                     | -               | 260                                        | kHz  | FREQSEL= 10                          |

|                                                                       |                        | 110                                     | -               | 200                                        | kHz  | FREQSEL= 11                          |

| Startup time from power-<br>on with code execution<br>from Flash      | t <sub>SPO</sub> CC    | 1.8                                     | 2.2             | 2.7                                        | ms   | $f_{ m WU}$ = 500 kHz                |

| Startup time from stopover mode with code execution from PSRAM        | t <sub>SSO</sub> CC    | 11 /<br>f <sub>WU</sub> <sup>3)</sup>   | _               | 12 /<br>f <sub>WU</sub> <sup>3)</sup>      | μS   |                                      |

| Core voltage (PVC) supervision level                                  | V <sub>PVC</sub> CC    | V <sub>LV</sub><br>- 0.03               | V <sub>LV</sub> | V <sub>LV</sub><br>+ 0.07<br><sub>4)</sub> | V    | 5)                                   |

| Supply watchdog (SWD) supervision level                               | V <sub>SWD</sub><br>CC | V <sub>LV</sub><br>- 0.10 <sup>6)</sup> | $V_{\rm LV}$    | V <sub>LV</sub><br>+ 0.15                  | V    | Lower voltage range <sup>5)</sup>    |

|                                                                       |                        | V <sub>LV</sub><br>- 0.15               | V <sub>LV</sub> | V <sub>LV</sub><br>+ 0.15                  | V    | Upper voltage<br>range <sup>5)</sup> |

#### Table 20 Various System Parameters

The short-term frequency deviation refers to a timeframe of a few hours and is measured relative to the current frequency at the beginning of the respective timeframe. This parameter is useful to determine a time span for re-triggering a LIN synchronization.

This parameter is tested for the fastest and the slowest selection. The medium selections are not subject to production test - verified by design/characterization

| Coding of bit fields LEVX | baing of bit fields LEVXV in Register SWDCONU (cont d)                                                                |  |  |  |  |  |  |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Default Voltage Level     | I Notes <sup>1)</sup>                                                                                                 |  |  |  |  |  |  |

| 4.5 V                     | LEV2V: no request                                                                                                     |  |  |  |  |  |  |

| 4.6 V                     |                                                                                                                       |  |  |  |  |  |  |

| 4.7 V                     |                                                                                                                       |  |  |  |  |  |  |

| 4.8 V                     |                                                                                                                       |  |  |  |  |  |  |

| 4.9 V                     |                                                                                                                       |  |  |  |  |  |  |

| 5.0 V                     |                                                                                                                       |  |  |  |  |  |  |

| 5.5 V                     |                                                                                                                       |  |  |  |  |  |  |

|                           | Default Voltage Level           4.5 V           4.6 V           4.7 V           4.8 V           4.9 V           5.0 V |  |  |  |  |  |  |

### Table 21 Coding of bit fields LEVxV in Register SWDCON0 (cont'd)

1) The indicated default levels are selected automatically after a power reset.

#### Table 22 Coding of Bitfields LEVxV in Registers PVCyCONz

| Code             | Default Voltage Level | Notes <sup>1)</sup>                    |

|------------------|-----------------------|----------------------------------------|

| 000 <sub>B</sub> | 0.95 V                |                                        |

| 001 <sub>B</sub> | 1.05 V                |                                        |

| 010 <sub>B</sub> | 1.15 V                |                                        |

| 011 <sub>B</sub> | 1.25 V                |                                        |

| 100 <sub>B</sub> | 1.35 V                | LEV1V: reset request                   |

| 101 <sub>B</sub> | 1.45 V                | LEV2V: interrupt request <sup>2)</sup> |

| 110 <sub>B</sub> | 1.55 V                |                                        |

| 111 <sub>B</sub> | 1.65 V                |                                        |

1) The indicated default levels are selected automatically after a power reset.

2) Due to variations of the tolerance of both the Embedded Voltage Regulators (EVR) and the PVC levels, this interrupt can be triggered inadvertently, even though the core voltage is within the normal range. It is, therefore, recommended not to use the this warning level.

## 4.6 AC Parameters

These parameters describe the dynamic behavior of the XC236xA.

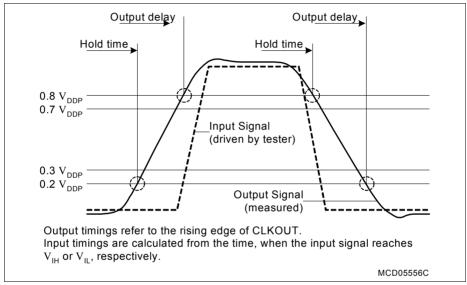

### 4.6.1 Testing Waveforms

These values are used for characterization and production testing (except pin XTAL1).

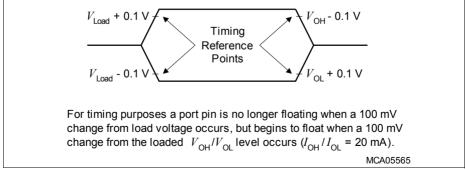

Figure 17 Input Output Waveforms

## 4.6.4 Pad Properties

The output pad drivers of the XC236xA can operate in several user-selectable modes. Strong driver mode allows controlling external components requiring higher currents such as power bridges or LEDs. Reducing the driving power of an output pad reduces electromagnetic emissions (EME). In strong driver mode, selecting a slower edge reduces EME.

The dynamic behavior, i.e. the rise time and fall time, depends on the applied external capacitance that must be charged and discharged. Timing values are given for a capacitance of 20 pF, unless otherwise noted.

In general, the performance of a pad driver depends on the available supply voltage  $V_{\text{DDP}}$ . The following table lists the pad parameters.

- Note: These parameters are not subject to production test but verified by design and/or characterization.

- Note: Operating Conditions apply.

Table 27 is valid under the following conditions:

$V_{\text{DDP}} \ge 3.0 \text{ V}; V_{\text{DDPtyp}} = 3.3 \text{ V}; V_{\text{DDP}} \le 4.5 \text{ V}; C_{\text{L}} \ge 20 \text{ pF}; C_{\text{L}} \le 100 \text{ pF};$

| Table 27 Standard Pad Parameters for Lower Voltage Range |

|----------------------------------------------------------|

|----------------------------------------------------------|

| Parameter                              | Symbol             | Values |      |                                          | Unit | Note /                        |

|----------------------------------------|--------------------|--------|------|------------------------------------------|------|-------------------------------|

|                                        |                    | Min.   | Тур. | Max.                                     |      | Test Condition                |

| Maximum output driver                  | I <sub>Omax</sub>  | -      | -    | 10                                       | mA   | Strong driver                 |

| current (absolute value) <sup>1)</sup> | CC                 | -      | -    | 2.5                                      | mA   | Medium driver                 |

|                                        |                    | -      | -    | 0.5                                      | mA   | Weak driver                   |

| Nominal output driver                  | I <sub>Onom</sub>  | -      | -    | 2.5                                      | mA   | Strong driver                 |

| current (absolute value)               | CC                 | -      | -    | 1.0                                      | mA   | Medium driver                 |

|                                        |                    | -      | -    | 0.1                                      | mA   | Weak driver                   |

| Rise and Fall times (10% -<br>90%)     | t <sub>RF</sub> CC | -      | -    | 6.2 +<br>0.24 x<br><i>C</i> <sub>L</sub> | ns   | Strong driver;<br>Sharp edge  |

|                                        |                    | -      | -    | 24 +<br>0.3 x<br><i>C</i> L              | ns   | Strong driver;<br>Medium edge |

|                                        |                    | -      | -    | 34 +<br>0.3 x<br>C <sub>L</sub>          | ns   | Strong driver;<br>Slow edge   |

|                                        |                    | _      | -    | 37 +<br>0.65 x<br><i>C</i> <sub>L</sub>  | ns   | Medium driver                 |

|                                        |                    | -      | -    | 500 +<br>2.5 x<br><i>C</i> <sub>L</sub>  | ns   | Weak driver                   |

The total output current that may be drawn at a given time must be limited to protect the supply rails from damage. For any group of 16 neighboring output pins, the total output current in each direction (ΣI<sub>OL</sub> and Σ-I<sub>OH</sub>) must remain below 50 mA.

| Parameter                                         | Symbol                    | Values           |      |      | Unit | Note /                 |

|---------------------------------------------------|---------------------------|------------------|------|------|------|------------------------|

|                                                   |                           | Min.             | Тур. | Max. |      | Test Condition         |

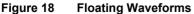

| DAP0 clock period                                 | <i>t</i> <sub>11</sub> SR | 25 <sup>1)</sup> | -    | -    | ns   |                        |

| DAP0 high time                                    | t <sub>12</sub> SR        | 8                | -    | -    | ns   |                        |

| DAP0 low time                                     | t <sub>13</sub> SR        | 8                | -    | -    | ns   |                        |

| DAP0 clock rise time                              | t <sub>14</sub> SR        | -                | -    | 4    | ns   |                        |

| DAP0 clock fall time                              | t <sub>15</sub> SR        | -                | -    | 4    | ns   |                        |

| DAP1 setup to DAP0<br>rising edge                 | <i>t</i> <sub>16</sub> SR | 6                | -    | -    | ns   | pad_type= stan<br>dard |

| DAP1 hold after DAP0 rising edge                  | <i>t</i> <sub>17</sub> SR | 6                | -    | -    | ns   | pad_type= stan<br>dard |

| DAP1 valid per DAP0<br>clock period <sup>2)</sup> | <i>t</i> <sub>19</sub> CC | 12               | 17   | -    | ns   | pad_type= stan<br>dard |

### Table 37 DAP Interface Timing for Lower Voltage Range

1) The debug interface cannot operate faster than the overall system, therefore  $t_{11} \ge t_{SYS}$ .

2) The Host has to find a suitable sampling point by analyzing the sync telegram response.

Figure 27 Test Clock Timing (DAP0)

#### Package and Reliability

# 5 Package and Reliability

The XC2000 Family devices use the package type PG-LQFP (Plastic Green - Low Profile Quad Flat Package). The following specifications must be regarded to ensure proper integration of the XC236xA in its target environment.

### 5.1 Packaging

These parameters specify the packaging rather than the silicon.

| Parameter                              | Symbol           | Lin  | nit Values | Unit | Notes                         |

|----------------------------------------|------------------|------|------------|------|-------------------------------|

|                                        |                  | Min. | Max.       |      |                               |

| Exposed Pad Dimension                  | $E x \times E y$ | -    | 6.2 × 6.2  | mm   | -                             |

| Power Dissipation                      | $P_{DISS}$       | -    | 1.0        | W    | -                             |

| Thermal resistance<br>Junction-Ambient | R <sub>OJA</sub> | -    | 47         | K/W  | No thermal via <sup>1)</sup>  |

|                                        |                  |      | 29         | K/W  | 4-layer, no pad <sup>2)</sup> |

|                                        |                  |      | 23         | K/W  | 4-layer, pad <sup>3)</sup>    |

#### Table 40 Package Parameters (PG-LQFP-100-8/-15)

Device mounted on a 2-layer JEDEC board (according to JESD 51-3) or a 4-layer board without thermal vias; exposed pad not soldered.

Device mounted on a 4-layer JEDEC board (according to JESD 51-7) with thermal vias; exposed pad not soldered.

Device mounted on a 4-layer JEDEC board (according to JESD 51-7) with thermal vias; exposed pad soldered to the board.

Note: To improve the EMC behavior, it is recommended to connect the exposed pad to the board ground, independent of the thermal requirements. Board layout examples are given in an application note.

### Package Compatibility Considerations

The XC236xA is a member of the XC2000 Family of microcontrollers. It is also compatible to a certain extent with members of similar families or subfamilies.

Each package is optimized for the device it houses. Therefore, there may be slight differences between packages of the same pin-count but for different device types. In particular, the size of the Exposed Pad (if present) may vary.

If different device types are considered or planned for an application, it must be ensured that the board layout fits all packages under consideration.