Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Core ProcessorC166SV2Core Size16/32-BitSpeed100MHzConnectivityCANbus, EBI/EMI, I²C, LINbus, SPI, SSC, UART/USART, USIPeripheralsI²S, POR, PWM, WDTNumber of I/O75Program Memory Size832KB (832K x 8)Program Memory TypeFLASHEEPROM Size-RAM SizeSOK x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.SVData ConvertersA/D 16x10bOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case100-LQFP Exposed PadSurface MountNot To Man | Detalls                    |                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------------------------------------------------------------|

| Core Size16/32-BitSpeed100MHzConnectivityCANbus, EBI/EMI, I²C, LINbus, SPI, SSC, UART/USART, USIPeripheralsI²S, POR, PWM, WDTNumber of I/O75Program Memory Size832KB (832K x 8)Program Memory TypeFLASHEEPROM Size-XAM Size50K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 16x10bOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case100-LQFP Exposed PadNonter PackagePG-LQFP-100-8                                                      | Product Status             | Obsolete                                                                           |

| Speed100MHzConnectivityCANbus, EBI/EMI, I²C, LINbus, SPI, SSC, UART/USART, USIPeripheralsI²S, POR, PWM, WDTNumber of I/O75Program Memory Size832KB (832K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size50K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 16x10bOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case100-LQFP Exposed PadNon ting Towice PackagePG-LQFP-100-8                                                               | Core Processor             | C166SV2                                                                            |

| ConnectivityCANbus, EBI/EMI, I²C, LINbus, SPI, SSC, UART/USART, USIPeripheralsI²S, POR, PWM, WDTNumber of I/O75Program Memory Size832KB (832K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size50K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 16x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case100-LQFP Exposed PadSupplier Device PackagePG-LQFP-100-8                                                   | Core Size                  | 16/32-Bit                                                                          |

| PeripheralsI²S, POR, PWM, WDTNumber of I/O75Program Memory Size832KB (832K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size50K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 16x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case100-LQFP Exposed PadSupplier Device PackagePG-LQFP-100-8                                                                                                                      | Speed                      | 100MHz                                                                             |

| Number of I/O75Program Memory Size832KB (832K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size50K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 16x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case100-LQFP Exposed PadSupplier Device PackagePG-LQFP-100-8                                                                                                                                                   | Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI               |

| Program Memory Size832KB (832K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size50K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 16x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case100-LQFP Exposed PadSupplier Device PackagePG-LQFP-100-8                                                                                                                                                                  | Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                    |

| Program Memory TypeFLASHEEPROM Size-RAM Size50K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 16x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case100-LQFP Exposed PadSupplier Device PackagePG-LQFP-100-8                                                                                                                                                                                                     | Number of I/O              | 75                                                                                 |

| EEPROM Size-RAM Size50K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 16x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case100-LQFP Exposed PadSupplier Device PackagePG-LQFP-100-8                                                                                                                                                                                                                             | Program Memory Size        | 832KB (832K x 8)                                                                   |

| RAM Size50K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 16x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case100-LQFP Exposed PadSupplier Device PackagePG-LQFP-100-8                                                                                                                                                                                                                                         | Program Memory Type        | FLASH                                                                              |

| Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 16x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case100-LQFP Exposed PadSupplier Device PackagePG-LQFP-100-8                                                                                                                                                                                                                                                        | EEPROM Size                | -                                                                                  |

| Data ConvertersA/D 16x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case100-LQFP Exposed PadSupplier Device PackagePG-LQFP-100-8                                                                                                                                                                                                                                                                                           | RAM Size                   | 50K x 8                                                                            |

| Oscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case100-LQFP Exposed PadSupplier Device PackagePG-LQFP-100-8                                                                                                                                                                                                                                                                                                                    | Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                          |

| Operating Temperature     -40°C ~ 125°C (TA)       Mounting Type     Surface Mount       Package / Case     100-LQFP Exposed Pad       Supplier Device Package     PG-LQFP-100-8                                                                                                                                                                                                                                                                                                  | Data Converters            | A/D 16x10b                                                                         |

| Mounting Type     Surface Mount       Package / Case     100-LQFP Exposed Pad       Supplier Device Package     PG-LQFP-100-8                                                                                                                                                                                                                                                                                                                                                     | Oscillator Type            | Internal                                                                           |

| Package / Case 100-LQFP Exposed Pad Supplier Device Package PG-LQFP-100-8                                                                                                                                                                                                                                                                                                                                                                                                         | Operating Temperature      | -40°C ~ 125°C (TA)                                                                 |

| Supplier Device Package PG-LQFP-100-8                                                                                                                                                                                                                                                                                                                                                                                                                                             | Mounting Type              | Surface Mount                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Package / Case             | 100-LQFP Exposed Pad                                                               |

| Purchase URL https://www.e-xfl.com/product-detail/infineon-technologies/xc2364a104f100labhxuma1                                                                                                                                                                                                                                                                                                                                                                                   | Supplier Device Package    | PG-LQFP-100-8                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc2364a104f100labhxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

٠

#### Summary of Features

- Two Synchronizable A/D Converters with a total of up to 16 channels, 10-bit resolution, conversion time below  $1 \,\mu$ s, optional data preprocessing (data reduction, range check), broken wire detection

- Up to 6 serial interface channels to be used as UART, LIN, high-speed synchronous channel (SPI), IIC bus interface (10-bit addressing, 400 kbit/s), IIS interface

- On-chip MultiCAN interface (Rev. 2.0B active) with up to 64 message objects (Full CAN/Basic CAN) on up to 3 CAN nodes and gateway functionality

- On-chip system timer and on-chip real time clock

- Up to 12 Mbytes external address space for code and data

- Programmable external bus characteristics for different address ranges

- Multiplexed or demultiplexed external address/data buses

- Selectable address bus width

- 16-bit or 8-bit data bus width

- Four programmable chip-select signals

- Single power supply from 3.0 V to 5.5 V

- Programmable watchdog timer and oscillator watchdog

- Up to 76 general purpose I/O lines

- On-chip bootstrap loaders

- Supported by a full range of development tools including C compilers, macroassembler packages, emulators, evaluation boards, HLL debuggers, simulators, logic analyzer disassemblers, programming boards

- · On-chip debug support via Device Access Port (DAP) or JTAG interface

- 100-pin Green LQFP package, 0.5 mm (19.7 mil) pitch

## **General Device Information**

| Tabl | Table 6Pin Definitions and Functions (cont'd) |       |      |                                               |  |  |  |

|------|-----------------------------------------------|-------|------|-----------------------------------------------|--|--|--|

| Pin  | Symbol                                        | Ctrl. | Туре | Function                                      |  |  |  |

| 30   | P5.8                                          | 1     | In/A | Bit 8 of Port 5, General Purpose Input        |  |  |  |

|      | ADC0_CH8                                      | I     | In/A | Analog Input Channel 8 for ADC0               |  |  |  |

|      | ADC1_CH8                                      | I     | In/A | Analog Input Channel 8 for ADC1               |  |  |  |

|      | CCU6x_T12H<br>RC                              | I     | In/A | External Run Control Input for T12 of CCU60/1 |  |  |  |

|      | CCU6x_T13H<br>RC                              | I     | In/A | External Run Control Input for T13 of CCU60/1 |  |  |  |

|      | U2C0_DX0F                                     | 1     | In/A | USIC2 Channel 0 Shift Data Input              |  |  |  |

| 31   | P5.9                                          | 1     | In/A | Bit 9 of Port 5, General Purpose Input        |  |  |  |

|      | ADC0_CH9                                      | I     | In/A | Analog Input Channel 9 for ADC0               |  |  |  |

|      | ADC1_CH9                                      | I     | In/A | Analog Input Channel 9 for ADC1               |  |  |  |

|      | CC2_T7IN                                      | I     | In/A | CAPCOM2 Timer T7 Count Input                  |  |  |  |

| 32   | P5.10                                         | I     | In/A | Bit 10 of Port 5, General Purpose Input       |  |  |  |

|      | ADC0_CH10                                     | I     | In/A | Analog Input Channel 10 for ADC0              |  |  |  |

|      | ADC1_CH10                                     | I     | In/A | Analog Input Channel 10 for ADC1              |  |  |  |

|      | BRKIN_A                                       | I     | In/A | OCDS Break Signal Input                       |  |  |  |

|      | U2C1_DX0F                                     | I     | In/A | USIC2 Channel 1 Shift Data Input              |  |  |  |

|      | CCU61_T13<br>HRA                              | I     | In/A | External Run Control Input for T13 of CCU61   |  |  |  |

| 33   | P5.11                                         | I     | In/A | Bit 11 of Port 5, General Purpose Input       |  |  |  |

|      | ADC0_CH11                                     | 1     | In/A | Analog Input Channel 11 for ADC0              |  |  |  |

|      | ADC1_CH11                                     | 1     | In/A | Analog Input Channel 11 for ADC1              |  |  |  |

| 34   | P5.13                                         | I     | In/A | Bit 13 of Port 5, General Purpose Input       |  |  |  |

|      | ADC0_CH13                                     | I     | In/A | Analog Input Channel 13 for ADC0              |  |  |  |

| 35   | P5.15                                         | 1     | In/A | Bit 15 of Port 5, General Purpose Input       |  |  |  |

|      | ADC0_CH15                                     | I     | In/A | Analog Input Channel 15 for ADC0              |  |  |  |

|      | RxDC2F                                        | I     | In/A | CAN Node 2 Receive Data Input                 |  |  |  |

| -    |                                               | •     |      |                                               |  |  |  |

## XC2361A, XC2363A, XC2364A, XC2365A XC2000 Family / Base Line

## **General Device Information**

| Table | Table 6Pin Definitions and Functions (cont'd) |            |      |                                                |  |  |

|-------|-----------------------------------------------|------------|------|------------------------------------------------|--|--|

| Pin   | Symbol                                        | Ctrl.      | Туре | Function                                       |  |  |

| 59    | P10.0                                         | O0 / I     | St/B | Bit 0 of Port 10, General Purpose Input/Output |  |  |

|       | U0C1_DOUT                                     | 01         | St/B | USIC0 Channel 1 Shift Data Output              |  |  |

|       | CCU60_CC6<br>0                                | O2         | St/B | CCU60 Channel 0 Output                         |  |  |

|       | AD0                                           | OH /<br>IH | St/B | External Bus Interface Address/Data Line 0     |  |  |

|       | CCU60_CC6<br>0INA                             | I          | St/B | CCU60 Channel 0 Input                          |  |  |

|       | ESR1_2                                        | I          | St/B | ESR1 Trigger Input 2                           |  |  |

|       | U0C0_DX0A                                     | I          | St/B | USIC0 Channel 0 Shift Data Input               |  |  |

| _     | U0C1_DX0A                                     | I          | St/B | USIC0 Channel 1 Shift Data Input               |  |  |

| 60    | P10.1 00 / I St/B E                           |            |      | Bit 1 of Port 10, General Purpose Input/Output |  |  |

|       | U0C0_DOUT                                     | 01         | St/B | USIC0 Channel 0 Shift Data Output              |  |  |

|       | CCU60_CC6<br>1                                | O2         | St/B | CCU60 Channel 1 Output                         |  |  |

|       | AD1                                           | OH /<br>IH | St/B | External Bus Interface Address/Data Line 1     |  |  |

|       | CCU60_CC6<br>1INA                             | I          | St/B | CCU60 Channel 1 Input                          |  |  |

|       | U0C0_DX1A                                     | I          | St/B | USIC0 Channel 0 Shift Clock Input              |  |  |

|       | U0C0_DX0B                                     | I          | St/B | USIC0 Channel 0 Shift Data Input               |  |  |

| 61    | P0.3                                          | O0 / I     | St/B | Bit 3 of Port 0, General Purpose Input/Output  |  |  |

|       | U1C0_SELO<br>0                                | O1         | St/B | USIC1 Channel 0 Select/Control 0 Output        |  |  |

|       | U1C1_SELO<br>1                                | O2         | St/B | USIC1 Channel 1 Select/Control 1 Output        |  |  |

|       | CCU61_COU<br>T60                              | O3         | St/B | CCU61 Channel 0 Output                         |  |  |

|       | A3                                            | ОН         | St/B | External Bus Interface Address Line 3          |  |  |

|       | U1C0_DX2A                                     | I          | St/B | USIC1 Channel 0 Shift Control Input            |  |  |

|       | RxDC0B                                        | I          | St/B | CAN Node 0 Receive Data Input                  |  |  |

## **General Device Information**

| Pin | Symbol            | Ctrl.      | Туре | Function                                       |  |

|-----|-------------------|------------|------|------------------------------------------------|--|

| 62  | P10.2             | 00/1       | -    | Bit 2 of Port 10, General Purpose Input/Output |  |

|     | U0C0_SCLK<br>OUT  | 01         | St/B | USIC0 Channel 0 Shift Clock Output             |  |

|     | CCU60_CC6<br>2    | O2         | St/B | CCU60 Channel 2 Output                         |  |

|     | AD2               | OH /<br>IH | St/B | External Bus Interface Address/Data Line 2     |  |

|     | CCU60_CC6<br>2INA | 1          | St/B | CCU60 Channel 2 Input                          |  |

|     | U0C0_DX1B         | I          | St/B | USIC0 Channel 0 Shift Clock Input              |  |

| 63  | P0.4              | O0 / I     | St/B | Bit 4 of Port 0, General Purpose Input/Output  |  |

|     | U1C1_SELO<br>0    | 01         | St/B | USIC1 Channel 1 Select/Control 0 Output        |  |

|     | U1C0_SELO<br>1    | O2         | St/B | USIC1 Channel 0 Select/Control 1 Output        |  |

|     | CCU61_COU<br>T61  | O3         | St/B | CCU61 Channel 1 Output                         |  |

|     | A4                | OH         | St/B | External Bus Interface Address Line 4          |  |

|     | U1C1_DX2A         | I          | St/B | USIC1 Channel 1 Shift Control Input            |  |

|     | RxDC1B            | I          | St/B | CAN Node 1 Receive Data Input                  |  |

|     | ESR2_8            | I          | St/B | ESR2 Trigger Input 8                           |  |

| 65  | P2.13             | O0 / I     | St/B | Bit 13 of Port 2, General Purpose Input/Output |  |

|     | U2C1_SELO<br>2    | 01         | St/B | USIC2 Channel 1 Select/Control 2 Output        |  |

|     | RxDC2D            | I          | St/B | CAN Node 2 Receive Data Input                  |  |

| 66  | P2.10             | O0 / I     | St/B | Bit 10 of Port 2, General Purpose Input/Output |  |

|     | U0C1_DOUT         | 01         | St/B | USIC0 Channel 1 Shift Data Output              |  |

|     | U0C0_SELO<br>3    | O2         | St/B | USIC0 Channel 0 Select/Control 3 Output        |  |

|     | CC2_CC23          | O3 / I     | St/B | CAPCOM2 CC23IO Capture Inp./ Compare Out.      |  |

|     | A23               | ОН         | St/B | External Bus Interface Address Line 23         |  |

|     | U0C1_DX0E         | I          | St/B | USIC0 Channel 1 Shift Data Input               |  |

|     | CAPINA            | I          | St/B | GPT12E Register CAPREL Capture Input           |  |

# XC2361A, XC2363A, XC2364A, XC2365A XC2000 Family / Base Line

## **General Device Information**

| Table | Table 6Pin Definitions and Functions (cont'd) |            |      |                                                |  |  |

|-------|-----------------------------------------------|------------|------|------------------------------------------------|--|--|

| Pin   | Symbol                                        | Ctrl.      | Туре | Function                                       |  |  |

| 67    | P10.3                                         | O0 / I     | St/B | Bit 3 of Port 10, General Purpose Input/Output |  |  |

|       | CCU60_COU<br>T60                              | O2         | St/B | CCU60 Channel 0 Output                         |  |  |

|       | AD3                                           | OH /<br>IH | St/B | External Bus Interface Address/Data Line 3     |  |  |

|       | U0C0_DX2A                                     | I          | St/B | USIC0 Channel 0 Shift Control Input            |  |  |

|       | U0C1_DX2A                                     | I          | St/B | USIC0 Channel 1 Shift Control Input            |  |  |

| 68    | P0.5                                          | O0 / I     | St/B | Bit 5 of Port 0, General Purpose Input/Output  |  |  |

|       | U1C1_SCLK<br>OUT                              | 01         | St/B | USIC1 Channel 1 Shift Clock Output             |  |  |

|       | U1C0_SELO<br>2                                | O2         | St/B | USIC1 Channel 0 Select/Control 2 Output        |  |  |

|       | CCU61_COU<br>T62                              | O3         | St/B | CCU61 Channel 2 Output                         |  |  |

|       | A5                                            | OH         | St/B | External Bus Interface Address Line 5          |  |  |

|       | U1C1_DX1A                                     | I          | St/B | USIC1 Channel 1 Shift Clock Input              |  |  |

|       | U1C0_DX1C                                     | I          | St/B | USIC1 Channel 0 Shift Clock Input              |  |  |

| 69    | P10.4                                         | O0 / I     | St/B | Bit 4 of Port 10, General Purpose Input/Output |  |  |

|       | U0C0_SELO<br>3                                | 01         | St/B | USIC0 Channel 0 Select/Control 3 Output        |  |  |

|       | CCU60_COU<br>T61                              | O2         | St/B | CCU60 Channel 1 Output                         |  |  |

|       | AD4                                           | OH /<br>IH | St/B | External Bus Interface Address/Data Line 4     |  |  |

|       | U0C0_DX2B                                     | I          | St/B | USIC0 Channel 0 Shift Control Input            |  |  |

|       | U0C1_DX2B                                     | I          | St/B | USIC0 Channel 1 Shift Control Input            |  |  |

|       | ESR1_9                                        | I          | St/B | ESR1 Trigger Input 9                           |  |  |

## **General Device Information**

| Pin         Sym           79         P10.           U0C |              | Ctrl.      | Туре |                                                                                                                                                                                                                                                                                                      |  |  |

|---------------------------------------------------------|--------------|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                         | .8           |            | Type | Function                                                                                                                                                                                                                                                                                             |  |  |

| U0C                                                     |              | O0 / I     | St/B | Bit 8 of Port 10, General Purpose Input/Output                                                                                                                                                                                                                                                       |  |  |

| OUT                                                     | 0_MCLK       | 01         | St/B | USIC0 Channel 0 Master Clock Output                                                                                                                                                                                                                                                                  |  |  |

| U0C<br>0                                                | 1_SELO       | 02         | St/B | USIC0 Channel 1 Select/Control 0 Output                                                                                                                                                                                                                                                              |  |  |

| U2C                                                     | 1_DOUT       | O3         | St/B | USIC2 Channel 1 Shift Data Output                                                                                                                                                                                                                                                                    |  |  |

| AD8                                                     |              | OH /<br>IH | St/B | External Bus Interface Address/Data Line 8                                                                                                                                                                                                                                                           |  |  |

| CCL<br>OS1                                              | J60_ССР<br>А | I          | St/B | CCU60 Position Input 1                                                                                                                                                                                                                                                                               |  |  |

| U0C                                                     | 0_DX1C       | I          | St/B | USIC0 Channel 0 Shift Clock Input                                                                                                                                                                                                                                                                    |  |  |

| BRK                                                     | (IN_B        | 1          | St/B | OCDS Break Signal Input                                                                                                                                                                                                                                                                              |  |  |

| T3E                                                     | UDB          | I          | St/B | GPT12E Timer T3 External Up/Down Control Input                                                                                                                                                                                                                                                       |  |  |

| 80 P10.                                                 | .9           | O0 / I     | St/B | Bit 9 of Port 10, General Purpose Input/Output                                                                                                                                                                                                                                                       |  |  |

| U0C<br>4                                                | 0_SELO       | 01         | St/B | USIC0 Channel 0 Select/Control 4 Output                                                                                                                                                                                                                                                              |  |  |

| U0C<br>OUT                                              | 1_MCLK       | 02         | St/B | USIC0 Channel 1 Master Clock Output                                                                                                                                                                                                                                                                  |  |  |

| AD9                                                     |              | OH /<br>IH | St/B | External Bus Interface Address/Data Line 9                                                                                                                                                                                                                                                           |  |  |

| CCL<br>OS2                                              | J60_CCP<br>A | I          | St/B | CCU60 Position Input 2                                                                                                                                                                                                                                                                               |  |  |

| ТСК                                                     | <u></u> B    | IH         | St/B | <b>DAP0/JTAG Clock Input</b><br>If JTAG pos. B is selected during start-up, an<br>internal pull-up device will hold this pin high when<br>nothing is driving it.<br>If DAP pos. 1 is selected during start-up, an<br>internal pull-down device will hold this pin low<br>when nothing is driving it. |  |  |

| T3IN                                                    | IB           | 1          | St/B | GPT12E Timer T3 Count/Gate Input                                                                                                                                                                                                                                                                     |  |  |

## **General Device Information**

| Table | Table 6Pin Definitions and Functions (cont'd) |        |      |                                                 |  |  |  |

|-------|-----------------------------------------------|--------|------|-------------------------------------------------|--|--|--|

| Pin   | Symbol                                        | Ctrl.  | Туре | Function                                        |  |  |  |

| 87    | P1.3                                          | O0 / I | St/B | Bit 3 of Port 1, General Purpose Input/Output   |  |  |  |

|       | U1C0_SELO<br>7                                | O2     | St/B | USIC1 Channel 0 Select/Control 7 Output         |  |  |  |

|       | U2C0_SELO<br>4                                | O3     | St/B | USIC2 Channel 0 Select/Control 4 Output         |  |  |  |

|       | A11                                           | ОН     | St/B | External Bus Interface Address Line 11          |  |  |  |

|       | ESR2_4                                        | I      | St/B | ESR2 Trigger Input 4                            |  |  |  |

| 89    | P10.14                                        | O0 / I | St/B | Bit 14 of Port 10, General Purpose Input/Output |  |  |  |

|       | U1C0_SELO<br>1                                | 01     | St/B | USIC1 Channel 0 Select/Control 1 Output         |  |  |  |

|       | U0C1_DOUT                                     | 02     | St/B | USIC0 Channel 1 Shift Data Output               |  |  |  |

|       | RD                                            | OH     | St/B | External Bus Interface Read Strobe Output       |  |  |  |

|       | ESR2_2                                        | I      | St/B | ESR2 Trigger Input 2                            |  |  |  |

|       | U0C1_DX0C                                     | I      | St/B | USIC0 Channel 1 Shift Data Input                |  |  |  |

| 90    | P1.4                                          | O0 / I | St/B | Bit 4 of Port 1, General Purpose Input/Output   |  |  |  |

|       | U1C1_SELO<br>4                                | O2     | St/B | USIC1 Channel 1 Select/Control 4 Output         |  |  |  |

|       | U2C0_SELO<br>5                                | O3     | St/B | USIC2 Channel 0 Select/Control 5 Output         |  |  |  |

|       | A12                                           | ОН     | St/B | External Bus Interface Address Line 12          |  |  |  |

|       | U2C0_DX2B                                     | I      | St/B | USIC2 Channel 0 Shift Control Input             |  |  |  |

| 91    | P10.15                                        | O0 / I | St/B | Bit 15 of Port 10, General Purpose Input/Output |  |  |  |

|       | U1C0_SELO<br>2                                | 01     | St/B | USIC1 Channel 0 Select/Control 2 Output         |  |  |  |

|       | U0C1_DOUT                                     | 02     | St/B | USIC0 Channel 1 Shift Data Output               |  |  |  |

|       | U1C0_DOUT                                     | O3     | St/B | USIC1 Channel 0 Shift Data Output               |  |  |  |

|       | ALE                                           | ОН     | St/B | External Bus Interf. Addr. Latch Enable Output  |  |  |  |

|       | U0C1_DX1C                                     | I      | St/B | USIC0 Channel 1 Shift Clock Input               |  |  |  |

### **Functional Description**

| Address Area         | Start Loc.           | End Loc.             | Area Size <sup>2)</sup> | Notes |  |  |  |  |

|----------------------|----------------------|----------------------|-------------------------|-------|--|--|--|--|

| Data SRAM            | 00'A000 <sub>H</sub> | 00'DFFF <sub>H</sub> | 16 Kbytes               | -     |  |  |  |  |

| Reserved for DSRAM   | 00'8000 <sub>H</sub> | 00'9FFF <sub>H</sub> | 8 Kbytes                | -     |  |  |  |  |

| External memory area | 00'0000 <sub>H</sub> | 00'7FFF <sub>H</sub> | 32 Kbytes               | -     |  |  |  |  |

### Table 8 XC236xA Memory Map (cont'd)<sup>1)</sup>

Accesses to the shaded areas are reserved. In devices with external bus interface these accesses generate external bus accesses.

2) The areas marked with "<" are slightly smaller than indicated. See column "Notes".

3) The uppermost 4-Kbyte sector of the first Flash segment is reserved for internal use (C0'F000<sub>H</sub> to C0'FFFF<sub>H</sub>).

4) Several pipeline optimizations are not active within the external IO area. This is necessary to control external peripherals properly.

This common memory space consists of 16 Mbytes organized as 256 segments of 64 Kbytes; each segment contains four data pages of 16 Kbytes. The entire memory space can be accessed bytewise or wordwise. Portions of the on-chip DPRAM and the register spaces (ESFR/SFR) additionally are directly bit addressable.

The internal data memory areas and the Special Function Register areas (SFR and ESFR) are mapped into segment 0, the system segment.

The Program Management Unit (PMU) handles all code fetches and, therefore, controls access to the program memories such as Flash memory and PSRAM.

The Data Management Unit (DMU) handles all data transfers and, therefore, controls access to the DSRAM and the on-chip peripherals.

Both units (PMU and DMU) are connected to the high-speed system bus so that they can exchange data. This is required if operands are read from program memory, code or data is written to the PSRAM, code is fetched from external memory, or data is read from or written to external resources. These include peripherals on the LXBus such as USIC or MultiCAN. The system bus allows concurrent two-way communication for maximum transfer performance.

**Up to 32 Kbytes of on-chip Program SRAM (PSRAM)** are provided to store user code or data. The PSRAM is accessed via the PMU and is optimized for code fetches. A section of the PSRAM with programmable size can be write-protected.

Up to 16 Kbytes of on-chip Data SRAM (DSRAM) are used for storage of general user data. The DSRAM is accessed via a separate interface and is optimized for data access.

**2 Kbytes of on-chip Dual-Port RAM (DPRAM)** provide storage for user-defined variables, for the system stack, and for general purpose register banks. A register bank can consist of up to 16 word-wide (R0 to R15) and/or byte-wide (RL0, RH0, ..., RL7, RH7) General Purpose Registers (GPRs).

The upper 256 bytes of the DPRAM are directly bit addressable. When used by a GPR, any location in the DPRAM is bit addressable.

### **Functional Description**

# 3.4 Memory Protection Unit (MPU)

The XC236xA's Memory Protection Unit (MPU) protects user-specified memory areas from unauthorized read, write, or instruction fetch accesses. The MPU can protect the whole address space including the peripheral area. This completes establisched mechanisms such as the register security mechanism or stack overrun/underrun detection.

Four Protection Levels support flexible system programming where operating system, low level drivers, and applications run on separate levels. Each protection level permits different access restrictions for instructions and/or data.

Every access is checked (if the MPU is enabled) and an access violating the permission rules will be marked as invalid and leads to a protection trap.

A set of protection registers for each protection level specifies the address ranges and the access permissions. Applications requiring more than 4 protection levels can dynamically re-program the protection registers.

## 3.5 Memory Checker Module (MCHK)

The XC236xA's Memory Checker Module calculates a checksum (fractional polynomial division) on a block of data, often called Cyclic Redundancy Code (CRC). It is based on a 32-bit linear feedback shift register and may, therefore, also be used to generate pseudo-random numbers.

The Memory Checker Module is a 16-bit parallel input signature compression circuitry which enables error detection within a block of data stored in memory, registers, or communicated e.g. via serial communication lines. It reduces the probability of error masking due to repeated error patterns by calculating the signature of blocks of data.

The polynomial used for operation is configurable, so most of the commonly used polynomials may be used. Also, the block size for generating a CRC result is configurable via a local counter. An interrupt may be generated if testing the current data block reveals an error.

An autonomous CRC compare circuitry is included to enable redundant error detection, e.g. to enable higher safety integrity levels.

The Memory Checker Module provides enhanced fault detection (beyond parity or ECC) for data and instructions in volatile and non volatile memories. This is especially important for the safety and reliability of embedded systems.

### **Functional Description**

# 3.16 Watchdog Timer

The Watchdog Timer is one of the fail-safe mechanisms which have been implemented to prevent the controller from malfunctioning for longer periods of time.

The Watchdog Timer is always enabled after an application reset of the chip. It can be disabled and enabled at any time by executing the instructions DISWDT and ENWDT respectively. The software has to service the Watchdog Timer before it overflows. If this is not the case because of a hardware or software failure, the Watchdog Timer overflows, generating a prewarning interrupt and then a reset request.

The Watchdog Timer is a 16-bit timer clocked with the system clock divided by 16,384 or 256. The Watchdog Timer register is set to a prespecified reload value (stored in WDTREL) in order to allow further variation of the monitored time interval. Each time it is serviced by the application software, the Watchdog Timer is reloaded and the prescaler is cleared.

Time intervals between 3.2  $\mu$ s and 13.42 s can be monitored (@ 80 MHz). The default Watchdog Timer interval after power-up is 6.5 ms (@ 10 MHz).

## 3.17 Clock Generation

The Clock Generation Unit can generate the system clock signal  $f_{SYS}$  for the XC236xA from a number of external or internal clock sources:

- External clock signals with pad voltage or core voltage levels

- External crystal or resonator using the on-chip oscillator

- On-chip clock source for operation without crystal/resonator

- · Wake-up clock (ultra-low-power) to further reduce power consumption

The programmable on-chip PLL with multiple prescalers generates a clock signal for maximum system performance from standard crystals, a clock input signal, or from the on-chip clock source. See also **Section 4.6.2**.

The Oscillator Watchdog (OWD) generates an interrupt if the crystal oscillator frequency falls below a certain limit or stops completely. In this case, the system can be supplied with an emergency clock to enable operation even after an external clock failure.

All available clock signals can be output on one of two selectable pins.

## 4.1.3 Pad Timing Definition

If not otherwise noted, all timing parameters are tested and are valid for the corresponding output pins operating in strong driver, fast edge mode. See also "Pad Properties" on Page 102.

### 4.1.4 Parameter Interpretation

The parameters listed in the following include both the characteristics of the XC236xA and its demands on the system. To aid in correctly interpreting the parameters when evaluating them for a design, they are marked accordingly in the column "Symbol":

**CC** (Controller Characteristics):

The logic of the XC236xA provides signals with the specified characteristics.

#### SR (System Requirement):

The external system must provide signals with the specified characteristics to the XC236xA.

| Table 23Flash Parameters (cont'd) |

|-----------------------------------|

|-----------------------------------|

| Parameter              | Symbol             | Values |      |        | Unit       | Note /                                                                                         |

|------------------------|--------------------|--------|------|--------|------------|------------------------------------------------------------------------------------------------|

|                        |                    | Min.   | Тур. | Max.   |            | Test Condition                                                                                 |

| Number of erase cycles | N <sub>Er</sub> SR | -      | -    | 15 000 | cycle<br>s | $t_{RET} \ge 5$ years;<br>Valid for up to<br>64 user-<br>selected<br>sectors (data<br>storage) |

|                        |                    | -      | -    | 1 000  | cycle<br>s | $t_{RET} \ge 20$ years                                                                         |

All Flash module(s) can be erased/programmed while code is executed and/or data is read from only one Flash module or from PSRAM. The Flash module that delivers code/data can, of course, not be erased/programmed.

Flash module 3 can be erased/programmed while code is executed and/or data is read from any other Flash module.

3) Value of IMB\_IMBCTRL.WSFLASH.

4) Programming and erase times depend on the internal Flash clock source. The control state machine needs a few system clock cycles. This increases the stated durations noticably only at extremely low system clock frequencies.

Access to the XC236xA Flash modules is controlled by the IMB. Built-in prefetch mechanisms optimize the performance for sequential access.

Flash access waitstates only affect non-sequential access. Due to prefetch mechanisms, the performance for sequential access (depending on the software structure) is only partially influenced by waitstates.

## PLL frequency band selection

Different frequency bands can be selected for the VCO so that the operation of the PLL can be adjusted to a wide range of input and output frequencies:

| Table 24 | System PLL | Parameters |

|----------|------------|------------|

|----------|------------|------------|

| Parameter Symbol     |                       |      | Values | ;    | Unit | Note /                   |

|----------------------|-----------------------|------|--------|------|------|--------------------------|

|                      |                       | Min. | Тур.   | Max. |      | Test Condition           |

| VCO output frequency | $f_{\rm VCO}{\rm CC}$ | 50   | -      | 110  | MHz  | VCOSEL = 00 <sub>B</sub> |

| (VCO controlled)     |                       | 100  | -      | 160  | MHz  | VCOSEL = 01 <sub>B</sub> |

| VCO output frequency | $f_{\rm VCO}$ CC      | 10   | -      | 40   | MHz  | VCOSEL = 00 <sub>B</sub> |

| (VCO free-running)   |                       | 20   | -      | 80   | MHz  | VCOSEL = 01 <sub>B</sub> |

## 4.6.2.2 Wakeup Clock

When wakeup operation is selected (SYSCON0.CLKSEL =  $00_B$ ), the system clock is derived from the low-frequency wakeup clock source:

$f_{SYS} = f_{WU}$ .

In this mode, a basic functionality can be maintained without requiring an external clock source and while minimizing the power consumption.

# 4.6.2.3 Selecting and Changing the Operating Frequency

When selecting a clock source and the clock generation method, the required parameters must be carefully written to the respective bit fields, to avoid unintended intermediate states.

Many applications change the frequency of the system clock ( $f_{SYS}$ ) during operation in order to optimize system performance and power consumption. Changing the operating frequency also changes the switching currents, which influences the power supply.

To ensure proper operation of the on-chip EVRs while they generate the core voltage, the operating frequency shall only be changed in certain steps. This prevents overshoots and undershoots of the supply voltage.

To avoid the indicated problems, recommended sequences are provided which ensure the intended operation of the clock system interacting with the power system. Please refer to the Programmer's Guide.

# 4.6.4 Pad Properties

The output pad drivers of the XC236xA can operate in several user-selectable modes. Strong driver mode allows controlling external components requiring higher currents such as power bridges or LEDs. Reducing the driving power of an output pad reduces electromagnetic emissions (EME). In strong driver mode, selecting a slower edge reduces EME.

The dynamic behavior, i.e. the rise time and fall time, depends on the applied external capacitance that must be charged and discharged. Timing values are given for a capacitance of 20 pF, unless otherwise noted.

In general, the performance of a pad driver depends on the available supply voltage  $V_{\text{DDP}}$ . The following table lists the pad parameters.

- Note: These parameters are not subject to production test but verified by design and/or characterization.

- Note: Operating Conditions apply.

Note: The term CLKOUT refers to the reference clock output signal which is generated by selecting  $f_{SYS}$  as the source signal for the clock output signal EXTCLK on pin P2.8 and by enabling the high-speed clock driver on this pin.

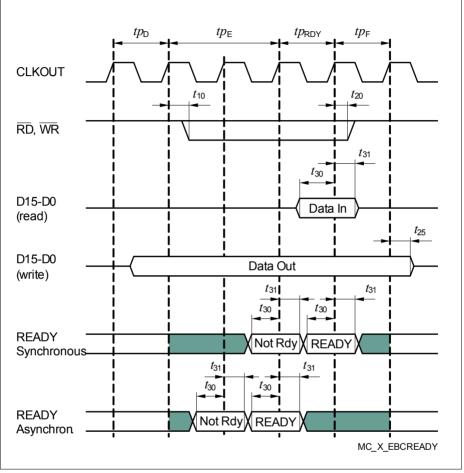

### Variable Memory Cycles

External bus cycles of the XC236xA are executed in five consecutive cycle phases (AB, C, D, E, F). The duration of each cycle phase is programmable (via the TCONCSx registers) to adapt the external bus cycles to the respective external module (memory, peripheral, etc.).

The duration of the access phase can optionally be controlled by the external module using the READY handshake input.

This table provides a summary of the phases and the ranges for their length.

| Table 29 | Programmable Bus C  | vcle Phases ( | see timino | diagrams) |

|----------|---------------------|---------------|------------|-----------|

|          | i logiannasio Bao e | ,             | 000        |           |

| Bus Cycle Phase                                                                                                                                | Parameter | Valid Values | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------|------|

| Address setup phase, the standard duration of this phase (1 $\dots$ 2 TCS) can be extended by 0 $\dots$ 3 TCS if the address window is changed | tpAB      | 1 2 (5)      | TCS  |

| Command delay phase                                                                                                                            | tpC       | 03           | TCS  |

| Write Data setup/MUX Tristate phase                                                                                                            | tpD       | 0 1          | TCS  |

| Access phase                                                                                                                                   | tpE       | 1 32         | TCS  |

| Address/Write Data hold phase                                                                                                                  | tpF       | 03           | TCS  |

Note: The bandwidth of a parameter (from minimum to maximum value) covers the whole operating range (temperature, voltage) as well as process variations. Within a given device, however, this bandwidth is smaller than the specified range. This is also due to interdependencies between certain parameters. Some of these interdependencies are described in additional notes (see standard timing).

Note: Operating Conditions apply;  $C_L = 20 \text{ pF}$ .

Figure 25 READY Timing

Note: If the READY input is sampled inactive at the indicated sampling point ("Not Rdy") a READY-controlled waitstate is inserted (tpRDY),

sampling the READY input active at the indicated sampling point ("Ready") terminates the currently running bus cycle.

Note the different sampling points for synchronous and asynchronous READY. This example uses one mandatory waitstate (see tpE) before the READY input value is used.

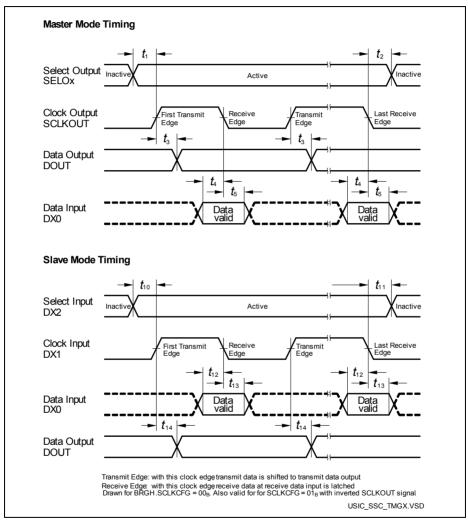

### Table 33 USIC SSC Master Mode Timing for Lower Voltage Range (cont'd)

| Parameter                                                   | Symbol            | Values |      |      | Unit | Note /         |

|-------------------------------------------------------------|-------------------|--------|------|------|------|----------------|

|                                                             |                   | Min.   | Тур. | Max. | 1    | Test Condition |

| Receive data input setup<br>time to SCLKOUT receive<br>edge | t <sub>4</sub> SR | 40     | -    | -    | ns   |                |

| Data input DX0 hold time<br>from SCLKOUT receive<br>edge    | t <sub>5</sub> SR | -5     | -    | -    | ns   |                |

1)  $t_{SYS} = 1 / f_{SYS}$

### Table 34 USIC SSC Slave Mode Timing for Upper Voltage Range

| Parameter                                                                         | Symbol                    | Values |      |      | Unit | Note /         |

|-----------------------------------------------------------------------------------|---------------------------|--------|------|------|------|----------------|

|                                                                                   |                           | Min.   | Тур. | Max. | 1    | Test Condition |

| Select input DX2 setup to first clock input DX1 transmit edge <sup>1)</sup>       | <i>t</i> <sub>10</sub> SR | 7      | -    | -    | ns   |                |

| Select input DX2 hold after<br>last clock input DX1<br>receive edge <sup>1)</sup> | <i>t</i> <sub>11</sub> SR | 7      | -    | -    | ns   |                |

| Receive data input setup<br>time to shift clock receive<br>edge <sup>1)</sup>     | <i>t</i> <sub>12</sub> SR | 7      | -    | -    | ns   |                |

| Data input DX0 hold time<br>from clock input DX1<br>receive edge <sup>1)</sup>    | <i>t</i> <sub>13</sub> SR | 5      | -    | -    | ns   |                |

| Data output DOUT valid time                                                       | <i>t</i> <sub>14</sub> CC | 7      | -    | 33   | ns   |                |

1) These input timings are valid for asynchronous input signal handling of slave select input, shift clock input, and receive data input (bits DXnCR.DSEN = 0).

Figure 26 USIC - SSC Master/Slave Mode Timing

Note: This timing diagram shows a standard configuration where the slave select signal is low-active and the serial clock signal is not shifted and not inverted.

### Debug via JTAG

The following parameters are applicable for communication through the JTAG debug interface. The JTAG module is fully compliant with IEEE1149.1-2000.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply;  $C_L$ = 20 pF.

| Parameter                                                                | Symbol                    | Values           |      |      | Unit | Note /         |

|--------------------------------------------------------------------------|---------------------------|------------------|------|------|------|----------------|

|                                                                          | l                         | Min.             | Тур. | Max. | 1    | Test Condition |

| TCK clock period                                                         | t <sub>1</sub> SR         | 50 <sup>1)</sup> | -    | -    | ns   | 2)             |

| TCK high time                                                            | t <sub>2</sub> SR         | 16               | -    | -    | ns   |                |

| TCK low time                                                             | t <sub>3</sub> SR         | 16               | -    | -    | ns   |                |

| TCK clock rise time                                                      | t <sub>4</sub> SR         | -                | -    | 8    | ns   |                |

| TCK clock fall time                                                      | t <sub>5</sub> SR         | -                | -    | 8    | ns   |                |

| TDI/TMS setup to TCK rising edge                                         | t <sub>6</sub> SR         | 6                | -    | -    | ns   |                |

| TDI/TMS hold after TCK rising edge                                       | t <sub>7</sub> SR         | 6                | -    | -    | ns   |                |

| TDO valid from TCK falling edge (propagation delay) <sup>3)</sup>        | t <sub>8</sub> CC         | _                | 25   | 29   | ns   |                |

| TDO high impedance to valid output from TCK falling edge <sup>4)3)</sup> | t <sub>9</sub> CC         | -                | 25   | 29   | ns   |                |

| TDO valid output to high impedance from TCK falling edge <sup>3)</sup>   | <i>t</i> <sub>10</sub> CC | -                | 25   | 29   | ns   |                |

| TDO hold after TCK falling edge <sup>3)</sup>                            | <i>t</i> <sub>18</sub> CC | 5                | -    | -    | ns   |                |

#### Table 38JTAG Interface Timing for Upper Voltage Range

1) The debug interface cannot operate faster than the overall system, therefore  $t_1 \ge t_{SYS}$ .

2) Under typical conditions, the interface can operate at transfer rates up to 20 MHz.

3) The falling edge on TCK is used to generate the TDO timing.

4) The setup time for TDO is given implicitly by the TCK cycle time.

# XC2361A, XC2363A, XC2364A, XC2365A XC2000 Family / Base Line

### Package and Reliability

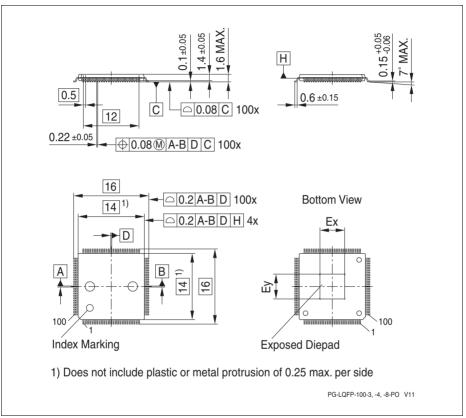

# Package Outlines

Figure 32 PG-LQFP-100-8/-15 (Plastic Green Thin Quad Flat Package)

All dimensions in mm.

You can find complete information about Infineon packages, packing and marking in our Infineon Internet Page "Packages": http://www.infineon.com/packages