Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ARM9®                                                                |

| Core Size                  | 16/32-Bit                                                            |

| Speed                      | 96MHz                                                                |

| Connectivity               | CANbus, I <sup>2</sup> C, Microwire, SPI, SSP, UART/USART, USB       |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT        |

| Number of I/O              | 40                                                                   |

| Program Memory Size        | 256KB (256K x 8)                                                     |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 96K x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 2V                                                           |

| Data Converters            | A/D 8x10b                                                            |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 80-LQFP                                                              |

| Supplier Device Package    | -                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/str911fm42x6 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|     | 2.23       | General purpose I/O                                                                                                          | 28   |

|-----|------------|------------------------------------------------------------------------------------------------------------------------------|------|

|     | 2.24       | A/D converter (ADC)                                                                                                          | 29   |

|     | 2.25       | Standard timers (TIM) with DMA                                                                                               | 29   |

|     |            | 2.25.1 DMA                                                                                                                   | . 30 |

|     | 2.26       | Three-phase induction motor controller (IMC)                                                                                 | 30   |

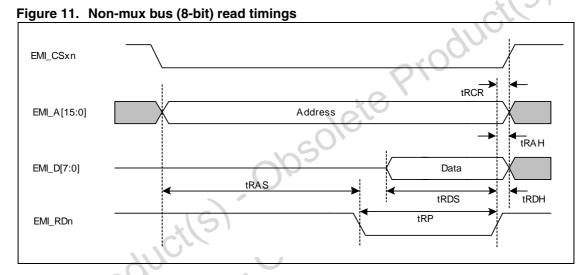

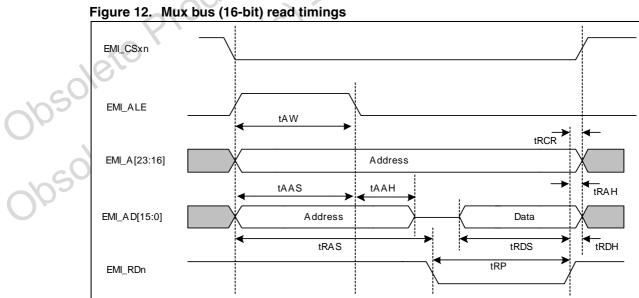

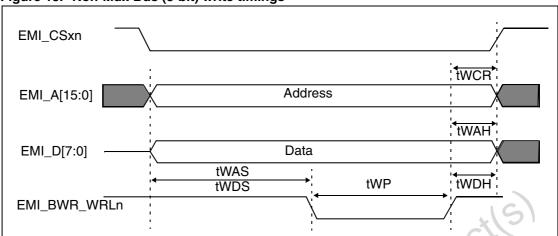

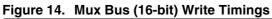

|     | 2.27       | External memory interface (EMI)                                                                                              | 30   |

| 3   | Relat      | ed documentation                                                                                                             | 33   |

| 4   | Pin d      | lescription                                                                                                                  | 34   |

|     | 4.1        | Default pin functions                                                                                                        |      |

| 5   | Mem        | ory mapping                                                                                                                  | 42   |

|     | 5.1        | Buffered and non-buffered writes                                                                                             | 42   |

|     | 5.2        | System (AHB) and peripheral (APB) buses                                                                                      | 42   |

|     | 5.3        | SRAM                                                                                                                         | 42   |

|     | 5.4        | SRAM Two independent Flash memories                                                                                          | 43   |

|     |            | 5.4.1 Default configuration                                                                                                  | . 43 |

|     |            | 5.4.2 Optional configuration                                                                                                 | . 43 |

| 6   | Elect      | rical characteristics                                                                                                        | 16   |

| 0   | 6.1        | Absolute maximum ratings                                                                                                     |      |

|     | 6.2        | Operating conditions                                                                                                         |      |

|     |            |                                                                                                                              |      |

|     | 6.3<br>6.4 | LVD electrical characteristics                                                                                               |      |

| c   | 6.5        | AC electrical characteristics                                                                                                |      |

| 005 |            |                                                                                                                              |      |

| U.  | 6.6<br>6.7 | RESET_INn and power-on-reset characteristics            Main oscillator electrical characteristics                           |      |

| ~   | 6.8        | RTC oscillator electrical characteristics                                                                                    |      |

| 005 | 6.9        | PLL electrical characteristics                                                                                               |      |

| 0   | 6.10       |                                                                                                                              |      |

|     |            | Flash memory characteristics                                                                                                 |      |

|     | 6.11       | EMC characteristics                                                                                                          |      |

|     |            | <ul><li>6.11.1 Functional EMS (Electro Magnetic Susceptibility)</li><li>6.11.2 Electro Magnetic Interference (EMI)</li></ul> |      |

|     |            | 6.11.3 Absolute Maximum Ratings (Electrical Sensitivity)                                                                     |      |

|     |            |                                                                                                                              |      |

#### Introduction 1

STR91xF is a series of ARM-powered microcontrollers which combines a 16/32-bit ARM966E-S RISC processor core, dual-bank Flash memory, large SRAM for data or code, and a rich peripheral set to form an ideal embedded controller for a wide variety of applications such as point-of-sale terminals, industrial automation, security and surveillance, vending machines, communication gateways, serial protocol conversion, and medical equipment. The ARM966E-S core can perform single-cycle DSP instructions, good for speech processing, audio algorithms, and low-end imaging.

This datasheet provides STR91xF ordering information, functional overview, mechanical information, and electrical device characteristics.

For complete information on STR91xF memory, registers, and peripherals, please refer to the STR91xF Reference Manual.

For information on programming the STR91xF Flash memory please refer to the STR9 Flash **Programming Reference Manual**

For information on the ARM966E-S core, please refer to the ARM966E-S Rev. 2 Technical Nete Reference Manual.

| M32X6       W32X6       M42X6       M44X6       W42X6         Flash       256+32       256+32       512+32       256+32         RAM -       64       96       96         Peripheral functions       CAN, 40 I/Os       CAN, EMI, 80 I/Os       USB, CAN, 40 I/Os       Ethernet, USB, C 80 I/Os         Packages       LQFP80       LQFP128       LQFP80       LQFP124 |        | STR912F |           | STR911F |         | STF    | Features |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------|-----------|---------|---------|--------|----------|--|

| Kbytes256+32256+32512+32256+32RAM -<br>Kbytes649696Peripheral<br>functionsCAN, 40 I/OsCAN, EMI,<br>80 I/OsUSB, CAN, 40 I/OsEthernet, USB, C<br>80 I/OsPackagesLQFP80LQFP128LQFP80LQFP128                                                                                                                                                                               | W44X6  | W42X6   | M44X6     | M42X6   | W32X6   | M32X6  | realures |  |

| Kbytes     64     96     96       Peripheral<br>functions     CAN, 40 I/Os     CAN, EMI,<br>80 I/Os     USB, CAN, 40 I/Os     Ethernet, USB, CAN, 40 I/Os       Packages     LQFP80     LQFP128     LQFP80     LQFP128                                                                                                                                                 | 512+32 | 256+32  | 512+32    | 256+32  | 6+32    | 250    |          |  |

| functions     CAN, 40 I/OS     80 I/Os     0SB, CAN, 40 I/OS     80 I/Os       Packages     LQFP80     LQFP128     LQFP80     LQFP128                                                                                                                                                                                                                                  |        | 96      | <b>35</b> | 90      | C       | (      |          |  |

| dete Product(S)                                                                                                                                                                                                                                                                                                                                                        |        |         |           |         |         |        |          |  |

| psolete Product(S)                                                                                                                                                                                                                                                                                                                                                     | 28     | LQFP    | P80       | LQF     | LQFP128 | LQFP80 | Packages |  |

|                                                                                                                                                                                                                                                                                                                                                                        |        |         |           |         |         |        |          |  |

#### Table 1. **Device summary**

# 2.10 Clock control unit (CCU)

The CCU generates a master clock of frequency  $f_{MSTR}$ . From this master clock the CCU also generates individually scaled and gated clock sources to each of the following functional blocks within the STR91xF.

- CPU, f<sub>CPUCLK</sub>

- Advanced High-performance Bus (AHB), f<sub>HCLK</sub>

- Advanced Peripheral Bus (APB), f<sub>PCLK</sub>

- Flash Memory Interface (FMI), f<sub>FMICLK</sub>

- External Memory Interface (EMI), f<sub>BCLK</sub>

- UART Baud Rate Generators, f<sub>BAUD</sub>

- USB, f<sub>USB</sub>

## 2.10.1 Master clock sources

The master clock in the CCU (f<sub>MSTR</sub>) is derived from one of three clock input sources. Under firmware control, the CPU can switch between the three CCU inputs without introducing any glitches on the master clock output. Inputs to the CCU are:

- Main Oscillator (f<sub>OSC</sub>). The source for the main oscillator input is a 4 to 25 MHz external crystal connected to STR91xF pins X1\_CPU and X2\_CPU, or an external oscillator device connected to pin X1\_CPU.

- PLL (f<sub>PLL</sub>). The PLL takes the 4 to 25 MHz oscillator clock as input and generates a master clock output up to 96 MHz (programmable). By default, at power-up the master clock is sourced from the main oscillator until the PLL is ready (locked) and then the CPU may switch to the PLL source under firmware control. The CPU can switch back to the main oscillator source at any time and turn off the PLL for low-power operation. The PLL is always turned off in Sleep mode.

- RTC (f<sub>RTC</sub>). A 32.768 kHz external crystal can be connected to pins X1\_RTC and X2\_RTC, or an external oscillator connected to pin X1\_RTC to constantly run the real-time clock unit. This 32.768 kHz clock source can also be used as an input to the CCU to run the CPU in slow clock mode for reduced power.

As an option, there are a number of peripherals that do not have to receive a clock sourced from the CCU. The USB interface can receive an external clock on pin P2.7, TIM timers TIM0/ TIM1 can receive an external clock on pin P2.4, and timers TIM2/TIM3 on pin P2.5.

- Some resets (external reset pin, low-voltage, power-up, JTAG debug command)

- RTC alarm

- Input from wake-up unit

# 2.12 Voltage supplies

The STR91xF requires two separate operating voltage supplies. The CPU and memories operate from a 1.65V to 2.0V on the VDD pins, and the I/O ring operates at 2.7V to 3.6V on the VDDQ pins.

## 2.12.1 Independent A/D converter supply and reference voltage

The ADC unit on 128-pin packages has an isolated analog voltage supply input at pin AVDD to accept a very clean voltage source, independent of the digital voltage supplies. The analog voltage supply range on pin AVDD is the same range as the digital voltage supply on pin VDDQ. Additionally, an isolated analog supply ground connection is provided on pin AVSS only on 128-pin packages for further ADC supply isolation. On 80-pin packages, the analog voltage supply is shared with the ADC reference voltage pin (as described next), and the analog ground is shared with the digital ground at a single point in the STR91xF device on pin AVSS\_VSSQ.

A separate external analog reference voltage input for the ADC unit is available on 128-pin packages at the AVREF pin for better accuracy on low voltage inputs, and the voltage on AVREF can range from 1.0V to  $V_{DDQ}$ . For 80-pin packages, the ADC reference voltage is tied internally to the ADC unit supply voltage at pin AVCC\_AVREF, meaning the ADC reference voltage is fixed to the ADC unit supply voltage.

## 2.12.2 Battery supply

An optional stand-by voltage from a battery or other source may be connected to pin VBATT to retain the contents of SRAM in the event of a loss of the  $V_{DD}$  supply. The SRAM will automatically switch its supply from the internal  $V_{DD}$  source to the VBATT pin when the voltage of  $V_{DD}$  drops below that of VBATT.

The VBATT pin also supplies power to the RTC unit, allowing the RTC to function even when the main digital supplies (V<sub>DD</sub> and V<sub>DDQ</sub>) are switched off. By configuring the RTC register, it is possible to select whether or not to power from VBATT only the RTC unit, or power the RTC unit and the SRAM when the STR91xF device is powered off.

# 2.21 I<sup>2</sup>C interfaces with DMA

The STR91xF supports two independent I2C serial interfaces, designated I2C0, and I2C1. Each interface allows direct connection to an I2C bus as either a bus master or bus slave device (firmware configurable). I2C is a two-wire communication channel, having a bidirectional data signal and a single-directional clock signal based on open-drain line drivers, requiring external pull-up resistors.

Byte-wide data is transferred between a Master device and a Slave device on two wires. More than one bus Master is allowed, but only one Master may control the bus at any given time. Data is not lost when another Master requests the use of a busy bus because I2C supports collision detection and arbitration. More than one Slave device may be present on the bus, each having a unique address. The bus Master initiates all data movement and generates the clock that permits the transfer. Once a transfer is initiated by the Master, any device that is addressed is considered a Slave. Automatic clock synchronization allows I2C devices with different bit rates to communicate on the same physical bus. A single device can play the role of Master or Slave, or a single device can be a Slave only. A Master or Slave device has the ability to suspend data transfers if the device needs more time to transmit or receive data.

Each I2C interface on the STR91xF has the following features:

- Programmable clock supports various rates up to I2C Standard rate (100 KHz) or Fast rate (400 KHz).

- Serial I/O Engine (SIOE) takes care of serial/parallel conversion; bus arbitration; clock generation and synchronization; and handshaking

- Multi-master capability

- 7-bit or 10-bit addressing

## 2.21.1 DMA

A programmable DMA channel may be assigned by CPU firmware to service each I2C channel for fast and direct transfers between the I2C bus and SRAM with little CPU involvement. Both DMA single-transfers and DMA burst-transfers are supported for transmit and receive.

ete.

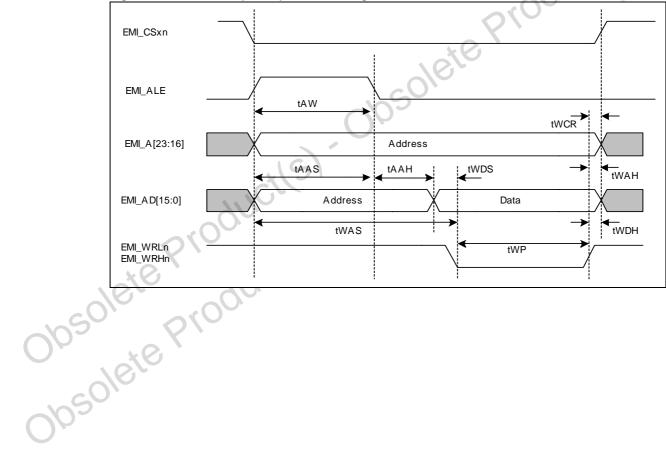

# 2.22 SSP interfaces (SPI, SSI, and Microwire) with DMA

The STR91xF supports two independent Synchronous Serial Port (SSP) interfaces, designated SSP0, and SSP1. Primary use of each interface is for supporting the industry standard Serial Peripheral Interface (SPI) protocol, but also supporting the similar Synchronous Serial Interface (SSI) and Microwire communication protocols.

SPI is a three or four wire synchronous serial communication channel, capable of full-duplex operation. In three-wire configuration, there is a clock signal, and two data signals (one data signal from Master to Slave, the other from Slave to Master). In four-wire configuration, an additional Slave Select signal is output from Master and received by Slave.

The SPI clock signal is a gated clock generated from the Master and regulates the flow of data bits. The Master may transmit at a variety of baud rates, up to 24 MHz

In multi-Slave operation, no more than one Slave device can transmit data at any given time. Slave selection is accomplished when a Slave's "Slave Select" input is permanently grounded or asserted active-low by a Master device. Slave devices that are not selected do not interfere with SPI activities. Slave devices ignore the clock signals and keep their data output pins in

| Ρ        | kg       |                 | be          |                                         |                                       |                                             | Alternate                           | e functions                                |                                         |

|----------|----------|-----------------|-------------|-----------------------------------------|---------------------------------------|---------------------------------------------|-------------------------------------|--------------------------------------------|-----------------------------------------|

| LQFP80   | LQFP128  | Pin Name        | Signal Type | Default Pin<br>Function                 | Default Input<br>Function             | Alternate<br>Input 1                        | Alternate<br>Output 1               | Alternate<br>Output 2                      | Alternate<br>Output 3                   |

| 43       | 68       | P3.7            | I/O         | GPIO_3.7,<br>GP Input, HiZ              | EXINT7,<br>External Intr              | SSP1_NSS,<br>SSP slv select in              | GPIO_3.7,<br>GP Output              | SSP1_NSS,<br>SSP mstr sel out              | TIM1_OCMP1, C<br>comp/PWM               |

| 4        | 3        | P4.0            | I/O         | GPIO_4.0,<br>GP Input, HiZ              | ADC0,<br>ADC input chnl               | TIM0_ICAP1,<br>Input Capture                | GPIO_4.0,<br>GP Output              | TIM0_OCMP1, Out<br>comp/PWM                | ETM_PCK0, ET<br>Packet                  |

| 3        | 2        | P4.1            | I/O         | GPIO_4.1,<br>GP Input, HiZ              | ADC1,<br>ADC input chnl               | TIM0_ICAP2,<br>Input Capture                | GPIO_4.1,<br>GP Output              | TIM0_OCMP2, Out comp                       | ETM_PCK1, ET<br>Packet                  |

| 2        | 1        | P4.2            | I/O         | GPIO_4.2,<br>GP Input, HiZ              | ADC2,<br>ADC input chnl               | TIM1_ICAP1,<br>Input Capture                | GPIO_4.2,<br>GP Output              | TIM1_OCMP1, Out<br>comp/PWM                | ETM_PCK2, ET<br>Packet                  |

| 1        | 128      | P4.3            | I/O         | GPIO_4.3,<br>GP Input, HiZ              | ADC3,<br>ADC input chnl               | TIM1_ICAP2,<br>Input Capture                | GPIO_4.3,<br>GP Output              | TIM1_OCMP2, Out<br>comp                    | ETM_PCK3, ET<br>Packet                  |

| 80       | 127      | P4.4            | I/O         | GPIO_4.4,<br>GP Input, HiZ              | ADC4,<br>ADC input chnl               | TIM2_ICAP1,<br>Input Capture                | GPIO_4.4,<br>GP Output              | TIM2_OCMP1, Out<br>comp/PWM                | ETM_PSTAT0,<br>ETM pipe statu           |

| 79       | 126      | P4.5            | I/O         | GPIO_4.5,<br>GP Input, HiZ              | ADC5,<br>ADC input chnl               | TIM2_ICAP2,<br>Input Capture                | GPIO_4.5,<br>GP Output              | TIM2_OCMP2, Out<br>comp                    | ETM_PSTAT1,<br>ETM pipe statu           |

| 78       | 125      | P4.6            | I/O         | GPIO_4.6,<br>GP Input, HiZ              | ADC6,<br>ADC input chnl               | TIM3_ICAP1,<br>Input Capture                | GPIO_4.6,<br>GP Output              | TIM3_OCMP1, Out<br>comp/PWM                | ETM_PSTAT2<br>ETM pipe statu            |

| 77       | 124      | P4.7            | I/O         | GPIO_4.7,<br>GP Input, HiZ              | ADC7,<br>ADC input chnl               | TIM3_ICAP2,<br>Input Capture                | GPIO_4.7,<br>GP Output              | TIM3_OCMP2, Out<br>comp                    | ETM_TRSYNC<br>ETM trace syn             |

| 9        | 12       | P5.0            | I/0         | GPIO_5.0,<br>GP Input, HiZ              | EXINT8,<br>External Intr              | CAN_RX,<br>CAN rcv data                     | GPIO_5.0,<br>GP Output              | ETM_TRCLK,<br>ETM trace clock              | UART0_TX,<br>UART xmit dat              |

| 12       | 18       | P5.1            | I/0         | GPIO_5.1,<br>GP Input, HiZ              | EXINT9,<br>External Intr              | UART0_RxD,<br>UART rcv data                 | GPIO_5.1,<br>GP Output              | CAN_TX,<br>CAN Tx data                     | UART2_TX,<br>UART xmit dat              |

| 17       | 25       | PHYCLK<br>_P5.2 | I/O         | GPIO_5.2,<br>GP Input, HiZ              | EXINT10,<br>External Intr             | UART2_RxD,<br>UART rcv data                 | GPIO_5.2,<br>GP Output              | MII_PHYCLK,<br>25Mhz to PHY                | TIM3_OCMP1, C<br>comp/PWM               |

| 18       | 27       | P5.3            | I/O         | GPIO_5.3,<br>GP Input, HiZ              | EXINT11,<br>External Intr             | ETM_EXTRIG,<br>ETM ext. trigger             | GPIO_5.3,<br>GP Output              | MII_TX_EN,<br>MAC xmit enbl                | TIM2_OCMP1, C<br>comp/PWM               |

| 44       | 70       | P5.4            | I/O         | GPIO_5.4,<br>GP Input, HiZ              | EXINT12,<br>External Intr             | SSP0_SCLK,<br>SSP slv clk in                | GPIO_5.4,<br>GP Output              | SSP0_SCLK,<br>SSP mstr clk out             | EMI_CS0n,<br>EMI Chip Sele              |

| 47       | 77       | P5.5            | I/O         | GPIO_5.5,<br>GP Input, HiZ              | EXINT13,<br>External Intr             | SSP0_MOSI,<br>SSP slv dat in                | GPIO_5.5,<br>GP Output              | SSP0_MOSI,<br>SSP mstr dat out             | EMI_CS1n,<br>EMI Chip Sele              |

| 48       | 79       | P5.6            | 1/0         | GPIO_5.6,<br>GP Input, HiZ<br>GPIO_5.7, | EXINT14,<br>External Intr             | SSP0_MISO,<br>SSP mstr dat in               | GPIO_5.6,<br>GP Output              | SSP0_MISO,<br>SSP slv data out             | EMI_CS2n,<br>EMI Chip Sele<br>EMI CS3n, |

| 49       | 80       | P5.7            | I/O         | GPI0_5.7,<br>GP Input, HiZ              | EXINT15,<br>External Intr             | SSP0_NSS,<br>SSP slv select in              | GPIO_5.7,<br>GP Output              | SSP0_NSS,<br>SSP mstr sel out              | EMI_CS3N,<br>EMI Chip Sele              |

| 19       | 29       | P6.0            | 1/0         | GPIO_6.0,<br>GP Input, HiZ              | EXINT16,<br>External Intr<br>EXINT17, | TIM0_ICAP1,<br>Input Capture                | GPIO_6.0,<br>GP Output              | TIM0_OCMP1, Out<br>comp/PWM                | MC_UH,<br>IMC phase U I                 |

| 20       | 31       | P6.1            | 1/0         | GPIO_6.1,<br>GP Input, HiZ<br>GPIO_6.2, | EXINTT7,<br>External Intr<br>EXINT18, | TIM0_ICAP2,<br>Input Capture<br>TIM1_ICAP1, | GPIO_6.1,<br>GP Output<br>GPIO_6.2, | TIM0_OCMP2, Out<br>comp<br>TIM1_OCMP1, Out | MC_UL,<br>IMC phase U I<br>MC VH,       |

| 13       | 19       | P6.2            | I/O         | GP Input, HiZ<br>GPIO_6.3,              | External Intr<br>EXINT19,             | Input Capture<br>TIM1_ICAP2,                | GP Output<br>GPIO_6.3,              | TIM1_OCMP2, Out                            | IMC phase V I<br>MC_VL,                 |

| 14       | 20       | P6.3            | 1/0         | GP Input, HiZ<br>GPIO_6.4,              | External Intr<br>EXINT20,             | Input Capture<br>TIM2_ICAP1,                | GP Output<br>GPIO_6.4,              | TIM2_OCMP1, Out                            | IMC phase V<br>MC_WH,                   |

| 52       | 83       | P6.4            | 1/0         | GP Input, HiZ<br>GPIO_6.5,              | External Intr<br>EXINT21,             | Input Capture<br>TIM2_ICAP2,                | GP Output<br>GPIO_6.5,              | comp/PWM<br>TIM2_OCMP2, Out                | IMC phase W<br>MC_WL,                   |

| 53       | 84       | P6.5            | 1/0         | GP Input, HiZ<br>GPIO_6.6,              | External Intr<br>EXINT22_TRIG,        | Input Capture<br>UART0_RxD,                 | GP Output<br>GPIO_6.6,              | Comp<br>TIM3_OCMP1, Out                    | IMC phase W<br>ETM_TRCLK                |

| 57<br>58 | 92<br>93 | P6.6<br>P6.7    | 1/O<br>1/O  | GP Input, HiZ<br>GPIO_6.7,              | Ext Intr & Tach<br>EXINT23_STOP,      | UART rcv data<br>ETM_EXTRIG,                | GP Output<br>GPIO_6.7,              | comp/PWM<br>TIM3_OCMP2, Out                | ETM trace cloo<br>UART0_TX,             |

| 58       | 93       | P0.7            | 1/0         | GP Input, HiZ                           | Ext Intr & Estop                      | ETM ext. trigger                            | GP Output                           | сотр                                       | UART xmit dat                           |

| Ρ      | kg      |                                                            | be          |                                                                                       |                           |                      | Alternate             | e functions           |                       |

|--------|---------|------------------------------------------------------------|-------------|---------------------------------------------------------------------------------------|---------------------------|----------------------|-----------------------|-----------------------|-----------------------|

| LQFP80 | LQFP128 | Pin Name                                                   | Signal Type | Default Pin<br>Function                                                               | Default Input<br>Function | Alternate<br>Input 1 | Alternate<br>Output 1 | Alternate<br>Output 2 | Alternate<br>Output 3 |

| -      | 21      | EMI_BWR<br>_WRLn<br>(used as<br>EMI_LBn in<br>future rev.) | 0           | EMI byte write<br>strobe (8 bit<br>mode) or low<br>byte write strobe<br>(16 bit mode) |                           |                      | N/A                   |                       |                       |

| -      | 22      | EMI_WRHn<br>(used as<br>EMI_UBn in<br>future rev.)         | ο           | EMI high byte<br>write strobe (16-<br>bit mode)                                       |                           |                      | N/A                   |                       |                       |

| -      | 74      | EMI_ALE                                                    | 0           | EMI address<br>latch enable<br>(mux mode)                                             |                           |                      | N/A                   |                       | 16)                   |

| -      | 75      | EMI_RDn                                                    | 0           | EMI read strobe                                                                       |                           |                      | N/A                   |                       | XU                    |

| -      | -       | EMI_BAAn                                                   | 0           | TBD                                                                                   |                           |                      | N/A                   |                       |                       |

| -      | -       | EMI_WAITn                                                  |             | TBD                                                                                   |                           |                      | N/A                   |                       |                       |

| -      | -       | EMI_BCLK                                                   | 0           | TBD<br>Reserved for                                                                   |                           |                      | N/A                   |                       |                       |

| -      | -       | EMI_WEn                                                    | 0           | future use                                                                            |                           |                      | N/A                   |                       | .(9)                  |

| -      | 91      | _IN                                                        | I           | input<br>MAC/PHY                                                                      |                           |                      | N/A                   |                       | <u>C</u>              |

| -      | 94      | MII_MDIO                                                   | I/O         | management<br>data line                                                               |                           |                      | N/A                   | du                    |                       |

| 59     | 95      | USBDN                                                      | I/O         | USB data (-) bus<br>connect                                                           |                           | ~nS'                 | N/A                   | 210                   |                       |

| 60     | 96      | USBDP                                                      | I/O         | USB data (+) bus<br>connect                                                           |                           | 04                   | N/A                   |                       |                       |

| 56     | 89      | RESET<br>_INn                                              | Ι           | External reset<br>input                                                               |                           |                      | N/A                   |                       |                       |

| 62     | 100     | RESET<br>_OUTn                                             | 0           | Global or System<br>reset output                                                      | 191                       | S                    | N/A                   |                       |                       |

| 65     | 104     | X1_CPU                                                     | I           | CPU oscillator or<br>crystal input                                                    |                           | Ov                   | N/A                   |                       |                       |

| 64     | 103     | X2_CPU                                                     | 0           | CPU crystal<br>connection                                                             |                           | ¢                    | N/A                   |                       |                       |

| 27     | 42      | X1_RTC                                                     | I           | RTC oscillator or<br>crystal input<br>(32.768 kHz)                                    | de                        |                      | N/A                   |                       |                       |

| 26     | 41      | X2_RTC                                                     | 0           | RTC crystal<br>connection                                                             |                           |                      | N/A                   |                       |                       |

| 61     | 97      | JRTCK                                                      | 0           | JTAG return<br>clock or RTC<br>clock                                                  |                           |                      | N/A                   |                       |                       |

| 67     | 107     | JTRSTn                                                     | T           | JTAG TAP<br>controller reset                                                          |                           |                      | N/A                   |                       |                       |

| 68     | 108     | JTCK                                                       | Ι           | JTAG clock                                                                            |                           |                      | N/A                   |                       |                       |

| 69     | 111     | JTMS                                                       | I           | JTAG mode select                                                                      |                           |                      | N/A                   |                       |                       |

| 72     | 115     | JTDI                                                       | Т           | JTAG data in                                                                          |                           |                      | N/A                   |                       |                       |

| 73     | 117     | JTDO                                                       | 0           | JTAG data out                                                                         |                           |                      | N/A                   |                       |                       |

| -      | 122     | AVDD                                                       | v           | ADC analog<br>voltage source,<br>2.7V - 3.6V                                          |                           |                      | N/A                   |                       |                       |

| -      | 4       | AVSS                                                       | G           | ADC analog<br>ground                                                                  |                           |                      | N/A                   |                       |                       |

| 5      | -       | AVSS<br>_VSSQ                                              | G           | Common ground<br>point for digital I/<br>O & analog ADC                               |                           |                      | N/A                   |                       |                       |

When other AHB bus masters (such as a DMA controller) write to SRAM, their access is never buffered. Only the CPU can make use of buffered AHB writes.

# 5.4 Two independent Flash memories

The STR91xF has two independent Flash memories, the larger primary Flash and the small secondary Flash. It is possible for the CPU to erase/write to one of these Flash memories while simultaneously reading from the other.

One or the other of these two Flash memories may reside at the "boot" address position of 0x0000.0000 at power-up or at reset as shown in *Figure 9*. The default configuration is that the first sector of primary Flash memory is enabled and residing at the boot position, and the secondary Flash memory is disabled. This default condition may be optionally changed as described below.

# 5.4.1 Default configuration

When the primary Flash resides at boot position, typical CPU initialization firmware would set the start address and size of the main Flash memory, and go on to enable the secondary Flash, define it's start address and size. Most commonly, firmware would place the secondary Flash start address at the location just after the end of the primary Flash memory. In this case, the primary Flash is used for code storage, and the smaller secondary flash can be used for data storage (EEPROM emulation).

# 5.4.2 Optional configuration

Using the STR91xF device configuration software tool, or IDE from 3rd party, one can specify that the smaller secondary Flash memory is at the boot location at reset and the primary Flash is disabled. The selection of which Flash memory is at the boot location is programmed in a non-volatile Flash-based configuration bit during JTAG ISP. The boot selection choice will remain as the default until the bit is erased and re-written by the JTAG interface. The CPU cannot change this choice for boot Flash, only the JTAG interface has access.

In this case where the secondary Flash defaults to the boot location upon reset, CPU firmware would typically initialize the Flash memories the following way. The secondary Flash start address and size is specified, then the primary Flash is enabled and its start address and size is specified. The primary Flash start address would typically be located just after the final address location of the secondary Flash. This configuration is particularly well-suited for In-Application-Programming (IAP). The CPU would boot from the secondary Flash memory, initialize the system, then check the contents of the primary Flash memory (by checksum or other means). If the contents of primary Flash is OK, then CPU execution continues from either Flash memory. If the main Flash contents are incorrect, the CPU, while executing code from the secondary Flash, can download new data from any STR91xF communication channel and program into primary Flash memory. Application code then starts after the new contents of primary Flash are verified.

# 6.2 Operating conditions

| Symbol                           | Parameter                                                                   | Test       | Va   | lue | Unit |

|----------------------------------|-----------------------------------------------------------------------------|------------|------|-----|------|

| Symbol                           | Faiametei                                                                   | Conditions | Min  | Max | Onic |

| V <sub>DD</sub>                  | Digital CPU supply voltage                                                  |            | 1.65 | 2.0 | V    |

| V <sub>DDQ</sub>                 | Digital I/O supply voltage                                                  |            | 2.7  | 3.6 | V    |

| V <sub>BATT</sub> <sup>(1)</sup> | SRAM backup and RTC supply voltage                                          |            | 2.5  | 3.6 | V    |

| AV <sub>DD</sub>                 | Analog ADC supply voltage (128-pin package)                                 |            | 2.7  | 3.6 | ×    |

| AV <sub>REF</sub>                | Analog ADC reference voltage (128-pin package)                              |            | 1.0  | 3.6 | S    |

| AV <sub>REF_AVDD</sub>           | Combined analog ADC<br>reference and ADC supply<br>voltage (80-pin package) |            | 2.7  | 3.6 | v    |

| T <sub>A</sub>                   | Ambient temperature under bias                                              |            | -40  | +85 | c    |

Table 5. Operating conditions

Notes: 1 The  $V_{BATT}$  pin should be connected to  $V_{DDQ}$  if no battery is installed

# 6.3 LVD electrical characteristics

$V_{DDQ}$  = 2.7 - 3.6V,  $V_{DD}$  = 1.65 - 2V,  $T_A$  = -40 / 85 °C unless otherwise specified.

| Symbol               | Parameter                                      | Test |      | Value |      | Unit |

|----------------------|------------------------------------------------|------|------|-------|------|------|

| Symbol               | Condit                                         |      | Min  | Тур   | Max  | Onit |

| V <sub>DD_LVD</sub>  | V <sub>DD</sub> LVD Threshold                  |      | 1.35 | 1.4   | 1.45 | V    |

| V <sub>DDQ_LVD</sub> | V <sub>DDO</sub> LVD Threshold                 | (1)  | 2.35 | 2.4   | 2.45 | V    |

| DDQ_EVD              | VDDQ LVD Hireshold                             | (2)  | 2.65 | 2.7   | 2.75 |      |

| V <sub>DD_BRN</sub>  | V <sub>DD</sub> Brown Out Warning<br>Threshold |      | 1.6  | 1.65  | 1.7  | V    |

| V <sub>DDQ_BRN</sub> | V <sub>DDQ</sub> Brown Out Warning             | (1)  | 2.6  | 2.65  | 2.7  | V    |

| BRN                  | Threshold                                      | (2)  | 2.9  | 2.95  | 3.0  |      |

# Table 6. LVD Electrical Characteristics

Notes: 1 For VDDQ I/O voltage operating at 2.7 - 3.3V.

- 2 For VDDQ I/O voltage operating at 3.0 3.6V.

- 3 Selection of V<sub>DDQ</sub> operation range is made using configuration software from ST, or IDE from 3rd parties. The default condition is V<sub>DDQ</sub>=2.7V 3.3V.

#### 6.4 **DC** electrical characteristics

$V_{DDQ}$  = 2.7 - 3.6V,  $V_{DD}$  = 1.65 - 2V,  $T_A$  = -40 / 85 °C unless otherwise specified.

| Symbol         Parameter         Test Conductors         Min         Typ         Max           V <sub>IH</sub> Input High Level         General inputs         2.0         (1)           V <sub>IL</sub> Input Low Level         General inputs         0.8V <sub>DDO</sub> 0.8           V <sub>HYS</sub> Input Hysteresis<br>Schmitt Trigger         General inputs         0.4         0.2V <sub>DDO</sub> V <sub>HYS</sub> Output High Level<br>High current pins         I/O ports 3 and 6:<br>Push-Pull, I <sub>OH</sub> = 8mA         V <sub>DDO</sub> -0.7         0.4           V <sub>OH</sub> Output High Level<br>High current pins         I/O ports 0,1,2,4,5,7,8,9:<br>Push-Pull, I <sub>OH</sub> = 4mA         V <sub>DDO</sub> -0.7         0.4           V <sub>OL</sub> Output Low Level<br>High current pins         I/O ports 0,1,2,4,5,7,8,9:<br>Push-Pull, I <sub>OL</sub> = 8mA         0.4         0.4           Notes: 1         Input pins are 5V tolerant, max input voltage is 5.5V         0.4         0.4         0.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Symbol      | Parameter Test Conditions |                                  |                       | Value |              | Unit |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------------------|----------------------------------|-----------------------|-------|--------------|------|--|

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Symbol      | Farameter                 | Test conditions                  | Min                   | Тур   | Max          | Uni  |  |

| $\begin{split} & RESE1 \text{ and 1CK inputs} & 0.8 V_{\text{DDQ}} & \mathbf{CR} \\ \hline RESE1 \text{ and 1CK inputs} & 0.8 V_{\text{DDQ}} & \mathbf{CR} \\ \hline V_{\text{IL}} & Input Low Level & \mathbf{CR} & General inputs & \mathbf{CR} & $ |             |                           | General inputs                   | 2.0                   |       | (1)          |      |  |

| VILInput Low LevelRESET and TCK inputs0.2V_{DDQ}V_HYSInput Hysteresis<br>Schmitt TriggerGeneral inputs0.40.2V_{DDQ}V_HYSOutput High Level<br>High current pinsI/O ports 3 and 6:<br>Push-Pull, I_OH = 8mAV_DDQ-0.70.4VOHOutput High Level<br>Standard current pinsI/O ports 0,1,2,4,5,7,8,9:<br>Push-Pull, I_OH = 4mAV_DDQ-0.70.4VOLOutput Low Level<br>High current pinsI/O ports 3 and 6:<br>Push-Pull, I_OH = 8mA0.40.4VOLOutput Low Level<br>High current pinsI/O ports 3 and 6:<br>Push-Pull, I_OL = 8mA0.40.4VOLOutput Low Level<br>High current pinsI/O ports 0,1,2,4,5,7,8,9:<br>Push-Pull, I_OL = 8mA0.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Н           | Input High Level          | RESET and TCK inputs             | 0.8V <sub>DDQ</sub>   |       |              |      |  |

| VHYSInput Hysteresis<br>Schmitt TriggerGeneral inputs0.4V_HYSInput Hysteresis<br>Schmitt TriggerGeneral inputs0.4VOHOutput High Level<br>High current pinsI/O ports 3 and 6:<br>Push-Pull, I <sub>OH</sub> = 8mAV_DDQ^-0.7Output High Level<br>Standard current pinsI/O ports 0,1,2,4,5,7,8,9:<br>Push-Pull, I <sub>OH</sub> = 4mAV_DDQ^-0.7VOLOutput Low Level<br>High current pinsI/O ports 3 and 6:<br>Push-Pull, I <sub>OH</sub> = 8mAV_DDQ^-0.7Output Low Level<br>High current pinsI/O ports 3 and 6:<br>Push-Pull, I <sub>OL</sub> = 8mA0.4Output Low Level<br>High current pinsI/O ports 0,1,2,4,5,7,8,9:<br>Push-Pull, I <sub>OL</sub> = 8mA0.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |                           | General inputs                   |                       |       | 0.8          | V    |  |

| VHYSSchmitt TriggerGeneral inputs0.4VOHOutput High Level<br>High current pinsI/O ports 3 and 6:<br>Push-Pull, I <sub>OH</sub> = 8mA $V_{DDQ}$ -0.7Output High Level<br>Standard current pinsI/O ports 0,1,2,4,5,7,8,9:<br>Push-Pull, I <sub>OH</sub> = 4mA $V_{DDQ}$ -0.7VOLOutput Low Level<br>High current pinsI/O ports 3 and 6:<br>Push-Pull, I <sub>OH</sub> = 8mA $V_{DDQ}$ -0.7Output Low Level<br>High current pinsI/O ports 3 and 6:<br>Push-Pull, I <sub>OL</sub> = 8mA0.4Output Low Level<br>High current pinsI/O ports 0,1,2,4,5,7,8,9:<br>Push-Pull, I <sub>OL</sub> = 8mA0.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | L           | Input Low Level           | RESET and TCK inputs             |                       |       | $0.2V_{DDQ}$ |      |  |

| VOHHigh current pinsPush-Pull, $I_{OH} = 8mA$ $V_{DDQ}$ -0.7Output High Level<br>Standard current pinsI/O ports 0,1,2,4,5,7,8,9:<br>Push-Pull, $I_{OH} = 4mA$ $V_{DDQ}$ -0.7VOLOutput Low Level<br>High current pinsI/O ports 3 and 6:<br>Push-Pull, $I_{OL} = 8mA$ 0.4Output Low Level<br>Standard current pinsI/O ports 0,1,2,4,5,7,8,9:<br>Push-Pull, $I_{OL} = 4mA$ 0.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |                           | General inputs                   | 0.4                   |       |              | 5,   |  |

| Output High Level<br>Standard current pins       I/O ports 0,1,2,4,5,7,8,9:<br>Push-Pull, I <sub>OH</sub> = 4mA       V <sub>DDQ</sub> -0.7         Output Low Level<br>High current pins       I/O ports 3 and 6:<br>Push-Pull, I <sub>OL</sub> = 8mA       0.4         Output Low Level<br>Standard current pins       I/O ports 0,1,2,4,5,7,8,9:<br>Push-Pull, I <sub>OL</sub> = 8mA       0.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |                           |                                  | V <sub>DDQ</sub> -0.7 |       |              |      |  |

| VOLHigh current pinsPush-Pull, IOL = 8mA0.4Output Low Level<br>Standard current pinsI/O ports 0,1,2,4,5,7,8,9:<br>Push-Pull, IOL = 4mA0.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |                           |                                  | V <sub>DDQ</sub> -0.7 | 510,  | -+[          | 5    |  |