Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

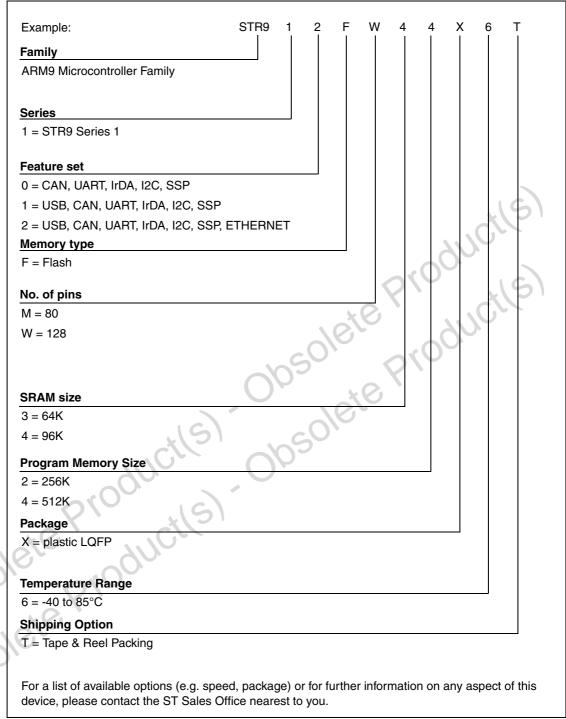

| Product Status             | Obsolete                                                                                     |

|----------------------------|----------------------------------------------------------------------------------------------|

| Core Processor             | ARM9®                                                                                        |

| Core Size                  | 16/32-Bit                                                                                    |

| Speed                      | 96MHz                                                                                        |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, Microwire, SPI, SSI, SSP, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                                |

| Number of I/O              | 80                                                                                           |

| Program Memory Size        | 512KB (512K x 8)                                                                             |

| Program Memory Type        | FLASH                                                                                        |

| EEPROM Size                | -                                                                                            |

| RAM Size                   | 96K x 8                                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 2V                                                                                   |

| Data Converters            | A/D 8x10b                                                                                    |

| Oscillator Type            | Internal                                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                            |

| Mounting Type              | Surface Mount                                                                                |

| Package / Case             | 128-LQFP                                                                                     |

| Supplier Device Package    | -                                                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/str912fw44x6                         |

|                            |                                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|     |      | 2.10.11 Operation example                                     | . 16 |

|-----|------|---------------------------------------------------------------|------|

|     | 2.11 | Flexible power management                                     | 17   |

|     |      | 2.11.1 Run mode                                               | . 17 |

|     |      | 2.11.2 Idle mode                                              | . 17 |

|     |      | 2.11.3 Sleep mode                                             | . 17 |

|     | 2.12 | Voltage supplies                                              | 18   |

|     |      | 2.12.1 Independent A/D converter supply and reference voltage | . 18 |

|     |      | 2.12.2 Battery supply                                         | . 18 |

|     | 2.13 | System supervisor                                             | 19   |

|     |      | 2.13.1 Supply voltage brownout                                | . 19 |

|     |      | 2.13.2 Supply voltage dropout                                 | . 19 |

|     |      | 2.13.3 Watchdog timer                                         | . 19 |

|     |      | 2.13.4 External RESET_INn pin      2.13.5 Power-up            | . 20 |

|     |      | 2.13.5 Power-up                                               | . 20 |

|     |      | 2.13.6 JTAG debug command                                     | . 20 |

|     |      | 2.13.7 Tamper detection                                       | . 20 |

|     | 2.14 | Real-time clock (RTC)     JTAG interface                      | 20   |

|     | 2.15 | JTAG interface                                                | 21   |

|     |      | 2.15.1 In-system-programming                                  | . 22 |

|     |      | 2.15.2 Boundary scan                                          | . 22 |

|     |      | 2.15.3 CPU debug                                              |      |

|     |      | 2.15.4 JTAG security bit                                      |      |

|     | 2.16 | Embedded trace module (ARM ETM9, v. r2p2)                     | 23   |

|     | 2.17 | Ethernet MAC interface with DMA                               | 24   |

|     | 2.18 | USB 2.0 slave device interface with DMA                       | 24   |

| SC  | )`   | 2.18.1 Packet buffer interface (PBI)                          | . 25 |

| 005 | . (  | 2.18.2 DMA                                                    | . 25 |

|     | 01   | 2.18.3 Suspend mode                                           | . 25 |

| ~   | 2.19 | CAN 2.0B interface                                            | 25   |

| ~05 | 2.20 | UART interfaces with DMA                                      | 26   |

| 0   |      | 2.20.1 DMA                                                    | . 26 |

|     | 2.21 | I2C interfaces with DMA                                       | 27   |

|     |      | 2.21.1 DMA                                                    | . 27 |

|     | 2.22 | SSP interfaces (SPI, SSI, and Microwire) with DMA             | 27   |

|     |      | 2.22.1 DMA                                                    | . 28 |

# 2.10 Clock control unit (CCU)

The CCU generates a master clock of frequency  $f_{MSTR}$ . From this master clock the CCU also generates individually scaled and gated clock sources to each of the following functional blocks within the STR91xF.

- CPU, f<sub>CPUCLK</sub>

- Advanced High-performance Bus (AHB), f<sub>HCLK</sub>

- Advanced Peripheral Bus (APB), f<sub>PCLK</sub>

- Flash Memory Interface (FMI), f<sub>FMICLK</sub>

- External Memory Interface (EMI), f<sub>BCLK</sub>

- UART Baud Rate Generators, f<sub>BAUD</sub>

- USB, f<sub>USB</sub>

#### 2.10.1 Master clock sources

The master clock in the CCU (f<sub>MSTR</sub>) is derived from one of three clock input sources. Under firmware control, the CPU can switch between the three CCU inputs without introducing any glitches on the master clock output. Inputs to the CCU are:

- Main Oscillator (f<sub>OSC</sub>). The source for the main oscillator input is a 4 to 25 MHz external crystal connected to STR91xF pins X1\_CPU and X2\_CPU, or an external oscillator device connected to pin X1\_CPU.

- PLL (f<sub>PLL</sub>). The PLL takes the 4 to 25 MHz oscillator clock as input and generates a master clock output up to 96 MHz (programmable). By default, at power-up the master clock is sourced from the main oscillator until the PLL is ready (locked) and then the CPU may switch to the PLL source under firmware control. The CPU can switch back to the main oscillator source at any time and turn off the PLL for low-power operation. The PLL is always turned off in Sleep mode.

- RTC (f<sub>RTC</sub>). A 32.768 kHz external crystal can be connected to pins X1\_RTC and X2\_RTC, or an external oscillator connected to pin X1\_RTC to constantly run the real-time clock unit. This 32.768 kHz clock source can also be used as an input to the CCU to run the CPU in slow clock mode for reduced power.

As an option, there are a number of peripherals that do not have to receive a clock sourced from the CCU. The USB interface can receive an external clock on pin P2.7, TIM timers TIM0/ TIM1 can receive an external clock on pin P2.4, and timers TIM2/TIM3 on pin P2.5.

# 2.11 Flexible power management

The STR91xF offers configurable and flexible power management control that allows the user to choose the best power option to fit the application. Power consumption can be dynamically managed by firmware and hardware to match the system's requirements. Power management is provided via clock control to the CPU and individual peripherals.

Clocks to the CPU and peripherals can be individually divided and gated off as needed. In addition to individual clock divisors, the CCU master clock source going to the CPU, AHB, APB, EMI, and FMI can be divided dynamically by as much as 1024 for low power operation. Additionally, the CCU may switch its input to the 32.768 kHz RTC clock at any time for low power.

The STR91xF supports the following three global power control modes:

- Run Mode: All clocks are on with option to gate individual clocks off via clock mask registers.

- Idle Mode: CPU and FMI clocks are off until an interrupt, reset, or wake-up occurs. Preconfigured clock mask registers selectively allow individual peripheral clocks to continue run during Idle Mode.

- Sleep Mode: All clocks off except RTC clock. Wake up unit remains powered, PLL is forced off.

A special mode is used when JTAG debug is active which never gates off any clocks even if the CPU enters Idle or Sleep mode.

#### 2.11.1 Run mode

This is the default mode after any reset occurs. Firmware can gate off or scale any individual clock. Also available is a special Interrupt Mode which allows the CPU to automatically run full speed during an interrupt service and return back to the selected CPU clock divisor rate when the interrupt has been serviced. The advantage here is that the CPU can run at a very low frequency to conserve power until a periodic wake-up event or an asynchronous interrupt occurs at which time the CPU runs full speed immediately.

#### 2.11.2 Idle mode

In this mode the CPU suspends code execution and the CPU and FMI clocks are turned off immediately after firmware sets the Idle Bit. Various peripherals continue to run based on the settings of the mask registers that exist just prior to entering Idle Mode. There are 3 ways to exit Idle Mode and return to Run Mode:

- Any reset (external reset pin, watchdog, low-voltage, power-up, JTAG debug command)

- Any interrupt (external, internal peripheral, RTC alarm or interval)

- Input from wake-up unit on GPIO pins

It is possible to remain in Idle Mode for the majority of the time and the RTC can be programmed to periodically wake up to perform a brief task or check status.

#### 2.11.3 Sleep mode

In this mode all clock circuits except the RTC are turned off and main oscillator input pins X1\_CPU and X2\_CPU are disabled. The RTC clock is required for the CPU to exit Sleep Mode. The entire chip is quiescent (except for RTC and wake-up circuitry). There are three means to exit Sleep Mode and re-start the system:

Note:

peripheral clock from the APB, and an 8-bit clock pre-scaler is available. When enabled by firmware as a watchdog, this timer will cause a system reset if firmware fails to periodically reload this timer before the terminal count of 0x0000 occurs, ensuring firmware sanity. The watchdog function is off by default after a reset and must be enabled by firmware.

#### 2.13.4 External RESET\_INn pin

This input signal is active-low with hystereses ( $V_{RHYS}$ ). Other open-drain, active-low system reset signals on the circuit board (such as closure to ground from a push-button) may be connected directly to the RESET\_INn pin, but an external pull-up resistor to  $V_{DDQ}$  must be present as there is no internal pullup on the RESET\_INn pin.

A valid active-low input signal of  $t_{RINMIN}$  duration on the RESET\_INn pin will cause a system reset within the STR91xF. There is also a RESET\_OUTn pin on the STR91xF that can drive other system components on the circuit board. RESET\_OUTn is active-low and has the same timing of the Power-On-Reset (POR) shown next,  $t_{POR}$ .

#### 2.13.5 Power-up

The LVD circuitry will always generate a global reset when the STR91xF powers up, meaning internal reset is active until  $V_{DDQ}$  and  $V_{DD}$  are both above the LVD thresholds. This POR condition has a duration of  $t_{POR}$ , after which the CPU will fetch its first instruction from address 0x0000.0000 in Flash memory. It is not possible for the CPU to boot from any other source other than Flash memory.

#### 2.13.6 JTAG debug command

When the STR91xF is in JTAG debug mode, an external device which controls the JTAG interface can command a system reset to the STR91xF over the JTAG channel.

#### 2.13.7 Tamper detection

On 128-pin STR91xF devices only, there is a tamper detect input pin, TAMPER\_IN, used to detect and record the time of a tamper event on the end product such as malicious opening of an enclosure, unwanted opening of a panel, etc. The activation mode of the tamper pin is programmable to one of two modes. One is Normally Closed/Tamper Open, the other mode will detect when a signal on the tamper input pin is driven from low-to-high, or high-to-low depending on firmware configuration. Once a tamper event occurs, the RTC time (millisecond resolution) and the date are recorded in the RTC unit. Simultaneously, the SRAM standby voltage source will be cut off to invalidate all SRAM contents. Tamper detection control and status logic are part of the RTC unit.

# 4 Real-time clock (RTC)

The RTC combines the functions of a complete time-of-day clock (millisecond resolution) with an alarm programmable up to one month, a 9999-year calender with leap-year support, periodic interrupt generation from 1 to 512 Hz, tamper detection (described in *Section 2.13.7*), and an optional clock calibration output on the JRTCK pin. The time is in 24 hour mode, and time/calendar values are stored in binary-coded decimal format.

The RTC also provides a self-isolation mode that is automatically activated during power down. This feature allows the RTC to continue operation when  $V_{DDO}$  and  $V_{DD}$  are absent, as long as

an alternate power source, such as a battery, is connected to the VBATT input pin. The current drawn by the RTC unit on the VBATT pin is very low in this standby mode, I<sub>RTC STBY</sub>.

# 2.15 JTAG interface

An IEEE-1149.1 JTAG interface on the STR91xF provides In-System-Programming (ISP) of all memory, boundary scan testing of pins, and the capability to debug the CPU.

STR91xF devices are shipped from ST with blank Flash memories. The CPU can only boot from Flash memory (selection of which Flash bank is programmable). Firmware must be initially programmed through JTAG into one of these Flash memories before the STR91xF is used.

Six pins are used on this JTAG serial interface. The five signals JTDI, JTDO, JTMS, JTCK, and JTRSTn are all standard JTAG signals complying with the IEEE-1149.1 specification. The sixth signal, JRTCK (Return TCK), is an output from the STR91xF and it is used to pace the JTCK clock signal coming in from the external JTAG test equipment for debugging. The frequency of the JTCK clock signal coming from the JTAG test equipment must be at least 10 times less than the ARM966E-S CPU core operating frequency (f<sub>CPUCLK</sub>). To ensure this, the signal JRTCK is output from the STR91xF and is input to the external JTAG test equipment to hold off transitions of JTCK until the CPU core is ready, meaning that the JTAG equipment cannot send the next rising edge of JTCK until the equipment receives a rising edge of JRTCK from the STR91xF. The JTAG test equipment must be able to interpret the signal JRTCK and perform this adaptive clocking function. If it is known that the CPU clock will always be at least ten times faster than the incoming JTCK clock signal, then the JRTCK signal is not needed.

The two die inside the STR91xF (CPU die and Flash memory die) are internally daisy-chained on the JTAG bus, see *Figure 3 on page 22*. The CPU die has two JTAG Test Access Ports (TAPs), one for boundary scan functions and one for ARM CPU debug. The Flash memory die has one TAP for program/erase of non-volatile memory. Because these three TAPs are daisychained, only one TAP will converse on the JTAG bus at any given time while the other two TAPs are in BYPASS mode. The TAP positioning order within this JTAG chain is the boundary scan TAP first, followed by the ARM debug TAP, followed by the Flash TAP. All three TAP controllers are reset simultaneously by one of two methods:

- A chip-level global reset, caused only by a Power-On-Reset (POR) or a Low Voltage Detect (LVD).

- A reset command issued by the external JTAG test equipment. This can be the assertion of the JTAG JTRSTn input pin on the STR91xF or a JTAG reset command shifted into the STR91xF serially.

This means that chip-level system resets from watchdog time-out or the assertion of RESET\_INn pin do not affect the operation of any JTAG TAP controller. Only global resets effect the TAPs.

- Supports USB low and full-speed transfers (12 Mbps), certified to comply with the USB 2.0 specification

- Supports isochronous, bulk, control, and interrupt endpoints

- Configurable number of endpoints allowing a mixture of up to 20 single-buffered monodirectional endpoints or up to 10 double-buffered bidirectional endpoints

- Dedicated, dual-port 2 Kbyte USB Packet Buffer SRAM. One port of the SRAM is connected by a Packet Buffer Interface (PBI) on the USB side, and the CPU connects to the other SRAM port.

- CRC generation and checking

- NRZI encoding-decoding and bit stuffing

- USB suspend resume operations

#### 2.18.1 Packet buffer interface (PBI)

The PBI manages a set of buffers inside the 2 Kbyte Packet Buffer, both for transmission and reception. The PBI will choose the proper buffer according to requests coming from the USB Serial Interface Engine (SIE) and locate it in the Packet SRAM according to addresses pointed by endpoint registers. The PBI will also auto-increment the address after each exchanged byte until the end of packet, keeping track of the number of exchanged bytes and preventing buffer overrun. Special support is provided by the PBI for isochronous and bulk transfers, implementing double-buffer usage which ensures there is always an available buffer for a USB packet while the CPU uses a different buffer.

#### 2.18.2 DMA

A programmable DMA channel may be assigned by CPU firmware to service the USB interface for fast and direct transfers between the USB bus and SRAM with little CPU involvement. This DMA channel includes the following features:

- Direct USB Packet Buffer SRAM to system SRAM transfers of receive packets, by descriptor chain for bulk or isochronous endpoints.

- Direct system SRAM to USB Packet Buffer SRAM transfers of transmit packets, by descriptor chain for bulk or isochronous endpoints.

- Linked-list descriptor chain support for multiple USB packets

#### 2.18.3 Suspend mode

CPU firmware may place the USB interface in a low-power suspend mode when required, and the USB interface will automatically wake up asynchronously upon detecting activity on the USB pins.

# CAN 2.0B interface

The STR91xF provides a CAN interface complying with CAN protocol version 2.0 parts A and B. An external CAN transceiver device connected to pins CAN\_RX and CAN\_TX is required for connection to the physical CAN bus.

The CAN interface manages up to 32 Message Objects and Identifier Masks using a Message SRAM and a Message Handler. The Message Handler takes care of low-level CAN bus activity such as acceptance filtering, transfer of messages between the CAN bus and the Message

2.19

**.**...

high-impedance state when not selected. The STR91xF supports SPI multi-Master operation because it provides collision detection.

Each SSP interface on the STR91xF has the following features:

- Full-duplex, three or four-wire synchronous transfers

- Master or Slave operation

- Programmable clock bit rate with prescaler, up to 24MHz for Master mode and 4MHz for Slave mode

- Separate transmit and receive FIFOs, each 16-bits wide and 8 locations deep

- Programmable data frame size from 4 to 16 bits

- Programmable clock and phase polarity

- Specifically for Microwire protocol:

- Half-duplex transfers using 8-bit control message

- Specifically for SSI protocol:

- Full-duplex four-wire synchronous transfer

- Transmit data pin tri-stateable when not transmitting

#### 2.22.1 DMA

A programmable DMA channel may be assigned by CPU firmware to service each SSP channel for fast and direct transfers between the SSP bus and SRAM with little CPU involvement. Both DMA single-transfers and DMA burst-transfers are supported for transmit and receive. Burst transfers require that FIFOs are enabled.

# 2.23 General purpose I/Q

There are up to 80 GPIO pins available on 10 I/O ports for 128-pin devices, and up to 40 GPIO pins on 5 I/O ports for 80-pin devices. Each and every GPIO pin by default (during and just after a reset condition) is in high-impedance input mode, and some GPIO pins are additionally routed to certain peripheral function inputs. CPU firmware may initialize GPIO pins to have alternate input or output functions as listed in *Table 3*. At any time, the logic state of any GPIO pin may be read by firmware as a GPIO input, regardless of its reassigned input or output function.

Bit masking is available on each port, meaning firmware may selectively read or write individual port pins, without disturbing other pins on the same port during a write.

Firmware may designate each GPIO pin to have open-drain or push-pull characteristics.

All GPIO pins are 5V tolerant, meaning in they can drive a voltage level up to  $V_{DDQ}$ , and can be safely driven by a voltage up to 5.5V.

There are no internal pull-up or pull-down resistors on GPIO pins. As such, it is recommended to ground, or pull up to  $V_{DDQ}$  with a 100K $\Omega$  resistor, all unused GPIO pins to minimize power consumption and noise generation.

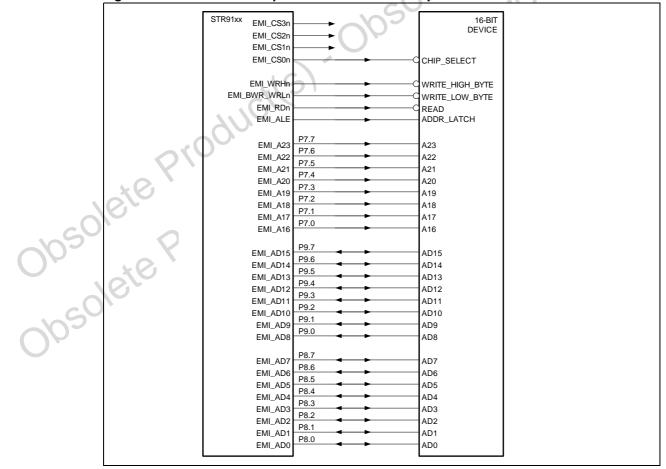

respectively. The output signal EMI\_RDn is the read strobe for both the low and high data bytes.

8-bit multiplexed data mode: This is a variant of the 16-bit multiplexed mode. Although this mode can provide 24 bits of address and 8 bits of data, it does require an external latch device on Port 8. However, this mode is most efficient when connecting devices that only require 8 bits of address on an 8-bit multiplexed address/data bus, and have simple read, write, and latch inputs as shown in *Figure 5*

To use all 24 address bits, the following applies: 8 bits of lowest-order data and 8 bits of lowest-order address are multiplexed on port 8. On port 9, 8-bits of mid-order address are multiplexed with 8 bits of data, but these 8 data values are always at logic zero on this port during a write operation, and these 8 data bits are ignored during a read operation. An external latch device (such as a '373 latch) is needed to de-multiplex the mid-order 8 address bits that are generated on port 8. Port 7 outputs the 8 highest-order address signals directly (not multiplexed). The output signal on pin EMI\_ALE is used to demultiplex the signal on pin EMI\_BWR\_WRLn is the data write strobe, and the output on pin EMI\_RDn is the data read strobe.

8-bit non-multiplexed data mode (*Figure 6*): Eight bits of data are on port 8, while 16 bits of address are output on ports 7 and 9. The output signal on pin EMI\_BWR\_BWLn is the data write strobe and the output on pin EMI\_RDn is the data read strobe.

#### Figure 4. EMI 16-bit multiplexed connection example

57

| Ρ        | kg       |                 | be          |                                         |                                       |                                             | Alternate                           | e functions                                |                                         |

|----------|----------|-----------------|-------------|-----------------------------------------|---------------------------------------|---------------------------------------------|-------------------------------------|--------------------------------------------|-----------------------------------------|

| LQFP80   | LQFP128  | Pin Name        | Signal Type | Default Pin<br>Function                 | Default Input<br>Function             | Alternate<br>Input 1                        | Alternate<br>Output 1               | Alternate<br>Output 2                      | Alternate<br>Output 3                   |

| 43       | 68       | P3.7            | I/O         | GPIO_3.7,<br>GP Input, HiZ              | EXINT7,<br>External Intr              | SSP1_NSS,<br>SSP slv select in              | GPIO_3.7,<br>GP Output              | SSP1_NSS,<br>SSP mstr sel out              | TIM1_OCMP1, C<br>comp/PWM               |

| 4        | 3        | P4.0            | I/O         | GPIO_4.0,<br>GP Input, HiZ              | ADC0,<br>ADC input chnl               | TIM0_ICAP1,<br>Input Capture                | GPIO_4.0,<br>GP Output              | TIM0_OCMP1, Out<br>comp/PWM                | ETM_PCK0, ET<br>Packet                  |

| 3        | 2        | P4.1            | I/O         | GPIO_4.1,<br>GP Input, HiZ              | ADC1,<br>ADC input chnl               | TIM0_ICAP2,<br>Input Capture                | GPIO_4.1,<br>GP Output              | TIM0_OCMP2, Out comp                       | ETM_PCK1, ET<br>Packet                  |

| 2        | 1        | P4.2            | I/O         | GPIO_4.2,<br>GP Input, HiZ              | ADC2,<br>ADC input chnl               | TIM1_ICAP1,<br>Input Capture                | GPIO_4.2,<br>GP Output              | TIM1_OCMP1, Out<br>comp/PWM                | ETM_PCK2, ET<br>Packet                  |

| 1        | 128      | P4.3            | I/O         | GPIO_4.3,<br>GP Input, HiZ              | ADC3,<br>ADC input chnl               | TIM1_ICAP2,<br>Input Capture                | GPIO_4.3,<br>GP Output              | TIM1_OCMP2, Out<br>comp                    | ETM_PCK3, ET<br>Packet                  |

| 80       | 127      | P4.4            | I/O         | GPIO_4.4,<br>GP Input, HiZ              | ADC4,<br>ADC input chnl               | TIM2_ICAP1,<br>Input Capture                | GPIO_4.4,<br>GP Output              | TIM2_OCMP1, Out<br>comp/PWM                | ETM_PSTAT0,<br>ETM pipe statu           |

| 79       | 126      | P4.5            | I/O         | GPIO_4.5,<br>GP Input, HiZ              | ADC5,<br>ADC input chnl               | TIM2_ICAP2,<br>Input Capture                | GPIO_4.5,<br>GP Output              | TIM2_OCMP2, Out<br>comp                    | ETM_PSTAT1,<br>ETM pipe statu           |

| 78       | 125      | P4.6            | I/O         | GPIO_4.6,<br>GP Input, HiZ              | ADC6,<br>ADC input chnl               | TIM3_ICAP1,<br>Input Capture                | GPIO_4.6,<br>GP Output              | TIM3_OCMP1, Out<br>comp/PWM                | ETM_PSTAT2<br>ETM pipe statu            |

| 77       | 124      | P4.7            | I/O         | GPIO_4.7,<br>GP Input, HiZ              | ADC7,<br>ADC input chnl               | TIM3_ICAP2,<br>Input Capture                | GPIO_4.7,<br>GP Output              | TIM3_OCMP2, Out<br>comp                    | ETM_TRSYNC<br>ETM trace syn             |

| 9        | 12       | P5.0            | I/0         | GPIO_5.0,<br>GP Input, HiZ              | EXINT8,<br>External Intr              | CAN_RX,<br>CAN rcv data                     | GPIO_5.0,<br>GP Output              | ETM_TRCLK,<br>ETM trace clock              | UART0_TX,<br>UART xmit dat              |

| 12       | 18       | P5.1            | I/0         | GPIO_5.1,<br>GP Input, HiZ              | EXINT9,<br>External Intr              | UART0_RxD,<br>UART rcv data                 | GPIO_5.1,<br>GP Output              | CAN_TX,<br>CAN Tx data                     | UART2_TX,<br>UART xmit dat              |

| 17       | 25       | PHYCLK<br>_P5.2 | I/O         | GPIO_5.2,<br>GP Input, HiZ              | EXINT10,<br>External Intr             | UART2_RxD,<br>UART rcv data                 | GPIO_5.2,<br>GP Output              | MII_PHYCLK,<br>25Mhz to PHY                | TIM3_OCMP1, C<br>comp/PWM               |

| 18       | 27       | P5.3            | I/O         | GPIO_5.3,<br>GP Input, HiZ              | EXINT11,<br>External Intr             | ETM_EXTRIG,<br>ETM ext. trigger             | GPIO_5.3,<br>GP Output              | MII_TX_EN,<br>MAC xmit enbl                | TIM2_OCMP1, C<br>comp/PWM               |

| 44       | 70       | P5.4            | I/O         | GPIO_5.4,<br>GP Input, HiZ              | EXINT12,<br>External Intr             | SSP0_SCLK,<br>SSP slv clk in                | GPIO_5.4,<br>GP Output              | SSP0_SCLK,<br>SSP mstr clk out             | EMI_CS0n,<br>EMI Chip Sele              |

| 47       | 77       | P5.5            | I/O         | GPIO_5.5,<br>GP Input, HiZ              | EXINT13,<br>External Intr             | SSP0_MOSI,<br>SSP slv dat in                | GPIO_5.5,<br>GP Output              | SSP0_MOSI,<br>SSP mstr dat out             | EMI_CS1n,<br>EMI Chip Sele              |

| 48       | 79       | P5.6            | 1/0         | GPIO_5.6,<br>GP Input, HiZ<br>GPIO_5.7, | EXINT14,<br>External Intr             | SSP0_MISO,<br>SSP mstr dat in               | GPIO_5.6,<br>GP Output              | SSP0_MISO,<br>SSP slv data out             | EMI_CS2n,<br>EMI Chip Sele<br>EMI CS3n, |

| 49       | 80       | P5.7            | I/O         | GPI0_5.7,<br>GP Input, HiZ              | EXINT15,<br>External Intr             | SSP0_NSS,<br>SSP slv select in              | GPIO_5.7,<br>GP Output              | SSP0_NSS,<br>SSP mstr sel out              | EMI_CS3N,<br>EMI Chip Sele              |

| 19       | 29       | P6.0            | 1/0         | GPIO_6.0,<br>GP Input, HiZ              | EXINT16,<br>External Intr<br>EXINT17, | TIM0_ICAP1,<br>Input Capture                | GPIO_6.0,<br>GP Output              | TIM0_OCMP1, Out<br>comp/PWM                | MC_UH,<br>IMC phase U I                 |

| 20       | 31       | P6.1            | 1/0         | GPIO_6.1,<br>GP Input, HiZ<br>GPIO_6.2, | EXINTT7,<br>External Intr<br>EXINT18, | TIM0_ICAP2,<br>Input Capture<br>TIM1_ICAP1, | GPIO_6.1,<br>GP Output<br>GPIO_6.2, | TIM0_OCMP2, Out<br>comp<br>TIM1_OCMP1, Out | MC_UL,<br>IMC phase U I<br>MC VH,       |

| 13       | 19       | P6.2            | I/O         | GP Input, HiZ<br>GPIO_6.3,              | External Intr<br>EXINT19,             | Input Capture<br>TIM1_ICAP2,                | GP Output<br>GPIO_6.3,              | TIM1_OCMP2, Out                            | IMC phase V I<br>MC_VL,                 |

| 14       | 20       | P6.3            | 1/0         | GP Input, HiZ<br>GPIO_6.4,              | External Intr<br>EXINT20,             | Input Capture<br>TIM2_ICAP1,                | GP Output<br>GPIO_6.4,              | TIM2_OCMP1, Out                            | IMC phase V<br>MC_WH,                   |

| 52       | 83       | P6.4            | 1/0         | GP Input, HiZ<br>GPIO_6.5,              | External Intr<br>EXINT21,             | Input Capture<br>TIM2_ICAP2,                | GP Output<br>GPIO_6.5,              | comp/PWM<br>TIM2_OCMP2, Out                | IMC phase W<br>MC_WL,                   |

| 53       | 84       | P6.5            | 1/0         | GP Input, HiZ<br>GPIO_6.6,              | External Intr<br>EXINT22_TRIG,        | Input Capture<br>UART0_RxD,                 | GP Output<br>GPIO_6.6,              | Comp<br>TIM3_OCMP1, Out                    | IMC phase W<br>ETM_TRCLK                |

| 57<br>58 | 92<br>93 | P6.6<br>P6.7    | 1/O<br>1/O  | GP Input, HiZ<br>GPIO_6.7,              | Ext Intr & Tach<br>EXINT23_STOP,      | UART rcv data<br>ETM_EXTRIG,                | GP Output<br>GPIO_6.7,              | comp/PWM<br>TIM3_OCMP2, Out                | ETM trace cloo<br>UART0_TX,             |

| 58       | 93       | P0.7            | 1/0         | GP Input, HiZ                           | Ext Intr & Estop                      | ETM ext. trigger                            | GP Output                           | сотр                                       | UART xmit dat                           |

| Ρ      | kg      |                                                            | be          |                                                                                       |                           |                      | Alternate             | e functions           |                       |

|--------|---------|------------------------------------------------------------|-------------|---------------------------------------------------------------------------------------|---------------------------|----------------------|-----------------------|-----------------------|-----------------------|

| LQFP80 | LQFP128 | Pin Name                                                   | Signal Type | Default Pin<br>Function                                                               | Default Input<br>Function | Alternate<br>Input 1 | Alternate<br>Output 1 | Alternate<br>Output 2 | Alternate<br>Output 3 |

| -      | 21      | EMI_BWR<br>_WRLn<br>(used as<br>EMI_LBn in<br>future rev.) | 0           | EMI byte write<br>strobe (8 bit<br>mode) or low<br>byte write strobe<br>(16 bit mode) |                           |                      | N/A                   |                       |                       |

| -      | 22      | EMI_WRHn<br>(used as<br>EMI_UBn in<br>future rev.)         | ο           | EMI high byte<br>write strobe (16-<br>bit mode)                                       |                           |                      | N/A                   |                       |                       |

| -      | 74      | EMI_ALE                                                    | 0           | EMI address<br>latch enable<br>(mux mode)                                             |                           |                      | N/A                   |                       | 16)                   |

| -      | 75      | EMI_RDn                                                    | 0           | EMI read strobe                                                                       |                           |                      | N/A                   |                       | XU                    |

| -      | -       | EMI_BAAn                                                   | 0           | TBD                                                                                   |                           |                      | N/A                   |                       |                       |

| -      | -       | EMI_WAITn                                                  | 1           | TBD                                                                                   |                           |                      | N/A                   |                       |                       |

| -      | -       | EMI_BCLK                                                   | 0           | TBD<br>Reserved for                                                                   |                           |                      | N/A                   |                       |                       |

| -      | -       | EMI_WEn                                                    | 0           | future use                                                                            |                           |                      | N/A                   |                       | .(9)                  |

| -      | 91      | _IN                                                        | I           | input<br>MAC/PHY                                                                      |                           |                      | N/A                   |                       | <u>C</u>              |

| -      | 94      | MII_MDIO                                                   | I/O         | management<br>data line                                                               |                           |                      | N/A                   | du                    |                       |

| 59     | 95      | USBDN                                                      | I/O         | USB data (-) bus<br>connect                                                           |                           | ~nS'                 | N/A                   | 210                   |                       |

| 60     | 96      | USBDP                                                      | I/O         | USB data (+) bus<br>connect                                                           |                           | 04                   | N/A                   |                       |                       |

| 56     | 89      | RESET<br>_INn                                              | Ι           | External reset<br>input                                                               |                           |                      | N/A                   |                       |                       |

| 62     | 100     | RESET<br>_OUTn                                             | 0           | Global or System<br>reset output                                                      | 191                       | S                    | N/A                   |                       |                       |

| 65     | 104     | X1_CPU                                                     | I           | CPU oscillator or<br>crystal input                                                    |                           | Ov                   | N/A                   |                       |                       |

| 64     | 103     | X2_CPU                                                     | 0           | CPU crystal<br>connection                                                             |                           | ¢                    | N/A                   |                       |                       |

| 27     | 42      | X1_RTC                                                     | I           | RTC oscillator or<br>crystal input<br>(32.768 kHz)                                    | de                        |                      | N/A                   |                       |                       |

| 26     | 41      | X2_RTC                                                     | 0           | RTC crystal<br>connection                                                             |                           |                      | N/A                   |                       |                       |

| 61     | 97      | JRTCK                                                      | 0           | JTAG return<br>clock or RTC<br>clock                                                  |                           |                      | N/A                   |                       |                       |

| 67     | 107     | JTRSTn                                                     | T           | JTAG TAP<br>controller reset                                                          |                           |                      | N/A                   |                       |                       |

| 68     | 108     | JTCK                                                       | Ι           | JTAG clock                                                                            |                           |                      | N/A                   |                       |                       |

| 69     | 111     | JTMS                                                       | I           | JTAG mode select                                                                      |                           |                      | N/A                   |                       |                       |

| 72     | 115     | JTDI                                                       | Т           | JTAG data in                                                                          |                           |                      | N/A                   |                       |                       |

| 73     | 117     | JTDO                                                       | 0           | JTAG data out                                                                         |                           |                      | N/A                   |                       |                       |

| -      | 122     | AVDD                                                       | v           | ADC analog<br>voltage source,<br>2.7V - 3.6V                                          |                           |                      | N/A                   |                       |                       |

| -      | 4       | AVSS                                                       | G           | ADC analog<br>ground                                                                  |                           |                      | N/A                   |                       |                       |

| 5      | -       | AVSS<br>_VSSQ                                              | G           | Common ground<br>point for digital I/<br>O & analog ADC                               |                           |                      | N/A                   |                       |                       |

When other AHB bus masters (such as a DMA controller) write to SRAM, their access is never buffered. Only the CPU can make use of buffered AHB writes.

# 5.4 Two independent Flash memories

The STR91xF has two independent Flash memories, the larger primary Flash and the small secondary Flash. It is possible for the CPU to erase/write to one of these Flash memories while simultaneously reading from the other.

One or the other of these two Flash memories may reside at the "boot" address position of 0x0000.0000 at power-up or at reset as shown in *Figure 9*. The default configuration is that the first sector of primary Flash memory is enabled and residing at the boot position, and the secondary Flash memory is disabled. This default condition may be optionally changed as described below.

#### 5.4.1 Default configuration

When the primary Flash resides at boot position, typical CPU initialization firmware would set the start address and size of the main Flash memory, and go on to enable the secondary Flash, define it's start address and size. Most commonly, firmware would place the secondary Flash start address at the location just after the end of the primary Flash memory. In this case, the primary Flash is used for code storage, and the smaller secondary flash can be used for data storage (EEPROM emulation).

#### 5.4.2 Optional configuration

Using the STR91xF device configuration software tool, or IDE from 3rd party, one can specify that the smaller secondary Flash memory is at the boot location at reset and the primary Flash is disabled. The selection of which Flash memory is at the boot location is programmed in a non-volatile Flash-based configuration bit during JTAG ISP. The boot selection choice will remain as the default until the bit is erased and re-written by the JTAG interface. The CPU cannot change this choice for boot Flash, only the JTAG interface has access.

In this case where the secondary Flash defaults to the boot location upon reset, CPU firmware would typically initialize the Flash memories the following way. The secondary Flash start address and size is specified, then the primary Flash is enabled and its start address and size is specified. The primary Flash start address would typically be located just after the final address location of the secondary Flash. This configuration is particularly well-suited for In-Application-Programming (IAP). The CPU would boot from the secondary Flash memory, initialize the system, then check the contents of the primary Flash memory (by checksum or other means). If the contents of primary Flash is OK, then CPU execution continues from either Flash memory. If the main Flash contents are incorrect, the CPU, while executing code from the secondary Flash, can download new data from any STR91xF communication channel and program into primary Flash memory. Application code then starts after the new contents of primary Flash are verified.

|               |                          |                                                         | APB BASE +                 | PERIPHERAL BUS<br>MEMORY SPACE <sup>(4)</sup> |

|---------------|--------------------------|---------------------------------------------------------|----------------------------|-----------------------------------------------|

|               | TOTAL 4 GB CPU           |                                                         | OFFSET<br>APB1+0x03FF.FFFF |                                               |

|               | MEMORY SPACE             |                                                         | APB1+0x0000.E000 _         | RESERVED                                      |

| 0xFFFF.FFFF   |                          | l ~                                                     |                            | I2C1 4 КВ                                     |

| 0xFFFF.F000 _ | VIC0                     | 4 КВ АНВ                                                | APB1+0x0000.D000           | I2C0 4 кв                                     |

| 0xFC01.0000   | RESERVED                 | > NON-<br>( BUFFERED                                    | APB1+0x0000.C000 _         | WATCHDOG 4 KB                                 |

| 0xFC00.0000   | VIC1                     | 64 КВ 🔍                                                 | APB1+0x0000.B000 _         | ADC 4 KB                                      |

|               |                          |                                                         | APB1+0x0000.A000           | CAN 4 KB                                      |

|               |                          |                                                         | APB1+0x0000.9000 _         |                                               |

|               | RESERVED                 |                                                         | APB1+0x0000.8000 _         |                                               |

|               |                          |                                                         | APB1+0x0000.7000 _         | SSP0 4 KB to A<br>LIART2 4 KB Brid            |

| 00000.0000    |                          |                                                         | APB1+0x0000.6000           |                                               |

| 0x8000.0000 . | ENET                     | 64 MB                                                   | APB1+0x0000.5000 _         | UART1 4 KB                                    |

| 0x7C00.0000 _ | 8-CH DMA                 | 64 MB AHB                                               | APB1+0x0000.4000           | UARTO 4 KB                                    |

| 0x7800.0000 _ | EMI                      | 64 MB BUFFERED                                          | APB1+0x0000.3000 _         | IMC 4 KB                                      |

| 0x7400.0000 - | USB                      | 64 MB                                                   | APB1+0x0000.2000 _         | SCU 4 KB                                      |

| 0x7000.0000 . | ENET                     | 64 MB                                                   | APB1+0x0000.1000 _         | RTC 4 KB                                      |

| 0x6C00.0000 _ | 8-CH DMA                 |                                                         | APB1+0x0000.0000           | APB1 CONFIG 4 KB /                            |

| 0x6800.0000 _ | EMI                      | 64 MB AHB<br>BUFFERED                                   |                            | X                                             |

| 0x6400.0000 - | USB                      | 64 MB                                                   | APB0+0x03FF.FFFF           | RESERVED                                      |

| 0x6000.0000 . | APB1                     | 64 MB / PERIPHERAL BUS,                                 | APB0+0x0001.0000           | GPIO PORT P9 4 KB                             |

| 0x5C00.0000 _ | APB1<br>APB0             | NON-BUFFERED                                            | APB0+0x0000.F000           | GPIO PORT P8 4 KB                             |

| 0x5800.0000 _ |                          | NON-                                                    | APB0+0x0000.E000 _         |                                               |

| 0x5400.0000 - | FMI                      | 64 MB BUFFERED                                          | APB0+0x0000.D000           |                                               |

| 0x5000.0000 . | SRAM, AHB (2)            | 64 MB /                                                 | APB0+0x0000.C000 _         | GPIO PORT P6 4 KB                             |

| 0x4C00.0000 - | APB1                     | 64 MB PERIPHERAL BUS,<br>BUFFERED ACCESS <sup>(3)</sup> | APB0+0x0000.B000           | GPIO PORT P5 4 KB                             |

| 0x4800.0000 _ | APB0                     | 64 MB AHB                                               | APB0+0x0000.A000 _         | GPIO PORT P4 4 KB                             |

| 0x4400.0000 - | FMI                      | 64 MB BUFFERED                                          | APB0+0x0000.9000 _         | GPIO PORT P3 4 KB APE                         |

| 0x4000.0000 . | SRAM, AHB <sup>(2)</sup> | 64 MB                                                   | APB0+0x0000.8000 _         | GPIO PORT P2 4 KB to-A                        |

| 0x3C00.0000 - | Ext. MEM, CS0            | 64 MB                                                   | APB0+0x0000.7000 _         | GPIO PORT P1 4 KB Brid                        |

| 0x3800.0000 _ | Ext. MEM, CS1            | 64 MB AHB                                               | APB0+0x0000.6000           | GPIO PORT P0 4 KB                             |

| 0x3400.0000 - | Ext. MEM, CS2            | 64 MB BUFFERED                                          | APB0+0x0000.5000           | TIM3 4 KB                                     |

| 0x3000.0000 . | Ext. MEM, CS3            | 64 MB                                                   | APB0+0x0000.4000           | TIM2 4 KB                                     |

| 0x2C00.0000 _ | Ext. MEM, CS0            | 64 MB                                                   | APB0+0x0000.3000 _         | TIM1 4 КВ                                     |

| 0x2800.0000   | Ext. MEM, CS1            | 64 MB AHB                                               | APB0+0x0000.2000 _         | TIMO 4 кв                                     |

| 0x2400.0000   | Ext. MEM, CS2            | 64 MB BUFFERED                                          | APB0+0x0000.1000 _         | WAKE-UP UNIT 4 KB                             |

| 0x2000.0000 . | Ext. MEM, CS3            | 64 MB                                                   | APB0+0x0000.0000 _         | APB0 CONFIG 4 KB /                            |

| Ŷ             |                          |                                                         |                            |                                               |

|               |                          | C                                                       | Order of the two Flash me  | emories is user defined.                      |

|               |                          |                                                         | SECONDARY                  |                                               |

|               | RESERVED                 |                                                         | FLASH (BANK 1),<br>32KB    | MAIN FLASH<br>(BANK 0),                       |

| C             |                          |                                                         | 02110                      | 256KB or 512KB                                |

| 0,0800,0000   |                          |                                                         | MAIN FLASH                 |                                               |

| 0x0800.0000 _ | SRAM, D-TCM (2)          | Using 64 KB or 96                                       | (BANK 0),                  |                                               |

| 0x0400.0000   | FLASH, I-TCM (1)         | KB<br>Using 288 KB or 544                               | 256KB or 512KB             | FLASH (BANK 1),<br>32KB                       |

| 0x0000.0000   | · · ·                    | КВ 0x0000.0000                                          | DEFAULT ORDER              | OPTIONAL ORDER                                |

#### Figure 9. STR91xF memory map

# 6.7 Main oscillator electrical characteristics

$V_{DDQ}$  = 2.7 - 3.6V,  $V_{DD}$  = 1.65 - 2V,  $T_A$  = -40 / 85 °C unless otherwise specified.

#### Table 11. Main oscillator electrical characteristics

| Symbol                 | Parameter                | Test Conditions         |     | Unit |     |     |  |

|------------------------|--------------------------|-------------------------|-----|------|-----|-----|--|

| Symbol                 | i didineter              |                         | Min | Тур  | Max | Ont |  |

| t <sub>STUP(OSC)</sub> | Oscillator Start-up Time | Stable V <sub>DDQ</sub> |     |      | 3   | mS  |  |

# 6.8 **RTC oscillator electrical characteristics**

$V_{DDQ}$  = 2.7 - 3.6V,  $V_{DD}$  = 1.65 - 2V,  $T_A$  = -40 / 85  $^\circ C$  unless otherwise specified.

#### Table 12. RTC oscillator electrical characteristics

| Symbol                 | Parameter                 | Test Conditions         |                   | Value | V.      | Unit |

|------------------------|---------------------------|-------------------------|-------------------|-------|---------|------|

| Symbol                 | i didineter               |                         | Min               | Тур   | Max     | S    |

| 9м(RTC)                | Oscillator Start _voltage |                         | LVD <sup>1)</sup> |       | $C^{r}$ | v    |

| t <sub>STUP(RTC)</sub> | Oscillator Start-up Time  | Stable V <sub>DDQ</sub> | 2                 |       |         | S    |

Notes: 1 Min oscillator start voltage is the same as low voltage detect level (2.4V or 2.7V) for VDDQ

#### Table 13. RTC crystal electrical characteristics

|                | Symbol         | Parameter C        | Test Conditions | 0   | Value  |     | Unit |

|----------------|----------------|--------------------|-----------------|-----|--------|-----|------|

|                | Symbol         | Farameter          | Test conditions | Min | Тур    | Max | Onit |

|                | f <sub>O</sub> | Resonant frequency | 0v              |     | 32.768 |     | kHz  |

|                | R <sub>S</sub> | Series resistance  |                 |     |        | 40  | kΩ   |

|                | CL             | Load capacitance   |                 |     | 8      |     | pF   |

| Obsol<br>Obsol | eter           | produces           |                 |     |        |     |      |

# 6.9 PLL electrical characteristics

$V_{DDQ}$  = 2.7 - 3.6V,  $V_{DD}$  = 1.65 - 2V,  $T_A$  = -40 / 85  $^\circ C$  unless otherwise specified.

| Symbol                  | Symbol Parameter Test Conditions |                  |            | Unit |       |    |

|-------------------------|----------------------------------|------------------|------------|------|-------|----|

| Symbol                  |                                  |                  | Min        | Тур  | Max   | Un |

| f <sub>PLL</sub>        | PLL Output Clock                 |                  | 6.25       |      | 96    | MH |

| f <sub>OSC</sub>        | Clock Input                      |                  | 4          |      | 25    | MH |

| t <sub>LOCK</sub>       | PLL lock time                    |                  |            | 300  | 1500  | με |

| $\Delta t_{\rm JITTER}$ | PLL Jitter (peak to peak)        |                  |            | 0.1  | 0.2   | n  |

| olete                   | Product(S)<br>Product(S)         | obsoli<br>obsoli | ste<br>ste | 510c | Jucil | 5  |

Table 14.

PLL Electrical Characteristics

## 6.11.3 Absolute Maximum Ratings (Electrical Sensitivity)

Based on three different tests (ESD, LU and DLU) using specific measurement methods, the product is stressed in order to determine its performance in terms of electrical sensitivity. For more details, refer to the application note AN1181.

# 6.11.4 Electro-Static Discharge (ESD)

Electro-Static Discharges (3 positive then 3 negative pulses separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts\*(n+1) supply pin). Two models can be simulated: Human Body Model and Charge Device Model. This test conforms to the JESD22-A114A/A115A standard.

| Table 19.             | ESD Absolute Maximum ratings                              |                       | .15                            |      |

|-----------------------|-----------------------------------------------------------|-----------------------|--------------------------------|------|

| Symbol                | Ratings                                                   | Conditions            | Maximum<br>value <sup>1)</sup> | Unit |

| V <sub>ESD(HBM)</sub> | Electro-static discharge voltage<br>(Human Body Model)    | T <sub>A</sub> =+25°C | +/-2000                        | V    |

| V <sub>ESD(CDM)</sub> | Electro-static discharge voltage<br>(Charge Device Model) |                       | 1000                           | v    |

#### Notes:

1. Data based on characterization results, not tested in production.

#### 6.11.5 Static and Dynamic Latch-Up

- LU: 3 complementary static tests are required on 10 parts to assess the latch-up performance. A supply overvoltage (applied to each power supply pin) and a current injection (applied to each input, output and configurable I/O pin) are performed on each sample. This test conforms to the EIA/JESD 78 IC latch-up standard. For more details, refer to the application note AN1181.

- **DLU**: Electro-Static Discharges (one positive then one negative test) are applied to each pin of 3 samples when the micro is running to assess the latch-up performance in dynamic mode. Power supplies are set to the typical values, the oscillator is connected as near as possible to the pins of the micro and the component is put in reset mode. This test conforms to the IEC1000-4-2 and SAEJ1752/3 standards. For more details, refer to the application note AN1181.

# 6.11.6 Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations:

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

| Symbol | Parameter                              | Symbol                 | Va    | Unit |      |

|--------|----------------------------------------|------------------------|-------|------|------|

| Symbol | Falanetei                              | Gymbol                 | Min   | Max  | onit |

| 1      | MDIO delay from rising edge of MDC     | t <sub>c</sub> (MDIO)  |       | 2.83 | ns   |

| 2      | MDIO setup time to rising edge of MDC  | T <sub>su</sub> (MDIO) | 2.70  |      | ns   |

| 3      | MDIO hold time from rising edge of MDC | T <sub>h</sub> (MDIO)  | -2.03 |      | ns   |

Table 26.

Ethernet MII management timing table

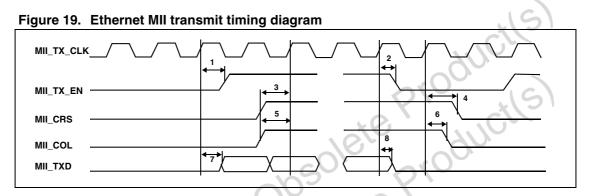

#### **Ethernet MII transmit timings**

#### Table 27. Ethernet MII transmit timing table

|      | Symbol | Parameter                               | Symbol                         | Val  | ue   | Unit |

|------|--------|-----------------------------------------|--------------------------------|------|------|------|

|      | Symbol | Faialleter                              | Symbol                         | Min  | Max  | Onit |

|      | 1      | MII_TX_CLK high to<br>MII_TX_EN valid   | t <sub>VAL</sub> (MII_TX_EN)   |      | 4.20 | ns   |

|      | 2      | MII_TX_CLK high to<br>MII_TX_EN invalid | T <sub>inval</sub> (MII_TX_EN) |      | 4.86 | ns   |

|      | 3      | MII_CRS valid to<br>MII_TX_CLK high     | T <sub>su</sub> (MII_CRS)      | 0.61 |      | ns   |

| 50   | 4      | MII_TX_CLK high to<br>MII_CRS invalid   | T <sub>h</sub> (MII_CRS)       | 0.00 |      | ns   |

| 00   | 5      | MII_COL valid to<br>MII_TX_CLK high     | T <sub>su</sub> (MII_COL)      | 0.81 |      | ns   |

| cO   | 6      | MII_TX_CLK high to<br>MII_COL invalid   | T <sub>h</sub> (MII_COL)       | 0.00 |      | ns   |

| 0,02 | 7      | MII_TX_CLK high to<br>MII_TXD valid     | t <sub>VAL</sub> (MII_TXD)     |      | 5.02 | ns   |

|      | 8      | MII_TXCLK high to<br>MII_TXD invalid    | T <sub>inval</sub> (MII_TXD    |      | 5.02 | ns   |

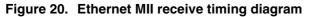

#### **Ethernet MII Receive timings**

#### Figure 21. Ethernet MII receive timing table

| Symbol                                      | Parameter                             | Symbol                    | Value |      | Unit |  |  |  |  |

|---------------------------------------------|---------------------------------------|---------------------------|-------|------|------|--|--|--|--|

|                                             |                                       |                           | Min   | Мах  | S    |  |  |  |  |

| 1                                           | MII_RXD valid to<br>MII_RX_CLK high   | T <sub>su</sub> (MII_RXD) | 0.81  | 1,10 | ns   |  |  |  |  |

| 2                                           | MII_RX_CLK high to<br>MII_RXD invalid | T <sub>h</sub> (MII_RXD)  | 0.00  | 50   | ns   |  |  |  |  |

| USB electrical interface characteristics    |                                       |                           |       |      |      |  |  |  |  |

| USB 2.0 Compliant in Full Speed Mode        |                                       |                           |       |      |      |  |  |  |  |

|                                             |                                       |                           |       |      |      |  |  |  |  |

| CAN interface electrical characteristics    |                                       |                           |       |      |      |  |  |  |  |

| Conforms to CAN 2.0B protocol specification |                                       |                           |       |      |      |  |  |  |  |

| MCIC Ops                                    |                                       |                           |       |      |      |  |  |  |  |

# 6.14.2 USB electrical interface characteristics

# reproduces of the production o 6.14.3 CAN interface electrical characteristics

57

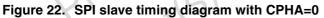

### 6.14.5 SPI electrical characteristics

$V_{DDQ}$  = 2.7 - 3.6V,  $V_{DD}$  = 1.65 - 2V,  $T_A$  = -40 / 85  $^\circ C$  unless otherwise specified.

| Symbol                 | Downworker                    | Test Conditions        | Value           |               |                   |

|------------------------|-------------------------------|------------------------|-----------------|---------------|-------------------|

|                        | Parameter                     | lest Conditions        | Тур             | Max           | Unit              |

| f <sub>SCLK</sub>      | SPI clock frequency           | Master                 |                 | 24            | MHz               |

| 1/t <sub>c(SCLK)</sub> |                               | Slave                  |                 | 4             |                   |

| t <sub>r(SCLK)</sub>   | SPI clock rise and fall times | 50pF load              | 0.1             |               | V/ns              |

| t <sub>f(SCLK)</sub>   |                               |                        |                 |               |                   |

| t <sub>su(SS)</sub>    | SS setup time                 | Slave                  | 1               |               | 51                |

| t <sub>h(SS)</sub>     | SS hold time                  | Slave                  | 1               | C/            |                   |

| t <sub>w(SCLKH)</sub>  | SCLK high and low time        | Master                 |                 | $\mathcal{O}$ |                   |

| t <sub>w(SCLKL)</sub>  |                               | Slave                  | ~0 <sup>~</sup> |               |                   |

| t <sub>su(MI)</sub>    | Data input setup time         | Master                 | 5               | ×             | 51                |

| t <sub>su(SI)</sub>    | Data input setup time         | Slave Slave            |                 |               |                   |

| t <sub>h(MI)</sub>     | Data input hold time          | Master                 | 6               | 2             |                   |

| t <sub>h(SI)</sub>     | Bata input noid time          | Slave                  | 0,              |               | t <sub>PCLK</sub> |

| t <sub>a(SO)</sub>     | Data output access time       | Slave                  |                 | 6             |                   |

| t <sub>dis(SO)</sub>   | Data output disable time      | Slave                  | -               | 6             |                   |

| t <sub>v(SO)</sub>     | Data output valid time        | Slave (after enable    |                 | 6             |                   |

| t <sub>h(SO)</sub>     | Data output hold time         | edge)                  | 0               |               |                   |

| t <sub>v(MO)</sub>     | Data output valid time        | Master (before capture | 0.25            |               |                   |

| t <sub>h(MO)</sub>     | Data output hold time         | edge)                  | 0.25            |               |                   |

Table 29.

SPI electrical characteristics

57

# 9 Revision history

|                                                 | Date          | Revision | Changes                                                           |  |  |

|-------------------------------------------------|---------------|----------|-------------------------------------------------------------------|--|--|

|                                                 | 12-Apr-2006   | 1        | Initial release                                                   |  |  |

|                                                 | 28-June-2006  | 2        | Added LFBGA144 package                                            |  |  |

|                                                 | 20-3011e-2000 |          | Updated electrical characteristics section                        |  |  |

|                                                 |               | 3        | Changed number of GPIOs in 80 pin packge to 40                    |  |  |

|                                                 | 04-Sep-2006   |          | Changed EMI_RDYn pin name to EMI_WAITn                            |  |  |

|                                                 |               |          | Added RTC clock to description of JRTCK in Table 3                |  |  |

|                                                 |               |          | UART max baud rate changed to 1.5 Mbps in Section 2.20 on page 26 |  |  |

|                                                 |               |          | Modified Figure 2: Clock control on page 15                       |  |  |

|                                                 | 01-Feb-2007   | 4        | Removed LFBGA144 package, (transferred to separate STR91xFA       |  |  |

|                                                 |               |          | datasheet).                                                       |  |  |

| <u>01-Feb-2007</u> <u>4</u> <u>datasheet</u> ). |               |          |                                                                   |  |  |

72/73