Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | F <sup>2</sup> MC-16LX                                                            |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 32MHz                                                                             |

| Connectivity               | CANbus, LINbus, UART/USART                                                        |

| Peripherals                | LCD, LVD, POR, PWM, WDT                                                           |

| Number of I/O              | 93                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | Mask ROM                                                                          |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 10K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                         |

| Data Converters            | A/D 8x8/10b                                                                       |

| Oscillator Type            | External                                                                          |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 120-LQFP                                                                          |

| Supplier Device Package    | 120-LQFP (16x16)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90922ncspmc-gs-154e1 |

|                            |                                                                                   |

### **■ PIN DESCRIPTIONS**

| Pin no. | Pin name | I/O circuit<br>type*1 | Function                                 |

|---------|----------|-----------------------|------------------------------------------|

| 108     | X0       | A                     | High-speed oscillation input pin         |

| 107     | X1       |                       | High-speed oscillation output pin        |

| 13      | X0A      | В                     | Low-speed oscillation input pin          |

| 13      | P92      | I                     | General-purpose I/O port                 |

| 14      | X1A      | В                     | Low-speed oscillation output pin         |

| 14      | P93      | 1                     | General-purpose I/O port                 |

| 90      | RST      | С                     | Reset input pin                          |

| 93      | P00      | F                     | General-purpose I/O port                 |

| 93      | SEG24    | <del>т</del> Г        | LCD controller/driver segment output pin |

| 94      | P01      | F                     | General-purpose I/O port                 |

| 94      | SEG25    | <del>т</del> Г        | LCD controller/driver segment output pin |

| 95 -    | P02      | F                     | General-purpose I/O port                 |

| 95      | SEG26    | ₹ <b>Г</b>            | LCD controller/driver segment output pin |

| 96      | P03      | F                     | General-purpose I/O port                 |

| 90      | SEG27    | <del>т</del> Г        | LCD controller/driver segment output pin |

| 97 -    | P04      | F                     | General-purpose I/O port                 |

| 97      | SEG28    | <del>т</del> Г        | LCD controller/driver segment output pin |

| 98 -    | P05      | F                     | General-purpose I/O port                 |

| 90      | SEG29    | <b>Т</b>              | LCD controller/driver segment output pin |

| 99      | P06      | F                     | General-purpose I/O port                 |

| 99      | SEG30    | <b>т</b>              | LCD controller/driver segment output pin |

| 100     | P07      | F                     | General-purpose I/O port                 |

| 100     | SEG31    | <del>т</del> Г        | LCD controller/driver segment output pin |

|         | P10      |                       | General-purpose I/O port                 |

| 101     | PPG2     | l                     | 16-bit PPG ch.2 output pin               |

|         | IN5      |                       | Input capture ch.5 trigger input pin     |

|         | P11      |                       | General-purpose I/O port                 |

| 102     | ТОТ0     | ]                     | 16-bit reload timer ch.0 TOT output pin  |

| 102     | PPG3     | ] '                   | 16-bit PPG ch.3 output pin               |

|         | IN4      |                       | Input capture ch.4 trigger input pin     |

|         | P12      |                       | General-purpose I/O port                 |

| 103     | TIN0     | ı                     | 16-bit reload timer ch.0 TIN input pin   |

|         | PPG4     |                       | 16-bit PPG ch.4 output pin               |

#### **■ HANDLING DEVICES**

#### Strictly observe maximum rated voltages (preventing latch-up)

In CMOS IC devices, a condition known as latch-up may occur if voltages higher than Vcc or lower than Vss are applied to input or output pins other than medium or high withstand voltage pins, or if the voltage applied between VCC and VSS pins exceeds the rated voltage level. If a latch-up occurs, the power supply current may increase dramatically and may destroy semiconductor elements. When using semiconductor devices, always take sufficient care to avoid exceeding maximum ratings.

When the analog system power supply is switched on or off, be careful not to apply the analog power supply (AVcc, AVRH), the analog input voltages and the power supply voltage for the high current output buffer pins (DVcc) in excess of the digital power supply voltage (Vcc).

Once the digital power supply voltage (Vcc) has been disconnected, the analog power supply (AVcc, AVRH) and the power supply voltage for the high current output buffer pins (DVcc) may be turned on in any sequence.

#### Supply voltage stabilization

Rapid fluctuations in the power supply voltage can cause malfunctions even if the Vcc power supply voltage remains within the warranted operating range. It is recommended that the power supply be stabilized such that ripple fluctuations (P-P value) at commercial frequencies (50 Hz/60 Hz) be limited to within 10% of the standard Vcc value, and that transient fluctuations due to power supply switching, etc. be limited to a rate of 0.1 V/ms or less.

#### • Precautions when turning the power on

In order to prevent the built-in step-down circuits from malfunctioning, the time taken for the voltage to rise (0.2 V to 2.7 V) during power-on should be less than 50  $\mu$ s.

#### · Handling unused pins

If unused input pins are left open, they may cause malfunctions or latch-up which may lead to permanent damage to the semiconductor. Unused input pins should therefore be pulled up or pulled down through a resistor of at least  $2 \text{ k}\Omega$ .

Unused input/output pins may be set to the output state and left open, or set to the input state and connected to a pull-up or pull-down resistance of 2  $k\Omega$  or more.

#### • Handling A/D converter power supply pins

Even if the A/D converter is not used, the power supply pins should be connected such as  $AV_{CC} = V_{CC}$ , and  $AV_{SS} = AVRH = V_{SS}$ .

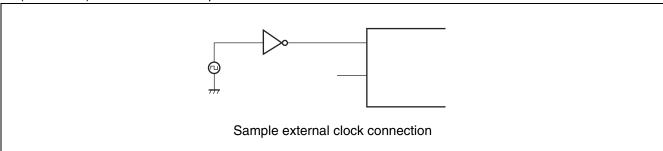

#### · Notes on using an external clock

Even when an external clock is used, an oscillation stabilization wait time is required following power-on reset or release from sub clock mode or stop mode. Furthermore, only the X0A pin should be driven when an external clock is used, with the X1A pin open as shown in the following diagram. Do not use high-speed oscillation pins (X0 and X1) for external clock input.

| Address                  | Register name                             | Symbol         | Read/write            | Resource name       | Initial value |

|--------------------------|-------------------------------------------|----------------|-----------------------|---------------------|---------------|

| 000024н                  |                                           | 00010          | R/W                   |                     | XXXXXXXXB     |

| 000025н                  | Compare clear register                    | CPCLR          | R/W                   |                     | XXXXXXXXB     |

| 000026н                  | Time and data was into a                  | TODT           | R/W                   | 16-bit              | 00000000в     |

| 000027н                  | Timer data register                       | TCDT           | R/W                   | free-run timer      | 00000000в     |

| 000028н                  | Lower timer control status register       | TCCSL          | R/W                   |                     | 00000000в     |

| 000029н                  | Higher timer control status register      | TCCSH          | R/W                   |                     | 01-00000в     |

| 00002Ан                  | Lower PPG0 control status register        | PCNTL0         | R/W                   | 16 hit DDC0         | 00000000в     |

| 00002Вн                  | Higher PPG0 control status register       | PCNTH0         | R/W                   | 16-bit PPG0         | 0000001в      |

| 00002Сн                  | Lower PPG1 control status register        | PCNTL1         | R/W                   | 16 hit DDC1         | 00000000в     |

| 00002Dн                  | Higher PPG1 control status register       | PCNTH1         | R/W                   | 16-bit PPG1         | 0000001в      |

| 00002Ен                  | Lower PPG2 control status register        | PCNTL2         | R/W                   | 16 hit DDC0         | 0000000В      |

| 00002Fн                  | Higher PPG2 control status register       | PCNTH2         | R/W                   | 16-bit PPG2         | 0000001в      |

| 000030н                  | External interrupt enable                 | ENIR           | R/W                   |                     | 00000000в     |

| 000031н                  | External interrupt request                | EIRR           | R/W                   | External interrupt  | 00000000в     |

| 000032н                  | Lower external interrupt level            | ELVRL          | R/W                   | External interrupt  | 00000000в     |

| 000033н                  | Higher external interrupt level           | ELVRH          | R/W                   |                     | 00000000в     |

| 000034н                  | Serial mode register 0                    | SMR0           | R/W, W                |                     | 00000000в     |

| 000035н                  | Serial control register 0                 | SCR0           | R/W, W                |                     | 0000000В      |

| 000036н                  | Reception/transmission data register 1    | RDR0/<br>TDR0  | R/W                   |                     | 0000000В      |

| 000037н                  | Serial status register 0                  | SSR0           | R/W, R                | UART                | 00001000в     |

| 000038н                  | Extended communication control register 0 | ECCR0          | R/W, R                | (LIN/SCI) 0         | 000000XXB     |

| 000039н                  | Extended status control register 0        | ESCR0          | R/W                   |                     | 00000100в     |

| 00003Ан                  | Baud rate generator register 00           | BGR00          | R/W                   |                     | 0000000В      |

| 00003Вн                  | Baud rate generator register 01           | BGR01          | R/W, R                |                     | 0000000В      |

| 00003Сн<br>to<br>00003Fн |                                           | (Disab         | led)                  |                     |               |

| 000040н<br>to<br>00004Fн | Area reserved for CAN C                   | ontroller 0. R | efer to " <b>■</b> CA | IN CONTROLLERS"     |               |

| 000050н                  | Lower timer control status register 0     | TMCSR0L        | R/W                   |                     | 0000000В      |

| 000051н                  | Higher timer control status register 0    | TMCSR0H        | R/W                   | 16-bit reload timer | ХХХ10000в     |

| 000052н                  | Timer register 0/relead register 0        | TMR0/          | DAM                   | 0                   | XXXXXXXXB     |

| 000053н                  | Timer register 0/reload register 0        | TMRLR0         | R/W                   |                     | XXXXXXXXB     |

| Address | Register name                             | Symbol        | Read/write | Resource name     | Initial value         |

|---------|-------------------------------------------|---------------|------------|-------------------|-----------------------|

| 0000Д4н | Lower timer control status register 2     | TMCSR2L       | R/W        | 16-bit            | 0000000В              |

| 0000Д5н | Higher timer control status register 2    | TMCSR2H       | R/W        | reload timer 2    | XXX10000 <sub>B</sub> |

| 0000Д6н | Lower timer control status register 3     | TMCSR3L       | R/W        | 16-bit            | 0000000В              |

| 0000D7н | Higher timer control status register 3    | TMCSR3H       | R/W        | reload timer 3    | ХХХ10000в             |

| 0000Д8н | Lower sound control register 1            | SGCRL1        | R/W        | Cound generator 1 | 0000000В              |

| 0000D9н | Higher sound control register 1           | SGCRH1        | R/W        | Sound generator 1 | 0XXXX100 <sub>B</sub> |

| 0000Дн  | Lower PPG3 control status register        | PCNTL3        | R/W        | 16-bit PPG3       | 0000000В              |

| 0000ДВн | Higher PPG3 control status register       | PCNTH3        | R/W        | 16-bit PPG3       | 0000001в              |

| 0000DСн | Lower PPG4 control status register        | PCNTL4        | R/W        | 16-bit PPG4       | 0000000В              |

| 0000DDн | Higher PPG4 control status register       | PCNTH4        | R/W        | 16-bit PPG4       | 0000001в              |

| 0000ДЕн | Lower PPG5 control status register        | PCNTL5        | R/W        | 16-bit PPG5       | 0000000В              |

| 0000DFн | Higher PPG5 control status register       | PCNTH5        | R/W        | 10-bit FFG5       | 0000001в              |

| 0000Е0н | Serial mode register 2                    | SMR2          | R/W, W     |                   | 0000000В              |

| 0000Е1н | Serial control register 2                 | SCR2          | R/W, W     |                   | 0000000В              |

| 0000Е2н | Reception/transmission data register 2    | RDR2/<br>TDR2 | R/W        |                   | 0000000В              |

| 0000ЕЗн | Serial status register 2                  | SSR2          | R/W, R     | UART              | 00001000в             |

| 0000Е4н | Extended communication control register 2 | ECCR2         | R/W, R     | (LIN/SCI) 2       | 000000XXB             |

| 0000Е5н | Extended status control register 2        | ESCR2         | R/W        |                   | 00000100в             |

| 0000Е6н | Baud rate generator register 20           | BGR20         | R/W        |                   | 0000000В              |

| 0000Е7н | Baud rate generator register 21           | BGR21         | R/W, R     |                   | 0000000В              |

| 0000Е8н | Serial mode register 3                    | SMR3          | R/W, W     |                   | 0000000В              |

| 0000Е9н | Serial control register 3                 | SCR3          | R/W, W     |                   | 0000000В              |

| 0000ЕАн | Reception/transmission data register 3    | RDR3/<br>TDR3 | R/W        |                   | 0000000В              |

| 0000ЕВн | Serial status register 3                  | SSR3          | R/W, R     | UART              | 00001000в             |

| 0000ЕСн | Extended communication control register 3 | ECCR3         | R/W, R     | (LIN/SCI) 3       | 000000XXB             |

| 0000ЕДн | Extended status control register 3        | ESCR3         | R/W        |                   | 00000100в             |

| 0000ЕЕн | Baud rate generator register 30           | BGR30         | R/W        |                   | 0000000В              |

| 0000EFн | Baud rate generator register 31           | BGR31         | R/W, R     |                   | 0000000В              |

| 001FF0н | Program address detection register 0      | PADR0         | R/W        |                   | XXXXXXX               |

| 001FF1н | Program address detection register 1      | PADR0         | R/W        |                   | XXXXXXX               |

| 001FF2н | Program address detection register 2      | PADR0         | R/W        | Address match     | XXXXXXX               |

| 001FF3н | Program address detection register 3      | PADR1         | R/W        | detection         | XXXXXXX               |

| 001FF4н | Program address detection register 4      | PADR1         | R/W        |                   | XXXXXXX               |

| 001FF5н | Program address detection register 5      | PADR1         | R/W        |                   | XXXXXXXXB             |

| Address       | Register name                                                    | Symbol          | Read/write            | Resource name     | Initial value         |  |  |  |  |  |  |  |

|---------------|------------------------------------------------------------------|-----------------|-----------------------|-------------------|-----------------------|--|--|--|--|--|--|--|

| 003700н       |                                                                  |                 |                       |                   | 1                     |  |  |  |  |  |  |  |

| to            | Area reserved for CAN C                                          | Controller 2. R | efer to " <b>■</b> CA | N CONTROLLERS"    |                       |  |  |  |  |  |  |  |

| 0037FFн       |                                                                  |                 |                       |                   |                       |  |  |  |  |  |  |  |

| 003800н<br>to | Area received for CAN C                                          | Controller 2 D  | ofor to "■ CA         | NI CONTDOLLEDO"   |                       |  |  |  |  |  |  |  |

| 0038FFн       | Area reserved for CAN Controller 3. Refer to "■ CAN CONTROLLERS" |                 |                       |                   |                       |  |  |  |  |  |  |  |

| 003900н       |                                                                  |                 |                       |                   |                       |  |  |  |  |  |  |  |

| to            | (Disabled)                                                       |                 |                       |                   |                       |  |  |  |  |  |  |  |

| 00391Fн       |                                                                  |                 |                       |                   |                       |  |  |  |  |  |  |  |

| 003920н       | PPG0 down counter register                                       | PDCR0           | R                     |                   | 11111111В             |  |  |  |  |  |  |  |

| 003921н       | The do down obtained regions.                                    | 1 20110         |                       | 16-bit PPG0       | 111111111             |  |  |  |  |  |  |  |

| 003922н       | PPG0 cycle setting register                                      | PCSR0           | W                     | 10 51(11 00       | 111111111             |  |  |  |  |  |  |  |

| 003923н       | Trade dydic setting register                                     | 1 00110         |                       |                   | 111111111             |  |  |  |  |  |  |  |

| 003924н       | PPG0 duty setting register                                       | PDUT0           | W                     |                   | 0000000В              |  |  |  |  |  |  |  |

| 003925н       | Prad daty setting register                                       | PDOTO           | VV                    | 16-bit PPG0       | 0000000в              |  |  |  |  |  |  |  |

| 003926н       | PPG0 output division setting register                            | PPGDIV0         | R/W, R                |                   | 11111100в             |  |  |  |  |  |  |  |

| 003927н       |                                                                  | (Disabl         | ed)                   |                   |                       |  |  |  |  |  |  |  |

| 003928н       | DDO4 dever country as sister.                                    | DDCD4           | Б                     |                   | 111111111             |  |  |  |  |  |  |  |

| 003929н       | PPG1 down counter register                                       | PDCR1           | R                     |                   | 111111111             |  |  |  |  |  |  |  |

| 00392Ан       | DDO4 I W II                                                      | D00D4           | CSR1 W DUT1 W         |                   | 111111111             |  |  |  |  |  |  |  |

| 00392Вн       | PPG1 cycle setting register                                      | PCSR1           |                       | 16-bit PPG1       | 111111111             |  |  |  |  |  |  |  |

| 00392Сн       |                                                                  | DD1174          |                       |                   | 0000000в              |  |  |  |  |  |  |  |

| 00392Dн       | PPG1 duty setting register                                       | PDUII           |                       |                   | 0000000в              |  |  |  |  |  |  |  |

| 00392Ен       | PPG1output division setting register                             | PPGDIV1         | R/W, R                |                   | 11111100в             |  |  |  |  |  |  |  |

| 00392Fн       | ,                                                                | (Disabl         | ed)                   |                   | 1                     |  |  |  |  |  |  |  |

| 003930н       |                                                                  | <u> </u>        |                       |                   | 111111111             |  |  |  |  |  |  |  |

| 003931н       | PPG2 down counter register                                       | PDCR2           | R                     |                   | 111111111             |  |  |  |  |  |  |  |

| 003932н       |                                                                  |                 |                       |                   | 11111111 <sub>B</sub> |  |  |  |  |  |  |  |

| 003933н       | PPG2 cycle setting register                                      | PCSR2           | W                     | 16-bit PPG2       | 111111111             |  |  |  |  |  |  |  |

| 003934н       |                                                                  |                 |                       |                   | 0000000B              |  |  |  |  |  |  |  |

| 003935н       | PPG2 duty setting register                                       | PDUT2           | W                     |                   | 0000000               |  |  |  |  |  |  |  |

| 003936н       | PPG2 output division setting register                            | PPGDIV2         | R/W, R                |                   | 11111100в             |  |  |  |  |  |  |  |

| 003937н       | ,                                                                |                 | , , , , ,             |                   | 1                     |  |  |  |  |  |  |  |

| to            |                                                                  | (Disabl         | ed)                   |                   |                       |  |  |  |  |  |  |  |

| 00393Fн       |                                                                  |                 | <del>, '</del>        |                   |                       |  |  |  |  |  |  |  |

| 003940н       | Input capture register 4                                         | IPCP4           | R                     |                   | XXXXXXXXB             |  |  |  |  |  |  |  |

| 003941н       | par saprare register i                                           | 5               | .,                    | Input capture 4/5 | XXXXXXX               |  |  |  |  |  |  |  |

| 003942н       | Input capture register 5                                         | IPCP5           | R                     | par captaro =/0   | XXXXXXXXB             |  |  |  |  |  |  |  |

| 003943н       | In particular or regional or                                     | 5. 5            |                       |                   | XXXXXXXXB             |  |  |  |  |  |  |  |

| Address                  | Register name                                                    | Symbol         | Read/write             | Resource name   | Initial value |  |  |  |  |

|--------------------------|------------------------------------------------------------------|----------------|------------------------|-----------------|---------------|--|--|--|--|

| 003998н                  | DIAMA access of the C                                            | DWO10          | DAM                    |                 | XXXXXXXXB     |  |  |  |  |

| 003999н                  | PWM1 compare register 3                                          | PWC13          | R/W                    |                 | XXXXXXXXB     |  |  |  |  |

| 00399Ан                  | DIAMA compare verietos o                                         | DMCoo          | D/M                    | Stepping motor  | XXXXXXX       |  |  |  |  |

| 00399Вн                  | PWM2 compare register 3                                          | PWC23          | R/W                    | controller 3    | XXXXXXX       |  |  |  |  |

| 00399Сн                  | PWM1 select register 3                                           | PWS13          | R/W                    |                 | 0000000В      |  |  |  |  |

| 00399Dн                  | PWM2 select register 3                                           | PWS23          | R/W                    |                 | Х000000В      |  |  |  |  |

| 00399Eн<br>to<br>0039A5н |                                                                  | (Disab         | led)                   |                 |               |  |  |  |  |

| 0039А6н                  | Flash write control register 0                                   | FWR0           | DAM                    |                 | 0000000В      |  |  |  |  |

| 0039А7н                  | Flash write control register 1                                   | FWR1           | - R/W                  | Flash I/F       | 0000000В      |  |  |  |  |

| 0039A8н<br>to<br>0039BFн | (Disabled)                                                       |                |                        |                 |               |  |  |  |  |

| 0039C0н<br>to<br>0039DFн | Area reserved for CAN Controller 2. Refer to "■ CAN CONTROLLERS" |                |                        |                 |               |  |  |  |  |

| 0039E0н<br>to<br>0039FFн | Area reserved for CAN C                                          | ontroller 3. F | Refer to " <b>■</b> CA | N CONTROLLERS"  |               |  |  |  |  |

| 003A00н<br>to<br>003AFFн | Area reserved for CAN C                                          | ontroller 0. F | Refer to " <b>■</b> CA | IN CONTROLLERS" |               |  |  |  |  |

| 003B00н<br>to<br>003BFFн | Area reserved for CAN C                                          | ontroller 1. F | Refer to " <b>■</b> CA | IN CONTROLLERS" |               |  |  |  |  |

| 003С00н<br>to<br>003СFFн | Area reserved for CAN C                                          | ontroller 0. F | Refer to " <b>■</b> CA | IN CONTROLLERS" |               |  |  |  |  |

| 003D00н<br>to<br>003DFFн | Area reserved for CAN C                                          | ontroller 1. F | Refer to " <b>■</b> CA | IN CONTROLLERS" |               |  |  |  |  |

| 003E00н<br>to<br>003EFFн | Area reserved for CAN C                                          | ontroller 2. F | Refer to " <b>■</b> CA | .N CONTROLLERS" |               |  |  |  |  |

| 003F00н<br>to<br>003FFFн | Area reserved for CAN Controller 3. Refer to "■ CAN CONTROLLERS" |                |                        |                 |               |  |  |  |  |

**List of Message Buffers (Data register)**

| Address                  |                          | ress                     | LISUUI                   | Message Buffers (Data regis |         | Abbro  |                               |  |  |  |  |

|--------------------------|--------------------------|--------------------------|--------------------------|-----------------------------|---------|--------|-------------------------------|--|--|--|--|

| CAN0                     | CAN1                     | CAN2                     | CAN3                     | Register                    | viation | Access | Initial Value                 |  |  |  |  |

| 003A80н<br>to<br>003A87н | 003B80н<br>to<br>003B87н | 003780н<br>to<br>003787н | 003880н<br>to<br>003887н | Data register 0 (8 bytes)   | DTR0    | R/W    | XXXXXXXXB<br>to<br>XXXXXXXXB  |  |  |  |  |

| 003A88н<br>to<br>003A8Fн | 003B88н<br>to<br>003B8Fн | 003788н<br>to<br>00378Fн | 003888н<br>to<br>00388Fн | Data register 1 (8 bytes)   | DTR1    | R/W    | XXXXXXXXB<br>to<br>XXXXXXXXB  |  |  |  |  |

| 003A90н<br>to<br>003A97н | 003В90н<br>to<br>003В97н | 003790н<br>to<br>003797н | 003890н<br>to<br>003897н | Data register 2 (8 bytes)   | DTR2    | R/W    | XXXXXXXXB<br>to<br>XXXXXXXXB  |  |  |  |  |

| 003A98н<br>to<br>003A9Fн | 003В98н<br>to<br>003В9Fн | 003798н<br>to<br>00379Fн | 003898н<br>to<br>00389Fн | Data register 3 (8 bytes)   | DTR3    | R/W    | XXXXXXXXB<br>to<br>XXXXXXXXB  |  |  |  |  |

| 003AA0н<br>to<br>003AA7н | 003BA0н<br>to<br>003BA7н | 0037A0н<br>to<br>0037A7н | 0038A0н<br>to<br>0038A7н | Data register 4 (8 bytes)   | DTR4    | R/W    | XXXXXXXXB<br>to<br>XXXXXXXXB  |  |  |  |  |

| 003AA8н<br>to<br>003AAFн | 003BA8н<br>to<br>003BAFн | 0037A8н<br>to<br>0037AFн | 0038A8н<br>to<br>0038AFн | Data register 5 (8 bytes)   | DTR5    | R/W    | XXXXXXXXB<br>to<br>XXXXXXXXXB |  |  |  |  |

| 003AB0н<br>to<br>003AB7н | 003BB0н<br>to<br>003BB7н | 0037B0н<br>to<br>0037B7н | 0038В0н<br>to<br>0038В7н | Data register 6 (8 bytes)   | DTR6    | R/W    | XXXXXXXXB<br>to<br>XXXXXXXXXB |  |  |  |  |

| 003AB8н<br>to<br>003ABFн | 003BB8н<br>to<br>003BBFн | 0037В8н<br>to<br>0037ВFн | 0038В8н<br>to<br>0038ВFн | Data register 7 (8 bytes)   | DTR7    | R/W    | XXXXXXXXB<br>to<br>XXXXXXXXXB |  |  |  |  |

| 003AC0н<br>to<br>003AC7н | 003BC0н<br>to<br>003BC7н | 0037C0н<br>to<br>0037C7н | 0038C0н<br>to<br>0038C7н | Data register 8 (8 bytes)   | DTR8    | R/W    | XXXXXXXXB<br>to<br>XXXXXXXXB  |  |  |  |  |

| 003AC8н<br>to<br>003ACFн | 003BC8н<br>to<br>003BCFн | 0037С8н<br>to<br>0037СFн | 0038С8н<br>to<br>0038СFн | Data register 9 (8 bytes)   | DTR9    | R/W    | XXXXXXXXB<br>to<br>XXXXXXXXB  |  |  |  |  |

| 003AD0н<br>to<br>003AD7н | 003BD0н<br>to<br>003BD7н | 0037D0н<br>to<br>0037D7н | 0038D0н<br>to<br>0038D7н | Data register 10 (8 bytes)  | DTR10   | R/W    | XXXXXXXXB<br>to<br>XXXXXXXXXB |  |  |  |  |

| 003AD8н<br>to<br>003ADFн | 003BD8н<br>to<br>003BDFн | 0037D8н<br>to<br>0037DFн | 0038D8н<br>to<br>0038DFн | Data register 11 (8 bytes)  | DTR11   | R/W    | XXXXXXXXB<br>to<br>XXXXXXXXXB |  |  |  |  |

| 003AE0н<br>to<br>003AE7н | 003BE0н<br>to<br>003BE7н | 0037E0н<br>to<br>0037E7н | 0038E0н<br>to<br>0038E7н | Data register 12 (8 bytes)  | DTR12   | R/W    | XXXXXXXXB<br>to<br>XXXXXXXXXB |  |  |  |  |

| 003AE8н<br>to<br>003AEFн | 003BE8н<br>to<br>003BEFн | 0037E8н<br>to<br>0037EFн | 0038E8н<br>to<br>0038EFн | Data register 13 (8 bytes)  | DTR13   | R/W    | XXXXXXXXB<br>to<br>XXXXXXXXB  |  |  |  |  |

| 003AF0н<br>to<br>003AF7н | 003BF0н<br>to<br>003BF7н | 0037F0н<br>to<br>0037F7н | 0038F0н<br>to<br>0038F7н | Data register 14 (8 bytes)  | DTR14   | R/W    | XXXXXXXXB<br>to<br>XXXXXXXXB  |  |  |  |  |

| 003AF8н<br>to<br>003AFFн | 003BF8н<br>to<br>003BFFн | 0037F8н<br>to<br>0037FFн | 0038F8н<br>to<br>0038FFн | Data register 15 (8 bytes)  | DTR15   | R/W    | XXXXXXXXB<br>to<br>XXXXXXXXB  |  |  |  |  |

### ■ INTERRUPT SOURCES, INTERRUPT VECTORS, AND INTERRUPT CONTROL REGISTERS

| Interrupt source                                                  | El <sup>2</sup> OS | Int | terrupt | vector              | Interru<br>re | Priority               |          |

|-------------------------------------------------------------------|--------------------|-----|---------|---------------------|---------------|------------------------|----------|

| ·                                                                 | corresponding      | Nun | nber    | Address             | ICR           | Address                | - *2     |

| Reset                                                             | ×                  | #08 | 08н     | FFFFDC <sub>H</sub> | _             | _                      | High     |

| INT9 instruction                                                  | ×                  | #09 | 09н     | FFFFD8 <sub>H</sub> | _             | _                      | <b>A</b> |

| Exception processing                                              | ×                  | #10 | 0Ан     | FFFFD4 <sub>H</sub> | _             | _                      | Ī Ī      |

| CAN0 received/CAN2 received                                       | ×                  | #11 | 0Вн     | FFFFD0 <sub>H</sub> |               |                        |          |

| CAN0 transmitted/node status/<br>CAN2 transmitted/node status     | ×                  | #12 | 0Сн     | FFFFCCH             | ICR00         | 0000В0н*1              |          |

| CAN1 received/CAN3 received                                       | ×                  | #13 | 0Дн     | FFFFC8 <sub>H</sub> |               |                        | 1        |

| CAN1 transmitted/node status/<br>CAN3 transmitted/node status/SIO | ×                  | #14 | 0Ен     | FFFFC4 <sub>H</sub> | ICR01         | 0000В1н*1              |          |

| Input capture 0                                                   | Δ                  | #15 | 0Гн     | FFFFC0 <sub>H</sub> |               |                        |          |

| DTP/ external interrupt - ch.0/ch.1 detected                      | Δ                  | #16 | 10н     | FFFFBC <sub>H</sub> | ICR02         | 0000B2н*1              |          |

| Reload timer 0                                                    | Δ                  | #17 | 11н     | FFFFB8 <sub>H</sub> | ICR03         | 0000B3н*1              | 1        |

| Reload timer 2                                                    | Δ                  | #18 | 12н     | FFFFB4 <sub>H</sub> | ICHU3         | 0000ВЗН .              |          |

| Input capture 1                                                   | Δ                  | #19 | 13н     | FFFFB0 <sub>H</sub> |               | 0000В4н*1              |          |

| DTP/ external interrupt - ch.2/ch.3 detected                      | Δ                  | #20 | 14н     | FFFFACH             | ICR04         |                        |          |

| Input capture 2                                                   | Δ                  | #21 | 15н     | FFFFA8 <sub>H</sub> | ICR05         | 0000B5н*1              |          |

| Reload timer 3                                                    | Δ                  | #22 | 16н     | FFFFA4 <sub>H</sub> | ICHUS         | ООООБЭН .              |          |

| Input capture 3/4/5/6/7                                           | Δ                  | #23 | 17н     | FFFFA0 <sub>H</sub> |               |                        |          |

| DTP/ external interrupt - ch.4/ ch.5 detected UART3 RX            | Δ                  | #24 | 18н     | FFFF9C <sub>H</sub> | ICR06         | 0000В6н*1              |          |

| PPG timer 0                                                       | Δ                  | #25 | 19н     | FFFF98 <sub>H</sub> |               |                        | 1        |

| DTP/ external interrupt - ch.6/ ch.7 detected UART3 TX            | Δ                  | #26 | 1Ан     | FFFF94 <sub>H</sub> | ICR07         | 0000В7н*1              |          |

| PPG timer 1                                                       | Δ                  | #27 | 1Вн     | FFFF90 <sub>H</sub> | ICR08         | 0000B8н*1              |          |

| Reload timer 1                                                    | Δ                  | #28 | 1Сн     | FFFF8C <sub>H</sub> | ICHUO         | ООООВОН .              |          |

| PPG timer 2/3/4/5                                                 | 0                  | #29 | 1Dн     | FFFF88 <sub>H</sub> |               |                        | ]        |

| Real time watch timer watch timer (sub clock)                     | ×                  | #30 | 1Ен     | FFFF84 <sub>H</sub> | ICR09         | 0000В9н*1              |          |

| Free-run timer overflow/clear                                     | ×                  | #31 | 1Fн     | FFFF80 <sub>H</sub> | ICR10         | 0000BAн *1             |          |

| A/D converter conversion complete                                 | 0                  | #32 | 20н     | FFFF7C <sub>H</sub> | IUNIU         | UUUUDAH "              |          |

| Sound generator 0/1                                               | ×                  | #33 | 21н     | FFFF78 <sub>H</sub> | ICD11         | 0000BBн*1              | ]        |

| Time-base timer                                                   | ×                  | #34 | 22н     | FFFF74 <sub>H</sub> | ICR11         | UUUUDDH                |          |

| UART2 RX                                                          | 0                  | #35 | 23н     | FFFF70 <sub>H</sub> | ICR12         | 0000BC <sub>н</sub> *1 | ] ♦      |

| UART2 TX                                                          | Δ                  | #36 | 24н     | FFFF6C <sub>H</sub> | IUNIZ         | OUUDCH '               | Low      |

#### (Continued)

| Interrupt source                 | El <sup>2</sup> OS | Interrupt vector |                   |                     | Interre<br>re | Priority               |          |  |

|----------------------------------|--------------------|------------------|-------------------|---------------------|---------------|------------------------|----------|--|

| ·                                | corresponding      | Number           |                   | Address             | ICR           | Address                | 2        |  |

| UART 1 RX                        | 0                  | #37              | 25н FFFF68н ICR13 |                     | 0000BDн*1     | High                   |          |  |

| UART 1 TX                        | Δ                  | #38              | 26н               | FFFF64 <sub>H</sub> | ICHIS         | OOOODH .               | <b>A</b> |  |

| UART 0 RX                        | 0                  | #39              | 27н               | FFFF60 <sub>H</sub> | ICR14         | 0000BEн*1              |          |  |

| UART 0 TX                        | Δ                  | #40              | 28н               | FFFF5C <sub>H</sub> | ION14         | 0000BEH                |          |  |

| Flash memory status              | ×                  | #41              | 29н               | FFFF58⊦             | ICR15         | 0000BF <sub>H</sub> *1 | 1 ₩      |  |

| Delay interrupt generator module | ×                  | #42              | 2Ан               | FFFF54 <sub>H</sub> | 101113        | OOOODEH '              | Low      |  |

©: Usable, and has expanded intelligent I/O services (EI2OS) stop function

○ : Usable

$\triangle\,$  : Usable when interrupt sources sharing ICR are not in use

× : Unusable

- \*1 : Peripheral functions that share the ICR register have the same interrupt level.

- If the expanded intelligent I/O service (El<sup>2</sup>OS) is used with peripheral functions that share the ICR register, only one of the peripheral functions that share the register can be used.

- When the expanded intelligent I/O service (El<sup>2</sup>OS) is specified for one of the peripheral functions that shares the ICR register, interrupts cannot be used from the other peripheral functions that share the register.

- \*2 : Priority applies when interrupts of the same level are generated.

#### (Continued)

- \*5 : Average output current is defined as the average value of the current flowing through any one of the corresponding pins within a period of 100 ms. The "average value" can be calculated by multiplying the "operating current" by the "operating factor".

- \*6 : Average total output current is defined as the average value of the current flowing through all of the corresponding pins within a period of 100 ms. The "average value" can be calculated by multiplying the "operating current" by the "operating factor".

- \*7: Applicable to pins: P10 to P15,P50 to P57,P60 to P67,P70 to P77,P80 to P87,PC0 to PC7,PD0 to PD6, PE0 to PE2

- Use within recommended operating conditions.

- Use at DC voltage (current) .

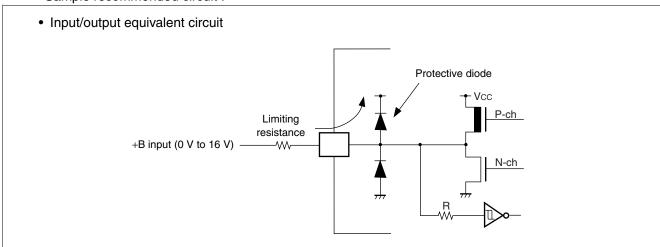

- The +B signal should always be applied with a limiting resistance placed between the +B signal and the microcontroller.

- The value of the limiting resistance should be set so that when the +B signal is applied, the input current to the microcontroller pin does not exceed rated values, either instantaneously or for prolonged periods.

- Note that when the microcontroller drive current is low, such as in the power saving modes, the +B input potential may pass through the protective diode and increase the potential at the Vcc pin, and this may affect other devices.

- Note that if a +B signal is input when the microcontroller power supply is off (not fixed at 0 V), the microcontroller may partially malfunction on power supplied through the +B signal pin.

- Note that if the +B input is applied during power-on, the power supply voltage may reach a level such that the power-on reset does not function due to the power supplied from the +B signal.

- Care must be taken not to leave +B input pins open.

- Note that analog system input/output pins (LCD drive pins, comparator input pins, etc.) cannot accept +B signal inputs.

- Sample recommended circuit :

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

### 3. DC Characteristics

(Vcc = 5.0 V  $\pm 10\%$ , Vss = DVss = AVss = 0.0 V, T<sub>A</sub> = -40 °C to +105 °C)

|                            |         |      |                                                                                               |         | Value |         |      | <u> </u>                                                      |

|----------------------------|---------|------|-----------------------------------------------------------------------------------------------|---------|-------|---------|------|---------------------------------------------------------------|

| Parameter                  | Symbol  | name | Conditions                                                                                    | Min     | Тур   | Max     | Unit | Remarks                                                       |

|                            | VIHA    |      | _                                                                                             | 0.8 Vcc | _     | _       | ٧    | Pin inputs if<br>Automotive input<br>levels are selected      |

| "H" level<br>input voltage | VIHS    |      | _                                                                                             | 0.8 Vcc |       |         | V    | Pin inputs if CMOS<br>hysteresis input<br>levels are selected |

|                            | VIHC    | _    | _                                                                                             | 0.7 Vcc |       |         | ٧    | RST input pin (CMOS hysteresis)                               |

|                            | VILA    |      | _                                                                                             | _       |       | 0.5 Vcc | V    | Pin inputs if<br>Automotive input<br>levels are selected      |

| "L" level<br>input voltage | VILS    |      | _                                                                                             |         | _     | 0.2 Vcc | V    | Pin inputs if CMOS<br>hysteresis input<br>levels are selected |

|                            | VILR    | _    | _                                                                                             |         |       | 0.3 Vcc | ٧    | RST input pin (CMOS hysteresis)                               |

|                            | Icc     |      | Maximum operating frequency F <sub>CP</sub> = 32 MHz, normal operation                        |         | 35    | 45      | mA   |                                                               |

|                            | 100     |      | Maximum operating frequency F <sub>CP</sub> = 32 MHz, writing Flash memory                    |         | 55    | 65      | mA   |                                                               |

|                            | Iccs    |      | Operating frequency<br>Fcp = 32 MHz,<br>sleep mode                                            |         | 13    | 20      | mA   |                                                               |

|                            | Істѕ    |      | Operating frequency FCP = 2 MHz, time-base timer mode                                         | _       | 0.6   | 1.0     | mA   |                                                               |

| Powersupply current*       | ICTSPLL | Vcc  | Operating frequency FCP = 32 MHz, PLL timer mode, External frequency = 4 MHz                  | _       | 2.5   | 4       | mA   |                                                               |

|                            | Iccl    |      | Operating frequency $F_{CP} = 8 \text{ kHz}, T_A = +25 ^{\circ}\text{C},$ sub clock operation | _       | 120   | 270     | μΑ   |                                                               |

|                            | Iccls   |      | Operating frequency $F_{CP} = 8 \text{ kHz}, T_A = +25 ^{\circ}\text{C},$ sub sleep operation |         | 100   | 200     | μΑ   |                                                               |

|                            | Ісст    |      | Operating frequency $F_{CP} = 8 \text{ kHz}, T_A = +25 ^{\circ}\text{C},$ watch mode          | _       | 90    | 180     | μΑ   |                                                               |

|                            | Іссн    |      | T <sub>A</sub> = + 25 °C, stop mode                                                           | _       | 80    | 170     | μΑ   |                                                               |

(Vcc = 5.0 V  $\pm 10\%$ , Vss = DVss = AVss = 0.0 V, T<sub>A</sub> = -40 °C to +105 °C)

| Davamatav                                 | Ole ed           | Din nome                                                                                      | O a maliki a ma                                              | V         | alue |      | 11   | Domorko                                 |

|-------------------------------------------|------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----------|------|------|------|-----------------------------------------|

| Parameter                                 | Symbol           | Pin name                                                                                      | Conditions                                                   | Min       | Тур  | Max  | Unit | Remarks                                 |

| Input leakage current                     | lı∟              | All input pins                                                                                | Vcc = DVcc = AVcc = 5.5 V,<br>Vss < V <sub>I</sub> < Vcc     | _         |      | 10   | μΑ   |                                         |

| Input capacitance 1                       | Cin1             | All pins except<br>VCC, VSS,<br>DVCC, DVSS,<br>AVCC, AVSS,<br>C,<br>P70 to P77,<br>P80 to P87 | _                                                            | _         | _    | 15   | pF   |                                         |

| Input capacitance 2                       | C <sub>IN2</sub> | P70 to P77,<br>P80 to P87                                                                     | _                                                            | _         |      | 45   | pF   |                                         |

| Pull-up resistance                        | Rup              | RST                                                                                           | _                                                            | 25        | 50   | 100  | kΩ   |                                         |

| Pull-down<br>resistance                   | Roown            | MD2                                                                                           | _                                                            | _         | _    | 100  | kΩ   | Excluding<br>Flash<br>memory<br>product |

| General-purpose output "H" voltage        | Vон1             | All pins except<br>P70 to P77,<br>P80 to P87                                                  | Vcc = 4.5 V,<br>Іон = -4.0 mA                                | Vcc - 0.5 |      |      | V    |                                         |

| Stepping motor output "H" voltage         | V <sub>OH2</sub> | P70 to P77,<br>P80 to P87                                                                     | $V_{CC} = 4.5 \text{ V},$<br>$I_{OH} = -30.0 \text{ mA}$     | Vcc - 0.5 | _    | _    | ٧    |                                         |

| General-purpose output "L" voltage        | V <sub>OL1</sub> | All pins except<br>P70 to P77,<br>P80 to P87                                                  | Vcc = 4.5 V,<br>IoL = 4.0 mA                                 | _         |      | 0.4  | ٧    |                                         |

| Stepping motor output "L" voltage         | V <sub>OL2</sub> | P70 to P77,<br>P80 to P87                                                                     | Vcc = 4.5 V,<br>loL = 30.0 mA                                | _         | _    | 0.55 | V    |                                         |

| Stepping motor output phase variation "H" | ΔVон             | PWM1Pn,<br>PWM1Mn,<br>PWM2Pn,<br>PWM2Mn,<br>n = 0 to 3                                        | Vcc = 4.5 V,<br>Iон = -30.0 mA,<br>maximum deviation<br>Vон2 | _         | _    | 90   | mV   |                                         |

| Stepping motor output phase variation "L" | ΔVoL             | PWM1Pn,<br>PWM1Mn,<br>PWM2Pn,<br>PWM2Mn,<br>n = 0 to 3                                        | Vcc = 4.5 V,<br>IoL = 30.0 mA,<br>maximum deviation<br>VoH2  | _         | _    | 90   | mV   |                                         |

| Lopiu                                     |                  | Between V0<br>and V1,                                                                         |                                                              | 50        | 100  | 200  | kΩ   | Evaluation product                      |

| LCD internal divider resistance           | RLCD             | Between V1<br>and V2,<br>Between V2<br>and V3                                                 | _                                                            | 8.75      | 12.5 | 17.0 | kΩ   | Flash<br>memory<br>product              |

#### • Guaranteed PLL Operation Range

Internal operating clock frequency vs. Power supply voltage

Power supply voltage Vcc (V)

Range of warranted PLL operation

Namal operating range

Internal clock fcp (MHz)

Notes: • For PLL  $1 \times$  only, use with tcp = 4 MHz or greater.

• Refer to "5. A/D Converter (1) Electrical Characteristics" for details on the A/D converter operating frequency.

#### (4) UART0/1/2/3 (LIN/SCI)

• Bit setting: ESCR0/1/2/3:SCES=0, ECCR0/1/2/3:SCDE=0

$(Vcc = 5.0 V\pm 10 \%, Vss = AVss = 0.0 V, T_A = -40 °C to +105 °C)$

| Dougnator                                      | Cumbal         | Din nome                      | Conditions                              | Va         | lue        | Heit |

|------------------------------------------------|----------------|-------------------------------|-----------------------------------------|------------|------------|------|

| Parameter                                      | Symbol         | Pin name                      | Conditions                              | Min        | Max        | Unit |

| Serial clock cycle time                        | tscyc          | SCK0 to SCK3                  |                                         | 5 tcp      | _          | ns   |

| $SCK \downarrow \to SOT$ delay time            | tsLovi         | SCK0 to SCK3,<br>SOT0 to SOT3 | Internal shift clock<br>mode output pin | - 50       | + 50       | ns   |

| Valid SIN → SCK ↑                              | tıvsнı         | SCK0 to SCK3,                 | C <sub>L</sub> = 80 pF + 1TTL           | tcp + 80   | _          | ns   |

| $SCK \uparrow \rightarrow valid SIN hold time$ | <b>t</b> shixi | SIN0 to SIN3                  |                                         | 0          | _          | ns   |

| Serial clock "L" pulse width                   | <b>t</b> slsh  | CCKO to CCKO                  |                                         | 3 tcp - tr | _          | ns   |

| Serial clock "H" pulse width                   | <b>t</b> shsl  | SCK0 to SCK3                  |                                         | tcp + 10   | _          | ns   |

| $SCK \downarrow \to SOT$ delay time            | tslove         | SCK0 to SCK3,<br>SOT0 to SOT3 | External shift clock                    |            | 2 tcp + 60 | ns   |

| Valid SIN $\rightarrow$ SCK $↑$                | tivshe         | SCK0 to SCK3,                 | mode output pin<br>C∟ = 80 pF + 1TTL    | 30         | _          | ns   |

| $SCK \uparrow \rightarrow valid SIN hold time$ | <b>t</b> shixe | SIN0 to SIN3                  | 00 = 00 pr + 1112                       | tcp + 30   | _          | ns   |

| SCK ↓ time                                     | tr             | SCK0 to SCK3                  |                                         | _          | 10         | ns   |

| SCK ↑ time                                     | <b>t</b> R     | SCRU IU SCRS                  |                                         | _          | 10         | ns   |

Notes: • Depending on the machine clock frequency to be used, the maximum baud rate may be limited by some parameters. These parameters are shown in "MB90920 series hardware manual".

• C<sub>L</sub> is the load capacitance connected to the pin during testing.

• tcp is the internal operating clock cycle time. Refer to "(1) Clock timing".

#### • Bit setting: ESCR0/1/2/3:SCES=1, ECCR0/1/2/3:SCDE=0

$(Vcc = 5.0 V \pm 10\%, Vss = AVss = 0.0 V, T_A = -40 °C to +105 °C)$

| Parameter                                         | Cumbal                    | Din nome                      | Conditions                                                               | Value      |            | Hoit |  |

|---------------------------------------------------|---------------------------|-------------------------------|--------------------------------------------------------------------------|------------|------------|------|--|

| Parameter                                         | Parameter Symbol Pin name |                               | Conditions                                                               | Min        | Max        | Unit |  |

| Serial clock cycle time                           | tscyc                     | SCK0 to SCK3                  |                                                                          | 5 tcp      | _          | ns   |  |

| SCK $\uparrow \rightarrow$ SOT delay time         | <b>t</b> shovi            | SCK0 to SCK3,<br>SOT0 to SOT3 | Internal shift clock<br>mode output pin<br>C <sub>L</sub> = 80 pF + 1TTL | - 50       | + 50       | ns   |  |

| Valid SIN $\rightarrow$ SCK $↓$                   | tıvslı                    | SCK0 to SCK3,                 |                                                                          | tcp + 80   | _          | ns   |  |

| $SCK \downarrow \to valid \; SIN \; hold \; time$ | tslixi                    | SIN0 to SIN3                  |                                                                          | 0          | _          | ns   |  |

| Serial clock "H" pulse width                      | <b>t</b> shsl             | SCK0 to SCK3                  |                                                                          | 3 tcp - tR | _          | ns   |  |

| Serial clock "L" pulse width                      | <b>t</b> slsh             | 30KU 10 30K3                  |                                                                          | tcp + 10   | _          | ns   |  |

| $SCK \uparrow \rightarrow SOT$ delay time         | tshove                    | SCK0 to SCK3,<br>SOT0 to SOT3 | External shift clock                                                     | _          | 2 tcp + 60 | ns   |  |

| Valid SIN → SCK $\downarrow$                      | tivsle                    | SCK0 to SCK3,                 | mode output pin $C_L = 80 \text{ pF} + 1 \text{TTL}$                     | 30         | _          | ns   |  |

| $SCK \downarrow \to valid \; SIN \; hold \; time$ | tslixe                    | SIN0 to SIN3                  |                                                                          | tcp + 30   | _          | ns   |  |

| SCK ↓ time                                        | tr                        | SCK0 to SCK0                  |                                                                          | _          | 10         | ns   |  |

| SCK ↑ time                                        | <b>t</b> R                | SCK0 to SCK3                  |                                                                          | _          | 10         | ns   |  |

Notes: • Depending on the machine clock frequency to be used, the maximum baud rate may be limited by some parameters. These parameters are shown in "MB90920 series hardware manual".

- C<sub>L</sub> is the load capacitance connected to the pin during testing.

- top is the internal operating clock cycle time. Refer to "(1) Clock timing".

#### 5. A/D Converter

#### (1) Electrical Characteristics

(Vcc = AVcc = AVRH = 4.0 V to 5.5 V, Vss = AVss = 0.0 V,  $T_A = -40$  °C to +105 °C)

| Parameter                     | Cumbal | Din nome   | Value             |                   |                   |      | Domostro                |  |

|-------------------------------|--------|------------|-------------------|-------------------|-------------------|------|-------------------------|--|

| Parameter                     | Symbol | Pin name   | Min               | Тур               | Max               | Unit | Remarks                 |  |

| Resolution                    |        |            |                   | _                 | 10                | bit  |                         |  |

| Total error                   | _      | _          | - 3.0             | _                 | + 3.0             | LSB  |                         |  |

| Non-linear error              | _      | _          | - 2.5             | _                 | + 2.5             | LSB  |                         |  |

| Differential linear error     | _      | _          | <b>– 1.9</b>      | _                 | + 1.9             | LSB  |                         |  |

| Zero transition voltage       | Vот    | AN0 to AN7 | AVss –<br>1.5 LSB | AVss +<br>0.5 LSB | AVss +<br>2.5 LSB | V    | 1 LSB =                 |  |

| Full scale transition voltage | VFST   | AN0 to AN7 | AVRH –<br>3.5 LSB | AVRH –<br>1.5 LSB | AVRH +<br>0.5 LSB | V    | (AVRH – AVss) /<br>1024 |  |

| Sampling time                 | tsmp   | _          | 0.4               |                   | 16500             |      | 4.5 V ≤ AVcc ≤ 5.5 V    |  |

|                               |        |            | 1.0               |                   | 16500             | μs   | 4.0 V ≤ AVcc ≤ 4.5 V    |  |

| Compare time                  | tсмр   | _          | 0.66              |                   |                   | μs   | 4.5 V ≤ AVcc ≤ 5.5 V    |  |

|                               |        |            | 2.2               |                   |                   |      | 4.0 V ≤ AVcc ≤ 4.5 V    |  |

| A/D conversion time           | tcnv   | _          | 1.44              |                   | _                 | μs   | *1                      |  |

| Analog port input current     | lain   | AN0 to AN7 | - 0.3             | _                 | + 10              | μА   |                         |  |

| Analog input voltage          | Vain   | AN0 to AN7 | 0                 | _                 | AVRH              | V    |                         |  |

| Reference voltage             | AV+    | AVRH       | AVss + 2.7        | _                 | AVcc              | V    |                         |  |

| Davier aventy avent           | lΑ     | AVcc       | _                 | 2.3               | 6.0               | mA   |                         |  |

| Power supply current          | Іан    | AVCC       | _                 | _                 | 5                 | μΑ   | *2                      |  |

| Reference voltage             | IR     | AVRH       | _                 | 520               | 900               | μΑ   | Vavrh = 5.0 V           |  |

| supply current IRH            |        | AVIIII     |                   |                   | 5                 | μΑ   | *2                      |  |

| Inter-channel variation       |        | AN0 to AN7 |                   |                   | 4                 | LSB  |                         |  |

<sup>\*1 :</sup> The time per channel (4.5 V  $\leq$  AVcc  $\leq$  5.5 V, and internal operating frequency = 32 MHz) .

<sup>\*2 :</sup> Defined as supply current (when  $V_{CC} = AV_{CC} = AV_{CC}$

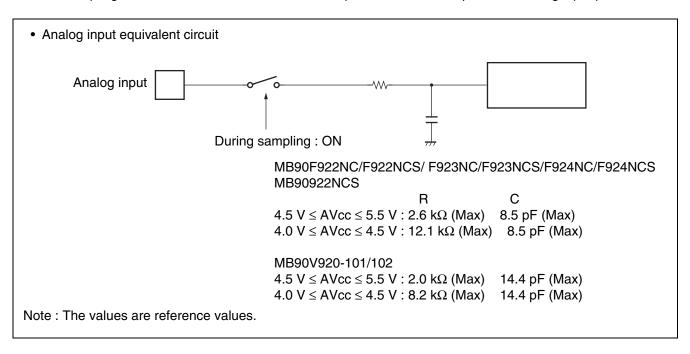

#### • Notes on the external impedance and sampling time of analog inputs

A/D converter with sample and hold circuit. If the external impedance is too high to keep sufficient sampling time, the analog voltage charged to the internal sample and hold capacitor is insufficient, adversely affecting A/D conversion precision. Therefore, to satisfy the A/D conversion precision standard, consider the relationship between the external impedance and minimum sampling time and either adjust the register value and operating frequency or decrease the external impedance so that the sampling time is longer than the minimum value. If the sampling time is still not sufficient, connect a capacitor of about 0.1  $\mu$ F to the analog input pin.

### 6. Flash Memory Program/Erase Characteristics

| Parameter                            | Conditions                                | Value |     |     | Unit  | Remarks                               |

|--------------------------------------|-------------------------------------------|-------|-----|-----|-------|---------------------------------------|

| Parameter                            |                                           | Min   | Тур | Max | Offic | nemarks                               |

| Sector erase time                    | T <sub>A</sub> = + 25 °C<br>Vcc = 5.0 V   | _     | 0.9 | 3.6 | s     | Excludes pre-programming before erase |

| Word (16-bit width) programming time |                                           | _     | 23  | 370 | μs    | Excludes system-level overhead        |

| Chip programming time                | $T_A = +25  ^{\circ}C,$ $V_{CC} = 5.0  V$ | _     | 3.4 | 55  | s     |                                       |

| Erase/program cycle                  | _                                         | 10000 |     | _   | cycle |                                       |

| Flash memory data retention time     | Average<br>T <sub>A</sub> = + 85 °C       | 20    |     | _   | year  | *                                     |

$<sup>^*</sup>$ : This value is calculated from the results of evaluating the reliability of the technology (using Arrhenius equation to translate high temperature measurements into normalized value at + 85  $^{\circ}$ C).

### **■** ORDERING INFORMATION

| Part number                                                                                         | Package                                | Remarks        |

|-----------------------------------------------------------------------------------------------------|----------------------------------------|----------------|

| MB90F922NCPMC MB90F922NCSPMC MB90922NCSPMC MB90F923NCPMC MB90F923NCSPMC MB90F924NCPMC MB90F924NCPMC | 120-pin plastic LQFP<br>(FPT-120P-M21) |                |

| MB90V920-101CR<br>MB90V920-102CR                                                                    | 299-pin ceramic PGA<br>(PGA-299C-A01)  | For evaluation |

### **■ MAJOR CHANGES IN THIS EDITION**

| Page | Section                                            | Change Results                                                                                |

|------|----------------------------------------------------|-----------------------------------------------------------------------------------------------|

| 12   | ■I/O CIRCUIT TYPE                                  | Corrected the circuit type B.                                                                 |

| 20   | ■ HANDLING DEVICES                                 | Added the following items;                                                                    |

| 31   | ■ I/O MAP                                          | Corrected "Address: 003970н".<br>Clock supervisor control register → (Disabled)               |

| 46   | ■ ELECTRICAL CHARACTERISTICS 3. DC Characteristics | Added the item for "LCD output impedance".                                                    |

| 68   | ■ ORDERING INFORMATION                             | Corrected the part numbers;<br>MB90V920-101 → MB90V920-101CR<br>MB90V920-102 → MB90V920-102CR |

The vertical lines marked in the left side of the page show the changes.