Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Obsolete                                                                          |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | F <sup>2</sup> MC-16LX                                                            |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 32MHz                                                                             |

| Connectivity               | CANbus, LINbus, UART/USART                                                        |

| Peripherals                | LCD, LVD, POR, PWM, WDT                                                           |

| Number of I/O              | 93                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | Mask ROM                                                                          |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 10K × 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                         |

| Data Converters            | A/D 8x8/10b                                                                       |

| Oscillator Type            | External                                                                          |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

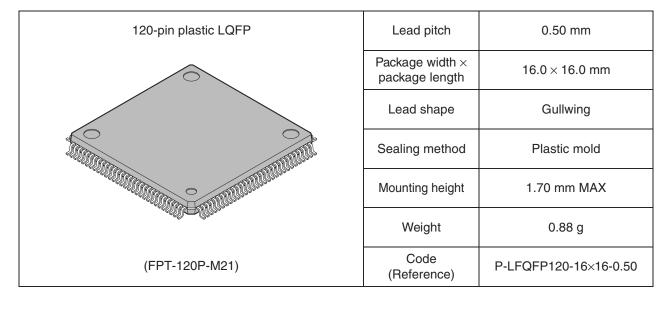

| Package / Case             | 120-LQFP                                                                          |

| Supplier Device Package    | 120-LQFP (16x16)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90922ncspmc-gs-181e1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 16-bit Microcontroller

CMOS

# F<sup>2</sup>MC-16LX MB90920 Series

# MB90F922NC/F922NCS/922NCS/F923NC/F923NCS/ MB90F924NC/F924NCS/V920-101/V920-102

### DESCRIPTION

The MB90920 series is a family of general-purpose FUJITSU SEMICONDUCTOR 16-bit microcontrollers designed for applications such as vehicle instrument panel control.

The instruction set retains the AT architecture from the F<sup>2</sup>MC-8L and F<sup>2</sup>MC-16LX families, with further refinements including high-level language instructions, extended addressing modes, improved multiplication and division operations (signed), and bit processing. In addition, long word processing is made possible by the inclusion of a built-in 32-bit accumulator.

Note : F<sup>2</sup>MC is the abbreviation of FUJITSU Flexible Microcontroller.

### ■ FEATURES

Clock

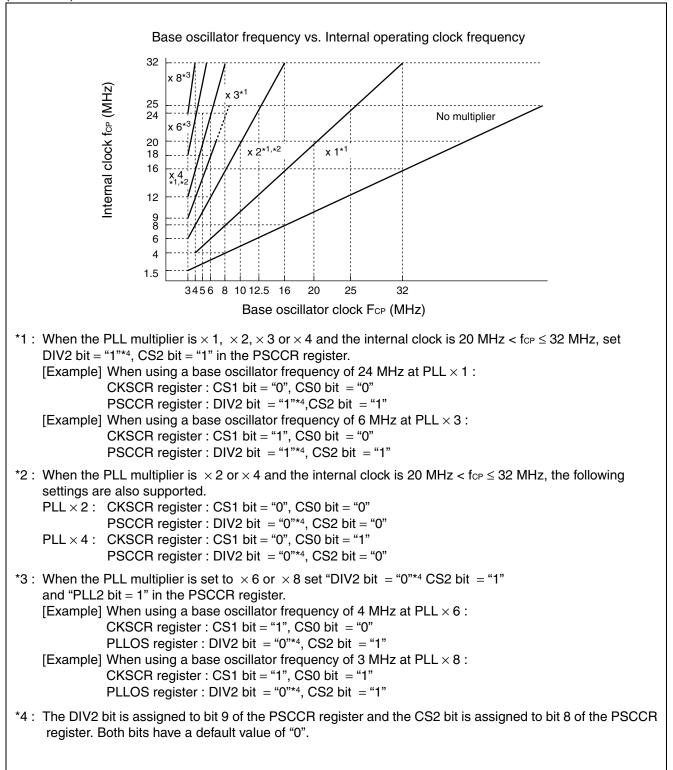

Built-in PLL clock frequency multiplication circuit.

Selection of machine clocks (PLL clocks) is allowed among frequency division by two on oscillation clock, and multiplication of 1 to 8 times of oscillation clock (for 4 MHz oscillation clock, 4 MHz to 32 MHz). Operation by sub clock (up to 50 kHz : 100 kHz oscillation clock divided by two) is allowed.

- 16-bit input capture (8 channels) Detects rising, falling, or both edges.

- 16-bit capture register × 8

The value of a 16-bit free-run timer counter is latched upon detection of an edge input to pin and an interrupt request is generated.

(Continued)

For the information for microcontroller supports, see the following web site.

This web site includes the **"Customer Design Review Supplement"** which provides the latest cautions on system development and the minimal requirements to be checked to prevent problems before the system development.

http://edevice.fujitsu.com/micom/en-support/

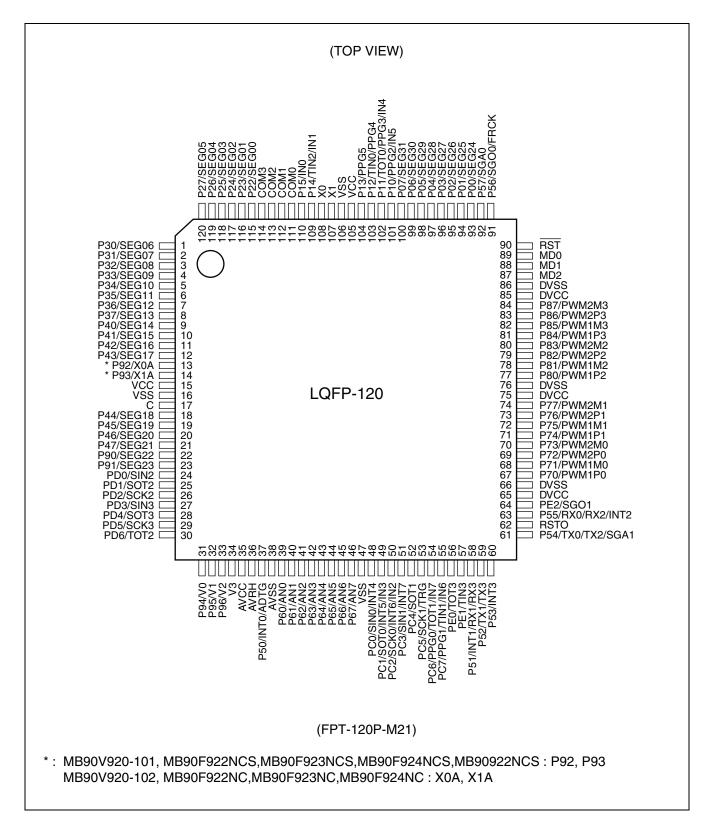

### ■ PIN ASSIGNMENT

| Pin no. | Pin name | I/O circuit<br>type*1 | Function                                         |

|---------|----------|-----------------------|--------------------------------------------------|

| 70      | P73      | <br>- L               | General-purpose output-only port                 |

| 70      | PWM2M0   |                       | Stepping motor controller ch.0 output pin        |

| 71      | P74      | - L                   | General-purpose output-only port                 |

| / 1     | PWM1P1   |                       | Stepping motor controller ch.1 output pin        |

| 72      | P75      | L                     | General-purpose output-only port                 |

| 12      | PWM1M1   |                       | Stepping motor controller ch.1 output pin        |

| 73      | P76      | <br>- L               | General-purpose output-only port                 |

| 73      | PWM2P1   |                       | Stepping motor controller ch.1 output pin        |

| 74      | P77      | L                     | General-purpose output-only port                 |

| 74      | PWM2M1   |                       | Stepping motor controller ch.1 output pin        |

| 77      | P80      | L                     | General-purpose output-only port                 |

| 11      | PWM1P2   |                       | Stepping motor controller ch.2 output pin        |

| 78      | P81      | - L                   | General-purpose output-only port                 |

| 70      | PWM1M2   |                       | Stepping motor controller ch.2 output pin        |

| 79      | P82      | L                     | General-purpose output-only port                 |

| 19      | PWM2P2   |                       | Stepping motor controller ch.2 output pin        |

| 80      | P83      | L                     | General-purpose output-only port                 |

| 00      | PWM2M2   |                       | Stepping motor controller ch.2 output pin        |

| 81      | P84      | L                     | General-purpose output-only port                 |

| 01      | PWM1P3   |                       | Stepping motor controller ch.3 output pin        |

| 82      | P85      | L                     | General-purpose output-only port                 |

| 02      | PWM1M3   |                       | Stepping motor controller ch.3 output pin        |

| 83      | P86      |                       | General-purpose output-only port                 |

| 03      | PWM2P3   |                       | Stepping motor controller ch.3 output pin        |

| 84      | P87      | 1                     | General-purpose output-only port                 |

| 04      | PWM2M3   | - L                   | Stepping motor controller ch.3 output pin        |

| 00      | P90      | Г                     | General-purpose I/O port                         |

| 22      | SEG22    | F                     | LCD controller/driver segment output pin         |

| 00      | P91      | Г                     | General-purpose I/O port                         |

| 23      | SEG23    | F                     | LCD controller/driver segment output pin         |

| 01      | P94      | <u> </u>              | General-purpose I/O port                         |

| 31      | V0       | G                     | LCD controller/driver reference power supply pin |

| 20      | P95      | 6                     | General-purpose I/O port                         |

| 32      | V1       | G                     | LCD controller/driver reference power supply pin |

| Pin no.   | Pin name | I/O circuit<br>type*1 | Function                                           |

|-----------|----------|-----------------------|----------------------------------------------------|

| 33 -      | P96      | G                     | General-purpose I/O port                           |

|           | V2       | G                     | LCD controller/driver reference power supply pin   |

| 34        | V3       | _                     | LCD controller/driver reference power supply pin   |

|           | PC0      |                       | General-purpose I/O port                           |

| 48        | SIN0     | J                     | UART ch.0 serial data input pin                    |

|           | INT4     |                       | INT4 external interrupt input pin                  |

|           | PC1      |                       | General-purpose I/O port                           |

| 40        | SOT0     | I                     | UART ch.0 serial data output pin                   |

| 49        | 49 INT5  |                       | INT5 external interrupt input pin                  |

|           | IN3      |                       | Input capture ch.3 trigger input pin               |

|           | PC2      |                       | General-purpose I/O port                           |

| 50        | SCK0     | I                     | UART ch.0 serial clock I/O pin                     |

| 50        | INT6     | I                     | INT6 external interrupt input pin                  |

|           | IN2      |                       | Input capture ch.2 trigger input pin               |

|           | PC3      |                       | General-purpose I/O port                           |

| 51        | SIN1     | J                     | UART ch.1 serial data input pin                    |

|           | INT7     |                       | INT7 external interrupt input pin                  |

| 52 -      | PC4      | I                     | General-purpose I/O port                           |

| 52        | SOT1     | I                     | UART ch.1 serial data output pin                   |

|           | PC5      |                       | General-purpose I/O port                           |

| 53        | SCK1     | I                     | UART ch.1 serial clock I/O pin                     |

|           | TRG      |                       | 16-bit PPG ch.0 to ch.5 external trigger input pin |

|           | PC6      |                       | General-purpose I/O port                           |

| 54        | PPG0     | I                     | 16-bit PPG ch.0 output pin                         |

| 54        | TOT1     | I                     | 16-bit reload timer ch.1 TOT output pin            |

|           | IN7      |                       | Input capture ch.7 trigger input pin               |

|           | PC7      |                       | General-purpose I/O port                           |

| <b>FF</b> | PPG1     | Ι                     | 16-bit PPG ch.1 output pin                         |

| 55        | 55 TIN1  |                       | 16-bit reload timer ch.1 TIN input pin             |

|           | IN6      |                       | Input capture ch.6 trigger input pin               |

| 04        | PD0      |                       | General-purpose I/O port                           |

| 24        | SIN2     | J                     | UART ch.2 serial data input pin                    |

| 0F        | PD1      | 1                     | General-purpose I/O port                           |

| 25 -      | SOT2     | I                     | UART ch.2 serial data output pin                   |

(Continued)

| Pin no.     | Pin name | I/O circuit<br>type*1 | Function                                                                                  |

|-------------|----------|-----------------------|-------------------------------------------------------------------------------------------|

| 06          | PD2      |                       | General-purpose I/O port                                                                  |

| 26 -        | SCK2     |                       | UART ch.2 serial clock I/O pin                                                            |

| 27 -        | PD3      | - J                   | General-purpose I/O port                                                                  |

| 21          | SIN3     | J                     | UART ch.3 serial data input pin                                                           |

| 28          | PD4      |                       | General-purpose I/O port                                                                  |

| 20          | SOT3     |                       | UART ch.3 serial data output pin                                                          |

| 29          | PD5      | I                     | General-purpose I/O port                                                                  |

| 29          | SCK3     |                       | UART ch.3 serial clock I/O pin                                                            |

| 30 -        | PD6      |                       | General-purpose I/O port                                                                  |

|             | TOT2     |                       | 16-bit reload timer ch.2 TOT output pin                                                   |

| 56          | PE0      |                       | General-purpose I/O port                                                                  |

| 50          | ТОТ3     |                       | 16-bit reload timer ch.3 TOT output pin                                                   |

| 57          | PE1      |                       | General-purpose I/O port                                                                  |

| 57          | TIN3     |                       | 16-bit reload timer ch.3 TIN input pin                                                    |

| 64          | PE2      |                       | General-purpose I/O port                                                                  |

| 04          | SGO1     |                       | Sound generator ch.1 SGO output pin                                                       |

| 62          | RSTO     | N                     | Internal reset signal output pin                                                          |

| 65, 75, 85  | DVCC     |                       | Power supply input pins dedicated for high current output buffer                          |

| 66, 76, 86  | DVSS     |                       | Power supply GND pins dedicated for high current output buffer                            |

| 35          | AVCC     |                       | A/D converter dedicated power supply input pin                                            |

| 38          | AVSS     |                       | A/D converter dedicated power supply GND pin                                              |

| 36          | AVRH     |                       | A/D converter Vref+ input pin. Vref- is fixed to AVSS.                                    |

| 89          | MD0      | D                     | Mode setting input pin. Connect to VCC pin.                                               |

| 88          | MD1      | D                     | Mode setting input pin. Connect to VCC pin.                                               |

| 87          | MD2      | D/E*2                 | Mode setting input pin. Connect to VSS pin.                                               |

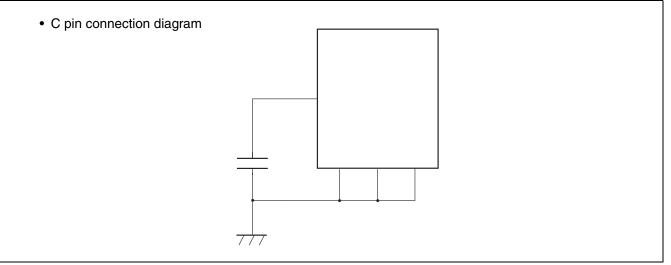

| 17          | С        | _                     | External capacitor pin. Connect a 0.1 $\mu$ F capacitor between this pin and the VSS pin. |

| 15, 105     | VCC      |                       | Power supply input pins                                                                   |

| 16, 47, 106 | VSS      | _                     | GND power supply pins                                                                     |

\*1 : For I/O circuit type, refer to " ■ I/O CIRCUIT TYPES".

$^{\ast}2$  : The I/O circuit type is D for Flash memory products and E for evaluation products.

### • Handling the power supply for high-current output buffer pins (DVcc, DVss)

### • Flash memory products and MASK ROM products (MB90F922NC/F922NCS/922NCS/F923NC/ F923NCS/F924NC/F924NCS)

In the Flash memory products and MASK ROM products, the power supply for the high-current output buffer pins (DVcc, DVss) is isolated from the digital power supply (Vcc).

Therefore, DVcc can therefore be set to a higher voltage than Vcc. If the power supply for the high-current output buffer pins (DVcc, DVss) is supplied before the digital power supply (Vcc), however, care needs to be taken because it is possible that the port 7 or port 8 stepping motor outputs may momentarily output an "H" or "L" level. In order to prevent this, connect the digital power supply (Vcc) prior to connecting the power supply for the high-current output buffer pins. Even when the high-current output buffer pins are used as general-purpose ports, power should be supplied to the power supply pins for the high-current output buffer pins (DVcc, DVss).

### • Evaluation product (MB90V920-101/MB90V920-102)

In the evaluation products, the power supply for the high-current output buffer pins (DV<sub>cc</sub>, DV<sub>ss</sub>) is not isolated from the digital power supply (V<sub>cc</sub>). Therefore, DV<sub>cc</sub> must therefore be set to a lower voltage than Vcc. The power supply for the high-current output buffer pins (DV<sub>cc</sub>, DV<sub>ss</sub>) must always be applied after the digital power supply (V<sub>cc</sub>) has been connected, and disconnected before the digital power supply (V<sub>cc</sub>) is disconnected (the power supply for the high-current output buffer pins may also be connected and disconnected simultaneously with the digital power supply).

Even when the high-current output buffer pins are used as general-purpose ports, power should be supplied to the power supply pins for the high-current output buffer pins (DVcc, DVss).

### Pull-up/pull-down resistors

MB90920 series does not support internal pull-up/pull-down resistors. Use external components as necessary.

### Precautions when not using a sub clock signal

If the X0A and X1A pins are not connected to an oscillator, apply a pull-down resistance to the X0A pin and leave the X1A pin open.

### Notes on operating when the external clock is stopped

The MB90920 series is not guaranteed to operate correctly using the internal oscillator circuit when there is no external oscillator or the external clock input is stopped.

### • Flash memory security function

A security bit is located within the Flash memory region. The security function is activated by writing the protection code  $01_{H}$  to the security bit.

Do not write the value  $01_{\text{H}}$  to this address if you are not using the security function.

Please refer to following table for the address of the security bit.

|                           | Flash memory size             | Address for security bit |

|---------------------------|-------------------------------|--------------------------|

| MB90F922NC<br>MB90F922NCS | Built-in 2 Mbits Flash Memory | FC0001н                  |

| MB90F923NCS               | Built-in 3 Mbits Flash Memory | <b>F80001</b> н          |

| MB90F924NCS               | Built-in 4 Mbits Flash Memory | <b>F80001</b> н          |

#### • Serial communication

In serial communication, reception of wrong data may occur due to noise or other causes. Therefore, design a printed circuit board to prevent noise from occurring. Taking account of the reception of wrong data, detect errors by measures such as adding a checksum to the end of data. If an error is detected, retransmit the data.

#### • Characteristic difference between flash device and MASK ROM device

In the flash device and the MASK ROM device, the electrical characteristic including current consumption, ESD, latch-up, the noise characteristic, and oscillation characteristic, etc. is different according to the difference between the chip layout and the memory structure.

Reconfirm the electrical characteristic when the product is replaced by another product of the same series.

| Address                  | Register name                             | Symbol         | Read/write            | Resource name       | Initial value         |  |

|--------------------------|-------------------------------------------|----------------|-----------------------|---------------------|-----------------------|--|

| 000024н                  |                                           |                | R/W                   |                     | XXXXXXXXB             |  |

| 000025н                  | Compare clear register                    | CPCLR          | R/W                   |                     | XXXXXXXXB             |  |

| 000026н                  | Timor doto registor                       | TCDT           | R/W                   | 16-bit              | 0000000в              |  |

| 000027н                  | Timer data register                       | ICDI           | R/W                   | free-run timer      | 0000000в              |  |

| 000028н                  | Lower timer control status register       | TCCSL          | R/W                   |                     | 0000000в              |  |

| 000029н                  | Higher timer control status register      | TCCSH          | R/W                   |                     | 01-00000в             |  |

| 00002Ан                  | Lower PPG0 control status register        | PCNTL0         | R/W                   | 16-bit PPG0         | 0000000в              |  |

| 00002Вн                  | Higher PPG0 control status register       | PCNTH0         | R/W                   |                     | 0000001в              |  |

| 00002Сн                  | Lower PPG1 control status register        | PCNTL1         | R/W                   | 16-bit PPG1         | 0000000в              |  |

| 00002Dн                  | Higher PPG1 control status register       | PCNTH1         | R/W                   |                     | 0000001в              |  |

| 00002Eн                  | Lower PPG2 control status register        | PCNTL2         | R/W                   | 16-bit PPG2         | 0000000в              |  |

| 00002Fн                  | Higher PPG2 control status register       | PCNTH2         | R/W                   |                     | 0000001в              |  |

| 000030н                  | External interrupt enable                 | ENIR           | R/W                   |                     | 0000000в              |  |

| 000031н                  | External interrupt request                | EIRR           | R/W                   | External interrupt  | 0000000в              |  |

| 000032н                  | Lower external interrupt level            | ELVRL          | R/W                   |                     | 0000000в              |  |

| 000033н                  | Higher external interrupt level           | ELVRH          | R/W                   |                     | 0000000в              |  |

| 000034н                  | Serial mode register 0                    | SMR0           | R/W, W                |                     | 0000000в              |  |

| 000035н                  | Serial control register 0                 | SCR0           | R/W, W                |                     | 0000000в              |  |

| 000036н                  | Reception/transmission data register 1    | RDR0/<br>TDR0  | R/W                   |                     | 0000000в              |  |

| 000037н                  | Serial status register 0                  | SSR0           | R/W, R                | UART                | 00001000в             |  |

| 000038н                  | Extended communication control register 0 | ECCR0          | R/W, R                | (LIN/SCI) 0         | 000000XX <sub>B</sub> |  |

| 000039н                  | Extended status control register 0        | ESCR0          | R/W                   |                     | 00000100в             |  |

| 00003Ан                  | Baud rate generator register 00           | BGR00          | R/W                   |                     | 0000000в              |  |

| 00003Вн                  | Baud rate generator register 01           | BGR01          | R/W, R                |                     | 0000000в              |  |

| 00003Cн<br>to<br>00003Fн | (Disabled)                                |                |                       |                     |                       |  |

| 000040н<br>to<br>00004Fн | Area reserved for CAN C                   | ontroller 0. R | efer to " <b>∎</b> CA | N CONTROLLERS"      |                       |  |

| 000050н                  | Lower timer control status register 0     | TMCSR0L        | R/W                   |                     | 0000000в              |  |

| 000051н                  | Higher timer control status register 0    | TMCSR0H        | R/W                   | 16-bit reload timer | XXX10000 <sub>B</sub> |  |

| 000052н                  |                                           | TMR0/          |                       | 0                   | XXXXXXXXB             |  |

| 000053н                  | Timer register 0/reload register 0        | TMRLR0         | R/W                   |                     | XXXXXXXXB             |  |

| Address | Register name                             | Symbol        | Read/write | Resource name     | Initial value         |

|---------|-------------------------------------------|---------------|------------|-------------------|-----------------------|

| 0000D4H | Lower timer control status register 2     | TMCSR2L       | R/W        | 16-bit            | 0000000в              |

| 0000D5н | Higher timer control status register 2    | TMCSR2H       | R/W        | reload timer 2    | XXX10000 <sub>B</sub> |

| 0000D6н | Lower timer control status register 3     | TMCSR3L       | R/W        | 16-bit            | 0000000в              |

| 0000D7н | Higher timer control status register 3    | TMCSR3H       | R/W        | reload timer 3    | XXX10000 <sub>B</sub> |

| 0000D8н | Lower sound control register 1            | SGCRL1        | R/W        | Cound concretor 1 | 0000000в              |

| 0000D9н | Higher sound control register 1           | SGCRH1        | R/W        | Sound generator 1 | 0XXXX100 <sub>B</sub> |

| 0000DAH | Lower PPG3 control status register        | PCNTL3        | R/W        | 16-bit PPG3       | 0000000в              |

| 0000DBH | Higher PPG3 control status register       | PCNTH3        | R/W        | 10-bit FFG3       | 0000001в              |

| 0000DCH | Lower PPG4 control status register        | PCNTL4        | R/W        | 16-bit PPG4       | 0000000в              |

| 0000DDH | Higher PPG4 control status register       | PCNTH4        | R/W        | TO-DIL PPG4       | 0000001в              |

| 0000DEH | Lower PPG5 control status register        | PCNTL5        | R/W        |                   | 0000000в              |

| 0000DFH | Higher PPG5 control status register       | PCNTH5        | R/W        | 16-bit PPG5       | 0000001в              |

| 0000E0H | Serial mode register 2                    | SMR2          | R/W, W     |                   | 0000000в              |

| 0000E1н | Serial control register 2                 | SCR2          | R/W, W     |                   | 0000000в              |

| 0000E2н | Reception/transmission data register 2    | RDR2/<br>TDR2 | R/W        |                   | 0000000в              |

| 0000E3H | Serial status register 2                  | SSR2          | R/W, R     | UART              | 00001000в             |

| 0000E4H | Extended communication control register 2 | ECCR2         | R/W, R     | (LIN/SCI) 2       | 000000XXв             |

| 0000E5н | Extended status control register 2        | ESCR2         | R/W        |                   | 00000100в             |

| 0000E6н | Baud rate generator register 20           | BGR20         | R/W        |                   | 0000000в              |

| 0000E7н | Baud rate generator register 21           | BGR21         | R/W, R     |                   | 0000000в              |

| 0000E8H | Serial mode register 3                    | SMR3          | R/W, W     |                   | 0000000в              |

| 0000E9H | Serial control register 3                 | SCR3          | R/W, W     |                   | 0000000в              |

| 0000EAH | Reception/transmission data register 3    | RDR3/<br>TDR3 | R/W        |                   | 0000000в              |

| 0000EBH | Serial status register 3                  | SSR3          | R/W, R     | UART              | 00001000в             |

| 0000ECH | Extended communication control register 3 | ECCR3         | R/W, R     | (LIN/SCI) 3       | 000000XX <sub>B</sub> |

| 0000EDH | Extended status control register 3        | ESCR3         | R/W        |                   | 00000100в             |

| 0000EEH | Baud rate generator register 30           | BGR30         | R/W        |                   | 0000000в              |

| 0000EFH | Baud rate generator register 31           | BGR31         | R/W, R     |                   | 0000000в              |

| 001FF0н | Program address detection register 0      | PADR0         | R/W        |                   | XXXXXXXXB             |

| 001FF1н | Program address detection register 1      | PADR0         | R/W        |                   | XXXXXXXXB             |

| 001FF2н | Program address detection register 2      | PADR0         | R/W        | Address match     | XXXXXXXXB             |

| 001FF3н | Program address detection register 3      | PADR1         | R/W        | detection         | XXXXXXXXB             |

| 001FF4н | Program address detection register 4      | PADR1         | R/W        |                   | XXXXXXXXB             |

| 001FF5н | Program address detection register 5      | PADR1         | R/W        |                   | XXXXXXXXB             |

| Address         | Register name                                                    | Symbol        | Read/write    | Resource name     | Initial value         |  |  |  |

|-----------------|------------------------------------------------------------------|---------------|---------------|-------------------|-----------------------|--|--|--|

| 003700н         |                                                                  |               |               |                   |                       |  |  |  |

| to              | Area reserved for CAN Controller 2. Refer to "■ CAN CONTROLLERS" |               |               |                   |                       |  |  |  |

| 0037FFн         |                                                                  |               |               |                   |                       |  |  |  |

| 003800н<br>to   | Area reserved for CAN C                                          | ontrollar 3 R | ofor to "■ CA |                   |                       |  |  |  |

| 0038FFн         | Area reserved for CAN Controller 3. Refer to "■ CAN CONTROLLERS" |               |               |                   |                       |  |  |  |

| 003900н         |                                                                  |               |               |                   |                       |  |  |  |

| to              |                                                                  | (Disabl       | ed)           |                   |                       |  |  |  |

| 00391Fн         |                                                                  | 1             | 1             |                   |                       |  |  |  |

| 003920н         | PPG0 down counter register                                       | PDCR0         | R             |                   | 11111111 <sub>В</sub> |  |  |  |

| <b>003921</b> н |                                                                  |               |               | 16-bit PPG0       | 11111111 <sub>в</sub> |  |  |  |

| 003922н         | PPG0 cycle setting register                                      | PCSR0         | W             |                   | 11111111 <sub>В</sub> |  |  |  |

| 003923н         |                                                                  | 1 00110       | vv            |                   | 11111111в             |  |  |  |

| 003924н         | PPG0 duty setting register                                       | PDUT0         | W             |                   | 0000000в              |  |  |  |

| 003925н         |                                                                  | FD010         | vv            | 16-bit PPG0       | 0000000в              |  |  |  |

| 003926н         | PPG0 output division setting register                            | PPGDIV0       | R/W, R        |                   | 11111100в             |  |  |  |

| 003927н         |                                                                  | (Disabl       | ed)           |                   |                       |  |  |  |

| 003928н         |                                                                  | PDCR1         | R             | 16-bit PPG1       | 11111111в             |  |  |  |

| 003929н         | PPG1 down counter register                                       |               |               |                   | 11111111в             |  |  |  |

| 00392Ан         |                                                                  | PCSR1         |               |                   | 11111111в             |  |  |  |

| 00392Вн         | PPG1 cycle setting register                                      |               | W             |                   | 11111111в             |  |  |  |

| 00392Сн         |                                                                  |               |               |                   | 0000000в              |  |  |  |

| 00392Dн         | PPG1 duty setting register                                       | PDUT1         | W             |                   | 0000000в              |  |  |  |

| 00392Ен         | PPG1output division setting register                             | PPGDIV1       | R/W, R        |                   | 11111100 <sub>B</sub> |  |  |  |

| <b>00392F</b> н |                                                                  | (Disabl       | ed)           |                   |                       |  |  |  |

| 003930н         |                                                                  |               |               |                   | 11111111в             |  |  |  |

| <b>003931</b> н | PPG2 down counter register                                       | PDCR2         | R             |                   | 11111111 <sub>в</sub> |  |  |  |

| 003932н         |                                                                  |               |               |                   | 11111111в             |  |  |  |

| 003933н         | PPG2 cycle setting register                                      | PCSR2         | W             | 16-bit PPG2       | 11111111в             |  |  |  |

| 003934н         |                                                                  |               |               |                   | 0000000в              |  |  |  |

| 003935н         | PPG2 duty setting register                                       | PDUT2         | W             |                   | 0000000в              |  |  |  |

| 003936н         | PPG2 output division setting register                            | PPGDIV2       | R/W, R        |                   | 11111100в             |  |  |  |

| <b>003937</b> н |                                                                  | I             |               |                   | I                     |  |  |  |

| to              |                                                                  | (Disabl       | ed)           |                   |                       |  |  |  |

| 00393Fн         |                                                                  | 1             | ,             |                   |                       |  |  |  |

| 003940н         | Input capture register 4                                         | IPCP4         | R             |                   | XXXXXXXXB             |  |  |  |

| <b>003941</b> н |                                                                  |               |               | Input capture 4/5 | XXXXXXXXB             |  |  |  |

| 003942н         | Input capture register 5                                         | IPCP5         | R             |                   | XXXXXXXXB             |  |  |  |

| 003943н         | Input capture register o                                         |               |               |                   | XXXXXXXXB             |  |  |  |

|                 |                                                                  |               |               |                   | (Continued)           |  |  |  |

| Address                  | Register name              | Symbol     | Read/write | Resource name                  | Initial value |  |  |

|--------------------------|----------------------------|------------|------------|--------------------------------|---------------|--|--|

| 003970н<br>to<br>003973н |                            | (Disab     | led)       |                                |               |  |  |

| 003974н                  | Frequency data register 1  | SGFR1      | R/W        |                                | XXXXXXXXB     |  |  |

| 003975н                  | Amplitude data register 1  | SGAR1      | R/W        | Sound concretor 1              | 0000000в      |  |  |

| 003976н                  | Decrement grade register 1 | SGDR1      | R/W        | Sound generator 1              | XXXXXXXXB     |  |  |

| 003977н                  | Tone count register 1      | SGTR1      | R/W        |                                | XXXXXXXXB     |  |  |

| 003978н<br>to<br>00397Fн |                            | (Disabled) |            |                                |               |  |  |

| 003980н                  | DWM1 compare register 0    | PWC10      | R/W        |                                | XXXXXXXXB     |  |  |

| <b>003981</b> н          | PWM1 compare register 0    | FWCIU      | U/ M       |                                | XXXXXXXXB     |  |  |

| 003982н                  | BWW compare register 0     | PWC20      | R/W        | Stepping motor                 | XXXXXXXXB     |  |  |

| 003983н                  | PWM2 compare register 0    | F WC20     | U/ M       | controller 0                   | XXXXXXXXB     |  |  |

| 003984н                  | PWM1 select register 0     | PWS10      | R/W        |                                | 0000000в      |  |  |

| 003985н                  | PWM2 select register 0     | PWS20      | R/W        |                                | Х000000в      |  |  |

| 003986н,<br>003987н      |                            | (Disab     | led)       |                                |               |  |  |

| 003988н                  | DWM1 compare register 1    | PWC11      | R/W        |                                | XXXXXXXXB     |  |  |

| 003989н                  | PWM1 compare register 1    | PWCII      | H/ VV      |                                | XXXXXXXXB     |  |  |

| 00398Ан                  | DWM2 compare register 1    | PWC21      | R/W        | Stepping motor<br>controller 1 | XXXXXXXXB     |  |  |

| 00398Вн                  | PWM2 compare register 1    |            | H/ VV      |                                | XXXXXXXXB     |  |  |

| 00398Сн                  | PWM1 select register 1     | PWS11      | R/W        |                                | 0000000в      |  |  |

| 00398Dн                  | PWM2 select register 1     | PWS21      | R/W        |                                | Х000000в      |  |  |

| 00398Eн,<br>00398Fн      |                            | (Disab     | led)       |                                |               |  |  |

| 003990н                  |                            |            |            |                                | XXXXXXXXB     |  |  |

| <b>003991</b> н          | PWM1 compare register 2    | PWC12      | R/W        |                                | XXXXXXXXB     |  |  |

| 003992н                  | DW/M2 compare register 2   |            |            | Stepping motor                 | XXXXXXXXB     |  |  |

| 003993н                  | PWM2 compare register 2    | PWC22      | R/W        | controller 2                   | XXXXXXXXB     |  |  |

| 003994н                  | PWM1 select register 2     | PWS12      | R/W        |                                | 0000000в      |  |  |

| 003995н                  | PWM2 select register 2     |            | Х000000в   |                                |               |  |  |

| 003996н,<br>003997н      |                            | (Disab     | led)       |                                | (Continued    |  |  |

### CAN CONTROLLERS

The CAN controller has the following features :

- Conforms to CAN Specification Version 2.0 Part A and B

- Supports transmission/reception in standard frame and extended frame formats

- Supports transmission of data frames by receiving remote frames

- 16 transmission/reception message buffers

- 29-bit ID and 8-byte data

- Multi-level message buffer configuration

- Provides full-bit comparison, full-bit mask, acceptance register 0/acceptance register 1 for each message buffer as ID acceptance mask

- 2 acceptance mask registers in either standard frame format or extended frame formats

- Bit rate programmable from 10 kbps to 2 Mbps (when input clock is at 16 MHz)

|         | Add                 | ress                |                 | Register                | Abbreviation | Access     | Initial Value         |  |

|---------|---------------------|---------------------|-----------------|-------------------------|--------------|------------|-----------------------|--|

| CAN0    | CAN1                | CAN2                | CAN3            | negister                | Abbreviation | ALLESS     |                       |  |

| 003С00н | 003D00н             | <b>003E00</b> н     | 003F00н         | Control status register | CSR          | R/W, R     | 00000в                |  |

| 003C01н | 003D01н             | <b>003E01</b> н     | <b>003F01</b> н | Control Status register | 0311         | 11/ VV, 11 | 00-1в                 |  |

| 003C02н | 003D02 <sub>H</sub> | 003E02н             | 003F02н         | Last event indicator    | LEIR         | R/W        | В                     |  |

| 003C03н | 003D03н             | 003E03н             | 003F03н         | register                |              | 11/ VV     | 000-0000в             |  |

| 003C04н | 003D04 <sub>H</sub> | 003E04 <sub>H</sub> | 003F04н         | RX/TX error counter     | RTEC         | R          | 0000000в              |  |

| 003C05н | 003D05н             | 003E05н             | 003F05н         |                         | meo          | 11         | 0000000в              |  |

| 003C06н | 003D06н             | 003E06н             | 003F06н         | Bit timing register     | BTR          | R/W        | -1111111в             |  |

| 003C07н | 003D07н             | <b>003E07</b> н     | <b>003F07</b> н |                         | BIN          | I 1/ V V   | 11111111 <sub>В</sub> |  |

#### List of Control Registers(1)

## ■ ELECTRICAL CHARACTERISTICS

### 1. Absolute Maximum Ratings

| Devementer                  | Cumhal                        | Rating    |           | Unit | Remarks                          |  |

|-----------------------------|-------------------------------|-----------|-----------|------|----------------------------------|--|

| Parameter                   | Symbol                        | Min       | Max       | Unit | nemarks                          |  |

|                             | Vcc                           | Vss - 0.3 | Vss + 6.0 | V    |                                  |  |

| Dowor oupply voltogo*1      | AVcc                          | Vss - 0.3 | Vss + 6.0 | V    | $AVcc = Vcc^{*2}$                |  |

| Power supply voltage*1      | AVRH                          | Vss - 0.3 | Vss + 6.0 | V    | AVcc ≥ AVRH*2                    |  |

|                             | DVcc                          | Vss - 0.3 | Vss + 6.0 | V    | $DVcc = Vcc^{*2}$                |  |

| Input voltage*1             | Vı                            | Vss - 0.3 | Vcc + 0.3 | V    | *3                               |  |

| Output voltage*1            | Vo                            | Vss - 0.3 | Vcc + 0.3 | V    |                                  |  |

| Maximum clamp current       | CLAMP                         | - 4       | + 4       | mA   | *7                               |  |

| Total maximum clamp current | $\Sigma$   Iclamp             |           | 40        | mA   | *7                               |  |

| "L" level maximum           | OL1                           |           | 15        | mA   | Except P70 to P77 and P80 to P87 |  |

| output current*4            |                               | _         | 40        | mA   | P70 to P77 and P80 to P87        |  |

| "L" level average output    | OLAV1                         |           | 4         | mA   | Except P70 to P77 and P80 to P87 |  |

| current*5                   | OLAV2                         |           | 30        | mA   | P70 to P77 and P80 to P87        |  |

| "L" level maximum           | $\Sigma$ IOL1                 | _         | 100       | mA   | Except P70 to P77 and P80 to P87 |  |

| total output current        | $\Sigma$ Iol2                 | _         | 330       | mA   | P70 to P77 and P80 to P87        |  |

| "L" level average total     | $\Sigma$ IOLAV1               |           | 50        | mA   | Except P70 to P77 and P80 to P87 |  |

| output current              | $\Sigma$ Iolav2               | _         | 250       | mA   | P70 to P77 and P80 to P87        |  |

| "H" level maximum           | Он1*4                         | _         | -15       | mA   | Except P70 to P77 and P80 to P87 |  |

| output current              | он2*4                         |           | -40       | mA   | P70 to P77 and P80 to P87        |  |

| "H" level average           | OHAV1*5                       | _         | -4        | mA   | Except P70 to P77 and P80 to P87 |  |

| output current              | OHAV2 <sup>*5</sup>           | _         | -30       | mA   | P70 to P77 and P80 to P87        |  |

| "H" level maximum           | $\Sigma$ Іон1                 |           | -100      | mA   | Except P70 to P77 and P80 to P87 |  |

| total output current        | $\Sigma$ Іон2                 | _         | -330      | mA   | P70 to P77 and P80 to P87        |  |

| "H" level average total     | $\Sigma$ IOHAV1 <sup>*6</sup> |           | -50       | mA   | Except P70 to P77 and P80 to P87 |  |

| output current              | $\Sigma$ Iohav2 <sup>*6</sup> |           | -250      | mA   | P70 to P77 and P80 to P87        |  |

| Power consumption           | PD                            |           | 625       | mW   |                                  |  |

| Operating temperature       | TA                            | - 40      | + 105     | °C   |                                  |  |

| Storage temperature         | Тѕтс                          | - 55      | + 150     | °C   |                                  |  |

\*1 : The parameter is based on  $V_{SS} = AV_{SS} = DV_{SS} = 0.0 V.$

\*2 : AVcc, AVRH must not exceed Vcc, and AVRH must not exceed AVcc. When using an evaluation product, DVcc must not exceed Vcc (however, DVcc can be set to a higher voltage than Vcc when using a Flash memory product).

\*3 : If the input current or the maximum input current is limited using external components, ICLAMP is the applicable rating instead of VI.

\*4 : Maximum output current is defined as the peak value of current through any one of the corresponding pins.

### 2. Recommended Operating Conditions

$(V_{SS} = DV_{SS} = AV_{SS} = 0.0 V)$

| Darameter                | Parameter Symbol Value U |      | Unit  | Remarks |                                                                                                                                                                                                  |

|--------------------------|--------------------------|------|-------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Farameter                | Symbol                   | Min  | Max   | Onit    | nemarks                                                                                                                                                                                          |

| Power supply             | Vcc                      | 4.0  | 5.5   | V       | The low voltage detection reset operates when the power supply voltage reaches 4.2 V $\pm$ 0.2 V.                                                                                                |

| voltage                  | AVcc<br>DVcc             | 4.4  | 5.5   | v       | Maintain stop operation status The low voltage detection reset operates when the power supply voltage reaches 4.2 V $\pm$ 0.2 V.                                                                 |

| Smoothing<br>capacitor*  | Cs                       | 0.1  | 1.0   | μF      | Use a ceramic capacitor or other capacitor of equivalent frequency characteristics. Use a capacitor with a capacitance greater than this capacitor as the bypass capacitor for the $V_{CC}$ pin. |

| Operating<br>temperature | TA                       | - 40 | + 105 | °C      |                                                                                                                                                                                                  |

\*: Refer to the following diagram for details on the connection of the smoothing capacitor Cs.

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their representatives beforehand.

### 3. DC Characteristics

| Devenueter                 | • • • • | Pin<br>name | Conditions                                                                                        | Value   |     |         |      | Demontos                                                      |

|----------------------------|---------|-------------|---------------------------------------------------------------------------------------------------|---------|-----|---------|------|---------------------------------------------------------------|

| Parameter                  | Symbol  |             | Conditions                                                                                        | Min     | Тур | Мах     | Unit | Remarks                                                       |

| "H" level<br>input voltage | VIHA    |             | _                                                                                                 | 0.8 Vcc |     |         | V    | Pin inputs if<br>Automotive input<br>levels are selected      |

|                            | VIHS    |             | _                                                                                                 | 0.8 Vcc |     |         | V    | Pin inputs if CMOS<br>hysteresis input<br>levels are selected |

|                            | VIHC    |             | _                                                                                                 | 0.7 Vcc |     |         | V    | RST input pin<br>(CMOS hysteresis)                            |

| "L" level<br>input voltage | VILA    |             | _                                                                                                 |         |     | 0.5 Vcc | V    | Pin inputs if<br>Automotive input<br>levels are selected      |

|                            | VILS    | _           | _                                                                                                 |         | _   | 0.2 Vcc | V    | Pin inputs if CMOS<br>hysteresis input<br>levels are selected |

|                            | VILR    |             |                                                                                                   |         |     | 0.3 Vcc | V    | RST input pin<br>(CMOS hysteresis)                            |

| Power supply<br>current*   | lcc     |             | Maximum operating<br>frequency FcP = 32 MHz,<br>normal operation                                  |         | 35  | 45      | mA   |                                                               |

|                            |         |             | Maximum operating<br>frequency FcP = 32 MHz,<br>writing Flash memory                              |         | 55  | 65      | mA   |                                                               |

|                            | Iccs    |             | Operating frequency<br>$F_{CP} = 32 \text{ MHz},$<br>sleep mode                                   |         | 13  | 20      | mA   |                                                               |

|                            | Істѕ    |             | Operating frequency<br>$F_{CP} = 2 MHz$ ,<br>time-base timer mode                                 |         | 0.6 | 1.0     | mA   |                                                               |

|                            | Ictspll | Vcc         | Operating frequency<br>F <sub>CP</sub> = 32 MHz,<br>PLL timer mode,<br>External frequency = 4 MHz |         | 2.5 | 4       | mA   |                                                               |

|                            | Iccl    |             | Operating frequency<br>$F_{CP} = 8 \text{ kHz}, T_A = +25 \text{ °C},$<br>sub clock operation     |         | 120 | 270     | μA   |                                                               |

|                            | Iccls   |             | Operating frequency<br>$F_{CP} = 8 \text{ kHz}, T_A = +25 \text{ °C},$<br>sub sleep operation     | _       | 100 | 200     | μA   |                                                               |

|                            | Ісст    |             | Operating frequency<br>$F_{CP} = 8 \text{ kHz}, T_A = +25 \text{ °C},$<br>watch mode              |         | 90  | 180     | μA   |                                                               |

|                            | Іссн    | 1           | $T_A = + 25 \ ^{\circ}C$ , stop mode                                                              | —       | 80  | 170     | μA   |                                                               |

(Vcc = 5.0 V  $\pm 10\%$ , Vss = DVss = AVss = 0.0 V, T<sub>A</sub> = -40 °C to +105 °C)

### 4. AC Characteristics

### (1) Clock timing

| Deveneter                             | Symbol        | Pinname  | Condi-<br>tions | Value |        |      |      | ·                                                         |

|---------------------------------------|---------------|----------|-----------------|-------|--------|------|------|-----------------------------------------------------------|

| Parameter                             |               |          |                 | Min   | Тур    | Max  | Unit | Remarks                                                   |

|                                       |               | X0, X1   |                 | 3     | _      | 16   | MHz  | 1/2 (PLL stopped)<br>When using the<br>oscillator circuit |

|                                       |               |          |                 | 3     | —      | 32   | MHz  | 1/2 (PLL stopped)<br>When using an external<br>clock      |

|                                       | Fc            |          |                 | 4     | —      | 32   | MHz  | PLL multiplied by 1                                       |

| Clock frequency                       |               |          |                 | 3     |        | 16   | MHz  | PLL multiplied by 2                                       |

|                                       |               |          |                 | 3     |        | 10.7 | MHz  | PLL multiplied by 3                                       |

|                                       |               |          |                 | 3     |        | 8    | MHz  | PLL multiplied by 4                                       |

|                                       |               |          |                 | 3     |        | 5.33 | MHz  | PLL multiplied by 6                                       |

|                                       |               |          |                 | 3     |        | 4    | MHz  | PLL multiplied by 8                                       |

|                                       | FLC           | X0A, X1A |                 | _     | 32.768 |      | kHz  |                                                           |

|                                       | <b>t</b> cy∟  | X0, X1   |                 | 62.5  |        | 333  | ns   | When using an oscillator                                  |

| Clock cycle time                      |               |          |                 | 31.25 |        | 333  | ns   | External clock input                                      |

|                                       | <b>t</b> LCYL | X0A, X1A |                 |       | 30.5   |      | μs   |                                                           |

| Input clock pulse<br>width            | Pwн, Pwl      | X0       |                 | 5     |        | _    | ns   | Use duty ratio of $50\%\pm3\%$ as a guideline             |

| Width                                 | Pwlh, Pwll    | X0A      |                 |       | 15.2   |      | μs   |                                                           |

| Input clock<br>rise and fall time     | tcr, tcf      | X0       |                 | _     |        | 5    | ns   | When using an external clock signal                       |

| Internal operating<br>clock frequency | Fcp           | _        |                 | 1.5   |        | 32   | MHz  | Using main clock<br>(PLL clock)                           |

|                                       | FLCP          | —        |                 | _     | 8.192  |      | kHz  | Using sub clock                                           |

| Internal operating clock cycle time   | tcp           | _        |                 | 31.25 | —      | 666  | ns   | Using main clock<br>(PLL clock)                           |

|                                       | <b>t</b> LCP  |          |                 |       | 122.1  |      | μs   | Using sub clock                                           |

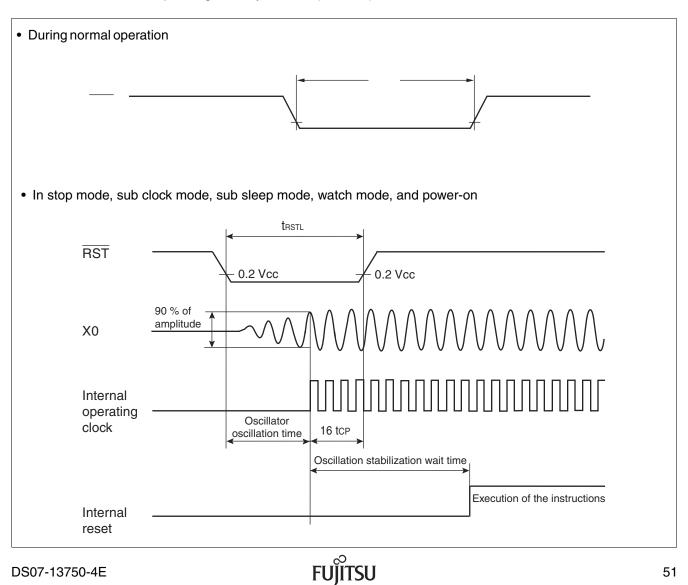

### (2) Reset input

| $(V_{CC} = 5.0 \text{ V} \pm 10\%, \text{ Vss} = \text{AVss} = 0.0 \text{ V}, \text{ T}_{\text{A}} = -40 ^{\circ}\text{C} \text{ to} +10$ |        |          |                                       |     |      |                                                                       |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------|--------|----------|---------------------------------------|-----|------|-----------------------------------------------------------------------|--|--|

| Parameter                                                                                                                                 | Symbol | Pin name | Value                                 |     |      | Remarks                                                               |  |  |

| Falameter                                                                                                                                 |        |          | Min                                   | Max | Unit | nemarks                                                               |  |  |

| Reset input time                                                                                                                          | trs⊤∟  | RST      | 500                                   |     | ns   | During normal operation                                               |  |  |

|                                                                                                                                           |        |          | Oscillator oscillation time* + 16 tcp | _   | ms   | In stop mode,<br>sub clock mode,<br>sub sleep mode,<br>and watch mode |  |  |

|                                                                                                                                           |        |          | 100                                   |     | μs   | In time-base timer<br>mode                                            |  |  |

\*: The oscillation time of the oscillator is the time taken to reach 90% of the amplitude. The oscillation time of a crystal oscillator is between several ms and tens of ms. The oscillation time of a ceramic oscillator is between hundreds of  $\mu$ s and several ms. The oscillation time of an external clock is 0 ms.

Note : tcp is the internal operating clock cycle time. (Unit : ns)

FU

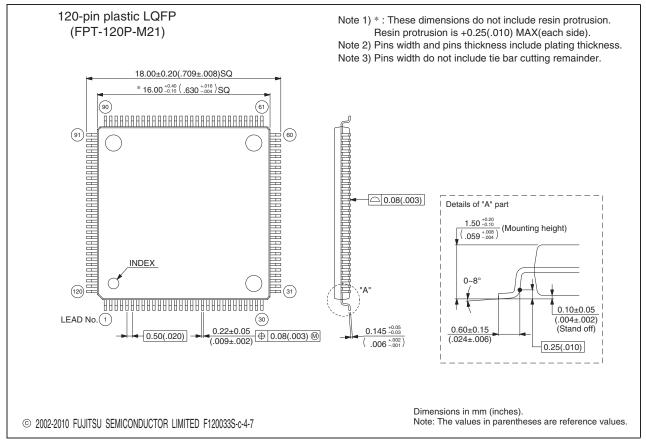

### ■ PACKAGE DIMENSION

Please check the latest package dimension at the following URL. http://edevice.fujitsu.com/package/en-search/

# FUJITSU SEMICONDUCTOR LIMITED

Nomura Fudosan Shin-yokohama Bldg. 10-23, Shin-yokohama 2-Chome, Kohoku-ku Yokohama Kanagawa 222-0033, Japan Tel: +81-45-415-5858 http://jp.fujitsu.com/fsl/en/

For further information please contact:

#### North and South America

FUJITSU SEMICONDUCTOR AMERICA, INC. 1250 E. Arques Avenue, M/S 333 Sunnyvale, CA 94085-5401, U.S.A. Tel: +1-408-737-5600 Fax: +1-408-737-5999 http://us.fujitsu.com/micro/

#### Europe

FUJITSU SEMICONDUCTOR EUROPE GmbH Pittlerstrasse 47, 63225 Langen, Germany Tel: +49-6103-690-0 Fax: +49-6103-690-122 http://emea.fujitsu.com/semiconductor/

#### Korea

FUJITSU SEMICONDUCTOR KOREA LTD. 206 Kosmo Tower Building, 1002 Daechi-Dong, Gangnam-Gu, Seoul 135-280, Republic of Korea Tel: +82-2-3484-7100 Fax: +82-2-3484-7111 http://kr.fujitsu.com/fmk/

#### Asia Pacific

FUJITSU SEMICONDUCTOR ASIA PTE. LTD. 151 Lorong Chuan, #05-08 New Tech Park 556741 Singapore Tel : +65-6281-0770 Fax : +65-6281-0220 http://www.fujitsu.com/sg/services/micro/semiconductor/

FUJITSU SEMICONDUCTOR SHANGHAI CO., LTD. Rm. 3102, Bund Center, No.222 Yan An Road (E), Shanghai 200002, China Tel : +86-21-6146-3688 Fax : +86-21-6335-1605 http://cn.fujitsu.com/fss/

FUJITSU SEMICONDUCTOR PACIFIC ASIA LTD. 10/F., World Commerce Centre, 11 Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel : +852-2377-0226 Fax : +852-2376-3269 http://cn.fujitsu.com/fsp/

Specifications are subject to change without notice. For further information please contact each office.

#### All Rights Reserved.

The contents of this document are subject to change without notice.

Customers are advised to consult with sales representatives before ordering.

The information, such as descriptions of function and application circuit examples, in this document are presented solely for the purpose of reference to show examples of operations and uses of FUJITSU SEMICONDUCTOR device; FUJITSU SEMICONDUCTOR does not warrant proper operation of the device with respect to use based on such information. When you develop equipment incorporating the device based on such information, you must assume any responsibility arising out of such use of the information.

FUJITSU SEMICONDUCTOR assumes no liability for any damages whatsoever arising out of the use of the information.

Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of FUJITSU SEMICONDUCTOR or any third party or does FUJITSU SEMICONDUCTOR warrant non-infringement of any third-party's intellectual property right or other right by using such information. FUJITSU SEMICONDUCTOR assumes no liability for any infringement of the intellectual property rights or other rights or other rights of third parties which would result from the use of information contained herein.

The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that FUJITSU SEMICONDUCTOR will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

Exportation/release of any products described in this document may require necessary procedures in accordance with the regulations of the Foreign Exchange and Foreign Trade Control Law of Japan and/or US export control laws.

The company names and brand names herein are the trademarks or registered trademarks of their respective owners.