Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | F <sup>2</sup> MC-16LX                                                            |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 32MHz                                                                             |

| Connectivity               | CANbus, LINbus, UART/USART                                                        |

| Peripherals                | LCD, LVD, POR, PWM, WDT                                                           |

| Number of I/O              | 93                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | Mask ROM                                                                          |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 10K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                         |

| Data Converters            | A/D 8x8/10b                                                                       |

| Oscillator Type            | External                                                                          |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 120-LQFP                                                                          |

| Supplier Device Package    | 120-LQFP (16x16)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90922ncspmc-gs-192e1 |

# 16-bit Microcontroller

**CMOS**

# F<sup>2</sup>MC-16LX MB90920 Series

# MB90F922NC/F922NCS/922NCS/F923NC/F923NCS/MB90F924NC/F924NCS/V920-101/V920-102

### **■ DESCRIPTION**

The MB90920 series is a family of general-purpose FUJITSU SEMICONDUCTOR 16-bit microcontrollers designed for applications such as vehicle instrument panel control.

The instruction set retains the AT architecture from the F<sup>2</sup>MC-8L and F<sup>2</sup>MC-16LX families, with further refinements including high-level language instructions, extended addressing modes, improved multiplication and division operations (signed), and bit processing. In addition, long word processing is made possible by the inclusion of a built-in 32-bit accumulator.

Note: F<sup>2</sup>MC is the abbreviation of FUJITSU Flexible Microcontroller.

## **■ FEATURES**

Clock

Built-in PLL clock frequency multiplication circuit.

Selection of machine clocks (PLL clocks) is allowed among frequency division by two on oscillation clock, and multiplication of 1 to 8 times of oscillation clock (for 4 MHz oscillation clock, 4 MHz to 32 MHz).

Operation by sub clock (up to 50 kHz: 100 kHz oscillation clock divided by two) is allowed.

• 16-bit input capture (8 channels)

Detects rising, falling, or both edges.

16-bit capture register  $\times$  8

The value of a 16-bit free-run timer counter is latched upon detection of an edge input to pin and an interrupt request is generated.

(Continued)

For the information for microcontroller supports, see the following web site.

This web site includes the "Customer Design Review Supplement" which provides the latest cautions on system development and the minimal requirements to be checked to prevent problems before the system development.

http://edevice.fujitsu.com/micom/en-support/

### (Continued)

• 16-bit reload timer (4 channels)

16-bit reload timer operation (select toggle output or one-shot output)

Selectable event count function

• Real time watch timer (main clock)

Operates directly from oscillator clock.

Interrupt can be generated by second/minute/hour/date counter overflow.

• PPG timer (6 channels)

Output pins (3 channels), external trigger input pin (1 channel)

Operation clock frequencies: fcp, fcp/22, fcp/24, fcp/26

Delay interrupt

Generates interrupt for task switching.

Interrupts to CPU can be generated/cleared by software setting.

• External interrupts (8 channels)

8-channel independent operation

Interrupt source setting available: "L" to "H" edge/ "H" to "L" edge/ "L" level/ "H" level.

• 8/10-bit A/D converter (8 channels)

Conversion time :  $3 \mu s$  (at  $f_{CP} = 32 \text{ MHz}$ )

External trigger activation available (P50/INT0/ADTG)

Internal timer activation available (16-bit reload timer 1)

• UART(LIN/SCI) (4 channels)

Equipped with full duplex double buffer

Clock-asynchronous or clock-synchronous serial transfer is available

• CAN interface (4 channels: CAN0 and CAN2, and CAN1 and CAN3 share transmission and reception pins, and interrupt control registers).

Conforms to CAN specifications version 2.0 Part A and B.

Automatic resend in case of error.

Automatic transfer in response to remote frame.

16 prioritized message buffers for data and ID

Multiple message support

Flexible configuration for receive filter: Full bit compare/full bit mask/two partial bit masks

Supports up to 1 Mbps

CAN wakeup function (RX connected to INT0 internally)

• LCD controller/driver (32 segment x 4 common)

Segment driver and command driver with direct LCD panel (display) drive capability

• Reset on detection of low voltage/program loop

Automatic reset when low voltage is detected

Program looping detection function

Stepping motor controller (4 channels)

High current output for each channel × 4

Synchronized 8/10-bit PWM for each channel × 2

• Sound generator (2 channels)

8-bit PWM signal mixed with tone frequency from 8-bit reload counter.

PWM frequencies: 125 kHz, 62.5 kHz, 31.2 kHz, 15.6 kHz (at fcp = 32 MHz)

Tone frequencies: PWM frequency /2/, divided by (reload frequency +1)

· Input/output ports

General-purpose input/output port (CMOS output) 93 ports

• Function for port input level selection

Automotive/CMOS-Schmitt

• Flash memory security function

Protects the contents of Flash memory (Flash memory product only)

| Pin no. | Pin name | I/O circuit<br>type*1 | Function                                 |

|---------|----------|-----------------------|------------------------------------------|

| 104     | P13      |                       | General-purpose I/O port                 |

| 104     | PPG5     | -<br>                 | 16-bit PPG ch.5 output pin               |

|         | P14      |                       | General-purpose I/O port                 |

| 109     | TIN2     | -<br>                 | 16-bit reload timer ch.2 TIN input pin   |

|         | IN1      |                       | Input capture ch.1 trigger input pin     |

| 110     | P15      |                       | General-purpose I/O port                 |

| 110     | IN0      | - I                   | Input capture ch.0 trigger input pin     |

| 111     | COM0     | Р                     | LCD controller/driver common output pin  |

| 112     | COM1     | Р                     | LCD controller/driver common output pin  |

| 113     | COM2     | Р                     | LCD controller/driver common output pin  |

| 114     | COM3     | Р                     | LCD controller/driver common output pin  |

| 445     | P22      | _                     | General-purpose I/O port                 |

| 115     | SEG00    | - F                   | LCD controller/driver segment output pin |

| 440     | P23      | _                     | General-purpose I/O port                 |

| 116     | SEG01    | F                     | LCD controller/driver segment output pin |

| 447     | P24      | _                     | General-purpose I/O port                 |

| 117     | SEG02    | F                     | LCD controller/driver segment output pin |

| 440     | P25      | _                     | General-purpose I/O port                 |

| 118     | SEG03    | F                     | LCD controller/driver segment output pin |

| 440     | P26      | _                     | General-purpose I/O port                 |

| 119     | SEG04    | F                     | LCD controller/driver segment output pin |

| 100     | P27      | _                     | General-purpose I/O port                 |

| 120     | SEG05    | F                     | LCD controller/driver segment output pin |

| _       | P30      | _                     | General-purpose I/O port                 |

| 1       | SEG06    | F                     | LCD controller/driver segment output pin |

| 0       | P31      | _                     | General-purpose I/O port                 |

| 2       | SEG07    | - F                   | LCD controller/driver segment output pin |

|         | P32      | _                     | General-purpose I/O port                 |

| 3       | SEG08    | F                     | LCD controller/driver segment output pin |

| 4       | P33      | _                     | General-purpose I/O port                 |

| 4       | SEG09    | - F                   | LCD controller/driver segment output pin |

| _       | P34      | _                     | General-purpose I/O port                 |

| 5       | SEG10    | F                     | LCD controller/driver segment output pin |

| _       | P35      | -                     | General-purpose I/O port                 |

| 6       | SEG11    | - F                   | LCD controller/driver segment output pin |

| Туре | Circuit                                                                                                                                                                               | Remarks                                                                                                                                                                                                                    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Н    | P-ch Pout  N-ch Nout  Analog input  CMOS hysteresis input Standby control signal or analog input enable signal  Automotive input Standby control signal or analog input enable signal | A/D converter input common general-purpose port  • CMOS output (IoH/IoL = ± 4 mA)  • CMOS hysteresis input (VH/VIL = 0.8 Vcc/0.2 Vcc)  • Automotive input (VH/VIL = 0.8 Vcc/0.5 Vcc)                                       |

| I    | P-ch Pout  Nout  CMOS hysteresis input  Standby control signal  Automotive input  Standby control signal                                                                              | General-purpose port  CMOS output (IoH/IoL = ± 4 mA)  CMOS hysteresis input (VIH/VIL = 0.8 Vcc/0.2 Vcc)  Automotive input (VIH/VIL = 0.8 Vcc/0.5 Vcc)                                                                      |

| J    | P-ch Nout  CMOS hysteresis input Standby control signal Automotive input Standby control signal  CMOS input (SIN) Standby control signal                                              | General-purpose port (serial input)  • CMOS output (IoH/IoL = ± 4 mA)  • CMOS hysteresis input (VIH/VIL = 0.8 Vcc/0.2 Vcc)  • CMOS input (SIN) (VIH/VIL = 0.7 Vcc/0.3 Vcc)  • Automotive input (VIH/VIL = 0.8 Vcc/0.5 Vcc) |

| Туре | Circuit                                          | Remarks                                                     |

|------|--------------------------------------------------|-------------------------------------------------------------|

| N    | Evaluation product  P-ch  N-ch  Nout  Nout  Nout | N-ch open-drain pin IoL = 4 mA                              |

| 0    | Automotive input                                 | Input-only pin Automotive input (VIH/VIL = 0.8 Vcc/0.5 Vcc) |

| P    | P-ch LCDC output                                 | LCDC output pin (COM pin)                                   |

### · Notes on operating in PLL clock mode

On this microcontroller, if in case the crystal oscillator breaks off or an external reference clock input stops while the PLL clock mode is selected, a self-oscillator circuit contained in the PLL may continue its operation at its self-running frequency. However, FUJITSU SEMICONDUCTOR will not guarantee results of operations if such failure occurs.

### Crystal oscillator circuit

Noise around the X0/X1, or X0A/X1A pins may cause this device to operate abnormally. In the interest of stable operation it is strongly recommended that printed circuit artwork places ground bypass capacitors as close as possible to the X0/X1, X0A/X1A and crystal oscillator (or ceramic oscillator) and that oscillator lines do not cross the lines of other circuits.

Please ask each crystal maker to evaluate the oscillational characteristics of the crystal and this device.

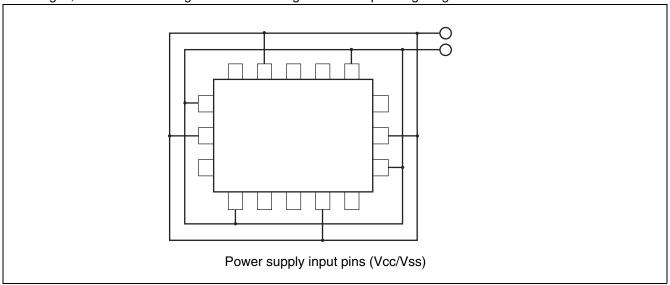

## · Power supply pins

Devices including multiple VCC or VSS pins are designed such that pins that need to be at the same potential are interconnected internally to prevent malfunctions such as latch-up. To reduce unnecessary radiation, prevent malfunctioning of the strobe signal due to the rise of ground level, and observe the standard for total output current, be sure to connect the VCC and VSS pins to the power supply and ground externally.

Always connect all of the VCC pins to the same potential and all of the VSS pins to ground as shown in the following diagram. The device will not operate correctly if multiple VCC or VSS pins are connected to different voltages, even if those voltages are within the guaranteed operating ranges.

In addition, care must be given to connecting the VCC and VSS pins of this device to the current supply source with as low impedance as possible. It is recommended that a 1.0  $\mu$ F bypass capacitor be connected between the VCC and VSS pins as close to the pins as possible.

## Sequence for connecting the A/D converter power supply and analog inputs

The A/D converter power supply (AVcc, AVRH) and analog inputs (AN0 to AN7) must be applied after the digital power supply (Vcc) is switched on. When turning the power off, the A/D converter power supply and analog inputs must be disconnected before the digital power supply is switched off (Vcc). Ensure that AVRH does not exceed AVcc during either power-on or power-off. Even when pins which double as analog input pins are used as input ports, be sure that the input voltage does not exceed AVcc (turning on/off the analog and digital power supplies simultaneously is acceptable).

### • Handling the power supply for high-current output buffer pins (DVcc, DVss)

# Flash memory products and MASK ROM products (MB90F922NC/F922NCS/922NCS/F923NC/F923NCS/F924NC/F924NCS)

In the Flash memory products and MASK ROM products, the power supply for the high-current output buffer pins (DVcc, DVss) is isolated from the digital power supply (Vcc).

Therefore, DVcc can therefore be set to a higher voltage than Vcc. If the power supply for the high-current output buffer pins (DVcc, DVss) is supplied before the digital power supply (Vcc), however, care needs to be taken because it is possible that the port 7 or port 8 stepping motor outputs may momentarily output an "H" or "L" level. In order to prevent this, connect the digital power supply (Vcc) prior to connecting the power supply for the high-current output buffer pins. Even when the high-current output buffer pins are used as general-purpose ports, power should be supplied to the power supply pins for the high-current output buffer pins (DVcc, DVss).

## Evaluation product (MB90V920-101/MB90V920-102)

In the evaluation products, the power supply for the high-current output buffer pins (DVcc, DVss) is not isolated from the digital power supply (Vcc). Therefore, DVcc must therefore be set to a lower voltage than Vcc. The power supply for the high-current output buffer pins (DVcc, DVss) must always be applied after the digital power supply (Vcc) has been connected, and disconnected before the digital power supply (Vcc) is disconnected (the power supply for the high-current output buffer pins may also be connected and disconnected simultaneously with the digital power supply).

Even when the high-current output buffer pins are used as general-purpose ports, power should be supplied to the power supply pins for the high-current output buffer pins (DVcc, DVss).

## • Pull-up/pull-down resistors

MB90920 series does not support internal pull-up/pull-down resistors. Use external components as necessary.

### Precautions when not using a sub clock signal

If the X0A and X1A pins are not connected to an oscillator, apply a pull-down resistance to the X0A pin and leave the X1A pin open.

## · Notes on operating when the external clock is stopped

The MB90920 series is not guaranteed to operate correctly using the internal oscillator circuit when there is no external oscillator or the external clock input is stopped.

### Flash memory security function

A security bit is located within the Flash memory region. The security function is activated by writing the protection code 01<sub>H</sub> to the security bit.

Do not write the value 01H to this address if you are not using the security function.

Please refer to following table for the address of the security bit.

|                           | Flash memory size             | Address for security bit |

|---------------------------|-------------------------------|--------------------------|

| MB90F922NC<br>MB90F922NCS | Built-in 2 Mbits Flash Memory | FC0001н                  |

| MB90F923NCS               | Built-in 3 Mbits Flash Memory | F80001 <sub>H</sub>      |

| MB90F924NCS               | Built-in 4 Mbits Flash Memory | F80001 <sub>H</sub>      |

### Serial communication

In serial communication, reception of wrong data may occur due to noise or other causes. Therefore, design a printed circuit board to prevent noise from occurring. Taking account of the reception of wrong data, detect errors by measures such as adding a checksum to the end of data. If an error is detected, retransmit the data.

### Characteristic difference between flash device and MASK ROM device

In the flash device and the MASK ROM device, the electrical characteristic including current consumption, ESD, latch-up, the noise characteristic, and oscillation characteristic, etc. is different according to the difference between the chip layout and the memory structure.

Reconfirm the electrical characteristic when the product is replaced by another product of the same series.

| Address                  | Register name                              | Symbol | Read/write | Resource name               | Initial value         |  |  |  |

|--------------------------|--------------------------------------------|--------|------------|-----------------------------|-----------------------|--|--|--|

| 000083н                  |                                            | (Disab | led)       |                             | •                     |  |  |  |

| 000084н                  | PWM control register 2                     | PWC2   | R/W        | Stepping motor controller 2 | 000000Х0в             |  |  |  |

| 000085н                  |                                            | (Disab | led)       |                             | •                     |  |  |  |

| 000086н                  | PWM control register 3                     | PWC3   | R/W        | Stepping motor controller 3 | 000000Х0в             |  |  |  |

| 000087н                  |                                            |        | •          |                             |                       |  |  |  |

| 000088н                  | LCD output control register 3              | LOCR3  | R/W        | LCDC                        | XXXXX111 <sub>B</sub> |  |  |  |

| 000089н                  |                                            | (Disab | led)       |                             | •                     |  |  |  |

| 00008Ан                  | A/D setting register 0                     | ADSR0  | R/W        | A/D convertor               | 0000000В              |  |  |  |

| 00008Вн                  | A/D setting register 1                     | ADSR1  | R/W        | A/D converter               | 0000000В              |  |  |  |

| 00008Сн                  | Port input level select 0                  | PIL0   | R/W        |                             | 0000000В              |  |  |  |

| 00008Dн                  | Port input level select 1                  | PIL1   | R/W        | Port input level<br>select  | XXXX0000B             |  |  |  |

| 00008Ен                  | Port input level select 2                  | PIL2   | R/W        | 301001                      | XXXX0000B             |  |  |  |

| 00008Fн<br>to<br>00009Dн | (Disabled)                                 |        |            |                             |                       |  |  |  |

| 00009Ен                  | Program address detection control register | PACSR  | R/W        | Address match detection     | XXXX0X0X <sub>B</sub> |  |  |  |

| 00009Fн                  | Delayed Interrupt/Release Register         | DIRR   | R/W        | Delay interrupt             | XXXXXXX0 <sub>B</sub> |  |  |  |

| 0000А0н                  | Power saving mode control register         | LPMCR  | R/W        | Power saving                | 00011000в             |  |  |  |

| 0000А1н                  | Clock select register                      | CKSCR  | R/W, R     | control circuit             | 11111100в             |  |  |  |

| 0000A2н<br>to<br>0000A7н |                                            | (Disab | led)       |                             |                       |  |  |  |

| 0000А8н                  | Watchdog timer control register            | WDTC   | R, W       | Watchdog timer              | XXXXX111 <sub>B</sub> |  |  |  |

| 0000А9н                  | Time-base timer control register           | TBTC   | R/W, W     | Time-base timer             | 1XX00100 <sub>B</sub> |  |  |  |

| 0000ААн                  | Watch timer control register               | WTC    | R/W, W, R  | Watch timer (sub clock)     | 10001000в             |  |  |  |

| 0000ABн<br>to<br>0000ADн | (Disabled)                                 |        |            |                             |                       |  |  |  |

| 0000АЕн                  | Flash memory control status register       | FMCS   | R/W        | Flash interface             | 000Х0000в             |  |  |  |

| 0000АГн                  |                                            | (Disab | led)       |                             |                       |  |  |  |

| Address       | Register name                                        | Symbol          | Read/write            | Resource name     | Initial value         |  |  |  |  |  |

|---------------|------------------------------------------------------|-----------------|-----------------------|-------------------|-----------------------|--|--|--|--|--|

| 003700н       |                                                      |                 |                       |                   | 1                     |  |  |  |  |  |

| to            | Area reserved for CAN C                              | Controller 2. R | efer to " <b>■</b> CA | N CONTROLLERS"    |                       |  |  |  |  |  |

| 0037FFн       |                                                      |                 |                       |                   |                       |  |  |  |  |  |

| 003800н<br>to | Area reserved for CAN C                              | Controller 2 D  | ofor to "■ CA         | NI CONTDOLLEDO"   |                       |  |  |  |  |  |

| 0038FFн       | Area reserved for CAIN C                             | onilionei 3. n  | elel to  CA           | N CONTROLLERS     |                       |  |  |  |  |  |

| 003900н       |                                                      |                 |                       |                   |                       |  |  |  |  |  |

| to            |                                                      | (Disabl         | ed)                   |                   |                       |  |  |  |  |  |

| 00391Fн       |                                                      |                 | , ,                   |                   |                       |  |  |  |  |  |

| 003920н       | PPG0 down counter register                           | PDCR0           | R                     |                   | 11111111В             |  |  |  |  |  |

| 003921н       | Trade de l'interesse regiones                        | 1 20110         |                       | 16-bit PPG0       | 111111111             |  |  |  |  |  |

| 003922н       | PPG0 cycle setting register                          | PCSR0           | W                     | 10 51(11 00       | 111111111             |  |  |  |  |  |

| 003923н       | Trade dydic setting register                         | 1 00110         |                       |                   | 111111111             |  |  |  |  |  |

| 003924н       | PPG0 duty setting register                           | PDUT0           | W                     | 16-bit PPG0       | 0000000В              |  |  |  |  |  |

| 003925н       | Prad daty setting register                           | PDOTO           | VV                    |                   | 0000000в              |  |  |  |  |  |

| 003926н       | PPG0 output division setting register PPGDIV0 R/W, R |                 |                       |                   |                       |  |  |  |  |  |

| 003927н       |                                                      | (Disabl         | ed)                   |                   |                       |  |  |  |  |  |

| 003928н       | DDO4 dever country as sister.                        | PDCR1           | R                     |                   | 111111111             |  |  |  |  |  |

| 003929н       | PPG1 down counter register                           |                 |                       |                   | 111111111             |  |  |  |  |  |

| 00392Ан       | DDO4 I W II                                          | PCSR1           | W                     |                   | 111111111             |  |  |  |  |  |

| 00392Вн       | PPG1 cycle setting register                          |                 |                       | 16-bit PPG1       | 111111111             |  |  |  |  |  |

| 00392Сн       |                                                      | PDUT1           | W                     |                   | 0000000в              |  |  |  |  |  |

| 00392Dн       | PPG1 duty setting register                           |                 |                       |                   | 0000000в              |  |  |  |  |  |

| 00392Ен       | PPG1output division setting register                 | PPGDIV1         | R/W, R                |                   | 11111100в             |  |  |  |  |  |

| 00392Fн       | ,                                                    | (Disabl         | ed)                   |                   | 1                     |  |  |  |  |  |

| 003930н       |                                                      | <u> </u>        |                       |                   | 111111111             |  |  |  |  |  |

| 003931н       | PPG2 down counter register                           | PDCR2           | R                     |                   | 111111111             |  |  |  |  |  |

| 003932н       |                                                      |                 |                       |                   | 11111111 <sub>B</sub> |  |  |  |  |  |

| 003933н       | PPG2 cycle setting register                          | PCSR2           | W                     | 16-bit PPG2       | 111111111             |  |  |  |  |  |

| 003934н       |                                                      |                 |                       |                   | 0000000B              |  |  |  |  |  |

| 003935н       | PPG2 duty setting register                           | PDUT2           | W                     |                   | 0000000               |  |  |  |  |  |

| 003936н       | PPG2 output division setting register                | PPGDIV2         | R/W, R                |                   | 11111100в             |  |  |  |  |  |

| 003937н       | ,                                                    |                 | , , , , ,             |                   | 1                     |  |  |  |  |  |

| to            |                                                      | (Disabl         | ed)                   |                   |                       |  |  |  |  |  |

| 00393Fн       |                                                      |                 | <del>, '</del>        |                   | 1                     |  |  |  |  |  |

| 003940н       | Input capture register 4                             | IPCP4           | R                     |                   | XXXXXXXXB             |  |  |  |  |  |

| 003941н       | par saprare register i                               | 5               | .,                    | Input capture 4/5 | XXXXXXX               |  |  |  |  |  |

| 003942н       | Input capture register 5                             | IPCP5           | R                     | pat captalo =/0   | XXXXXXXXB             |  |  |  |  |  |

| 003943н       | in par supraise register o                           | 5. 5            |                       |                   | XXXXXXXXB             |  |  |  |  |  |

| Address                  | Register name                                                    | Symbol         | Read/write             | Resource name               | Initial value |  |  |  |

|--------------------------|------------------------------------------------------------------|----------------|------------------------|-----------------------------|---------------|--|--|--|

| 003998н                  | DIAMA access of the C                                            | DWO10          | DAM                    |                             | XXXXXXXXB     |  |  |  |

| 003999н                  | PWM1 compare register 3                                          | PWC13          | R/W                    |                             | XXXXXXXXB     |  |  |  |

| 00399Ан                  | DIAMA compare verietos o                                         | DMC00          | D/M                    | Stepping motor controller 3 | XXXXXXX       |  |  |  |

| 00399Вн                  | PWM2 compare register 3                                          | PWC23          | R/W                    |                             | XXXXXXX       |  |  |  |

| 00399Сн                  | PWM1 select register 3 PWS13                                     |                | R/W                    |                             | 0000000В      |  |  |  |

| 00399Dн                  | PWM2 select register 3                                           | PWS23          | R/W                    |                             | Х000000В      |  |  |  |

| 00399Eн<br>to<br>0039A5н |                                                                  |                |                        |                             |               |  |  |  |

| 0039А6н                  | Flash write control register 0 FWR0                              |                |                        |                             |               |  |  |  |

| 0039А7н                  | Flash write control register 1                                   | FWR1           | - R/W                  | Flash I/F                   | 0000000В      |  |  |  |

| 0039A8н<br>to<br>0039BFн | (Disabled)                                                       |                |                        |                             |               |  |  |  |

| 0039C0н<br>to<br>0039DFн | Area reserved for CAN Controller 2. Refer to "■ CAN CONTROLLERS" |                |                        |                             |               |  |  |  |

| 0039E0н<br>to<br>0039FFн | Area reserved for CAN Controller 3. Refer to "■ CAN CONTROLLERS" |                |                        |                             |               |  |  |  |

| 003A00н<br>to<br>003AFFн | Area reserved for CAN Controller 0. Refer to "■ CAN CONTROLLERS" |                |                        |                             |               |  |  |  |

| 003B00н<br>to<br>003BFFн | Area reserved for CAN C                                          | ontroller 1. F | Refer to " <b>■</b> CA | IN CONTROLLERS"             |               |  |  |  |

| 003С00н<br>to<br>003СFFн | Area reserved for CAN Controller 0. Refer to "■ CAN CONTROLLERS" |                |                        |                             |               |  |  |  |

| 003D00н<br>to<br>003DFFн | Area reserved for CAN Controller 1. Refer to "■ CAN CONTROLLERS" |                |                        |                             |               |  |  |  |

| 003E00н<br>to<br>003EFFн | Area reserved for CAN Controller 2. Refer to "■ CAN CONTROLLERS" |                |                        |                             |               |  |  |  |

| 003F00н<br>to<br>003FFFн | Area reserved for CAN Controller 3. Refer to "■ CAN CONTROLLERS" |                |                        |                             |               |  |  |  |

### (Continued)

- \*5 : Average output current is defined as the average value of the current flowing through any one of the corresponding pins within a period of 100 ms. The "average value" can be calculated by multiplying the "operating current" by the "operating factor".

- \*6 : Average total output current is defined as the average value of the current flowing through all of the corresponding pins within a period of 100 ms. The "average value" can be calculated by multiplying the "operating current" by the "operating factor".

- \*7: Applicable to pins: P10 to P15,P50 to P57,P60 to P67,P70 to P77,P80 to P87,PC0 to PC7,PD0 to PD6, PE0 to PE2

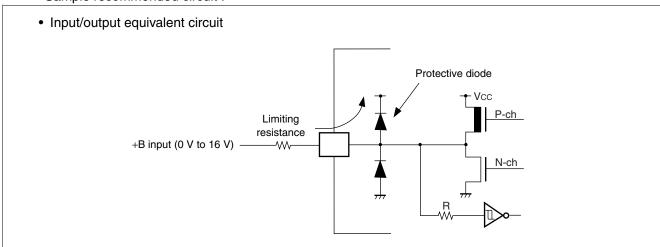

- Use within recommended operating conditions.

- Use at DC voltage (current) .

- The +B signal should always be applied with a limiting resistance placed between the +B signal and the microcontroller.

- The value of the limiting resistance should be set so that when the +B signal is applied, the input current to the microcontroller pin does not exceed rated values, either instantaneously or for prolonged periods.

- Note that when the microcontroller drive current is low, such as in the power saving modes, the +B input potential may pass through the protective diode and increase the potential at the Vcc pin, and this may affect other devices.

- Note that if a +B signal is input when the microcontroller power supply is off (not fixed at 0 V), the microcontroller may partially malfunction on power supplied through the +B signal pin.

- Note that if the +B input is applied during power-on, the power supply voltage may reach a level such that the power-on reset does not function due to the power supplied from the +B signal.

- Care must be taken not to leave +B input pins open.

- Note that analog system input/output pins (LCD drive pins, comparator input pins, etc.) cannot accept +B signal inputs.

- Sample recommended circuit :

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

## 2. Recommended Operating Conditions

(Vss = DVss = AVss = 0.0 V)

| Parameter                      | Symbol   | Val         | ue    | Unit  | Remarks                                                                                                                                                                                     |

|--------------------------------|----------|-------------|-------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Farameter                      | Syllibol | Min         | Max   | Oilit | nemarks                                                                                                                                                                                     |

| Power cupply                   | Vcc      | 4.0         | 5.5   | V     | The low voltage detection reset operates when the power supply voltage reaches 4.2 V $\pm$ 0.2 V.                                                                                           |

| Power supply voltage AVcc DVcc |          | 4.4         | 5.5   | V     | Maintain stop operation status The low voltage detection reset operates when the power supply voltage reaches 4.2 V $\pm$ 0.2 V.                                                            |

| Smoothing capacitor*           | Cs       | 0.1         | 1.0   | μF    | Use a ceramic capacitor or other capacitor of equivalent frequency characteristics. Use a capacitor with a capacitance greater than this capacitor as the bypass capacitor for the Vcc pin. |

| Operating temperature          | Та       | <b>- 40</b> | + 105 | °C    |                                                                                                                                                                                             |

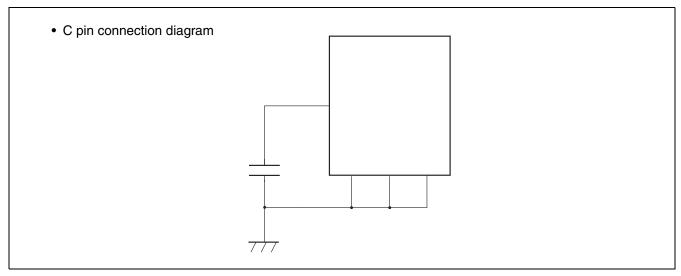

<sup>\*:</sup> Refer to the following diagram for details on the connection of the smoothing capacitor Cs.

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

> Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their representatives beforehand.

## 4. AC Characteristics

## (1) Clock timing

(Vcc = 5.0 V  $\pm 10\%$  , Vss = DVss = AVss = 0.0 V, Ta = -40 °C to +105 °C)

| Doromotor                           | Symbol       | Pin name | Condi- | Value |        | Unit | Remarks |                                                      |  |

|-------------------------------------|--------------|----------|--------|-------|--------|------|---------|------------------------------------------------------|--|

| Parameter                           | Symbol       | Pinname  | tions  | Min   | Тур    | Max  | Unit    | nemarks                                              |  |

|                                     |              |          |        | 3     | _      | 16   | MHz     | 1/2 (PLL stopped) When using the oscillator circuit  |  |

|                                     |              |          |        | 3     | _      | 32   | MHz     | 1/2 (PLL stopped)<br>When using an external<br>clock |  |

| Ola ala fua accessa                 | Fc           | X0, X1   |        | 4     |        | 32   | MHz     | PLL multiplied by 1                                  |  |

| Clock frequency                     |              |          |        | 3     | _      | 16   | MHz     | PLL multiplied by 2                                  |  |

|                                     |              |          |        | 3     | _      | 10.7 | MHz     | PLL multiplied by 3                                  |  |

|                                     |              |          |        | 3     | _      | 8    | MHz     | PLL multiplied by 4                                  |  |

|                                     |              |          |        | 3     |        | 5.33 | MHz     | PLL multiplied by 6                                  |  |

|                                     |              |          |        | 3     |        | 4    | MHz     | PLL multiplied by 8                                  |  |

|                                     | FLC          | X0A, X1A |        |       | 32.768 | _    | kHz     |                                                      |  |

|                                     | tcyL         | X0, X1   |        | 62.5  |        | 333  | ns      | When using an oscillator                             |  |

| Clock cycle time                    |              |          |        | 31.25 |        | 333  | ns      | External clock input                                 |  |

|                                     | tlcyl        | X0A, X1A | Α      |       | 30.5   | _    | μs      |                                                      |  |

| Input clock pulse width             | Pwh, Pwl     | X0       |        | 5     | _      | _    | ns      | Use duty ratio of $50\% \pm 3\%$ as a guideline      |  |

| Width                               | Pwlh, Pwll   | X0A      |        | _     | 15.2   | _    | μs      |                                                      |  |

| Input clock rise and fall time      | tcr, tcf     | X0       |        |       |        | 5    | ns      | When using an external clock signal                  |  |

| Internal operating clock frequency  | Fcp          | _        |        | 1.5   | _      | 32   | MHz     | Using main clock (PLL clock)                         |  |

| Clock frequency                     | FLCP         | FLCP —   |        | _     | 8.192  | _    | kHz     | Using sub clock                                      |  |

| Internal operating clock cycle time | tcp          | _        |        | 31.25 | _      | 666  | ns      | Using main clock<br>(PLL clock)                      |  |

| Clock Cycle tille                   | <b>t</b> LCP | _        |        |       | 122.1  |      | μs      | Using sub clock                                      |  |

## • Guaranteed PLL Operation Range

Internal operating clock frequency vs. Power supply voltage

Power supply voltage Vcc (V)

Range of warranted PLL operation

Namal operating range

Internal clock fcp (MHz)

Notes: • For PLL  $1 \times$  only, use with tcp = 4 MHz or greater.

• Refer to "5. A/D Converter (1) Electrical Characteristics" for details on the A/D converter operating frequency.

## • Bit setting: ESCR0/1/2/3:SCES=1, ECCR0/1/2/3:SCDE=0

$(Vcc = 5.0 V \pm 10\%, Vss = AVss = 0.0 V, T_A = -40 °C to +105 °C)$

| Parameter                                         | Cumbal        | Din nome                      | Conditions                              | Value      |            | Unit |

|---------------------------------------------------|---------------|-------------------------------|-----------------------------------------|------------|------------|------|

| Parameter                                         | Symbol        | Pin name                      | Conditions                              | Min        | Max        | Onit |

| Serial clock cycle time                           | tscyc         | SCK0 to SCK3                  |                                         | 5 tcp      | _          | ns   |

| $SCK \uparrow \rightarrow SOT$ delay time         | tsноvі        | SCK0 to SCK3,<br>SOT0 to SOT3 | Internal shift clock<br>mode output pin | - 50       | + 50       | ns   |

| Valid SIN $\rightarrow$ SCK $↓$                   | tıvslı        | SCK0 to SCK3,                 | C <sub>L</sub> = 80 pF + 1TTL           | tcp + 80   | _          | ns   |

| $SCK \downarrow \to valid \; SIN \; hold \; time$ | tslixi        | SIN0 to SIN3                  |                                         | 0          | _          | ns   |

| Serial clock "H" pulse width                      | <b>t</b> shsl | SCK0 to SCK3                  |                                         | 3 tcp - tR | _          | ns   |

| Serial clock "L" pulse width                      | <b>t</b> slsh | SCRU IU SCRS                  | External shift clock                    | tcp + 10   | _          | ns   |

| $SCK \uparrow \rightarrow SOT$ delay time         | tshove        | SCK0 to SCK3,<br>SOT0 to SOT3 |                                         | _          | 2 tcp + 60 | ns   |

| Valid SIN → SCK $\downarrow$                      | tivsle        | SCK0 to SCK3,                 | mode output pin CL = 80 pF + 1TTL       | 30         | _          | ns   |

| $SCK \downarrow \rightarrow valid SIN hold time$  | tslixe        | SIN0 to SIN3                  | 01 - 00 pr + 111L                       | tcp + 30   | _          | ns   |

| SCK ↓ time                                        | tғ            | SCKU to SCKU                  |                                         | _          | 10         | ns   |

| SCK ↑ time                                        | <b>t</b> R    | SCK0 to SCK3                  |                                         | _          | 10         | ns   |

Notes: • Depending on the machine clock frequency to be used, the maximum baud rate may be limited by some parameters. These parameters are shown in "MB90920 series hardware manual".

- C<sub>L</sub> is the load capacitance connected to the pin during testing.

- top is the internal operating clock cycle time. Refer to "(1) Clock timing".

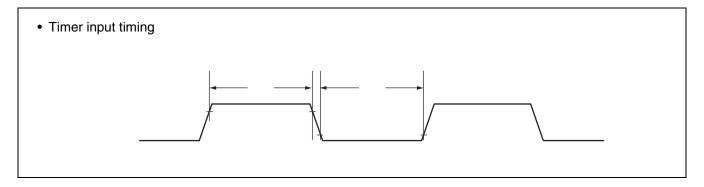

## (5) Timer input timing

$(Vcc = 5.0 V\pm 10\%, Vss = AVss = 0.0 V, T_A = -40 °C to +105 °C)$

| Parameter         | Symbol         | Pin name                  | Conditions |       | lue | Unit |  |

|-------------------|----------------|---------------------------|------------|-------|-----|------|--|

| rarameter         | Symbol         | i iii iiaiiie             | Conditions | Min   | Max | Oill |  |

| Input pulse width | tтıwн<br>tтıwL | TIN0, TIN1,<br>IN0 to IN3 | _          | 4 tcp | _   | ns   |  |

Note: tcp is the internal operating clock cycle time. Refer to "(1) Clock timing".

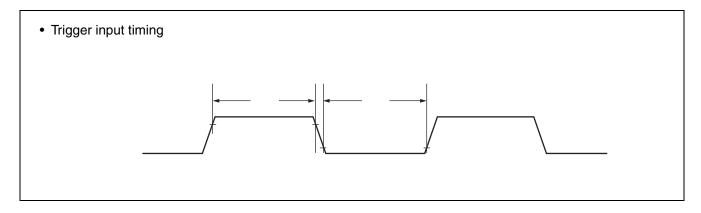

## (6) Trigger input timing

$(Vcc = 5.0 V\pm 10\%, Vss = AVss = 0.0 V, T_A = -40 °C to +105 °C)$

| Parameter         | Symbol          | Pin name     | Conditions | Value     |     | Unit  | Remarks                 |

|-------------------|-----------------|--------------|------------|-----------|-----|-------|-------------------------|

|                   |                 |              |            | Min       | Max | Oilit | i ieiliai ks            |

| Input pulse width | tтядн,<br>tтядь | INT0 to INT7 | _          | 200       | _   | ns    | During normal operation |

|                   |                 | ADTG         |            | tcp + 200 | —   | ns    |                         |

Note: tcp is the internal operating clock cycle time. Refer to "(1) Clock timing".

## 6. Flash Memory Program/Erase Characteristics

| Parameter                            | Conditions                                | Value |     |     | Unit  | Remarks                               |  |

|--------------------------------------|-------------------------------------------|-------|-----|-----|-------|---------------------------------------|--|

| Parameter                            | Conditions                                | Min   | Тур | Max | Oilit | nemarks                               |  |

| Sector erase time                    | T <sub>A</sub> = + 25 °C                  | _     | 0.9 | 3.6 | s     | Excludes pre-programming before erase |  |

| Word (16-bit width) programming time | Vcc = 5.0 V                               | _     | 23  | 370 | μs    | Excludes system-level overhead        |  |

| Chip programming time                | $T_A = +25  ^{\circ}C,$ $V_{CC} = 5.0  V$ | _     | 3.4 | 55  | s     |                                       |  |

| Erase/program cycle                  | _                                         | 10000 |     | _   | cycle |                                       |  |

| Flash memory data retention time     | Average<br>T <sub>A</sub> = + 85 °C       | 20    |     | _   | year  | *                                     |  |

$<sup>^*</sup>$ : This value is calculated from the results of evaluating the reliability of the technology (using Arrhenius equation to translate high temperature measurements into normalized value at + 85  $^{\circ}$ C).