Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                            |

|----------------------------|----------------------------|

| Product Status             | Obsolete                   |

| Core Processor             | F <sup>2</sup> MC-16LX     |

| Core Size                  | 16-Bit                     |

| Speed                      | 32MHz                      |

| Connectivity               | CANbus, LINbus, UART/USART |

| Peripherals                | LCD, LVD, POR, PWM, WDT    |

| Number of I/O              | 93                         |

| Program Memory Size        | 256KB (256K x 8)           |

| Program Memory Type        | Mask ROM                   |

| EEPROM Size                | -                          |

| RAM Size                   | 10K x 8                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                  |

| Data Converters            | A/D 8x8/10b                |

| Oscillator Type            | External                   |

| Operating Temperature      | -40°C ~ 105°C (TA)         |

| Mounting Type              | Surface Mount              |

| Package / Case             | 120-LQFP                   |

| Supplier Device Package    | 120-LQFP (16x16)           |

| Purchase URL               |                            |

| Туре | Circuit                                                                                                                                                                               | Remarks                                                                                                                                                                                                                    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Н    | P-ch Pout  N-ch Nout  Analog input  CMOS hysteresis input Standby control signal or analog input enable signal  Automotive input Standby control signal or analog input enable signal | A/D converter input common general-purpose port  • CMOS output (IoH/IoL = ± 4 mA)  • CMOS hysteresis input (VH/VIL = 0.8 Vcc/0.2 Vcc)  • Automotive input (VH/VIL = 0.8 Vcc/0.5 Vcc)                                       |

| I    | P-ch Pout  Nout  CMOS hysteresis input  Standby control signal  Automotive input  Standby control signal                                                                              | General-purpose port  CMOS output (IoH/IoL = ± 4 mA)  CMOS hysteresis input (VIH/VIL = 0.8 Vcc/0.2 Vcc)  Automotive input (VIH/VIL = 0.8 Vcc/0.5 Vcc)                                                                      |

| J    | P-ch Nout  CMOS hysteresis input Standby control signal Automotive input Standby control signal  CMOS input (SIN) Standby control signal                                              | General-purpose port (serial input)  • CMOS output (IoH/IoL = ± 4 mA)  • CMOS hysteresis input (VIH/VIL = 0.8 Vcc/0.2 Vcc)  • CMOS input (SIN) (VIH/VIL = 0.7 Vcc/0.3 Vcc)  • Automotive input (VIH/VIL = 0.8 Vcc/0.5 Vcc) |

| Туре | Circuit                                          | Remarks                                                     |

|------|--------------------------------------------------|-------------------------------------------------------------|

| N    | Evaluation product  P-ch  N-ch  Nout  Nout  Nout | N-ch open-drain pin IoL = 4 mA                              |

| 0    | Automotive input                                 | Input-only pin Automotive input (VIH/VIL = 0.8 Vcc/0.5 Vcc) |

| P    | P-ch LCDC output                                 | LCDC output pin (COM pin)                                   |

#### **■ HANDLING DEVICES**

#### Strictly observe maximum rated voltages (preventing latch-up)

In CMOS IC devices, a condition known as latch-up may occur if voltages higher than Vcc or lower than Vss are applied to input or output pins other than medium or high withstand voltage pins, or if the voltage applied between VCC and VSS pins exceeds the rated voltage level. If a latch-up occurs, the power supply current may increase dramatically and may destroy semiconductor elements. When using semiconductor devices, always take sufficient care to avoid exceeding maximum ratings.

When the analog system power supply is switched on or off, be careful not to apply the analog power supply (AVcc, AVRH), the analog input voltages and the power supply voltage for the high current output buffer pins (DVcc) in excess of the digital power supply voltage (Vcc).

Once the digital power supply voltage (Vcc) has been disconnected, the analog power supply (AVcc, AVRH) and the power supply voltage for the high current output buffer pins (DVcc) may be turned on in any sequence.

#### Supply voltage stabilization

Rapid fluctuations in the power supply voltage can cause malfunctions even if the Vcc power supply voltage remains within the warranted operating range. It is recommended that the power supply be stabilized such that ripple fluctuations (P-P value) at commercial frequencies (50 Hz/60 Hz) be limited to within 10% of the standard Vcc value, and that transient fluctuations due to power supply switching, etc. be limited to a rate of 0.1 V/ms or less.

#### • Precautions when turning the power on

In order to prevent the built-in step-down circuits from malfunctioning, the time taken for the voltage to rise (0.2 V to 2.7 V) during power-on should be less than 50  $\mu$ s.

#### · Handling unused pins

If unused input pins are left open, they may cause malfunctions or latch-up which may lead to permanent damage to the semiconductor. Unused input pins should therefore be pulled up or pulled down through a resistor of at least  $2 \text{ k}\Omega$ .

Unused input/output pins may be set to the output state and left open, or set to the input state and connected to a pull-up or pull-down resistance of 2  $k\Omega$  or more.

### • Handling A/D converter power supply pins

Even if the A/D converter is not used, the power supply pins should be connected such as  $AV_{CC} = V_{CC}$ , and  $AV_{SS} = AVRH = V_{SS}$ .

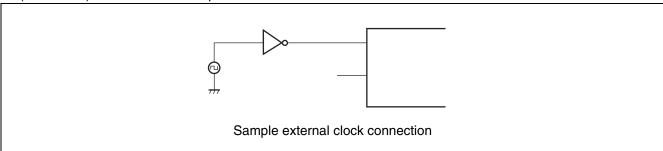

#### · Notes on using an external clock

Even when an external clock is used, an oscillation stabilization wait time is required following power-on reset or release from sub clock mode or stop mode. Furthermore, only the X0A pin should be driven when an external clock is used, with the X1A pin open as shown in the following diagram. Do not use high-speed oscillation pins (X0 and X1) for external clock input.

#### **■ MEMORY MAP**

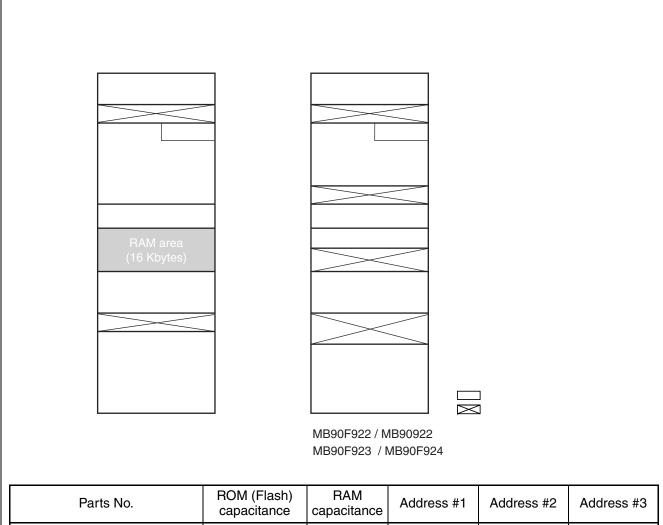

| Parts No.                 | ROM (Flash)<br>capacitance | RAM capacitance | Address #1          | Address #2 | Address #3 |

|---------------------------|----------------------------|-----------------|---------------------|------------|------------|

| MB90F922NC/F922NCS/922NCS | 256 Kbytes                 | 10 Kbytes       | FC0000н             | 004000н    | 002900н    |

| MB90F923NC/F923NCS        | 384 Kbytes                 | 16 Kbytes       | FA0000 <sub>H</sub> | 004А00н    | 003700н    |

| MB90F924NC/F924NCS        | 512 Kbytes                 | 24 Kbytes       | F80000н             | 006А00н    | 003700н    |

<sup>\*:</sup> Evaluation products do not contain internal ROM. Treat this address as the ROM decode area used by the tools.

Note: To select models without the ROM mirror function, refer to the "ROM Mirror Function Selection Module" in Hardware Manual. The image of the ROM data in the FF bank appears at the top of the 00 bank, in order to enable efficient use of small C compiler models. The lower 16-bits of the FF bank addresses are allocated to the same addresses as the lower 16-bits of the 00 bank, making it possible to reference tables in ROM without declaring the "far" modifier with the pointers. For example, when an access is made to the address 00C000H, the actual address to be accessed is FFC000H in ROM. Because the size of the FF bank ROM area exceeds 32 Kbytes, it is not possible to view the entire region in the 00 bank image. Therefore because the ROM data from FF8000H to FFFFFFH appears in the image from 008000H to 00FFFFH, it is recommended that ROM data tables be stored in the area from FF8000H to FFFFFFH.

| Address                  | Register name                             | Symbol         | Read/write            | Resource name       | Initial value |

|--------------------------|-------------------------------------------|----------------|-----------------------|---------------------|---------------|

| 000024н                  |                                           | 00010          | R/W                   |                     | XXXXXXXXB     |

| 000025н                  | Compare clear register                    | CPCLR          | R/W                   |                     | XXXXXXXXB     |

| 000026н                  | Time and data was sisten.                 | TODT           | R/W                   | 16-bit              | 00000000в     |

| 000027н                  | Timer data register                       | TCDT           | R/W                   | free-run timer      | 00000000в     |

| 000028н                  | Lower timer control status register       | TCCSL          | R/W                   |                     | 00000000в     |

| 000029н                  | Higher timer control status register      | TCCSH          | R/W                   |                     | 01-00000в     |

| 00002Ан                  | Lower PPG0 control status register        | PCNTL0         | R/W                   | 16 hit DDC0         | 00000000в     |

| 00002Вн                  | Higher PPG0 control status register       | PCNTH0         | R/W                   | 16-bit PPG0         | 0000001в      |

| 00002Сн                  | Lower PPG1 control status register        | PCNTL1         | R/W                   | 16 hit DDC1         | 00000000в     |

| 00002Dн                  | Higher PPG1 control status register       | PCNTH1         | R/W                   | 16-bit PPG1         | 0000001в      |

| 00002Ен                  | Lower PPG2 control status register        | PCNTL2         | R/W                   | 16 hit DDC0         | 0000000В      |

| 00002Fн                  | Higher PPG2 control status register       | PCNTH2         | R/W                   | 16-bit PPG2         | 0000001в      |

| 000030н                  | External interrupt enable                 | ENIR           | R/W                   |                     | 00000000в     |

| 000031н                  | External interrupt request                | EIRR           | R/W                   | External interrupt  | 00000000в     |

| 000032н                  | Lower external interrupt level            | ELVRL          | R/W                   | External interrupt  | 00000000в     |

| 000033н                  | Higher external interrupt level           | ELVRH          | R/W                   |                     | 00000000в     |

| 000034н                  | Serial mode register 0                    | SMR0           | R/W, W                |                     | 00000000в     |

| 000035н                  | Serial control register 0                 | SCR0           | R/W, W                |                     | 0000000В      |

| 000036н                  | Reception/transmission data register 1    | RDR0/<br>TDR0  | R/W                   |                     | 0000000В      |

| 000037н                  | Serial status register 0                  | SSR0           | R/W, R                | UART                | 00001000в     |

| 000038н                  | Extended communication control register 0 | ECCR0          | R/W, R                | (LIN/SCI) 0         | 000000XXB     |

| 000039н                  | Extended status control register 0        | ESCR0          | R/W                   |                     | 00000100в     |

| 00003Ан                  | Baud rate generator register 00           | BGR00          | R/W                   |                     | 0000000В      |

| 00003Вн                  | Baud rate generator register 01           | BGR01          | R/W, R                |                     | 0000000В      |

| 00003Сн<br>to<br>00003Fн |                                           | (Disab         | led)                  |                     |               |

| 000040н<br>to<br>00004Fн | Area reserved for CAN C                   | ontroller 0. R | efer to " <b>■</b> CA | IN CONTROLLERS"     |               |

| 000050н                  | Lower timer control status register 0     | TMCSR0L        | R/W                   |                     | 0000000В      |

| 000051н                  | Higher timer control status register 0    | TMCSR0H        | R/W                   | 16-bit reload timer | ХХХ10000в     |

| 000052н                  | Timer register 0/relead register 0        | TMR0/          | DAM                   | 0                   | XXXXXXXXB     |

| 000053н                  | Timer register 0/reload register 0        | TMRLR0         | R/W                   |                     | XXXXXXXXB     |

| Address                  | Register name                                                    | Symbol         | Read/write             | Resource name   | Initial value |  |  |  |  |  |

|--------------------------|------------------------------------------------------------------|----------------|------------------------|-----------------|---------------|--|--|--|--|--|

| 003998н                  | DIAMA access of the C                                            | DWO10          | DAM                    |                 | XXXXXXXXB     |  |  |  |  |  |

| 003999н                  | PWM1 compare register 3                                          | PWC13          | R/W                    |                 | XXXXXXXXB     |  |  |  |  |  |

| 00399Ан                  | DIAMA compare verietos o                                         | DMCoo          | D/M                    | Stepping motor  | XXXXXXX       |  |  |  |  |  |

| 00399Вн                  | PWM2 compare register 3                                          | PWC23 R/V      | R/W                    | controller 3    | XXXXXXX       |  |  |  |  |  |

| 00399Сн                  | PWM1 select register 3                                           | PWS13          | R/W                    |                 | 0000000В      |  |  |  |  |  |

| 00399Dн                  | PWM2 select register 3                                           | PWS23          | R/W                    |                 | Х000000В      |  |  |  |  |  |

| 00399Eн<br>to<br>0039A5н |                                                                  | (Disab         | led)                   |                 |               |  |  |  |  |  |

| 0039А6н                  | Flash write control register 0                                   | FWR0           | DAM                    |                 | 0000000В      |  |  |  |  |  |

| 0039А7н                  | Flash write control register 1                                   | FWR1           | - R/W                  | Flash I/F       | 0000000В      |  |  |  |  |  |

| 0039A8н<br>to<br>0039BFн |                                                                  | (Disab         | led)                   |                 |               |  |  |  |  |  |

| 0039C0н<br>to<br>0039DFн | Area reserved for CAN Controller 2. Refer to "■ CAN CONTROLLERS" |                |                        |                 |               |  |  |  |  |  |

| 0039E0н<br>to<br>0039FFн | Area reserved for CAN C                                          | ontroller 3. F | Refer to " <b>■</b> CA | N CONTROLLERS"  |               |  |  |  |  |  |

| 003A00н<br>to<br>003AFFн | Area reserved for CAN C                                          | ontroller 0. F | Refer to " <b>■</b> CA | IN CONTROLLERS" |               |  |  |  |  |  |

| 003B00н<br>to<br>003BFFн | Area reserved for CAN C                                          | ontroller 1. F | Refer to " <b>■</b> CA | IN CONTROLLERS" |               |  |  |  |  |  |

| 003С00н<br>to<br>003СFFн | Area reserved for CAN C                                          | ontroller 0. F | Refer to " <b>■</b> CA | IN CONTROLLERS" |               |  |  |  |  |  |

| 003D00н<br>to<br>003DFFн | Area reserved for CAN Controller 1. Refer to "■ CAN CONTROLLERS" |                |                        |                 |               |  |  |  |  |  |

| 003E00н<br>to<br>003EFFн | Area reserved for CAN Controller 2. Refer to "■ CAN CONTROLLERS" |                |                        |                 |               |  |  |  |  |  |

| 003F00н<br>to<br>003FFFн | Area reserved for CAN Controller 3. Refer to "■ CAN CONTROLLERS" |                |                        |                 |               |  |  |  |  |  |

**List of Message Buffers (ID Registers)**

|               | Add           | ress          |               | Message Buffers (ID Registe | Abbre-  | <b>A</b>      | located at Mariana |

|---------------|---------------|---------------|---------------|-----------------------------|---------|---------------|--------------------|

| CAN0          | CAN1          | CAN2          | CAN3          | Register                    | viation | Access        | Initial Value      |

| 003А00н       | 003В00н       | 003700н       | 003800н       |                             |         |               | XXXXXXXXB          |

| to<br>003A1Fн | to<br>003В1Fн | to<br>00371Fн | to<br>00381Fн | General-purpose RAM         | _       | R/W           | to<br>XXXXXXXXB    |

| 003А20н       | 003В20н       | 003720н       | 003820н       |                             |         |               | XXXXXXXX           |

| 003А21н       | 003В21н       | 003721н       | 003821н       |                             | IDDA    | D 444         | XXXXXXXXB          |

| 003А22н       | 003В22н       | 003722н       | 003822н       | ID register 0               | IDR0    | R/W           | XXXXX <sub>B</sub> |

| 003А23н       | 003В23н       | 003723н       | 003823н       |                             |         |               | XXXXXXXX           |

| 003А24н       | 003В24н       | 003724н       | 003824н       |                             |         |               | XXXXXXXX           |

| 003А25н       | 003В25н       | 003725н       | 003825н       | ID register 1               | IDR1    | R/W           | XXXXXXXX           |

| 003А26н       | 003В26н       | 003726н       | 003826н       | ID register 1               | IDKI    | ri/ VV        | XXXXXв             |

| 003А27н       | 003В27н       | 003727н       | 003827н       |                             |         |               | XXXXXXXXB          |

| 003А28н       | 003В28н       | 003728н       | 003828н       |                             |         |               | XXXXXXXX           |

| 003А29н       | 003В29н       | 003729н       | 003829н       | ID register 2               | IDR2    | R/W           | XXXXXXXXB          |

| 003А2Ан       | 003В2Ан       | 00372Ан       | 00382Ан       | 1D register 2               | IDNZ    | □/ <b>V V</b> | XXXXXв             |

| 003А2Вн       | 003В2Вн       | 00372Вн       | 00382Вн       |                             |         |               | XXXXXXXXB          |

| 003А2Сн       | 003В2Сн       | 00372Сн       | 00382Сн       |                             |         |               | XXXXXXXX           |

| 003А2Dн       | 003В2Dн       | 00372Dн       | 00382Dн       | ID register 3               | IDR3    | DR3 R/W       | XXXXXXX            |

| 003А2Ен       | 003В2Ен       | 00372Ен       | 00382Ен       | Tib register 5              |         |               | XXXXX <sub>B</sub> |

| 003А2Гн       | 003В2Гн       | 00372Fн       | 00382Fн       |                             |         |               | XXXXXXX            |

| 003А30н       | 003В30н       | 003730н       | 003830н       |                             |         |               | XXXXXXXXB          |

| 003А31н       | 003В31н       | 003731н       | 003831н       | ID register 4               | IDR4    | R/W           | XXXXXXXX           |

| 003А32н       | 003В32н       | 003732н       | 003832н       | Togistor 4                  | IDIT    | 10114         | XXXXXB             |

| 003А33н       | 003В33н       | 003733н       | 003833н       |                             |         |               | XXXXXXXX           |

| 003А34н       | 003В34н       | 003734н       | 003834н       |                             |         |               | XXXXXXXXB          |

| 003А35н       | 003В35н       | 003735н       | 003835н       | ID register 5               | IDR5    | R/W           | XXXXXXXXB          |

| 003А36н       | 003В36н       | 003736н       | 003836н       | is regional a               | 15110   |               | XXXXXB             |

| 003А37н       | 003В37н       | 003737н       | 003837н       |                             |         |               | XXXXXXXXB          |

| 003А38н       | 003В38н       | 003738н       | 003838н       |                             |         |               | XXXXXXXXB          |

| 003А39н       | 003В39н       | 003739н       | 003839н       | ID register 6               | IDR6    | R/W           | XXXXXXXXB          |

| 003А3Ан       | 003В3Ан       | 00373Ан       | 00383Ан       |                             |         |               | ХХХХХв             |

| 003А3Вн       | 003В3Вн       | 00373Вн       | 00383Вн       |                             |         |               | XXXXXXX            |

| 003А3Сн       | 003В3Сн       | 00373Сн       | 00383Сн       |                             |         |               | XXXXXXXX           |

| 003АЗДн       | 003В3Дн       | 00373Dн       | 00383Dн       | ID register 7               | IDR7    | R/W           | XXXXXXX            |

| 003А3Ен       | 003В3Ен       | 00373Ен       | 00383Ен       |                             |         |               | XXXXXB             |

| 003А3Гн       | 003В3Гн       | 00373Fн       | 00383Fн       |                             |         |               | XXXXXXXXB          |

(Continued)

35

DS07-13750-4E

### 3. DC Characteristics

(Vcc = 5.0 V  $\pm 10\%$ , Vss = DVss = AVss = 0.0 V, T<sub>A</sub> = -40 °C to +105 °C)

|                            |         | Pin  |                                                                                               | Value              |                                                       |         |      | <u> </u>                                                      |    |

|----------------------------|---------|------|-----------------------------------------------------------------------------------------------|--------------------|-------------------------------------------------------|---------|------|---------------------------------------------------------------|----|

| Parameter                  | Symbol  | name | Conditions                                                                                    | Conditions Min Typ |                                                       | Max     | Unit | Remarks                                                       |    |

|                            | VIHA    |      | _                                                                                             | 0.8 Vcc            | _                                                     | _       | ٧    | Pin inputs if<br>Automotive input<br>levels are selected      |    |

| "H" level<br>input voltage | VIHS    |      | _                                                                                             | 0.8 Vcc            |                                                       |         | V    | Pin inputs if CMOS<br>hysteresis input<br>levels are selected |    |

|                            | VIHC    | _    | _                                                                                             | 0.7 Vcc            |                                                       |         | ٧    | RST input pin (CMOS hysteresis)                               |    |

|                            | VILA    |      | _                                                                                             | _                  |                                                       | 0.5 Vcc | V    | Pin inputs if<br>Automotive input<br>levels are selected      |    |

| "L" level<br>input voltage | VILS    | _    | _                                                                                             |                    | _                                                     | 0.2 Vcc | V    | Pin inputs if CMOS<br>hysteresis input<br>levels are selected |    |

|                            | VILR    | _    | _                                                                                             |                    |                                                       | 0.3 Vcc | ٧    | RST input pin (CMOS hysteresis)                               |    |

|                            | Icc     |      | Maximum operating frequency F <sub>CP</sub> = 32 MHz, normal operation                        | _                  | 35                                                    | 45      | mA   |                                                               |    |

|                            | 100     |      | Maximum operating frequency F <sub>CP</sub> = 32 MHz, writing Flash memory                    |                    | 55                                                    | 65      | mA   |                                                               |    |

|                            | Iccs    |      | Operating frequency FCP = 32 MHz, sleep mode                                                  |                    | 13                                                    | 20      | mA   |                                                               |    |

|                            | Істѕ    |      |                                                                                               |                    | Operating frequency FCP = 2 MHz, time-base timer mode | _       | 0.6  | 1.0                                                           | mA |

| Power supply current*      | ICTSPLL | Vcc  | Operating frequency FCP = 32 MHz, PLL timer mode, External frequency = 4 MHz                  | _                  | 2.5                                                   | 4       | mA   |                                                               |    |

|                            | Iccl    |      | Operating frequency $F_{CP} = 8 \text{ kHz}, T_A = +25 ^{\circ}\text{C},$ sub clock operation | _                  | 120                                                   | 270     | μΑ   |                                                               |    |

|                            | Iccls   |      | Operating frequency $F_{CP} = 8 \text{ kHz}, T_A = +25 ^{\circ}\text{C},$ sub sleep operation |                    | 100                                                   | 200     | μΑ   |                                                               |    |

|                            | Ісст    |      | Operating frequency $F_{CP} = 8 \text{ kHz}, T_A = +25 ^{\circ}\text{C},$ watch mode          | _                  | 90                                                    | 180     | μΑ   |                                                               |    |

|                            | Іссн    |      | T <sub>A</sub> = + 25 °C, stop mode                                                           | _                  | 80                                                    | 170     | μΑ   |                                                               |    |

(Vcc = 5.0 V

$$\pm 10\%$$

, Vss = DVss = AVss = 0.0 V, TA =  $-40$  °C to  $+105$  °C)

| Parameter               | Symbol      | bol Pin name Conditions                                       |     | Value |         |     | Unit | Remarks |

|-------------------------|-------------|---------------------------------------------------------------|-----|-------|---------|-----|------|---------|

| raiametei               | Min Typ Max |                                                               | Max | Oilit | nemarks |     |      |         |

| LCDC leakage<br>current | ILCDC       | V0 to V3,<br>COMm<br>(m = 0 to 3),<br>SEGn,<br>(n = 00 to 31) | _   | _     | _       | 5.0 | μΑ   |         |

| LCD output impedance    | Rvcom       | COMn<br>(n = 0 to 3)                                          | _   | _     | _       | 4.5 | kΩ   |         |

|                         | Rvseg       | SEGn<br>(n = 00 to 31)                                        | _   |       | _       | 17  | kΩ   |         |

<sup>\*:</sup> Power supply current values assume an external clock supplied to the X1 pin and X1A pin. Users must be aware that power supply current levels differ depending on whether an external clock or oscillator is used.

#### (Continued)

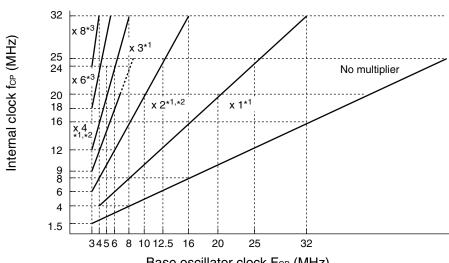

Base oscillator frequency vs. Internal operating clock frequency

Base oscillator clock Fcp (MHz)

\*1: When the PLL multiplier is  $\times$  1,  $\times$  2,  $\times$  3 or  $\times$  4 and the internal clock is 20 MHz < fcp  $\leq$  32 MHz, set DIV2 bit = "1"\*4, CS2 bit = "1" in the PSCCR register.

[Example] When using a base oscillator frequency of 24 MHz at PLL × 1:

CKSCR register : CS1 bit = "0", CS0 bit = "0" PSCCR register : DIV2 bit = "1"\*4,CS2 bit = "1"

[Example] When using a base oscillator frequency of 6 MHz at PLL × 3:

CKSCR register : CS1 bit = "1", CS0 bit = "0" PSCCR register: DIV2 bit = "1"\*4, CS2 bit = "1"

\*2: When the PLL multiplier is  $\times$  2 or  $\times$  4 and the internal clock is 20 MHz < fcp  $\leq$  32 MHz, the following settings are also supported.

PLL × 2: CKSCR register: CS1 bit = "0", CS0 bit = "0"

PSCCR register : DIV2 bit = "0"\*4, CS2 bit = "0"

PLL × 4: CKSCR register: CS1 bit = "0", CS0 bit = "1"

PSCCR register : DIV2 bit = "0"\*4, CS2 bit = "0"

\*3 : When the PLL multiplier is set to  $\times 6$  or  $\times 8$  set "DIV2 bit = "0"\*4 CS2 bit = "1" and "PLL2 bit = 1" in the PSCCR register.

[Example] When using a base oscillator frequency of 4 MHz at PLL × 6:

CKSCR register : CS1 bit = "1", CS0 bit = "0" PLLOS register: DIV2 bit = "0"\*4, CS2 bit = "1"

[Example] When using a base oscillator frequency of 3 MHz at PLL × 8:

CKSCR register : CS1 bit = "1", CS0 bit = "1" PLLOS register: DIV2 bit = "0"\*4, CS2 bit = "1"

\*4: The DIV2 bit is assigned to bit 9 of the PSCCR register and the CS2 bit is assigned to bit 8 of the PSCCR register. Both bits have a default value of "0".

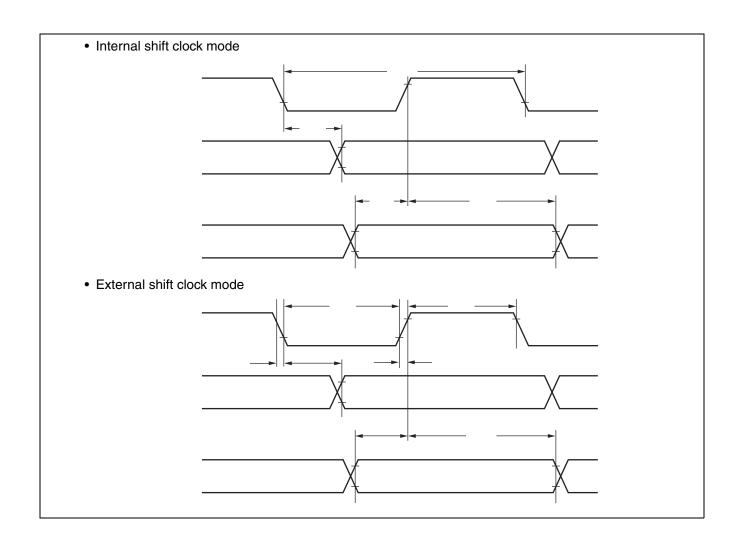

### • Bit setting: ESCR0/1/2/3:SCES=1, ECCR0/1/2/3:SCDE=0

$(Vcc = 5.0 V \pm 10\%, Vss = AVss = 0.0 V, T_A = -40 °C to +105 °C)$

| Parameter                                         | er Symbol Pin name Conditions |                               | Conditions                              | Va         | lue        | Heit |

|---------------------------------------------------|-------------------------------|-------------------------------|-----------------------------------------|------------|------------|------|

| Parameter                                         |                               |                               | Conditions                              | Min        | Max        | Unit |

| Serial clock cycle time                           | tscyc                         | SCK0 to SCK3                  |                                         | 5 tcp      | _          | ns   |

| $SCK \uparrow \rightarrow SOT$ delay time         | tsноvі                        | SCK0 to SCK3,<br>SOT0 to SOT3 | Internal shift clock<br>mode output pin | - 50       | + 50       | ns   |

| Valid SIN $\rightarrow$ SCK $↓$                   | tıvslı                        | SCK0 to SCK3,                 | C <sub>L</sub> = 80 pF + 1TTL           | tcp + 80   | _          | ns   |

| $SCK \downarrow \to valid \; SIN \; hold \; time$ | tslixi                        | SIN0 to SIN3                  |                                         | 0          | _          | ns   |

| Serial clock "H" pulse width                      | <b>t</b> shsl                 | SCK0 to SCK3                  |                                         | 3 tcp - tR | _          | ns   |

| Serial clock "L" pulse width                      | <b>t</b> slsh                 | SCRU IU SCRS                  |                                         | tcp + 10   | _          | ns   |

| $SCK \uparrow \rightarrow SOT$ delay time         | tshove                        | SCK0 to SCK3,<br>SOT0 to SOT3 | External shift clock                    | _          | 2 tcp + 60 | ns   |

| Valid SIN → SCK $\downarrow$                      | tivsle                        | SCK0 to SCK3,                 | mode output pin CL = 80 pF + 1TTL       | 30         | _          | ns   |

| $SCK \downarrow \rightarrow valid SIN hold time$  | tslixe                        | SIN0 to SIN3                  | 00 pr 1 1112                            | tcp + 30   | _          | ns   |

| SCK ↓ time                                        | tғ                            | SCKU to SCKU                  |                                         | _          | 10         | ns   |

| SCK ↑ time                                        | <b>t</b> R                    | SCK0 to SCK3                  |                                         | _          | 10         | ns   |

Notes: • Depending on the machine clock frequency to be used, the maximum baud rate may be limited by some parameters. These parameters are shown in "MB90920 series hardware manual".

- C<sub>L</sub> is the load capacitance connected to the pin during testing.

- top is the internal operating clock cycle time. Refer to "(1) Clock timing".

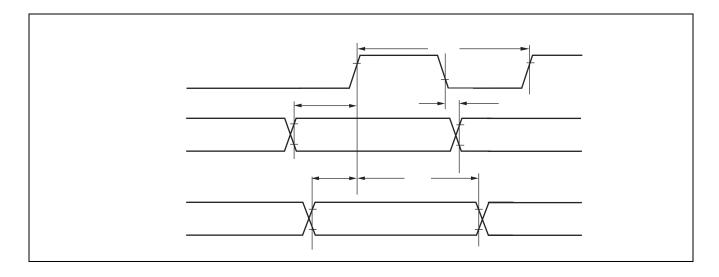

### • Bit setting: ESCR0/1/2/3:SCES=1, ECCR0/1/2/3:SCDE=1

$(Vcc = 5.0 V \pm 10\%, Vss = AVss = 0.0 V, T_A = -40 °C to +105 °C)$

| Parameter                                      | Symbol Pin name |                               | Conditions                                           | Val        | Unit |       |

|------------------------------------------------|-----------------|-------------------------------|------------------------------------------------------|------------|------|-------|

| Parameter                                      |                 |                               | Conditions                                           | Min        | Max  | Oilit |

| Serial clock cycle time                        | tscyc           | SCK0 to SCK3                  |                                                      | 5 tcp      | _    | ns    |

| $SCK \downarrow \to SOT$ delay time            | <b>t</b> sLOVI  | SCK0 to SCK3,<br>SOT0 to SOT3 | Internal shift clock                                 | - 50       | + 50 | ns    |

| Valid SIN $ ightarrow$ SCK $\downarrow$        | tıvshı          | SCK0 to SCK3,                 | mode output pin $C_L = 80 \text{ pF} + 1 \text{TTL}$ | tcp + 80   |      | ns    |

| $SCK \uparrow \rightarrow valid SIN hold time$ | tshixi          | SIN0 to SIN3                  |                                                      | 0          |      | ns    |

| $SOT \to SCK \uparrow delay time$              | tsovнı          | SCK0 to SCK3,<br>SOT0 to SOT3 |                                                      | 3 tcp - 70 | _    | ns    |

Notes: • Depending on the machine clock frequency to be used, the maximum baud rate may be limited by some parameters. These parameters are shown in "MB90920 series hardware manual".

- C<sub>L</sub> is the load capacitance connected to the pin during testing.

- tcp is the internal operating clock cycle time. Refer to "(1) Clock timing".

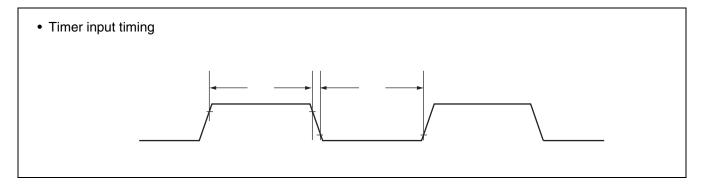

### (5) Timer input timing

$(Vcc = 5.0 V\pm 10\%, Vss = AVss = 0.0 V, T_A = -40 °C to +105 °C)$

| Parameter         | Symbol                  | Pin name                  | Conditions | Va    | lue   | Unit |

|-------------------|-------------------------|---------------------------|------------|-------|-------|------|

| rarameter         | Symbol Fin hame Conditi | Conditions                | Min        | Max   | Oilit |      |

| Input pulse width | tтıwн<br>tтıwL          | TIN0, TIN1,<br>IN0 to IN3 | _          | 4 tcp | _     | ns   |

Note: tcp is the internal operating clock cycle time. Refer to "(1) Clock timing".

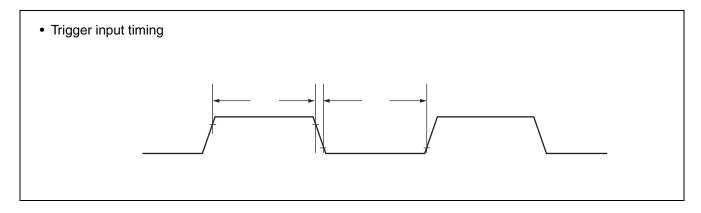

### (6) Trigger input timing

$(Vcc = 5.0 V\pm 10\%, Vss = AVss = 0.0 V, T_A = -40 °C to +105 °C)$

| Parameter         | Symbol          | Pin name     | Conditions | Value     |     | Unit  | Remarks                 |

|-------------------|-----------------|--------------|------------|-----------|-----|-------|-------------------------|

|                   |                 |              |            | Min       | Max | Oilit | nemarks                 |

| Input pulse width | tтядн,<br>tтядь | INT0 to INT7 | _          | 200       | _   | ns    | During normal operation |

|                   |                 | ADTG         |            | tcp + 200 | —   | ns    |                         |

Note: tcp is the internal operating clock cycle time. Refer to "(1) Clock timing".

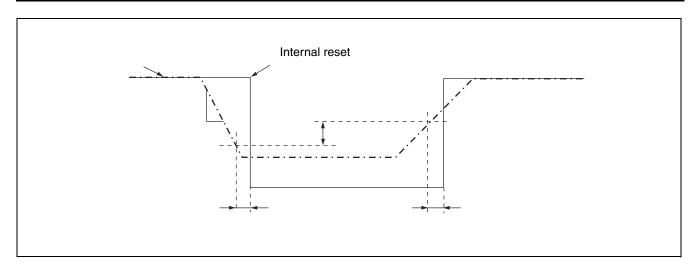

### (7) Low voltage detection

$(V_{SS} = AV_{SS} = 0.0 \text{ V}, T_A = -40 ^{\circ}\text{C to } +105 ^{\circ}\text{C})$

| Parameter                        | Symbol           | Pin name | Conditions | Value  |     |         |      |                                                                                                       |

|----------------------------------|------------------|----------|------------|--------|-----|---------|------|-------------------------------------------------------------------------------------------------------|

|                                  |                  |          |            | Min    | Тур | Max     | Unit | Remarks                                                                                               |

| Detection voltage                | V <sub>DL</sub>  | VCC      | _          | 4.0    | 4.2 | 4.4     | V    | Flash memory product, during voltage drop                                                             |

|                                  |                  |          |            | 3.7    | 4.0 | 4.3     | V    | Evaluation product, during voltage drop                                                               |

| Hysteresis width                 | V <sub>HYS</sub> | VCC      | _          | 190    |     |         | mV   | Flash memory product, during voltage rise                                                             |

|                                  |                  |          |            | 0.1    |     |         | ٧    | Evaluation product, during voltage rise                                                               |

| Power supply voltage change rate | dV/dt            | VCC      | _          | - 0.1  | _   | + 0.1   | V/μs | Flash memory<br>product, dV/dt at low<br>voltage reset                                                |

|                                  |                  |          |            | -0.004 |     | + 0.004 | V/µs | Flash memory<br>product, dV/dt at<br>standard value of<br>low voltage<br>detection/release<br>voltage |

|                                  |                  |          |            | - 0.1  | _   | + 0.02  | V/µs | Evaluation product                                                                                    |

| Detection delay time             | td               | _        | _          | _      | _   | 3.2     | μs   | Flash memory product, when $dV/dt \le 0.004 \ V/\mu s$                                                |

|                                  |                  |          |            |        |     | 35      | μs   | Evaluation product                                                                                    |

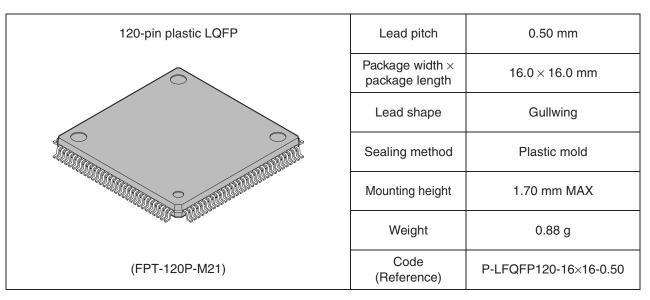

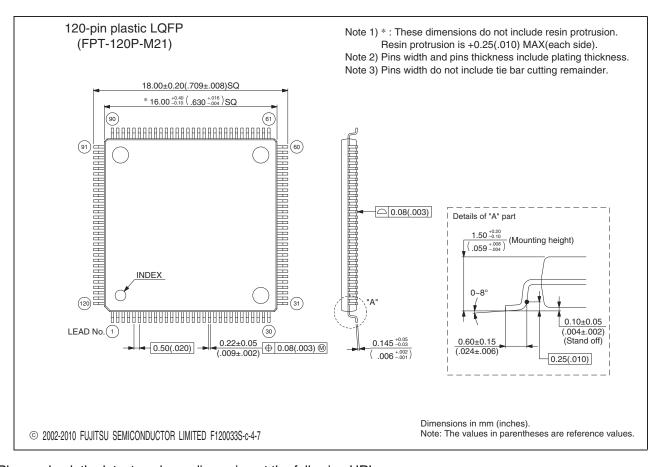

#### **■ PACKAGE DIMENSION**

Please check the latest package dimension at the following URL. http://edevice.fujitsu.com/package/en-search/

### **FUJITSU SEMICONDUCTOR LIMITED**

Nomura Fudosan Shin-yokohama Bldg. 10-23, Shin-yokohama 2-Chome, Kohoku-ku Yokohama Kanagawa 222-0033, Japan

Tel: +81-45-415-5858 http://jp.fujitsu.com/fsl/en/

For further information please contact:

#### **North and South America**

FUJITSU SEMICONDUCTOR AMERICA, INC. 1250 E. Arques Avenue, M/S 333 Sunnyvale, CA 94085-5401, U.S.A. Tel: +1-408-737-5600 Fax: +1-408-737-5999 http://us.fujitsu.com/micro/

#### **Europe**

FUJITSU SEMICONDUCTOR EUROPE GmbH Pittlerstrasse 47, 63225 Langen, Germany Tel: +49-6103-690-0 Fax: +49-6103-690-122 http://emea.fujitsu.com/semiconductor/

#### Korea

FUJITSU SEMICONDUCTOR KOREA LTD. 206 Kosmo Tower Building, 1002 Daechi-Dong, Gangnam-Gu, Seoul 135-280, Republic of Korea Tel: +82-2-3484-7100 Fax: +82-2-3484-7111 http://kr.fujitsu.com/fmk/

#### **Asia Pacific**

FUJITSU SEMICONDUCTOR ASIA PTE. LTD.

151 Lorong Chuan,

#05-08 New Tech Park 556741 Singapore

Tel: +65-6281-0770 Fax: +65-6281-0220

http://www.fujitsu.com/sg/services/micro/semiconductor/

FUJITSU SEMICONDUCTOR SHANGHAI CO., LTD. Rm. 3102, Bund Center, No.222 Yan An Road (E), Shanghai 200002, China

Tel: +86-21-6146-3688 Fax: +86-21-6335-1605

http://cn.fujitsu.com/fss/

FUJITSU SEMICONDUCTOR PACIFIC ASIA LTD. 10/F., World Commerce Centre, 11 Canton Road, Tsimshatsui, Kowloon, Hong Kong

Tel: +852-2377-0226 Fax: +852-2376-3269

http://cn.fujitsu.com/fsp/

Specifications are subject to change without notice. For further information please contact each office.

#### All Rights Reserved.

The contents of this document are subject to change without notice.

Customers are advised to consult with sales representatives before ordering.

The information, such as descriptions of function and application circuit examples, in this document are presented solely for the purpose of reference to show examples of operations and uses of FUJITSU SEMICONDUCTOR device; FUJITSU SEMICONDUCTOR does not warrant proper operation of the device with respect to use based on such information. When you develop equipment incorporating the device based on such information, you must assume any responsibility arising out of such use of the information.

FUJITSU SEMICONDUCTOR assumes no liability for any damages whatsoever arising out of the use of the information.

Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of FUJITSU SEMICONDUCTOR or any third party or does FUJITSU SEMICONDUCTOR warrant non-infringement of any third-party's intellectual property right or other right by using such information. FUJITSU SEMICONDUCTOR assumes no liability for any infringement of the intellectual property rights or other rights of third parties which would result from the use of information contained herein.

The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that FUJITSU SEMICONDUCTOR will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

Exportation/release of any products described in this document may require necessary procedures in accordance with the regulations of the Foreign Exchange and Foreign Trade Control Law of Japan and/or US export control laws.

The company names and brand names herein are the trademarks or registered trademarks of their respective owners.

Edited: Sales Promotion Department