Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | F <sup>2</sup> MC-16LX                                                            |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 32MHz                                                                             |

| Connectivity               | CANbus, LINbus, UART/USART                                                        |

| Peripherals                | LCD, LVD, POR, PWM, WDT                                                           |

| Number of I/O              | 93                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | Mask ROM                                                                          |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 10K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                         |

| Data Converters            | A/D 8x8/10b                                                                       |

| Oscillator Type            | External                                                                          |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 120-LQFP                                                                          |

| Supplier Device Package    | 120-LQFP (16x16)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90922ncspmc-gs-273e1 |

#### (Continued)

• 16-bit reload timer (4 channels)

16-bit reload timer operation (select toggle output or one-shot output)

Selectable event count function

• Real time watch timer (main clock)

Operates directly from oscillator clock.

Interrupt can be generated by second/minute/hour/date counter overflow.

• PPG timer (6 channels)

Output pins (3 channels), external trigger input pin (1 channel)

Operation clock frequencies: fcp, fcp/22, fcp/24, fcp/26

Delay interrupt

Generates interrupt for task switching.

Interrupts to CPU can be generated/cleared by software setting.

• External interrupts (8 channels)

8-channel independent operation

Interrupt source setting available: "L" to "H" edge/ "H" to "L" edge/ "L" level/ "H" level.

• 8/10-bit A/D converter (8 channels)

Conversion time :  $3 \mu s$  (at  $f_{CP} = 32 \text{ MHz}$ )

External trigger activation available (P50/INT0/ADTG)

Internal timer activation available (16-bit reload timer 1)

• UART(LIN/SCI) (4 channels)

Equipped with full duplex double buffer

Clock-asynchronous or clock-synchronous serial transfer is available

• CAN interface (4 channels: CAN0 and CAN2, and CAN1 and CAN3 share transmission and reception pins, and interrupt control registers).

Conforms to CAN specifications version 2.0 Part A and B.

Automatic resend in case of error.

Automatic transfer in response to remote frame.

16 prioritized message buffers for data and ID

Multiple message support

Flexible configuration for receive filter: Full bit compare/full bit mask/two partial bit masks

Supports up to 1 Mbps

CAN wakeup function (RX connected to INT0 internally)

• LCD controller/driver (32 segment x 4 common)

Segment driver and command driver with direct LCD panel (display) drive capability

• Reset on detection of low voltage/program loop

Automatic reset when low voltage is detected

Program looping detection function

Stepping motor controller (4 channels)

High current output for each channel × 4

Synchronized 8/10-bit PWM for each channel × 2

• Sound generator (2 channels)

8-bit PWM signal mixed with tone frequency from 8-bit reload counter.

PWM frequencies: 125 kHz, 62.5 kHz, 31.2 kHz, 15.6 kHz (at fcp = 32 MHz)

Tone frequencies: PWM frequency /2/, divided by (reload frequency +1)

· Input/output ports

General-purpose input/output port (CMOS output) 93 ports

• Function for port input level selection

Automotive/CMOS-Schmitt

• Flash memory security function

Protects the contents of Flash memory (Flash memory product only)

| Pin no. | Pin name | I/O circuit<br>type*1 | Function                                  |

|---------|----------|-----------------------|-------------------------------------------|

|         | P54      |                       | General-purpose I/O port                  |

| 61      | TX0      | 1 .                   | CAN interface 0 TX output pin             |

| 61      | TX2      |                       | CAN interface 2 TX output pin             |

|         | SGA1     |                       | Sound generator ch.1 SGA output pin       |

|         | P55      |                       | General-purpose I/O port                  |

| 60      | RX0      | 1 .                   | CAN interface 0 RX input pin              |

| 63      | RX2      |                       | CAN interface 2 RX input pin              |

|         | INT2     |                       | INT2 external interrupt input pin         |

|         | P56      |                       | General-purpose I/O port                  |

| 91      | SGO0     | I                     | Sound generator ch.0 SGO output pin       |

|         | FRCK     |                       | Free-run timer clock input pin            |

| 00      | P57      |                       | General-purpose I/O port                  |

| 92      | SGA0     |                       | Sound generator ch.0 SGA output pin       |

| 20      | P60      | 11                    | General-purpose I/O port                  |

| 39      | AN0      | - H                   | A/D converter input pin                   |

| 40      | P61      | 11                    | General-purpose I/O port                  |

| 40      | AN1      | - H                   | A/D converter input pin                   |

| 41      | P62      | - Н                   | General-purpose I/O port                  |

| 41      | AN2      | <b></b>               | A/D converter input pin                   |

| 42      | P63      | - Н                   | General-purpose I/O port                  |

| 42      | AN3      | <b></b>               | A/D converter input pin                   |

| 40      | P64      | - Н                   | General-purpose I/O port                  |

| 43      | AN4      | - n                   | A/D converter input pin                   |

| 44      | P65      | - Н                   | General-purpose I/O port                  |

| 44      | AN5      | <b></b>               | A/D converter input pin                   |

| 45      | P66      | - Н                   | General-purpose I/O port                  |

| 45      | AN6      | <b>-</b>   П          | A/D converter input pin                   |

| 46      | P67      | ы                     | General-purpose I/O port                  |

| 46      | AN7      | - H                   | A/D converter input pin                   |

| 67      | P70      |                       | General-purpose output-only port          |

| 67      | PWM1P0   | - L                   | Stepping motor controller ch.0 output pin |

| 60      | P71      |                       | General-purpose output-only port          |

| 68 –    | PWM1M0   | - L                   | Stepping motor controller ch.0 output pin |

| 60      | P72      | 1                     | General-purpose output-only port          |

| 69      | PWM2P0   | - L                   | Stepping motor controller ch.0 output pin |

| Pin no.     | Pin name | I/O circuit<br>type*1 | Function                                                                                        |

|-------------|----------|-----------------------|-------------------------------------------------------------------------------------------------|

| 06          | PD2      |                       | General-purpose I/O port                                                                        |

| 26          | SCK2     | - I                   | UART ch.2 serial clock I/O pin                                                                  |

| 07          | PD3      |                       | General-purpose I/O port                                                                        |

| 27          | SIN3     | . J                   | UART ch.3 serial data input pin                                                                 |

| 00          | PD4      |                       | General-purpose I/O port                                                                        |

| 28          | SOT3     | 1                     | UART ch.3 serial data output pin                                                                |

| 20          | PD5      |                       | General-purpose I/O port                                                                        |

| 29          | SCK3     | 1                     | UART ch.3 serial clock I/O pin                                                                  |

| 30          | PD6      |                       | General-purpose I/O port                                                                        |

| 30          | TOT2     | 1                     | 16-bit reload timer ch.2 TOT output pin                                                         |

| 56          | PE0      |                       | General-purpose I/O port                                                                        |

| 56          | TOT3     | -<br>                 | 16-bit reload timer ch.3 TOT output pin                                                         |

| F7          | PE1      |                       | General-purpose I/O port                                                                        |

| 57          | TIN3     | - I                   | 16-bit reload timer ch.3 TIN input pin                                                          |

| 64          | PE2      |                       | General-purpose I/O port                                                                        |

| 04          | SGO1     | 1                     | Sound generator ch.1 SGO output pin                                                             |

| 62          | RSTO     | N                     | Internal reset signal output pin                                                                |

| 65, 75, 85  | DVCC     | _                     | Power supply input pins dedicated for high current output buffer                                |

| 66, 76, 86  | DVSS     | _                     | Power supply GND pins dedicated for high current output buffer                                  |

| 35          | AVCC     | _                     | A/D converter dedicated power supply input pin                                                  |

| 38          | AVSS     | _                     | A/D converter dedicated power supply GND pin                                                    |

| 36          | AVRH     | _                     | A/D converter Vref+ input pin. Vref- is fixed to AVSS.                                          |

| 89          | MD0      | D                     | Mode setting input pin. Connect to VCC pin.                                                     |

| 88          | MD1      | D                     | Mode setting input pin. Connect to VCC pin.                                                     |

| 87          | MD2      | D/E*2                 | Mode setting input pin. Connect to VSS pin.                                                     |

| 17          | С        | _                     | External capacitor pin. Connect a 0.1 $\mu\text{F}$ capacitor between this pin and the VSS pin. |

| 15, 105     | VCC      | _                     | Power supply input pins                                                                         |

| 16, 47, 106 | VSS      |                       | GND power supply pins                                                                           |

<sup>\*1 :</sup> For I/O circuit type, refer to "■ I/O CIRCUIT TYPES".

<sup>\*2 :</sup> The I/O circuit type is D for Flash memory products and E for evaluation products.

### · Notes on operating in PLL clock mode

On this microcontroller, if in case the crystal oscillator breaks off or an external reference clock input stops while the PLL clock mode is selected, a self-oscillator circuit contained in the PLL may continue its operation at its self-running frequency. However, FUJITSU SEMICONDUCTOR will not guarantee results of operations if such failure occurs.

#### Crystal oscillator circuit

Noise around the X0/X1, or X0A/X1A pins may cause this device to operate abnormally. In the interest of stable operation it is strongly recommended that printed circuit artwork places ground bypass capacitors as close as possible to the X0/X1, X0A/X1A and crystal oscillator (or ceramic oscillator) and that oscillator lines do not cross the lines of other circuits.

Please ask each crystal maker to evaluate the oscillational characteristics of the crystal and this device.

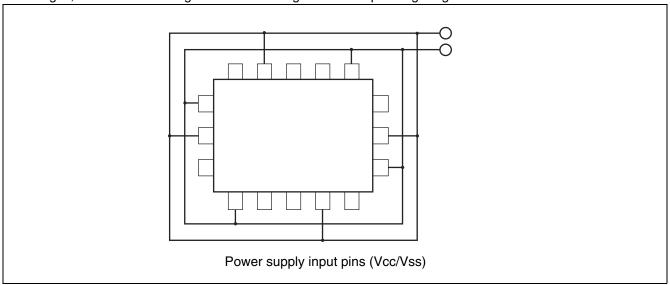

### · Power supply pins

Devices including multiple VCC or VSS pins are designed such that pins that need to be at the same potential are interconnected internally to prevent malfunctions such as latch-up. To reduce unnecessary radiation, prevent malfunctioning of the strobe signal due to the rise of ground level, and observe the standard for total output current, be sure to connect the VCC and VSS pins to the power supply and ground externally.

Always connect all of the VCC pins to the same potential and all of the VSS pins to ground as shown in the following diagram. The device will not operate correctly if multiple VCC or VSS pins are connected to different voltages, even if those voltages are within the guaranteed operating ranges.

In addition, care must be given to connecting the VCC and VSS pins of this device to the current supply source with as low impedance as possible. It is recommended that a 1.0  $\mu$ F bypass capacitor be connected between the VCC and VSS pins as close to the pins as possible.

### Sequence for connecting the A/D converter power supply and analog inputs

The A/D converter power supply (AVcc, AVRH) and analog inputs (AN0 to AN7) must be applied after the digital power supply (Vcc) is switched on. When turning the power off, the A/D converter power supply and analog inputs must be disconnected before the digital power supply is switched off (Vcc). Ensure that AVRH does not exceed AVcc during either power-on or power-off. Even when pins which double as analog input pins are used as input ports, be sure that the input voltage does not exceed AVcc (turning on/off the analog and digital power supplies simultaneously is acceptable).

#### Serial communication

In serial communication, reception of wrong data may occur due to noise or other causes. Therefore, design a printed circuit board to prevent noise from occurring. Taking account of the reception of wrong data, detect errors by measures such as adding a checksum to the end of data. If an error is detected, retransmit the data.

#### Characteristic difference between flash device and MASK ROM device

In the flash device and the MASK ROM device, the electrical characteristic including current consumption, ESD, latch-up, the noise characteristic, and oscillation characteristic, etc. is different according to the difference between the chip layout and the memory structure.

Reconfirm the electrical characteristic when the product is replaced by another product of the same series.

| Address                  | Register name                             | Symbol         | Read/write            | Resource name       | Initial value |

|--------------------------|-------------------------------------------|----------------|-----------------------|---------------------|---------------|

| 000024н                  |                                           | 00010          | R/W                   |                     | XXXXXXXXB     |

| 000025н                  | Compare clear register                    | CPCLR          | R/W                   |                     | XXXXXXXXB     |

| 000026н                  | Time and data was into a                  | TODT           | R/W                   | 16-bit              | 00000000в     |

| 000027н                  | Timer data register                       | TCDT -         | R/W                   | free-run timer      | 00000000в     |

| 000028н                  | Lower timer control status register       | TCCSL          | R/W                   |                     | 00000000в     |

| 000029н                  | Higher timer control status register      | TCCSH          | R/W                   |                     | 01-00000в     |

| 00002Ан                  | Lower PPG0 control status register        | PCNTL0         | R/W                   | 16 hit DDC0         | 00000000в     |

| 00002Вн                  | Higher PPG0 control status register       | PCNTH0         | R/W                   | 16-bit PPG0         | 0000001в      |

| 00002Сн                  | Lower PPG1 control status register        | PCNTL1         | R/W                   | 16 hit DDC1         | 00000000в     |

| 00002Dн                  | Higher PPG1 control status register       | PCNTH1         | R/W                   | 16-bit PPG1         | 0000001в      |

| 00002Ен                  | Lower PPG2 control status register        | PCNTL2         | R/W                   | 16 hit DDC0         | 0000000В      |

| 00002Fн                  | Higher PPG2 control status register       | PCNTH2         | R/W                   | 16-bit PPG2         | 0000001в      |

| 000030н                  | External interrupt enable                 | ENIR           | R/W                   |                     | 00000000в     |

| 000031н                  | External interrupt request                | EIRR           | R/W                   | Estamal intervent   | 00000000в     |

| 000032н                  | Lower external interrupt level            | ELVRL          | R/W                   | External interrupt  | 00000000в     |

| 000033н                  | Higher external interrupt level           | ELVRH          | R/W                   |                     | 00000000в     |

| 000034н                  | Serial mode register 0                    | SMR0           | R/W, W                |                     | 00000000в     |

| 000035н                  | Serial control register 0                 | SCR0           | R/W, W                |                     | 0000000В      |

| 000036н                  | Reception/transmission data register 1    | RDR0/<br>TDR0  | R/W                   |                     | 0000000В      |

| 000037н                  | Serial status register 0                  | SSR0           | R/W, R                | UART                | 00001000в     |

| 000038н                  | Extended communication control register 0 | ECCR0          | R/W, R                | (LIN/SCI) 0         | 000000XXB     |

| 000039н                  | Extended status control register 0        | ESCR0          | R/W                   |                     | 00000100в     |

| 00003Ан                  | Baud rate generator register 00           | BGR00          | R/W                   |                     | 0000000В      |

| 00003Вн                  | Baud rate generator register 01           | BGR01          | R/W, R                |                     | 0000000В      |

| 00003Сн<br>to<br>00003Fн |                                           | (Disab         | led)                  |                     |               |

| 000040н<br>to<br>00004Fн | Area reserved for CAN C                   | ontroller 0. R | efer to " <b>■</b> CA | IN CONTROLLERS"     |               |

| 000050н                  | Lower timer control status register 0     | TMCSR0L        | R/W                   |                     | 0000000В      |

| 000051н                  | Higher timer control status register 0    | TMCSR0H        | R/W                   | 16-bit reload timer | ХХХ10000в     |

| 000052н                  | Timer register O/relead register O        | TMR0/          | D/M                   | 0                   | XXXXXXXX      |

| 000053н                  | Timer register 0/reload register 0        | TMRLR0         | R/W                   |                     | XXXXXXXXB     |

| Address                  | Register name                             | Symbol        | Read/write | Resource name            | Initial value         |

|--------------------------|-------------------------------------------|---------------|------------|--------------------------|-----------------------|

| 0000В0н                  | Interrupt control register 00             | ICR00         | R/W        |                          | 00000111в             |

| 0000В1н                  | Interrupt control register 01             | ICR01         | R/W        |                          | 00000111в             |

| 0000В2н                  | Interrupt control register 02             | ICR02         | R/W        |                          | 00000111в             |

| 0000ВЗн                  | Interrupt control register 03             | ICR03         | R/W        |                          | 00000111в             |

| 0000В4н                  | Interrupt control register 04             | ICR04         | R/W        |                          | 00000111в             |

| 0000В5н                  | Interrupt control register 05             | ICR05         | R/W        |                          | 00000111в             |

| 0000В6н                  | Interrupt control register 06             | ICR06         | R/W        |                          | 00000111в             |

| 0000В7н                  | Interrupt control register 07             | ICR07         | R/W        | Interrupt controller     | 00000111в             |

| 0000В8н                  | Interrupt control register 08             | ICR08         | R/W        | Interrupt controller     | 00000111в             |

| 0000В9н                  | Interrupt control register 09             | ICR09         | R/W        |                          | 00000111в             |

| 0000ВАн                  | Interrupt control register 10             | ICR10         | R/W        |                          | 00000111в             |

| 0000ВВн                  | Interrupt control register 11             | ICR11         | R/W        |                          | 00000111в             |

| 0000ВСн                  | Interrupt control register 12             | ICR12         | R/W        |                          | 00000111в             |

| 0000ВДн                  | Interrupt control register 13             | ICR13         | R/W        |                          | 00000111в             |

| 0000ВЕн                  | Interrupt control register 14             | ICR14         | R/W        |                          | 00000111в             |

| 0000ВFн                  | Interrupt control register 15             | ICR15         | R/W        |                          | 00000111в             |

| 0000С0н<br>to<br>0000С3н |                                           | (Disab        | led)       |                          |                       |

| 0000С4н                  | Serial mode register 1                    | SMR1          | R/W, W     |                          | 0000000В              |

| 0000С5н                  | Serial control register 1                 | SCR1          | R/W, W     |                          | 0000000В              |

| 0000С6н                  | Reception/transmission data register 1    | RDR1/<br>TDR1 | R/W        |                          | 0000000в              |

| 0000С7н                  | Serial status register 1                  | SSR1          | R/W, R     | UART                     | 00001000в             |

| 0000С8н                  | Extended communication control register 1 | ECCR1         | R/W, R     | (LIN/SCI) 1              | 000000XXB             |

| 0000С9н                  | Extended status control register 1        | ESCR1         | R/W        |                          | 00000100в             |

| 0000САн                  | Baud rate generator register 10           | BGR10         | R/W        |                          | 0000000В              |

| 0000СВн                  | Baud rate generator register 11           | BGR11         | R/W, R     |                          | 0000000В              |

| 0000ССн                  | Lower watch timer control register        | WTCRL         | R/W        | Dealthre                 | 000XXXX0 <sub>B</sub> |

| 0000СDн                  | Middle watch timer control register       | WTCRM         | R/W        | Real-time<br>watch timer | 0000000В              |

| 0000СЕн                  | Higher watch timer control register       | WTCRH         | R/W        |                          | XXXXXX00 <sub>B</sub> |

| 0000СFн                  | Sub clock control register                | PSCCR         | W          | Sub clock                | XXXX0000 <sub>B</sub> |

| 0000D0н                  | Input capture control status 4/5          | ICS45         | R/W        | Input capture 4/5        | 0000000В              |

| 0000D1н                  | Input capture edge register 4/5           | ICE45         | R/W, R     | input capture 4/5        | XXXXXXX               |

| 0000D2н                  | Input capture control status 6/7          | ICS67         | R/W        | Input capture 6/7        | 0000000В              |

| 0000Д3н                  | Input capture edge register 6/7           | ICE67         | R/W, R     | input capture 6/7        | XXX0X0XX <sub>B</sub> |

| Address       | Register name                                                    | Symbol          | Read/write            | Resource name     | Initial value         |  |  |  |  |  |  |

|---------------|------------------------------------------------------------------|-----------------|-----------------------|-------------------|-----------------------|--|--|--|--|--|--|

| 003700н       |                                                                  |                 |                       |                   | 1                     |  |  |  |  |  |  |

| to            | Area reserved for CAN C                                          | Controller 2. R | efer to " <b>■</b> CA | N CONTROLLERS"    |                       |  |  |  |  |  |  |

| 0037FFн       |                                                                  |                 |                       |                   |                       |  |  |  |  |  |  |

| 003800н<br>to | Area reserved for CAN Controller 3. Refer to "■ CAN CONTROLLERS" |                 |                       |                   |                       |  |  |  |  |  |  |

| 0038FFн       | Area reserved for CAIN Controller 3. Refer to CAIN COINTROLLERS  |                 |                       |                   |                       |  |  |  |  |  |  |

| 003900н       |                                                                  |                 |                       |                   |                       |  |  |  |  |  |  |

| to            | (Disabled)                                                       |                 |                       |                   |                       |  |  |  |  |  |  |

| 00391Fн       |                                                                  |                 | , ,                   |                   |                       |  |  |  |  |  |  |

| 003920н       | PPG0 down counter register                                       | PDCR0           | R                     |                   | 11111111В             |  |  |  |  |  |  |

| 003921н       | The do down obtained regions.                                    | 1 20110         |                       | 16-bit PPG0       | 111111111             |  |  |  |  |  |  |

| 003922н       | PPG0 cycle setting register                                      | PCSR0           | W                     | 10 51(11 00       | 111111111             |  |  |  |  |  |  |

| 003923н       | Trade dydic setting register                                     | 1 00110         |                       |                   | 111111111             |  |  |  |  |  |  |

| 003924н       | PPG0 duty setting register                                       | PDUT0           | W                     |                   | 0000000В              |  |  |  |  |  |  |

| 003925н       | Prad daty setting register                                       | PDOTO           | VV                    | 16-bit PPG0       | 0000000В              |  |  |  |  |  |  |

| 003926н       | PPG0 output division setting register                            | PPGDIV0         | R/W, R                |                   | 11111100в             |  |  |  |  |  |  |

| 003927н       |                                                                  | (Disabl         | ed)                   |                   |                       |  |  |  |  |  |  |

| 003928н       | DDO4 dever country as sister.                                    | DDCD4           | П                     |                   | 111111111             |  |  |  |  |  |  |

| 003929н       | PPG1 down counter register                                       | PDCR1           | R                     |                   | 111111111             |  |  |  |  |  |  |

| 00392Ан       | DDO4 I W II                                                      | PCSR1 PDUT1     | 147                   | 16-bit PPG1       | 111111111             |  |  |  |  |  |  |

| 00392Вн       | PPG1 cycle setting register                                      |                 | W                     |                   | 111111111             |  |  |  |  |  |  |

| 00392Сн       |                                                                  |                 |                       |                   | 0000000в              |  |  |  |  |  |  |

| 00392Dн       | PPG1 duty setting register                                       |                 | W                     |                   | 0000000в              |  |  |  |  |  |  |

| 00392Ен       | PPG1output division setting register                             | PPGDIV1         | R/W, R                |                   | 11111100в             |  |  |  |  |  |  |

| 00392Fн       | ,                                                                | (Disabl         | ed)                   |                   | 1                     |  |  |  |  |  |  |

| 003930н       |                                                                  | <u> </u>        |                       |                   | 111111111             |  |  |  |  |  |  |

| 003931н       | PPG2 down counter register                                       | PDCR2           | R                     |                   | 111111111             |  |  |  |  |  |  |

| 003932н       |                                                                  |                 |                       |                   | 11111111 <sub>B</sub> |  |  |  |  |  |  |

| 003933н       | PPG2 cycle setting register                                      | PCSR2           | W                     | 16-bit PPG2       | 11111111В             |  |  |  |  |  |  |

| 003934н       |                                                                  |                 |                       |                   | 0000000B              |  |  |  |  |  |  |

| 003935н       | PPG2 duty setting register                                       | PDUT2           | W                     |                   | 0000000               |  |  |  |  |  |  |

| 003936н       | PPG2 output division setting register                            | PPGDIV2         | R/W, R                |                   | 11111100в             |  |  |  |  |  |  |

| 003937н       | ,                                                                |                 | , , , , ,             |                   | 1                     |  |  |  |  |  |  |

| to            |                                                                  | (Disabl         | ed)                   |                   |                       |  |  |  |  |  |  |

| 00393Fн       |                                                                  |                 | <del>, '</del>        |                   |                       |  |  |  |  |  |  |

| 003940н       | Input capture register 4                                         | IPCP4           | R                     |                   | XXXXXXXXB             |  |  |  |  |  |  |

| 003941н       | par saprare register i                                           | 5               | .,                    | Input capture 4/5 | XXXXXXX               |  |  |  |  |  |  |

| 003942н       | Input capture register 5                                         | IPCP5           | R                     | par captaro =/0   | XXXXXXXXB             |  |  |  |  |  |  |

| 003943н       | In particular or regional or                                     | 5. 5            |                       |                   | XXXXXXXXB             |  |  |  |  |  |  |

| Address                  | Register name                            | Symbol | Read/write | Resource name       | Initial value |

|--------------------------|------------------------------------------|--------|------------|---------------------|---------------|

| 003944н                  |                                          | IDODO  | _          |                     | XXXXXXXX      |

| 003945н                  | Input capture register 6                 | IPCP6  | R          | legant continue C/7 | XXXXXXXX      |

| 003946н                  | I I I                                    | IDOD7  | -          | Input capture 6/7   | XXXXXXX       |

| 003947н                  | Input capture register 7                 | IPCP7  | R          |                     | XXXXXXXX      |

| 003948н<br>to<br>00394Fн |                                          | (Disab | led)       |                     |               |

| 003950н                  | Minute data ragistar 2/Paland ragistar 2 | TMR2/  | R/W        | 16-bit reload timer | XXXXXXXX      |

| 003951н                  | Minute data register 2/Reload register 2 | TMRLR2 | IT/VV      | 2                   | XXXXXXXXB     |

| 003952н                  | Minute data register 2/Paland register 2 | TMR3/  | R/W        | 16-bit reload timer | XXXXXXX       |

| 003953н                  | Minute data register 3/Reload register 3 | TMRLR3 | IT/VV      | 3                   | XXXXXXX       |

| 003954н<br>to<br>003957н |                                          | (Disab | led)       |                     |               |

| 003958н                  |                                          |        |            |                     | XXXXXXXXB     |

| 003959н                  | Sub second data register                 | WTBR   | R/W        | Real time           | XXXXXXX       |

| 00395Ан                  |                                          |        |            |                     | XXXXXXX       |

| 00395Вн                  | Second data register                     | WTSR   | R/W        | watch timer         | ХХ000000в     |

| 00395Сн                  | Minute data register                     | WTMR   | R/W        |                     | ХХ000000в     |

| 00395Dн                  | Hour data register                       | WTHR   | R/W        |                     | XXX00000B     |

| 00395Ен                  | Day data register                        | WTDR   | R/W        |                     | 00Х00001в     |

| 00395Fн                  |                                          | (Disab | led)       |                     | <del> </del>  |

| 003960н                  |                                          |        |            |                     | XXXXXXXXB     |

| 003961н                  |                                          |        |            |                     | XXXXXXX       |

| 003962н                  |                                          |        |            |                     | XXXXXXX       |

| 003963н                  |                                          |        |            |                     | XXXXXXX       |

| 003964н                  |                                          |        |            |                     | XXXXXXX       |

| 003965н                  |                                          |        |            |                     | XXXXXXX       |

| 003966н                  |                                          |        |            | LCD                 | XXXXXXXXB     |

| 003967н                  | LCD display RAM                          | VRAM   | R/W        | controller/         | XXXXXXX       |

| 003968н                  |                                          |        |            | driver              | XXXXXXX       |

| 003969н                  |                                          |        |            |                     | XXXXXXXXB     |

| 00396Ан                  |                                          |        |            |                     | XXXXXXX       |

| 00396Вн                  |                                          |        |            |                     | XXXXXXX       |

| 00396Сн                  |                                          |        |            |                     | XXXXXXX       |

| 00396Dн                  |                                          |        |            |                     | XXXXXXX       |

| 00396Ен                  |                                          |        |            |                     | XXXXXXXXB     |

| 00396Fн                  |                                          |        |            |                     | (Continued    |

|         | Add     | ress    |         | Register         | Abbre-  | Access    | Initial Value      |  |

|---------|---------|---------|---------|------------------|---------|-----------|--------------------|--|

| CAN0    | CAN1    | CAN2    | CAN3    | negister         | viation | Access    | iiiiliai value     |  |

| 003А40н | 003В40н | 003740н | 003840н |                  |         |           | XXXXXXXXB          |  |

| 003А41н | 003В41н | 003741н | 003841н | ID register 8    | IDR8    | R/W       | XXXXXXX            |  |

| 003А42н | 003В42н | 003742н | 003842н | 12 Togister 6    | IDITO   | 1 1/ V V  | XXXXX <sub>B</sub> |  |

| 003А43н | 003В43н | 003743н | 003843н |                  |         |           | XXXXXXX            |  |

| 003А44н | 003В44н | 003744н | 003844н |                  |         |           | XXXXXXXXB          |  |

| 003А45н | 003В45н | 003745н | 003845н | ID register 9    | IDR9    | R/W       | XXXXXXXXB          |  |

| 003А46н | 003В46н | 003746н | 003846н | Tib Togistor o   | 15110   | 1000      | XXXXX <sub>B</sub> |  |

| 003А47н | 003В47н | 003747н | 003847н |                  |         |           | XXXXXXX            |  |

| 003А48н | 003В48н | 003748н | 003848н |                  |         |           | XXXXXXXXB          |  |

| 003А49н | 003В49н | 003749н | 003849н | ID register 10   | IDR10   | R/W       | XXXXXXX            |  |

| 003А4Ан | 003В4Ан | 00374Ан | 00384Ан | Togotor To       | IDITIO  | 1 17 V V  | XXXXX <sub>B</sub> |  |

| 003А4Вн | 003В4Вн | 00374Вн | 00384Вн |                  |         |           | XXXXXXX            |  |

| 003А4Сн | 003В4Сн | 00374Сн | 00384Сн |                  | IDR11   |           | XXXXXXXXB          |  |

| 003А4Dн | 003В4Он | 00374Dн | 00384Dн | ID register 11   |         | R/W       | XXXXXXX            |  |

| 003А4Ен | 003В4Ен | 00374Ен | 00384Ен | in a regional in |         |           | ХХХХХв             |  |

| 003А4Гн | 003В4Гн | 00374Fн | 00384Fн |                  |         |           | XXXXXXX            |  |

| 003А50н | 003В50н | 003750н | 003850н |                  | IDR12   |           | XXXXXXXXB          |  |

| 003А51н | 003В51н | 003751н | 003851н | ID register 12   |         | IDR12 R/W | XXXXXXX            |  |

| 003А52н | 003В52н | 003752н | 003852н |                  |         |           | ХХХХХв             |  |

| 003А5Зн | 003В53н | 003753н | 003853н |                  |         |           | XXXXXXX            |  |

| 003А54н | 003В54н | 003754н | 003854н |                  |         |           | XXXXXXXXB          |  |

| 003А55н | 003В55н | 003755н | 003855н | ID register 13   | IDR13   | R/W       | XXXXXXX            |  |

| 003А56н | 003В56н | 003756н | 003856н |                  |         |           | ХХХХХв             |  |

| 003А57н | 003В57н | 003757н | 003857н |                  |         |           | XXXXXXX            |  |

| 003А58н | 003В58н | 003758н | 003858н |                  |         |           | XXXXXXXXB          |  |

| 003А59н | 003В59н | 003759н | 003859н | ID register 14   | IDR14   | R/W       | XXXXXXX            |  |

| 003А5Ан | 003В5Ан | 00375Ан | 00385Ан |                  |         |           | XXXXXB             |  |

| 003А5Вн | 003В5Вн | 00375Вн | 00385Вн |                  |         |           | XXXXXXX            |  |

| 003А5Сн | 003В5Сн | 00375Сн | 00385Сн |                  |         |           | XXXXXXXX           |  |

| 003А5Дн | 003В5Дн | 00375Dн | 00385Dн | ID register 15   | IDR15   | R/W       | XXXXXXX            |  |

| 003А5Ен | 003В5Ен | 00375Ен | 00385Ен |                  |         |           | XXXXXB             |  |

| 003А5Гн | 003В5Гн | 00375Fн | 00385Fн |                  |         |           | XXXXXXX            |  |

### **List of Message Buffers (DLC Registers)**

| Address |         | Pogistor | Abbrevia- | Access          | Initial Value |                 |                                           |                   |

|---------|---------|----------|-----------|-----------------|---------------|-----------------|-------------------------------------------|-------------------|

| CAN0    | CAN1    | CAN2     | CAN3      | Register        | tion          | Access          | miliai value                              |                   |

| 003А60н | 003В60н | 003760н  | 003860н   | DLC register 0  | DLCR0         | R/W             | XXXX <sub>B</sub>                         |                   |

| 003А61н | 003В61н | 003761н  | 003861н   | DLC register 0  | DLCHU         | I               | <b>XXX</b> B                              |                   |

| 003А62н | 003В62н | 003762н  | 003862н   | DLC register 1  | DLCR1         | R/W             | XXXX <sub>B</sub>                         |                   |

| 003А63н | 003В63н | 003763н  | 003863н   | DLC register i  | DLCHI         | □/ <b>VV</b>    | <b>XXX</b> B                              |                   |

| 003А64н | 003В64н | 003764н  | 003864н   | DLC register 2  | DLCR2         | R/W             | VVV <sub>2</sub>                          |                   |

| 003А65н | 003В65н | 003765н  | 003865н   | DLC register 2  | DLUNZ         | I               | XXXX <sub>В</sub>                         |                   |

| 003А66н | 003В66н | 003766н  | 003866н   | DLC register 2  | DI CD2        | R/W             | XXXX <sub>B</sub>                         |                   |

| 003А67н | 003В67н | 003767н  | 003867н   | DLC register 3  | DLCR3         | □/ <b>VV</b>    | <b>XXX</b> B                              |                   |

| 003А68н | 003В68н | 003768н  | 003868н   | DLC register 4  | DLCR4         | R/W             | XXXX <sub>B</sub>                         |                   |

| 003А69н | 003В69н | 003769н  | 003869н   | DLC register 4  | DLUN4         | □/ <b>VV</b>    | <b>XXX</b> B                              |                   |

| 003А6Ан | 003В6Ан | 00376Ан  | 00386Ан   | DI C register 5 | DLCR5         | 5 R/W           | P/M/                                      | XXXX <sub>B</sub> |

| 003А6Вн | 003В6Вн | 00376Вн  | 00386Вн   | DLC register 5  | DLCho         |                 | <b>XXX</b> B                              |                   |

| 003А6Сн | 003В6Сн | 00376Сн  | 00386Сн   | DLC register 6  | DLCR6         | R6 R/W          | Β/MYY)                                    | XXXX <sub>B</sub> |

| 003А6Dн | 003В6Dн | 00376Dн  | 00386Dн   | DLC register 6  | DECITO        |                 | <b>XXX</b> B                              |                   |

| 003А6Ен | 003В6Ен | 00376Ен  | 00386Ен   | DLC register 7  | DLCR7         | R/W             | XXXX <sub>B</sub>                         |                   |

| 003А6Гн | 003В6Гн | 00376Fн  | 00386Fн   | DLC register /  | DEOIT         | 1 t/ <b>V V</b> | XXXXB                                     |                   |

| 003А70н | 003В70н | 003770н  | 003870н   | DLC register 8  | DLCR8         | R/W             | XXXX <sub>B</sub>                         |                   |

| 003А71н | 003В71н | 003771н  | 003871н   | DLC register o  | DLUNG         | 11/ V V         | XXXXB                                     |                   |

| 003А72н | 003В72н | 003772н  | 003872н   | DLC register 9  | DI CB0        | R/W             | XXXX <sub>B</sub>                         |                   |

| 003А73н | 003В73н | 003773н  | 003873н   | DLC register 9  | DLCR9         | H/VV            | XXXB                                      |                   |

| 003А74н | 003В74н | 003774н  | 003874н   | DLC register 10 | DLCR10        | DLCR10 R/W      | XXXX <sub>B</sub>                         |                   |

| 003А75н | 003В75н | 003775н  | 003875н   | DLO register 10 | DECITIO       | 1 1/ V V        | XXXXB                                     |                   |

| 003А76н | 003В76н | 003776н  | 003876н   | DLC register 11 | DLCR11        | R/W             | XXXX <sub>B</sub>                         |                   |

| 003А77н | 003В77н | 003777н  | 003877н   | DLO register 11 | DLOITI        | 1 1/ V V        | XXXXB                                     |                   |

| 003А78н | 003В78н | 003778н  | 003878н   | DLC register 12 | DLCR12        | R/W             | XXXX <sub>B</sub>                         |                   |

| 003А79н | 003В79н | 003779н  | 003879н   | DLC register 12 | DLONIZ        | I → / V V       | XXXXB                                     |                   |

| 003А7Ан | 003В7Ан | 00377Ан  | 00387Ан   | DLC register 13 | DLCR13        | D/M             | XXXX <sub>B</sub>                         |                   |

| 003А7Вн | 003В7Вн | 00377Вн  | 00387Вн   | DLO register 13 | DECITIO       | R/W             | XXXXB                                     |                   |

| 003А7Сн | 003В7Сн | 00377Сн  | 00387Сн   | DLC register 14 | DLCR14        | R/W             | XXXX <sub>B</sub>                         |                   |

| 003А7Dн | 003В7Dн | 00377Dн  | 00387Dн   | DEO legister 14 | DLON14        | 1 1/ V V        | <b>\</b> \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ |                   |

| 003А7Ен | 003В7Ен | 00377Ен  | 00387Ен   | DLC register 15 | DI CB15       | D/M             | XXXX <sub>B</sub>                         |                   |

| 003А7Гн | 003В7Гн | 00377Fн  | 00387Fн   | DEO legister 10 | DLCR15        | R/W             | <b>VVVV</b> R                             |                   |

## ■ INTERRUPT SOURCES, INTERRUPT VECTORS, AND INTERRUPT CONTROL REGISTERS

| Interrupt source                                                  | El <sup>2</sup> OS | Int    | terrupt | vector              | Interru<br>re | Priority   |          |

|-------------------------------------------------------------------|--------------------|--------|---------|---------------------|---------------|------------|----------|

| ·                                                                 | corresponding      | Number |         | Address             | ICR           | Address    | - *2     |

| Reset                                                             | ×                  | #08    | 08н     | FFFFDC <sub>H</sub> | _             | _          | High     |

| INT9 instruction                                                  | ×                  | #09    | 09н     | FFFFD8 <sub>H</sub> | _             | _          | <b>A</b> |

| Exception processing                                              | ×                  | #10    | 0Ан     | FFFFD4 <sub>H</sub> | _             | _          | 1 1      |

| CAN0 received/CAN2 received                                       | ×                  | #11    | 0Вн     | FFFFD0 <sub>H</sub> |               |            |          |

| CAN0 transmitted/node status/<br>CAN2 transmitted/node status     | ×                  | #12    | 0Сн     | FFFFCCH             | ICR00         | 0000В0н*1  |          |

| CAN1 received/CAN3 received                                       | ×                  | #13    | 0Дн     | FFFFC8 <sub>H</sub> |               |            |          |

| CAN1 transmitted/node status/<br>CAN3 transmitted/node status/SIO | ×                  | #14    | 0Ен     | FFFFC4 <sub>H</sub> | ICR01         | 0000В1н*1  |          |

| Input capture 0                                                   | Δ                  | #15    | 0Гн     | FFFFC0 <sub>H</sub> |               |            |          |

| DTP/ external interrupt - ch.0/ch.1 detected                      | Δ                  | #16    | 10н     | FFFFBC <sub>H</sub> | ICR02         | 0000В2н*1  |          |

| Reload timer 0                                                    | Δ                  | #17    | 11н     | FFFFB8 <sub>H</sub> | ICR03         | 0000B3н*1  | 1        |

| Reload timer 2                                                    | Δ                  | #18    | 12н     | FFFFB4 <sub>H</sub> | ICHU3         | 0000ВЗн    |          |

| Input capture 1                                                   | Δ                  | #19    | 13н     | FFFFB0 <sub>H</sub> |               | 0000В4н*1  |          |

| DTP/ external interrupt - ch.2/ch.3 detected                      | Δ                  | #20    | 14н     | FFFFACH             | ICR04         |            |          |

| Input capture 2                                                   | Δ                  | #21    | 15н     | FFFFA8 <sub>H</sub> | ICR05         | 0000B5н*1  |          |

| Reload timer 3                                                    | Δ                  | #22    | 16н     | FFFFA4 <sub>H</sub> | ICHUS         |            |          |

| Input capture 3/4/5/6/7                                           | Δ                  | #23    | 17н     | FFFFA0 <sub>H</sub> |               |            | 1        |

| DTP/ external interrupt - ch.4/ ch.5 detected UART3 RX            | Δ                  | #24    | 18н     | FFFF9C <sub>H</sub> | ICR06         | 0000В6н*1  |          |

| PPG timer 0                                                       | Δ                  | #25    | 19н     | FFFF98 <sub>H</sub> |               |            |          |

| DTP/ external interrupt - ch.6/ ch.7 detected UART3 TX            | Δ                  | #26    | 1Ан     | FFFF94 <sub>H</sub> | ICR07         | 0000B7н*1  |          |

| PPG timer 1                                                       | Δ                  | #27    | 1Вн     | FFFF90 <sub>H</sub> | ICR08         | 0000B8н*1  |          |

| Reload timer 1                                                    | Δ                  | #28    | 1Сн     | FFFF8C <sub>H</sub> | ICHUO         | ООООВОН .  |          |

| PPG timer 2/3/4/5                                                 | 0                  | #29    | 1Dн     | FFFF88 <sub>H</sub> |               |            | ]        |

| Real time watch timer watch timer (sub clock)                     | ×                  | #30    | 1Ен     | FFFF84 <sub>H</sub> | ICR09         | 0000В9н*1  |          |

| Free-run timer overflow/clear                                     | ×                  | #31    | 1Fн     | FFFF80 <sub>H</sub> | ICR10         | 0000BAн *1 |          |

| A/D converter conversion complete                                 | 0                  | #32    | 20н     | FFFF7C <sub>H</sub> |               | JUUUDAH '  |          |

| Sound generator 0/1                                               | ×                  | #33    | 21н     | FFFF78 <sub>H</sub> | ICR11         | 0000BBн*1  |          |

| Time-base timer                                                   | ×                  | #34    | 22н     | FFFF74 <sub>H</sub> | IUNII         | OUUUDDH '  |          |

| UART2 RX                                                          | 0                  | #35    | 23н     | FFFF70 <sub>H</sub> | ICR12         | 0000BCн*1  | <b>↑</b> |

| UART2 TX                                                          | Δ                  | #36    | 24н     | FFFF6C <sub>H</sub> | 101112        | OOOODOH .  | Low      |

### **■ ELECTRICAL CHARACTERISTICS**

### 1. Absolute Maximum Ratings

| Parameter                   | Symbol                     | Rating      |           | Unit | Remarks                          |  |  |

|-----------------------------|----------------------------|-------------|-----------|------|----------------------------------|--|--|

| Parameter                   | Symbol                     | Min         | Max       | Unit | nemarks                          |  |  |

|                             | Vcc                        | Vss - 0.3   | Vss + 6.0 | ٧    |                                  |  |  |

| Dower oupply voltoge*1      | AVcc                       | Vss - 0.3   | Vss + 6.0 | V    | AVcc = Vcc*2                     |  |  |

| Power supply voltage*1      | AVRH                       | Vss - 0.3   | Vss + 6.0 | V    | AVcc ≥ AVRH*2                    |  |  |

|                             | DVcc                       | Vss - 0.3   | Vss + 6.0 | V    | DVcc = Vcc*2                     |  |  |

| Input voltage*1             | Vı                         | Vss - 0.3   | Vcc + 0.3 | V    | *3                               |  |  |

| Output voltage*1            | Vo                         | Vss - 0.3   | Vcc + 0.3 | V    |                                  |  |  |

| Maximum clamp current       | ICLAMP                     | - 4         | + 4       | mA   | *7                               |  |  |

| Total maximum clamp current | Σ   ICLAMP                 | _           | 40        | mA   | *7                               |  |  |

| "L" level maximum           | l <sub>OL1</sub>           | _           | 15        | mA   | Except P70 to P77 and P80 to P87 |  |  |

| output current*4            | lol2                       | _           | 40        | mA   | P70 to P77 and P80 to P87        |  |  |

| "L" level average output    | lolav1                     | _           | 4         | mA   | Except P70 to P77 and P80 to P87 |  |  |

| current*5                   | lolav2                     |             | 30        | mA   | P70 to P77 and P80 to P87        |  |  |

| "L" level maximum           | $\Sigma l_{OL1}$           |             | 100       | mA   | Except P70 to P77 and P80 to P87 |  |  |

| total output current        | $\Sigma I_{OL2}$           |             | 330       | mA   | P70 to P77 and P80 to P87        |  |  |

| "L" level average total     | $\Sigma$ lolav1            |             | 50        | mA   | Except P70 to P77 and P80 to P87 |  |  |

| output current              | $\Sigma I_{OLAV2}$         |             | 250       | mA   | P70 to P77 and P80 to P87        |  |  |

| "H" level maximum           | <b>І</b> он1*4             |             | -15       | mA   | Except P70 to P77 and P80 to P87 |  |  |

| output current              | <b>І</b> он2 <sup>*4</sup> |             | -40       | mA   | P70 to P77 and P80 to P87        |  |  |

| "H" level average           | OHAV1*5                    | _           | -4        | mA   | Except P70 to P77 and P80 to P87 |  |  |

| output current              | OHAV2*5                    |             | -30       | mA   | P70 to P77 and P80 to P87        |  |  |

| "H" level maximum           | $\Sigma$ loh1              |             | -100      | mA   | Except P70 to P77 and P80 to P87 |  |  |

| total output current        | $\Sigma$ loh2              |             | -330      | mA   | P70 to P77 and P80 to P87        |  |  |

| "H" level average total     | Σ <b>Ι</b> ΟΗΑV1*6         |             | -50       | mA   | Except P70 to P77 and P80 to P87 |  |  |

| output current              | Σ <b>Ι</b> ΟΗΑV2*6         |             | -250      | mA   | P70 to P77 and P80 to P87        |  |  |

| Power consumption           | Po                         |             | 625       | mW   |                                  |  |  |

| Operating temperature       | TA                         | <b>- 40</b> | + 105     | °C   |                                  |  |  |

| Storage temperature         | Тѕтс                       | - 55        | + 150     | °C   |                                  |  |  |

<sup>\*1 :</sup> The parameter is based on  $V_{\text{SS}} = AV_{\text{SS}} = DV_{\text{SS}} = 0.0 \text{ V}.$

<sup>\*2 :</sup> AVcc, AVRH must not exceed Vcc, and AVRH must not exceed AVcc.

When using an evaluation product, DVcc must not exceed Vcc (however, DVcc can be set to a higher voltage than Vcc when using a Flash memory product).

<sup>\*3 :</sup> If the input current or the maximum input current is limited using external components, Iclamp is the applicable rating instead of Vi.

<sup>\*4 :</sup> Maximum output current is defined as the peak value of current through any one of the corresponding pins.

(Continued)

### • Guaranteed PLL Operation Range

Internal operating clock frequency vs. Power supply voltage

Power supply voltage Vcc (V)

Range of warranted PLL operation

Namal operating range

Internal clock fcp (MHz)

Notes: • For PLL  $1 \times \text{only}$ , use with tcp = 4 MHz or greater.

• Refer to "5. A/D Converter (1) Electrical Characteristics" for details on the A/D converter operating frequency.

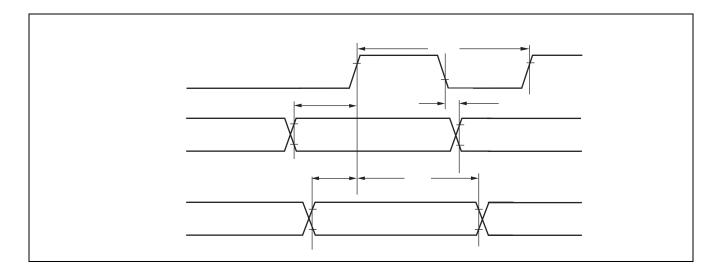

### • Bit setting: ESCR0/1/2/3:SCES=1, ECCR0/1/2/3:SCDE=1

$(Vcc = 5.0 V \pm 10\%, Vss = AVss = 0.0 V, T_A = -40 °C to +105 °C)$

| Parameter                                      | Symbol          | Pin name                      | Conditions                                           | Val        | Unit |       |

|------------------------------------------------|-----------------|-------------------------------|------------------------------------------------------|------------|------|-------|

| Parameter                                      | Symbol Fin hame |                               | Conditions                                           | Min        | Max  | Oilit |

| Serial clock cycle time                        | tscyc           | SCK0 to SCK3                  |                                                      | 5 tcp      | _    | ns    |

| $SCK \downarrow \to SOT$ delay time            | <b>t</b> sLOVI  | SCK0 to SCK3,<br>SOT0 to SOT3 | Internal shift clock                                 | - 50       | + 50 | ns    |

| Valid SIN $ ightarrow$ SCK $\downarrow$        | tıvsнı          | SCK0 to SCK3,                 | mode output pin $C_L = 80 \text{ pF} + 1 \text{TTL}$ | tcp + 80   |      | ns    |

| $SCK \uparrow \rightarrow valid SIN hold time$ | tshixi          | SIN0 to SIN3                  |                                                      | 0          |      | ns    |

| SOT 	o SCK 	op delay time                      | tsovнı          | SCK0 to SCK3,<br>SOT0 to SOT3 |                                                      | 3 tcp - 70 | _    | ns    |

Notes: • Depending on the machine clock frequency to be used, the maximum baud rate may be limited by some parameters. These parameters are shown in "MB90920 series hardware manual".

- C<sub>L</sub> is the load capacitance connected to the pin during testing.

- tcp is the internal operating clock cycle time. Refer to "(1) Clock timing".

### 5. A/D Converter

### (1) Electrical Characteristics

(Vcc = AVcc = AVRH = 4.0 V to 5.5 V, Vss = AVss = 0.0 V,  $T_A = -40$  °C to +105 °C)

| Parameter                        | Symbol           | Pin name   | Value             |                   |                   | Unit | Domostro                           |

|----------------------------------|------------------|------------|-------------------|-------------------|-------------------|------|------------------------------------|

|                                  |                  |            | Min               | Тур               | Max               | Unit | Remarks                            |

| Resolution                       | _                |            |                   | _                 | 10                | bit  |                                    |

| Total error                      | _                | _          | - 3.0             | _                 | + 3.0             | LSB  |                                    |

| Non-linear error                 | _                | _          | - 2.5             | _                 | + 2.5             | LSB  |                                    |

| Differential linear error        | _                | _          | <b>– 1.9</b>      | _                 | + 1.9             | LSB  |                                    |

| Zero transition voltage          | Vот              | AN0 to AN7 | AVss –<br>1.5 LSB | AVss +<br>0.5 LSB | AVss +<br>2.5 LSB | V    | 1 LSB =<br>(AVRH – AVss) /<br>1024 |

| Full scale transition voltage    | V <sub>FST</sub> | AN0 to AN7 | AVRH –<br>3.5 LSB | AVRH –<br>1.5 LSB | AVRH +<br>0.5 LSB | V    |                                    |

| Sampling time                    | tsмр             | _          | 0.4               | _                 | 16500             | μs   | 4.5 V ≤ AVcc ≤ 5.5 V               |

|                                  |                  |            | 1.0               |                   |                   |      | 4.0 V ≤ AVcc ≤ 4.5 V               |

| Compare time                     | tсмр             | _          | 0.66              |                   |                   | μs   | 4.5 V ≤ AVcc ≤ 5.5 V               |

|                                  |                  |            | 2.2               |                   |                   |      | 4.0 V ≤ AVcc ≤ 4.5 V               |

| A/D conversion time              | tcnv             | _          | 1.44              |                   | _                 | μs   | *1                                 |

| Analog port input current        | lain             | AN0 to AN7 | - 0.3             | _                 | + 10              | μА   |                                    |

| Analog input voltage             | Vain             | AN0 to AN7 | 0                 | _                 | AVRH              | V    |                                    |

| Reference voltage                | AV+              | AVRH       | AVss + 2.7        | _                 | AVcc              | V    |                                    |

| Power supply current             | lΑ               | AVcc       | _                 | 2.3               | 6.0               | mA   |                                    |

|                                  | Іан              |            | _                 | _                 | 5                 | μΑ   | *2                                 |

| Reference voltage supply current | IR               | AVRH       | _                 | 520               | 900               | μΑ   | Vavrh = 5.0 V                      |

|                                  | IRH              |            |                   |                   | 5                 | μΑ   | *2                                 |

| Inter-channel variation          | _                | AN0 to AN7 |                   |                   | 4                 | LSB  |                                    |

<sup>\*1 :</sup> The time per channel (4.5 V  $\leq$  AVcc  $\leq$  5.5 V, and internal operating frequency = 32 MHz) .

<sup>\*2 :</sup> Defined as supply current (when  $V_{CC} = AV_{CC} = AV_{CC}$

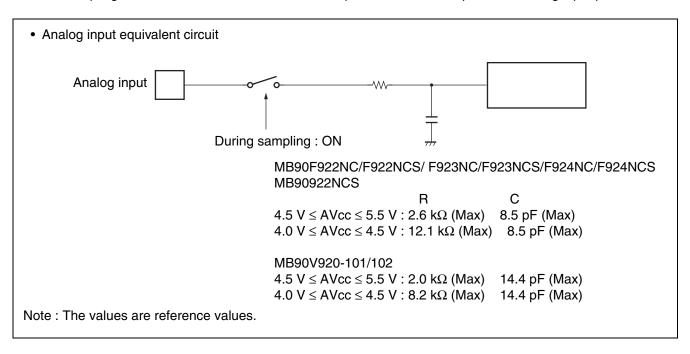

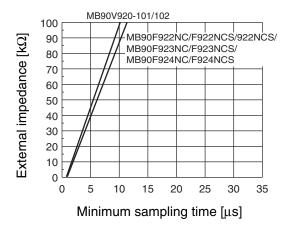

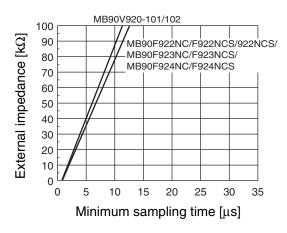

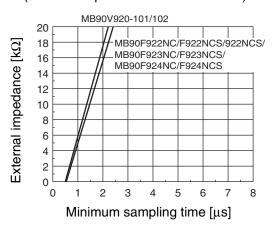

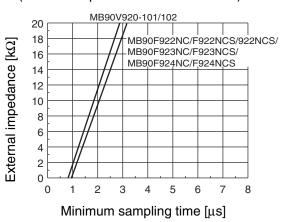

#### • Notes on the external impedance and sampling time of analog inputs

A/D converter with sample and hold circuit. If the external impedance is too high to keep sufficient sampling time, the analog voltage charged to the internal sample and hold capacitor is insufficient, adversely affecting A/D conversion precision. Therefore, to satisfy the A/D conversion precision standard, consider the relationship between the external impedance and minimum sampling time and either adjust the register value and operating frequency or decrease the external impedance so that the sampling time is longer than the minimum value. If the sampling time is still not sufficient, connect a capacitor of about 0.1  $\mu$ F to the analog input pin.

- The relationship between the external impedance and minimum sampling time

- At 4.5 V ≤ AVcc ≤ 5.5 V

(External impedance =  $0 \text{ k}\Omega$  to  $100 \text{ k}\Omega$ )

• At  $4.0 \text{ V} \leq \text{AVcc} \leq 4.5 \text{ V}$

(External impedance =  $0 \text{ k}\Omega$  to  $100 \text{ k}\Omega$ )

(External impedance =  $0 \text{ k}\Omega$  to  $20 \text{ k}\Omega$ )

(External impedance =  $0 \text{ k}\Omega$  to  $20 \text{ k}\Omega$ )

About errors

As |AVRH - AVss| becomes smaller, the relative errors grow larger.

## **FUJITSU SEMICONDUCTOR LIMITED**

Nomura Fudosan Shin-yokohama Bldg. 10-23, Shin-yokohama 2-Chome, Kohoku-ku Yokohama Kanagawa 222-0033, Japan

Tel: +81-45-415-5858 http://jp.fujitsu.com/fsl/en/

For further information please contact:

#### **North and South America**

FUJITSU SEMICONDUCTOR AMERICA, INC. 1250 E. Arques Avenue, M/S 333 Sunnyvale, CA 94085-5401, U.S.A. Tel: +1-408-737-5600 Fax: +1-408-737-5999 http://us.fujitsu.com/micro/

#### **Europe**

FUJITSU SEMICONDUCTOR EUROPE GmbH Pittlerstrasse 47, 63225 Langen, Germany Tel: +49-6103-690-0 Fax: +49-6103-690-122 http://emea.fujitsu.com/semiconductor/

#### Korea

FUJITSU SEMICONDUCTOR KOREA LTD. 206 Kosmo Tower Building, 1002 Daechi-Dong, Gangnam-Gu, Seoul 135-280, Republic of Korea Tel: +82-2-3484-7100 Fax: +82-2-3484-7111 http://kr.fujitsu.com/fmk/

#### **Asia Pacific**

FUJITSU SEMICONDUCTOR ASIA PTE. LTD.

151 Lorong Chuan,

#05-08 New Tech Park 556741 Singapore

Tel: +65-6281-0770 Fax: +65-6281-0220

http://www.fujitsu.com/sg/services/micro/semiconductor/

FUJITSU SEMICONDUCTOR SHANGHAI CO., LTD. Rm. 3102, Bund Center, No.222 Yan An Road (E), Shanghai 200002, China

Tel: +86-21-6146-3688 Fax: +86-21-6335-1605

http://cn.fujitsu.com/fss/

FUJITSU SEMICONDUCTOR PACIFIC ASIA LTD. 10/F., World Commerce Centre, 11 Canton Road, Tsimshatsui, Kowloon, Hong Kong

Tel: +852-2377-0226 Fax: +852-2376-3269

http://cn.fujitsu.com/fsp/

Specifications are subject to change without notice. For further information please contact each office.

#### All Rights Reserved.

The contents of this document are subject to change without notice.

Customers are advised to consult with sales representatives before ordering.

The information, such as descriptions of function and application circuit examples, in this document are presented solely for the purpose of reference to show examples of operations and uses of FUJITSU SEMICONDUCTOR device; FUJITSU SEMICONDUCTOR does not warrant proper operation of the device with respect to use based on such information. When you develop equipment incorporating the device based on such information, you must assume any responsibility arising out of such use of the information.

FUJITSU SEMICONDUCTOR assumes no liability for any damages whatsoever arising out of the use of the information.

Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of FUJITSU SEMICONDUCTOR or any third party or does FUJITSU SEMICONDUCTOR warrant non-infringement of any third-party's intellectual property right or other right by using such information. FUJITSU SEMICONDUCTOR assumes no liability for any infringement of the intellectual property rights or other rights of third parties which would result from the use of information contained herein.

The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that FUJITSU SEMICONDUCTOR will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

Exportation/release of any products described in this document may require necessary procedures in accordance with the regulations of the Foreign Exchange and Foreign Trade Control Law of Japan and/or US export control laws.

The company names and brand names herein are the trademarks or registered trademarks of their respective owners.

Edited: Sales Promotion Department