Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                         |

| Number of I/O              | 18                                                                       |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 64 × 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 20-VFQFN Exposed Pad                                                     |

| Supplier Device Package    | 20-QFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f631-e-ml |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Device    | Program<br>Memory | Data N          | lemory            |    | Comparators | Timers      | SSP      | ECCP+ | EUSART |        |

|-----------|-------------------|-----------------|-------------------|----|-------------|-------------|----------|-------|--------|--------|

| Device    | Flash<br>(words)  | SRAM<br>(bytes) | EEPROM<br>(bytes) |    | (ch)        | Comparators | 8/16-bit | 556   | LUUPT  | EUSARI |

| PIC16F631 | 1024              | 64              | 128               | 18 | —           | 2           | 1/1      | No    | No     | No     |

| PIC16F677 | 2048              | 128             | 256               | 18 | 12          | 2           | 1/1      | Yes   | No     | No     |

| PIC16F685 | 4096              | 256             | 256               | 18 | 12          | 2           | 2/1      | No    | Yes    | No     |

| PIC16F687 | 2048              | 128             | 256               | 18 | 12          | 2           | 1/1      | Yes   | No     | Yes    |

| PIC16F689 | 4096              | 256             | 256               | 18 | 12          | 2           | 1/1      | Yes   | No     | Yes    |

| PIC16F690 | 4096              | 256             | 256               | 18 | 12          | 2           | 2/1      | Yes   | Yes    | Yes    |

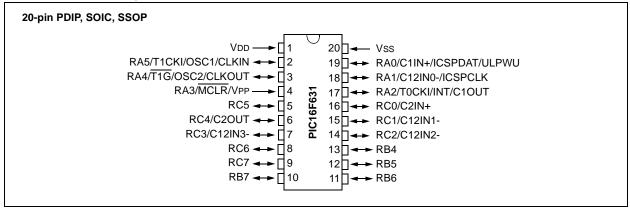

### PIC16F631 Pin Diagram

#### TABLE 1: PIC16F631 PIN SUMMARY

| I/O | Pin | Analog    | Comparators | Timers | Interrupt | Pull-up | Basic       |

|-----|-----|-----------|-------------|--------|-----------|---------|-------------|

| RA0 | 19  | AN0/ULPWU | C1IN+       | —      | IOC       | Y       | ICSPDAT     |

| RA1 | 18  | AN1       | C12IN0-     |        | IOC       | Y       | ICSPCLK     |

| RA2 | 17  | _         | C1OUT       | T0CKI  | IOC/INT   | Y       | —           |

| RA3 | 4   | —         | —           | —      | IOC       | Y(1)    | MCLR/Vpp    |

| RA4 | 3   | —         | —           | T1G    | IOC       | Y       | OSC2/CLKOUT |

| RA5 | 2   |           | —           | T1CKI  | IOC       | Y       | OSC1/CLKIN  |

| RB4 | 13  |           | —           | —      | IOC       | Y       | —           |

| RB5 | 12  | —         | —           | —      | IOC       | Y       | —           |

| RB6 | 11  | —         | —           | —      | IOC       | Y       | —           |

| RB7 | 10  |           | —           | _      | IOC       | Y       | —           |

| RC0 | 16  | AN4       | C2IN+       | —      | _         | —       | —           |

| RC1 | 15  | AN5       | C12IN1-     | _      |           |         | —           |

| RC2 | 14  | AN6       | C12IN2-     | —      |           | _       | —           |

| RC3 | 7   | AN7       | C12IN3-     |        |           |         | —           |

| RC4 | 6   |           | C2OUT       | —      |           |         | —           |

| RC5 | 5   |           | —           |        |           |         | —           |

| RC6 | 8   | —         |             | —      | _         | —       | —           |

| RC7 | 9   |           |             |        |           | _       | —           |

| —   | 1   |           |             | _      |           | _       | Vdd         |

| —   | 20  | _         |             | _      |           | _       | Vss         |

**Note 1:** Pull-up enabled only with external MCLR configuration.

| Name            | Function | Input<br>Type | Output<br>Type | Description                                                                                        |

|-----------------|----------|---------------|----------------|----------------------------------------------------------------------------------------------------|

| RB7             | RB7      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-change.<br>Individually enabled pull-up. |

| RC0/AN4/C2IN+   | RC0      | ST            | CMOS           | General purpose I/O.                                                                               |

|                 | AN4      | AN            | —              | A/D Channel 4 input.                                                                               |

|                 | C2IN+    | AN            | —              | Comparator C2 non-inverting input.                                                                 |

| RC1/AN5/C12IN1- | RC1      | ST            | CMOS           | General purpose I/O.                                                                               |

|                 | AN5      | AN            | —              | A/D Channel 5 input.                                                                               |

|                 | C12IN1-  | AN            | —              | Comparator C1 or C2 inverting input.                                                               |

| RC2/AN6/C12IN2- | RC2      | ST            | CMOS           | General purpose I/O.                                                                               |

|                 | AN6      | AN            | —              | A/D Channel 6 input.                                                                               |

|                 | C12IN2-  | AN            | —              | Comparator C1 or C2 inverting input.                                                               |

| RC3/AN7/C12IN3- | RC3      | ST            | CMOS           | General purpose I/O.                                                                               |

|                 | AN7      | AN            | —              | A/D Channel 7 input.                                                                               |

|                 | C12IN3-  | AN            | —              | Comparator C1 or C2 inverting input.                                                               |

| RC4/C2OUT       | RC4      | ST            | CMOS           | General purpose I/O.                                                                               |

|                 | C2OUT    | —             | CMOS           | Comparator C2 output.                                                                              |

| RC5             | RC5      | ST            | CMOS           | General purpose I/O.                                                                               |

| RC6/AN8/SS      | RC6      | ST            | CMOS           | General purpose I/O.                                                                               |

|                 | AN8      | AN            | —              | A/D Channel 8 input.                                                                               |

|                 | SS       | ST            | —              | Slave Select input.                                                                                |

| RC7/AN9/SDO     | RC7      | ST            | CMOS           | General purpose I/O.                                                                               |

|                 | AN9      | AN            | —              | A/D Channel 9 input.                                                                               |

|                 | SDO      | —             | CMOS           | SPI data output.                                                                                   |

| Vss             | Vss      | Power         | _              | Ground reference.                                                                                  |

| Vdd             | Vdd      | Power         | _              | Positive supply.                                                                                   |

#### TABLE 1-2: PINOUT DESCRIPTION – PIC16F677 (CONTINUED)

**Legend:** AN = Analog input or output

TTL = TTL compatible input

HV = High Voltage

XTAL= Crystal

CMOS=CMOS compatible input or output

ST= Schmitt Trigger input with CMOS levels

|                                       | File<br>Address |                                                   | File<br>Address |                                       | File          |                                             | File<br>Address |

|---------------------------------------|-----------------|---------------------------------------------------|-----------------|---------------------------------------|---------------|---------------------------------------------|-----------------|

| La dia a stata data (1)               | -               | la dina at a dala (1)                             | 1               | lucations et a statu (1)              | Address       | la dina sé a dala (1)                       |                 |

| Indirect addr. <sup>(1)</sup><br>TMR0 | 00h             | Indirect addr. <sup>(1)</sup><br>OPTION REG       | 80h             | Indirect addr. <sup>(1)</sup><br>TMR0 | 100h          | Indirect addr. <sup>(1)</sup><br>OPTION_REG | 180h            |

| PCL                                   | 01h             |                                                   | 81h             |                                       | 101h          |                                             | 181h            |

|                                       | 02h             | PCL                                               | 82h             | PCL                                   | 102h          | PCL                                         | 182h            |

| STATUS                                | 03h             | STATUS                                            | 83h             | STATUS                                | 103h          | STATUS                                      | 183h            |

| FSR                                   | 04h             | FSR                                               | 84h             | FSR                                   | 104h          | FSR                                         | 184h            |

| PORTA                                 | 05h             | TRISA                                             | 85h             | PORTA                                 | 105h          | TRISA                                       | 185h            |

| PORTB<br>PORTC                        | 06h<br>07h      | TRISB<br>TRISC                                    | 86h<br>87h      | PORTB<br>PORTC                        | 106h<br>107h  | TRISB<br>TRISC                              | 186h<br>187h    |

| FURIC                                 | 0711<br>08h     | TRISC                                             | 88h             | FURIC                                 | 10711<br>108h | TRISC                                       | 188h            |

|                                       |                 |                                                   | 89h             |                                       |               |                                             | 189h            |

| PCLATH                                | 09h             | PCLATH                                            |                 | PCLATH                                | 109h<br>104b  | PCLATH                                      | 18Ah            |

| INTCON                                | 0Ah             | INTCON                                            | 8Ah<br>8Bh      | INTCON                                | 10Ah<br>10Bh  | INTCON                                      | 18Bh            |

| PIR1                                  | 0Bh             |                                                   |                 |                                       | 10Bh<br>10Ch  |                                             |                 |

|                                       | 0Ch             | PIE1                                              | 8Ch             | EEDAT                                 | 10Ch          | EECON1                                      | 18Ch            |

| PIR2                                  | 0Dh             | PIE2                                              | 8Dh             | EEADR                                 | 10Dh          | EECON2 <sup>(1)</sup>                       | 18Dh            |

| TMR1L                                 | 0Eh             | PCON                                              | 8Eh             |                                       | 10Eh          |                                             | 18Eh            |

| TMR1H                                 | 0Fh             | OSCCON                                            | 8Fh             |                                       | 10Fh          |                                             | 18Fh            |

| T1CON                                 | 10h             | OSCTUNE                                           | 90h             |                                       | 110h          |                                             | 190h            |

|                                       | 11h             |                                                   | 91h             |                                       | 111h          |                                             | 191h            |

| 0000115                               | 12h             | 000400(2)                                         | 92h             |                                       | 112h          |                                             | 192h            |

| SSPBUF                                | 13h             | SSPADD <sup>(2)</sup>                             | 93h             |                                       | 113h          |                                             | 193h            |

| SSPCON                                | 14h             | SSPSTAT                                           | 94h             |                                       | 114h          |                                             | 194h            |

|                                       | 15h             | WPUA                                              | 95h             | WPUB                                  | 115h          |                                             | 195h            |

|                                       | 16h             | IOCA                                              | 96h             | IOCB                                  | 116h          |                                             | 196h            |

|                                       | 17h             | WDTCON                                            | 97h             |                                       | 117h          |                                             | 197h            |

|                                       | 18h             |                                                   | 98h             | VRCON                                 | 118h          |                                             | 198h            |

|                                       | 19h             |                                                   | 99h             | CM1CON0                               | 119h          |                                             | 199h            |

|                                       | 1Ah             |                                                   | 9Ah             | CM2CON0                               | 11Ah          |                                             | 19Ah            |

|                                       | 1Bh             |                                                   | 9Bh             | CM2CON1                               | 11Bh          |                                             | 19Bh            |

|                                       | 1Ch             |                                                   | 9Ch             |                                       | 11Ch          |                                             | 19Ch            |

|                                       | 1Dh             |                                                   | 9Dh             |                                       | 11Dh          |                                             | 19Dh            |

| ADRESH                                | 1Eh             | ADRESL                                            | 9Eh             | ANSEL                                 | 11Eh          | SRCON                                       | 19Eh            |

| ADCON0                                | 1Fh             | ADCON1                                            | 9Fh             | ANSELH                                | 11Fh          |                                             | 19Fh            |

| Quanta                                | 20h             | General<br>Purpose<br>Register                    | A0h             |                                       | 120h          |                                             | 1A0h            |

| General<br>Purpose<br>Register        |                 | 32 Bytes                                          | BFh<br>C0h      |                                       |               |                                             |                 |

| 96 Bytes                              |                 |                                                   | EFh             |                                       | 16Fh          |                                             | 1EFh            |

|                                       | 7Fh             | accesses<br>70h-7Fh                               | F0h<br>FFh      | accesses<br>70h-7Fh                   | 170h<br>17Fh  | accesses<br>70h-7Fh                         | 1F0h<br>1FFh    |

| Bank 0                                | -               | Bank 1                                            | -               | Bank 2                                |               | Bank 3                                      |                 |

| Note 1: Not a                         | physical re     | data memory locat<br>gister.<br>o accesses the SS |                 |                                       | under certa   | in conditions.                              |                 |

#### FIGURE 2-5: PIC16F677 SPECIAL FUNCTION REGISTERS

| GURE 2-7:                              | File                       | F687/PIC16F68                                          | File              |                                                          |               |                       | File         |

|----------------------------------------|----------------------------|--------------------------------------------------------|-------------------|----------------------------------------------------------|---------------|-----------------------|--------------|

|                                        |                            |                                                        |                   |                                                          | File          |                       | File         |

| Indirect addr. (1)                     | Address                    | ladias et e dela (1)                                   | Address           | ladias et e dala (1)                                     | Address       | Indinent ender (1)    | Addres       |

|                                        |                            | Indirect addr. <sup>(1)</sup>                          |                   | Indirect addr. <sup>(1)</sup>                            |               | Indirect addr. (1)    |              |

| TMR0<br>PCL                            | 01h                        | OPTION_REG<br>PCL                                      | 81h<br>82b        | TMR0<br>PCL                                              | 101h<br>102h  | OPTION_REG<br>PCL     | 181h         |

| STATUS                                 | 02h<br>03h                 | STATUS                                                 | 82h<br>83h        | STATUS                                                   | 102h<br>103h  | STATUS                | 182h<br>183h |

| FSR                                    | -                          | FSR                                                    |                   | FSR                                                      |               | FSR                   |              |

|                                        | 04h                        |                                                        | 84h               | PORTA                                                    | 104h<br>105h  |                       | 184h         |

| PORTA<br>PORTB                         | 05h<br>06h                 | TRISA<br>TRISB                                         | 85h<br>86h        | PORTA                                                    | 105h<br>106h  | TRISA<br>TRISB        | 185h<br>186h |

| PORTE                                  | 00n<br>07h                 | TRISE                                                  | 87h               | PORTE                                                    | 106h<br>107h  | TRISE                 | 187h         |

| FURIC                                  | 08h                        | TRIBC                                                  | 88h               | FORTC                                                    | 107h<br>108h  | TRISC                 | 188h         |

|                                        | 09h                        |                                                        | 89h               |                                                          | 109h          |                       | 189h         |

| PCLATH                                 | 0Ah                        | PCLATH                                                 | 8Ah               | PCLATH                                                   | 10911<br>10Ah | PCLATH                | 18Ah         |

| INTCON                                 | 0Bh                        | INTCON                                                 | 8Bh               | INTCON                                                   | 10An<br>10Bh  | INTCON                | 18Bh         |

| PIR1                                   | 0Ch                        | PIE1                                                   | 8Ch               | EEDAT                                                    | 10Dh          | EECON1                | 18Ch         |

|                                        | -                          |                                                        |                   |                                                          |               | EECON2 <sup>(1)</sup> |              |

| PIR2                                   | 0Dh                        | PIE2                                                   | 8Dh               | EEADR                                                    | 10Dh          | EECONZY               | 18Dh         |

| TMR1L                                  | 0Eh                        | PCON                                                   | 8Eh               | EEDATH <sup>(3)</sup>                                    | 10Eh          |                       | 18Eh         |

| TMR1H                                  | 0Fh                        | OSCCON                                                 | 8Fh               | EEADRH <sup>(3)</sup>                                    | 10Fh          |                       | 18Fh         |

| T1CON                                  | 10h                        | OSCTUNE                                                | 90h               |                                                          | 110h          |                       | 190h         |

|                                        | 11h                        |                                                        | 91h               |                                                          | 111h          |                       | 191h         |

|                                        | 12h                        | (2)                                                    | 92h               |                                                          | 112h          |                       | 192h         |

| SSPBUF                                 | 13h                        | SSPADD <sup>(2)</sup>                                  | 93h               |                                                          | 113h          |                       | 193h         |

| SSPCON                                 | 14h                        | SSPSTAT                                                | 94h               |                                                          | 114h          |                       | 194h         |

|                                        | 15h                        | WPUA                                                   | 95h               | WPUB                                                     | 115h          |                       | 195h         |

|                                        | 16h                        | IOCA                                                   | 96h               | IOCB                                                     | 116h          |                       | 196h         |

|                                        | 17h                        | WDTCON                                                 | 97h               |                                                          | 117h          |                       | 197h         |

| RCSTA                                  | 18h                        | TXSTA                                                  | 98h               | VRCON                                                    | 118h          |                       | 198h         |

| TXREG                                  | 19h                        | SPBRG                                                  | 99h               | CM1CON0                                                  | 119h          |                       | 199h         |

| RCREG                                  | 1Ah                        | SPBRGH                                                 | 9Ah               | CM2CON0                                                  | 11Ah          |                       | 19Ah         |

|                                        | 1Bh                        | BAUDCTL                                                | 9Bh               | CM2CON1                                                  | 11Bh          |                       | 19Bh         |

|                                        | 1Ch                        |                                                        | 9Ch               |                                                          | 11Ch          |                       | 19Ch         |

|                                        | 1Dh                        |                                                        | 9Dh               |                                                          | 11Dh          | 00001                 | 19Dh         |

| ADRESH                                 | 1Eh                        | ADRESL                                                 | 9Eh               | ANSEL                                                    | 11Eh          | SRCON                 | 19Eh         |

| ADCON0                                 | 1Fh                        | ADCON1                                                 | 9Fh               | ANSELH                                                   | 11Fh          |                       | 19Fh         |

| General<br>Purpose<br>Register         | 20h                        | General<br>Purpose<br>Register<br>32 Bytes<br>48 Bytes | A0h<br>BFh<br>C0h | General<br>Purpose<br>Register<br>80 Bytes<br>(PIC16F689 | 120h          |                       | 1A0h         |

| 96 Bytes                               |                            | (PIC16F689<br>only)                                    | EFh               | only)                                                    |               |                       |              |

|                                        | 7Fh                        | accesses<br>70h-7Fh                                    | F0h<br>FFh        | accesses<br>70h-7Fh                                      | 170h<br>17Fh  | accesses<br>70h-7Fh   | 1F0h<br>1FFh |

| Bank 0                                 | 1                          | Bank 1                                                 | I                 | Bank 2                                                   | I             | Bank 3                |              |

| lote 1: Not a p<br>2: Addres<br>See Re | ohysical reg<br>s 93h also | •                                                      | P Mask (SS        | as '0'.<br>SPMSK) register u                             | nder certai   | n conditions.         |              |

#### 2.2.2.6 PIR1 Register

The PIR1 register contains the interrupt flag bits, as shown in Register 2-6.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

## REGISTER 2-6: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

| U-0   | R/W-0               | R-0                 | R-0                 | R/W-0                | R/W-0                 | R/W-0                 | R/W-0  |

|-------|---------------------|---------------------|---------------------|----------------------|-----------------------|-----------------------|--------|

| —     | ADIF <sup>(5)</sup> | RCIF <sup>(3)</sup> | TXIF <sup>(3)</sup> | SSPIF <sup>(4)</sup> | CCP1IF <sup>(2)</sup> | TMR2IF <sup>(1)</sup> | TMR1IF |

| bit 7 |                     |                     |                     |                      |                       |                       | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7 | Unimplemented: Read as '0'                                                                                                                          |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | ADIF: A/D Converter Interrupt Flag bit <sup>(5)</sup>                                                                                               |

|       | <ul> <li>1 = A/D conversion complete (must be cleared in software)</li> <li>0 = A/D conversion has not completed or has not been started</li> </ul> |

| bit 5 | RCIF: EUSART Receive Interrupt Flag bit <sup>(3)</sup>                                                                                              |

|       | <ul> <li>1 = The EUSART receive buffer is full (cleared by reading RCREG)</li> <li>0 = The EUSART receive buffer is not full</li> </ul>             |

| bit 4 | <b>TXIF:</b> EUSART Transmit Interrupt Flag bit <sup>(3)</sup>                                                                                      |

|       | <ul> <li>1 = The EUSART transmit buffer is empty (cleared by writing to TXREG)</li> <li>0 = The EUSART transmit buffer is full</li> </ul>           |

| bit 3 | SSPIF: Synchronous Serial Port (SSP) Interrupt Flag bit <sup>(4)</sup>                                                                              |

|       | <ul> <li>1 = The Transmission/Reception is complete (must be cleared in software)</li> <li>0 = Waiting to Transmit/Receive</li> </ul>               |

| bit 2 | CCP1IF: CCP1 Interrupt Flag bit <sup>(2)</sup>                                                                                                      |

|       | Capture mode:                                                                                                                                       |

|       | <ul> <li>1 = A TMR1 register capture occurred (must be cleared in software)</li> <li>0 = No TMR1 register capture occurred</li> </ul>               |

|       | Compare mode:                                                                                                                                       |

|       | <ul> <li>1 = A TMR1 register compare match occurred (must be cleared in software)</li> <li>0 = No TMR1 register compare match occurred</li> </ul>   |

|       | <u>PWM mode:</u>                                                                                                                                    |

|       | Unused in this mode                                                                                                                                 |

| bit 1 | TMR2IF: Timer2 to PR2 Interrupt Flag bit <sup>(1)</sup>                                                                                             |

|       | <ul> <li>1 = A Timer2 to PR2 match occurred (must be cleared in software)</li> <li>0 = No Timer2 to PR2 match occurred</li> </ul>                   |

| bit 0 | TMR1IF: Timer1 Overflow Interrupt Flag bit                                                                                                          |

|       | <ul> <li>1 = The TMR1 register overflowed (must be cleared in software)</li> <li>0 = The TMR1 register did not overflow</li> </ul>                  |

| Note  | 1: PIC16F685/PIC16F690 only.                                                                                                                        |

|       | 2: PIC16F685/PIC16F689/PIC16F690 only.                                                                                                              |

|       | 3: PIC16F687/PIC16F689/PIC16F690 only.                                                                                                              |

|       | 4: PIC16F677/PIC16F687/PIC16F689/PIC16F690 only.                                                                                                    |

|       | 5: PIC16F677/PIC16F685/PIC16F687/PIC16F689/PIC16F690 only.                                                                                          |

## 3.2 Oscillator Control

The Oscillator Control (OSCCON) register (Figure 3-1) controls the system clock and frequency selection options. The OSCCON register contains the following bits:

- Frequency selection bits (IRCF)

- Frequency Status bits (HTS, LTS)

- System clock control bits (OSTS, SCS)

#### REGISTER 3-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0     | R/W-1 | R/W-1 | R/W-0 | R-1                 | R-0 | R-0 | R/W-0 |

|---------|-------|-------|-------|---------------------|-----|-----|-------|

| —       | IRCF2 | IRCF1 | IRCF0 | OSTS <sup>(1)</sup> | HTS | LTS | SCS   |

| bit 7   |       |       |       |                     |     |     | bit 0 |

|         |       |       |       |                     |     |     |       |

| Legend: |       |       |       |                     |     |     |       |

| Logona.           |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

| bit 7   | Unimplemented: Read as '0'                                                                                                                                                                                                           |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-4 | IRCF<2:0>: Internal Oscillator Frequency Select bits<br>111 = 8 MHz<br>110 = 4 MHz (default)<br>101 = 2 MHz<br>100 = 1 MHz<br>011 = 500 kHz<br>010 = 250 kHz<br>001 = 125 kHz<br>000 = 31 kHz (LFINTOSC)                             |

| bit 3   | <b>OSTS:</b> Oscillator Start-up Time-out Status bit <sup>(1)</sup><br>1 = Device is running from the clock defined by FOSC<2:0> of the CONFIG register<br>0 = Device is running from the internal oscillator (HFINTOSC or LFINTOSC) |

| bit 2   | <ul> <li>HTS: HFINTOSC Status bit (High Frequency – 8 MHz to 125 kHz)</li> <li>1 = HFINTOSC is stable</li> <li>0 = HFINTOSC is not stable</li> </ul>                                                                                 |

| bit 1   | LTS: LFINTOSC Stable bit (Low Frequency – 31 kHz)<br>1 = LFINTOSC is stable<br>0 = LFINTOSC is not stable                                                                                                                            |

| bit 0   | <ul> <li>SCS: System Clock Select bit</li> <li>1 = Internal oscillator is used for system clock</li> <li>0 = Clock source defined by FOSC&lt;2:0&gt; of the CONFIG register</li> </ul>                                               |

| Note 1. | Discrete to (o) with Two Greed Oters up and LD VT or LIC collected on the Opeillater mode on Feil                                                                                                                                    |

**Note 1:** Bit resets to '0' with Two-Speed Start-up and LP, XT or HS selected as the Oscillator mode or Fail-Safe mode is enabled.

### 3.5.3 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is an uncalibrated 31 kHz internal clock source.

The output of the LFINTOSC connects to a postscaler and multiplexer (see Figure 3-1). Select 31 kHz, via software, using the IRCF<2:0> bits of the OSCCON register. See **Section 3.5.4 "Frequency Select Bits (IRCF)**" for more information. The LFINTOSC is also the frequency for the Power-up Timer (PWRT), Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The LFINTOSC is enabled by selecting 31 kHz (IRCF<2:0> bits of the OSCCON register = 000) as the system clock source (SCS bit of the OSCCON register = 1), or when any of the following are enabled:

- Two-Speed Start-up IESO bit of the Configuration Word register = 1 and IRCF<2:0> bits of the OSCCON register = 000

- Power-up Timer (PWRT)

- Watchdog Timer (WDT)

- Fail-Safe Clock Monitor (FSCM)

The LF Internal Oscillator (LTS) bit of the OSCCON register indicates whether the LFINTOSC is stable or not.

#### 3.5.4 FREQUENCY SELECT BITS (IRCF)

The output of the 8 MHz HFINTOSC and 31 kHz LFINTOSC connects to a postscaler and multiplexer (see Figure 3-1). The Internal Oscillator Frequency Select bits IRCF<2:0> of the OSCCON register select the frequency output of the internal oscillators. One of eight frequencies can be selected via software:

- 8 MHz

- 4 MHz (Default after Reset)

- 2 MHz

- 1 MHz

- 500 kHz

- 250 kHz

- 125 kHz

- 31 kHz (LFINTOSC)

| Note: | Following any Reset, the IRCF<2:0> bits  |

|-------|------------------------------------------|

|       | of the OSCCON register are set to '110'  |

|       | and the frequency selection is set to    |

|       | 4 MHz. The user can modify the IRCF bits |

|       | to select a different frequency.         |

### 3.5.5 HFINTOSC AND LFINTOSC CLOCK SWITCH TIMING

When switching between the LFINTOSC and the HFINTOSC, the new oscillator may already be shut down to save power (see Figure 3-6). If this is the case, there is a delay after the IRCF<2:0> bits of the OSCCON register are modified before the frequency selection takes place. The LTS and HTS bits of the OSCCON register will reflect the current active status of the LFINTOSC and HFINTOSC oscillators. The timing of a frequency selection is as follows:

- 1. IRCF<2:0> bits of the OSCCON register are modified.

- 2. If the new clock is shut down, a clock start-up delay is started.

- 3. Clock switch circuitry waits for a falling edge of the current clock.

- 4. CLKOUT is held low and the clock switch circuitry waits for a rising edge in the new clock.

- CLKOUT is now connected with the new clock. LTS and HTS bits of the OSCCON register are updated as required.

- 6. Clock switch is complete.

See Figure 3-1 for more details.

If the internal oscillator speed selected is between 8 MHz and 125 kHz, there is no start-up delay before the new frequency is selected. This is because the old and new frequencies are derived from the HFINTOSC via the postscaler and multiplexer.

Start-up delay specifications are located in the oscillator tables of **Section 17.0** "**Electrical Specifications**".

#### 3.7.3 CHECKING TWO-SPEED CLOCK STATUS

Checking the state of the OSTS bit of the OSCCON register will confirm if the microcontroller is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Word register (CONFIG), or the internal oscillator.

| FIGURE 3-7:     | TWO-SPEED START-UP |        |

|-----------------|--------------------|--------|

| HFINTOSC /      |                    |        |

| OSC1            | ←Tost              |        |

| OSC2            |                    |        |

| Program Counter | PC - N 5 PC        | PC + 1 |

| System Clock    |                    |        |

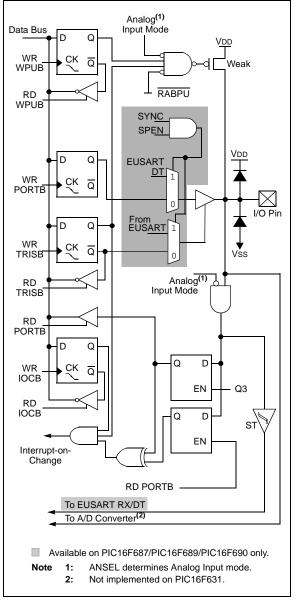

## 4.4.3.2 RB5/AN11/RX/DT<sup>(1, 2)</sup>

Figure 4-8 shows the diagram for this pin. The RB5/ AN11/RX/DT pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC (except PIC16F631)

- an asynchronous serial input

- a synchronous serial data I/O

Note 1: RX and DT are available on PIC16F687/ PIC16F689/PIC16F690 only.

2: AN11 is not implemented on PIC16F631.

#### FIGURE 4-8:

#### **BLOCK DIAGRAM OF RB5**

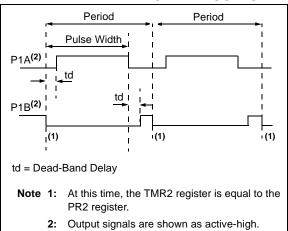

#### 11.4.6 PROGRAMMABLE DEAD-BAND DELAY MODE

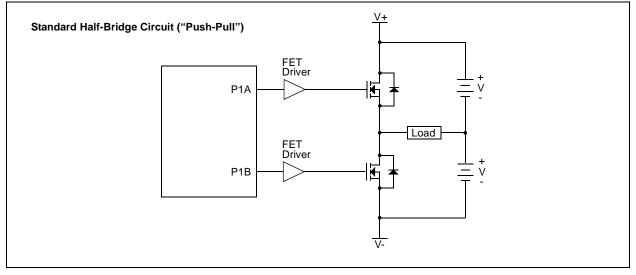

In Half-Bridge applications where all power switches are modulated at the PWM frequency, the power switches normally require more time to turn off than to turn on. If both the upper and lower power switches are switched at the same time (one turned on, and the other turned off), both switches may be on for a short period of time until one switch completely turns off. During this brief interval, a very high current (*shoot-through current*) will flow through both power switches, shorting the bridge supply. To avoid this potentially destructive shoot-through current from flowing during switching, turning on either of the power switches is normally delayed to allow the other switch to completely turn off.

In Half-Bridge mode, a digitally programmable deadband delay is available to avoid shoot-through current from destroying the bridge power switches. The delay occurs at the signal transition from the non-active state to the active state. See Figure 11-8 for illustration. The lower seven bits of the associated PWM1CON register (Register 11-3) sets the delay period in terms of microcontroller instruction cycles (TcY or 4 Tosc).

#### FIGURE 11-17: EXAMPLE OF HALF-BRIDGE PWM OUTPUT

### FIGURE 11-18: EXAMPLE OF HALF-BRIDGE APPLICATIONS

### 11.4.7 PULSE STEERING MODE

In Single Output mode, pulse steering allows any of the PWM pins to be the modulated signal. Additionally, the same PWM signal can be simultaneously available on multiple pins.

Once the Single Output mode is selected (CCP1M<3:2> = 11 and P1M<1:0> = 00 of the CCP1CON register), the user firmware can bring out the same PWM signal to one, two, three or four output pins by setting the appropriate STR<D:A> bits of the PSTRCON register, as shown in Figure 11-19.

Note: The associated TRIS bits must be set to output ('0') to enable the pin output driver in order to see the PWM signal on the pin.

While the PWM Steering mode is active, CCP1M<1:0> bits of the CCP1CON register select the PWM output polarity for the P1<D:A> pins.

The PWM auto-shutdown operation also applies to PWM Steering mode as described in **Section 11.4.4** "**Enhanced PWM Auto-shutdown mode**". An autoshutdown event will only affect pins that have PWM outputs enabled.

## **REGISTER 11-4: PSTRCON: PULSE STEERING CONTROL REGISTER<sup>(1)</sup>**

| U-0          | U-0          | U-0                                                                                  | R/W-0    | R/W-0            | R/W-0            | R/W-0           | R/W-1 |  |  |  |  |

|--------------|--------------|--------------------------------------------------------------------------------------|----------|------------------|------------------|-----------------|-------|--|--|--|--|

| _            | _            | —                                                                                    | STRSYNC  | STRD             | STRC             | STRB            | STRA  |  |  |  |  |

| bit 7        | ·            |                                                                                      |          |                  |                  |                 | bit ( |  |  |  |  |

| Legend:      |              |                                                                                      |          |                  |                  |                 |       |  |  |  |  |

| R = Readab   | ole bit      | W = Writable                                                                         | bit      | U = Unimpler     | nented bit, read | l as '0'        |       |  |  |  |  |

| -n = Value a | at POR       | '1' = Bit is se                                                                      | t        | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |  |  |  |  |

|              |              |                                                                                      |          |                  |                  |                 |       |  |  |  |  |

| bit 7-5      | Unimpleme    | nted: Read as                                                                        | '0'      |                  |                  |                 |       |  |  |  |  |

| bit 4        | STRSYNC:     | Steering Sync I                                                                      | pit      |                  |                  |                 |       |  |  |  |  |

|              | 1 = Output s | 1 = Output steering update occurs on next PWM period                                 |          |                  |                  |                 |       |  |  |  |  |

|              | 0 = Output s | 0 = Output steering update occurs at the beginning of the instruction cycle boundary |          |                  |                  |                 |       |  |  |  |  |

| bit 3        | STRD: Stee   | ring Enable bit                                                                      | D        |                  |                  |                 |       |  |  |  |  |

|              |              | 1 = P1D pin has the PWM waveform with polarity control from CCP1M<1:0>               |          |                  |                  |                 |       |  |  |  |  |

|              | 0 = P1D pin  | 0 = P1D pin is assigned to port pin                                                  |          |                  |                  |                 |       |  |  |  |  |

| bit 2        | STRC: Stee   | STRC: Steering Enable bit C                                                          |          |                  |                  |                 |       |  |  |  |  |

|              | 1 = P1C pin  | 1 = P1C pin has the PWM waveform with polarity control from CCP1M<1:0>               |          |                  |                  |                 |       |  |  |  |  |

|              | 0 = P1C pin  | 0 = P1C pin is assigned to port pin                                                  |          |                  |                  |                 |       |  |  |  |  |

| bit 1        |              | STRB: Steering Enable bit B                                                          |          |                  |                  |                 |       |  |  |  |  |

|              | 1 = P1B pin  | 1 = P1B pin has the PWM waveform with polarity control from CCP1M<1:0>               |          |                  |                  |                 |       |  |  |  |  |

|              | 0 = P1B pin  | 0 = P1B pin is assigned to port pin                                                  |          |                  |                  |                 |       |  |  |  |  |

| bit 0        | STRA: Stee   | STRA: Steering Enable bit A                                                          |          |                  |                  |                 |       |  |  |  |  |

|              | 1 = P1A pin  | 1 = P1A pin has the PWM waveform with polarity control from CCP1M<1:0>               |          |                  |                  |                 |       |  |  |  |  |

|              | 0 = P1A pin  | is assigned to                                                                       | port pin |                  |                  |                 |       |  |  |  |  |

Note 1: The PWM Steering mode is available only when the CCP1CON register bits CCP1M<3:2> = 11 and P1M<1:0> = 00.

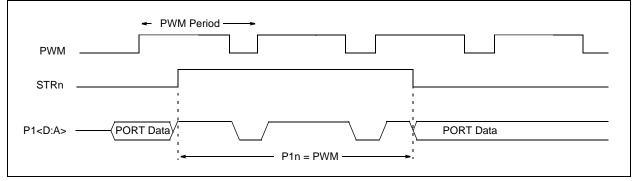

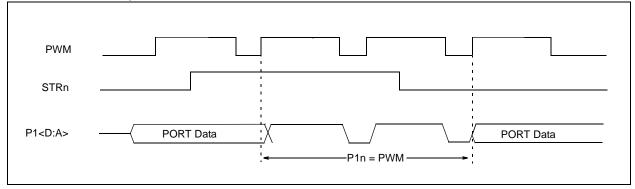

## 11.4.7.1 Steering Synchronization

The STRSYNC bit of the PSTRCON register gives the user two selections of when the steering event will happen. When the STRSYNC bit is '0', the steering event will happen at the end of the instruction that writes to the PSTRCON register. In this case, the output signal at the P1<D:A> pins may be an incomplete PWM waveform. This operation is useful when the user firmware needs to immediately remove a PWM signal from the pin.

When the STRSYNC bit is '1', the effective steering update will happen at the beginning of the next PWM period. In this case, steering on/off the PWM output will always produce a complete PWM waveform. Figures 11-20 and 11-21 illustrate the timing diagrams of the PWM steering depending on the STRSYNC setting.

## FIGURE 11-20: EXAMPLE OF STEERING EVENT AT END OF INSTRUCTION (STRSYNC = 0)

#### FIGURE 11-21: EXAMPLE OF STEERING EVENT AT BEGINNING OF INSTRUCTION (STRSYNC = 1)

| Name    | Bit 7                                                                                                | Bit 6      | Bit 5       | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|------------------------------------------------------------------------------------------------------|------------|-------------|--------|-------|--------|--------|--------|----------------------|---------------------------------|

| BAUDCTL | ABDOVF                                                                                               | RCIDL      | —           | SCKP   | BRG16 | _      | WUE    | ABDEN  | 01-0 0-00            | 01-0 0-00                       |

| INTCON  | GIE                                                                                                  | PEIE       | TOIE        | INTE   | RABIE | T0IF   | INTF   | RABIF  | x000 000x            | 0000 000x                       |

| PIE1    | —                                                                                                    | ADIE       | RCIE        | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | -000 0000            | -000 0000                       |

| PIR1    | —                                                                                                    | ADIF       | RCIF        | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | -000 0000            | -000 0000                       |

| RCREG   | EUSART F                                                                                             | Receive Da | ta Register |        |       |        |        |        | 0000 0000            | 0000 0000                       |

| RCSTA   | SPEN                                                                                                 | RX9        | SREN        | CREN   | ADDEN | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| SPBRG   | BRG7                                                                                                 | BRG6       | BRG5        | BRG4   | BRG3  | BRG2   | BRG1   | BRG0   | 0000 0000            | 0000 0000                       |

| SPBRGH  | BRG15                                                                                                | BRG14      | BRG13       | BRG12  | BRG11 | BRG10  | BRG9   | BRG8   | 0000 0000            | 0000 0000                       |

| TRISB   | TRISB7                                                                                               | TRISB6     | TRISB5      | TRISB4 |       |        |        |        | 1111                 | 1111                            |

| TXREG   | EUSART Transmit Data Register                                                                        |            |             |        |       |        |        |        | 0000 0000            | 0000 0000                       |

| TXSTA   | CSRC                                                                                                 | TX9        | TXEN        | SYNC   | SENDB | BRGH   | TRMT   | TX9D   | 0000 0010            | 0000 0010                       |

| Legend: | x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Asynchronous Transmission. |            |             |        |       |        |        |        |                      |                                 |

### TABLE 12-1: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Name    | Bit 7      | Bit 6                                                                                         | Bit 5       | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|------------|-----------------------------------------------------------------------------------------------|-------------|--------|-------|--------|--------|--------|----------------------|---------------------------------|

| BAUDCTL | ABDOVF     | RCIDL                                                                                         | —           | SCKP   | BRG16 | _      | WUE    | ABDEN  | 01-0 0-00            | 01-0 0-00                       |

| INTCON  | GIE        | PEIE                                                                                          | TOIE        | INTE   | RABIE | T0IF   | INTF   | RABIF  | x000 000x            | 0000 000x                       |

| PIE1    | —          | ADIE                                                                                          | RCIE        | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | -000 0000            | -000 0000                       |

| PIR1    | —          | ADIF                                                                                          | RCIF        | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | -000 0000            | -000 0000                       |

| RCREG   | EUSART F   | Receive Da                                                                                    | ta Register |        |       |        |        |        | 0000 0000            | 0000 0000                       |

| RCSTA   | SPEN       | RX9                                                                                           | SREN        | CREN   | ADDEN | FERR   | OERR   | RX9D   | x000 000x            | 0000 000x                       |

| SPBRG   | BRG7       | BRG6                                                                                          | BRG5        | BRG4   | BRG3  | BRG2   | BRG1   | BRG0   | 0000 0000            | 0000 0000                       |

| SPBRGH  | BRG15      | BRG14                                                                                         | BRG13       | BRG12  | BRG11 | BRG10  | BRG9   | BRG8   | 0000 0000            | 0000 0000                       |

| TRISB   | TRISB7     | TRISB6                                                                                        | TRISB5      | TRISB4 |       |        |        |        | 1111                 | 1111                            |

| TXREG   | EUSART     | EUSART Transmit Data Register                                                                 |             |        |       |        |        |        | 0000 0000            | 0000 0000                       |

| TXSTA   | CSRC       | TX9                                                                                           | TXEN        | SYNC   | SENDB | BRGH   | TRMT   | TX9D   | 0000 0010            | 0000 0010                       |

| Legend: | x = unknow | unknown, - = unimplemented read as '0'. Shaded cells are not used for Asynchronous Reception. |             |        |       |        |        |        |                      |                                 |

### TABLE 12-2: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

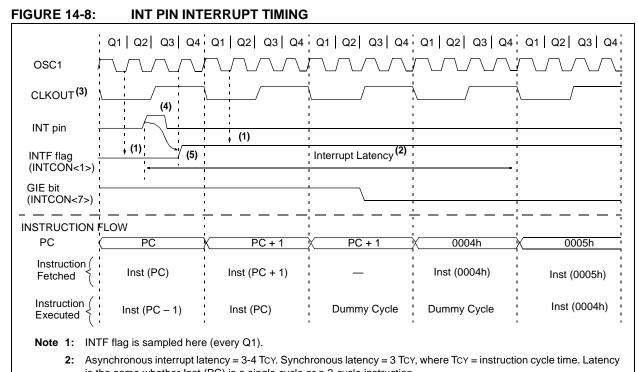

- is the same whether Inst (PC) is a single cycle or a 2-cycle instruction.

- 3: CLKOUT is available only in INTOSC and RC Oscillator modes.

- 4: For minimum width of INT pulse, refer to AC specifications in Section 17.0 "Electrical Specifications".

- 5: INTF is enabled to be set any time during the Q4-Q1 cycles.

#### TABLE 14-6: SUMMARY OF INTERRUPT REGISTERS

| Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-------|-------|-------|-------|-------|--------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE   | PEIE  | TOIE  | INTE  | RABIE | T0IF   | INTF   | RABIF  | x000 000x            | 0000 000x                       |

| PIE1   | —     | ADIE  | RCIE  | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | -000 0000            | -000 0000                       |

| PIE2   | OSFIE | C2IE  | C1IE  | EEIE  | —     | _      | —      | —      | 0000                 | 0000                            |

| PIR1   | —     | ADIF  | RCIF  | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | -000 0000            | -000 0000                       |

| PIR2   | OSFIF | C2IF  | C1IF  | EEIF  | —     | _      | —      | —      | 0000                 | 0000                            |

**Legend:** x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends upon condition.

Shaded cells are not used by the Interrupt module.

## 17.4 DC Characteristics: PIC16F631/677/685/687/689/690-I (Industrial) PIC16F631/677/685/687/689/690-E (Extended)

| DC CHA       | ARACTER | ISTICS                                     | Standard Operat          |       | herwise stated)<br>5°C for industrial<br>25°C for extended |       |                                                                                                     |  |

|--------------|---------|--------------------------------------------|--------------------------|-------|------------------------------------------------------------|-------|-----------------------------------------------------------------------------------------------------|--|

| Param<br>No. | Sym.    | Characteristic                             | Characteristic Min. Typ† |       | Max.                                                       | Units | Conditions                                                                                          |  |

|              | VIL     | Input Low Voltage                          |                          |       |                                                            |       |                                                                                                     |  |

|              |         | I/O Port:                                  |                          |       |                                                            |       |                                                                                                     |  |

| D030         |         | with TTL buffer                            | Vss                      | —     | 0.8                                                        | V     | $4.5V \leq V \text{DD} \leq 5.5V$                                                                   |  |

| D030A        |         |                                            | Vss                      | —     | 0.15 Vdd                                                   | V     | $2.0V \leq V\text{DD} \leq 4.5V$                                                                    |  |

| D031         |         | with Schmitt Trigger buffer                | Vss                      | —     | 0.2 Vdd                                                    | V     | $2.0V \le VDD \le 5.5V$                                                                             |  |

| D032         |         | MCLR, OSC1 (RC mode) <sup>(1)</sup>        | Vss                      | —     | 0.2 Vdd                                                    | V     |                                                                                                     |  |

| D033         |         | OSC1 (XT and LP modes)                     | Vss                      | _     | 0.3                                                        | V     |                                                                                                     |  |

| D033A        |         | OSC1 (HS mode)                             | Vss                      | —     | 0.3 Vdd                                                    | V     |                                                                                                     |  |

|              | VIH     | Input High Voltage                         |                          |       |                                                            |       |                                                                                                     |  |

|              |         | I/O Ports:                                 |                          | _     |                                                            |       |                                                                                                     |  |

| D040         |         | with TTL buffer                            | 2.0                      | _     | Vdd                                                        | V     | $4.5V \le VDD \le 5.5V$                                                                             |  |

| D040A        |         |                                            | 0.25 VDD + 0.8           | —     | Vdd                                                        | V     | $2.0V \le VDD \le 4.5V$                                                                             |  |

| D041         |         | with Schmitt Trigger buffer                | 0.8 Vdd                  | _     | Vdd                                                        | V     | $2.0V \le VDD \le 5.5V$                                                                             |  |

| D042         |         | MCLR                                       | 0.8 Vdd                  | _     | Vdd                                                        | V     |                                                                                                     |  |

| D043         |         | OSC1 (XT and LP modes)                     | 1.6                      | _     | Vdd                                                        | V     |                                                                                                     |  |

| D043A        |         | OSC1 (HS mode)                             | 0.7 Vdd                  | —     | Vdd                                                        | V     |                                                                                                     |  |

| D043B        |         | OSC1 (RC mode)                             | 0.9 Vdd                  | _     | Vdd                                                        | V     | (Note 1)                                                                                            |  |

|              | lı∟     | Input Leakage Current <sup>(2)</sup>       |                          |       |                                                            |       |                                                                                                     |  |

| D060         |         | I/O ports                                  | _                        | ± 0.1 | ± 1                                                        | μA    | $Vss \le VPIN \le VDD,$ Pin at high-impedance                                                       |  |

| D061         |         | MCLR <sup>(3)</sup>                        | —                        | ± 0.1 | ± 5                                                        | μA    | $VSS \leq VPIN \leq VDD$                                                                            |  |

| D063         |         | OSC1                                       | _                        | ± 0.1 | ± 5                                                        | μA    | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP oscillator configuration                                  |  |

| D070*        | IPUR    | PORTA Weak Pull-up Current                 | 50                       | 250   | 400                                                        | μΑ    | VDD = 5.0V, VPIN = VSS                                                                              |  |

|              | Vol     | Output Low Voltage <sup>(5)</sup>          |                          |       |                                                            |       |                                                                                                     |  |

| D080         |         | I/O ports                                  | —                        | —     | 0.6                                                        | V     | IOL = 8.5 mA, VDD = 4.5V (Ind.)                                                                     |  |

|              | Voh     | Output High Voltage <sup>(5)</sup>         |                          |       |                                                            |       |                                                                                                     |  |

| D090         |         | I/O ports                                  | Vdd - 0.7                | -     | _                                                          | V     | IOH = -3.0 mA, VDD = 4.5V (Ind.)                                                                    |  |

| D100         | IULP    | Ultra Low-Power Wake-up<br>Current         | _                        | 200   | _                                                          | nA    | See Application Note AN879,<br>"Using the Microchip Ultra<br>Low-Power Wake-up Module"<br>(DS00879) |  |

|              |         | Capacitive Loading Specs on<br>Output Pins |                          |       |                                                            |       |                                                                                                     |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

2: Negative current is defined as current sourced by the pin.

3: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

4: See Section 10.2.1 "Using the Data EEPROM" for additional information.

5: Including OSC2 in CLKOUT mode.

## 17.5 Thermal Considerations

| Param<br>No. | Sym.      | Characteristic             | Тур.  | Units | Conditions                                               |

|--------------|-----------|----------------------------|-------|-------|----------------------------------------------------------|

| TH01         | θJA       | Thermal Resistance         | 62.4  | C/W   | 20-pin PDIP package                                      |

|              |           | Junction to Ambient        | 85.2  | C/W   | 20-pin SOIC package                                      |

|              |           |                            | 108.1 | C/W   | 20-pin SSOP package                                      |

|              |           |                            | 40    | C/W   | 20-pin QFN 4x4mm package                                 |

| TH02         | θJC       | Thermal Resistance         | 28.1  | C/W   | 20-pin PDIP package                                      |

|              |           | Junction to Case           | 24.2  | C/W   | 20-pin SOIC package                                      |

|              |           |                            | 32.2  | C/W   | 20-pin SSOP package                                      |

|              |           |                            | 2.5   | C/W   | 20-pin QFN 4x4mm package                                 |

| TH03         | TDIE      | Die Temperature            | 150   | С     | For derated power calculations                           |

| TH04         | PD        | Power Dissipation          | _     | W     | PD = PINTERNAL + PI/O                                    |

| TH05         | PINTERNAL | Internal Power Dissipation | _     | W     | PINTERNAL = IDD x VDD<br>(Note 1)                        |

| TH06         | Pi/o      | I/O Power Dissipation      | —     | W     | $PI/O = \Sigma (IOL * VOL) + \Sigma (IOH * (VDD - VOH))$ |

| TH07         | Pder      | Derated Power              | _     | W     | PDER = PDMAX (TDIE - TA)/θJA<br>(Note 2, 3)              |

Note 1: IDD is current to run the chip alone without driving any load on the output pins.

**2:** TA = Ambient Temperature.

**3:** Maximum allowable power dissipation is the lower value of either the absolute maximum total power dissipation or derated power.

## **19.0 PACKAGING INFORMATION**

## 19.1 Package Marking Information

#### 20-Lead PDIP

20-Lead SOIC (7.50 mm)

#### 20-Lead SSOP

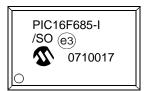

20-Lead QFN

Example

Example

### Example

Example

| Legend: | XXX<br>Y<br>YY<br>WW<br>NNN<br>(e3)<br>*                                                                                                                                                                      | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |  |  |  |  |  |  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|         | In the event the full Microchip part number cannot be marked on one line, it will<br>be carried over to the next line, thus limiting the number of available<br>characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

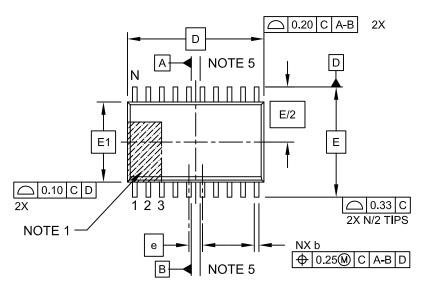

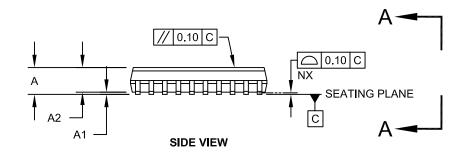

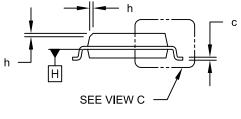

## 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

TOP VIEW

Microchip Technology Drawing C04-094C Sheet 1 of 2