# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | -                                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                        |

| Number of I/O              | 18                                                                      |

| Program Memory Size        | 1.75KB (1K x 14)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 128 x 8                                                                 |

| RAM Size                   | 64 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                               |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                 |

| Supplier Device Package    | 20-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f631-e-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2.2.5 PIE2 Register

The PIE2 register contains the interrupt enable bits, as shown in Register 2-5.

Note: Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

#### REGISTER 2-5: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-------|-------|-----|-----|-----|-------|

| OSFIE | C2IE  | C1IE  | EEIE  | —   | —   | —   | —     |

| bit 7 |       |       |       |     |     |     | bit 0 |

| Legend:         |                                                                                                                                                                  |                                                                                            |                        |                    |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------------------|--------------------|

| R = Readable    | bit                                                                                                                                                              | W = Writable bit                                                                           | U = Unimplemented bit, | read as '0'        |

| -n = Value at F | POR                                                                                                                                                              | '1' = Bit is set                                                                           | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7           | 1 = Enables                                                                                                                                                      | llator Fail Interrupt Enable b<br>oscillator fail interrupt<br>s oscillator fail interrupt | it                     |                    |

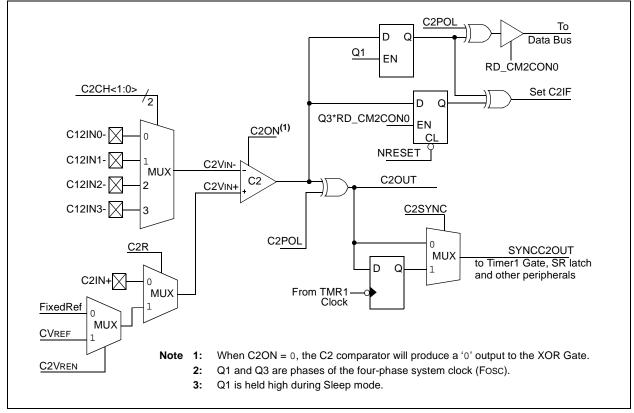

| bit 6           | <b>C2IE:</b> Comparator C2 Interrupt Enable bit<br>1 = Enables Comparator C2 interrupt<br>0 = Disables Comparator C2 interrupt                                   |                                                                                            |                        |                    |

| bit 5           | <b>C1IE:</b> Comparator C1 Interrupt Enable bit<br>1 = Enables Comparator C1 interrupt<br>0 = Disables Comparator C1 interrupt                                   |                                                                                            |                        |                    |

| bit 4           | <ul> <li>EEIE: EE Write Operation Interrupt Enable bit</li> <li>1 = Enables write operation interrupt</li> <li>0 = Disables write operation interrupt</li> </ul> |                                                                                            |                        |                    |

| bit 3-0         | Unimpleme                                                                                                                                                        | nted: Read as '0'                                                                          |                        |                    |

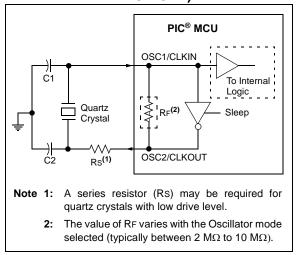

#### 3.4.3 LP, XT, HS MODES

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 3-3). The mode selects a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

LP Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

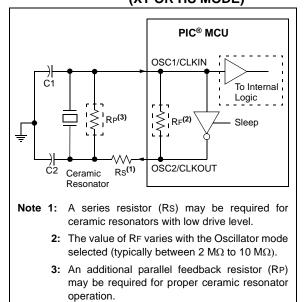

Figure 3-3 and Figure 3-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

- **Note 1:** Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- **2:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC<sup>®</sup> Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

#### FIGURE 3-3: QUARTZ CRYSTAL

#### OPERATION (LP, XT OR HS MODE)

#### CERAMIC RESONATOR OPERATION (XT OR HS MODE)

#### 3.5.3 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is an uncalibrated 31 kHz internal clock source.

The output of the LFINTOSC connects to a postscaler and multiplexer (see Figure 3-1). Select 31 kHz, via software, using the IRCF<2:0> bits of the OSCCON register. See **Section 3.5.4 "Frequency Select Bits (IRCF)**" for more information. The LFINTOSC is also the frequency for the Power-up Timer (PWRT), Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The LFINTOSC is enabled by selecting 31 kHz (IRCF<2:0> bits of the OSCCON register = 000) as the system clock source (SCS bit of the OSCCON register = 1), or when any of the following are enabled:

- Two-Speed Start-up IESO bit of the Configuration Word register = 1 and IRCF<2:0> bits of the OSCCON register = 000

- Power-up Timer (PWRT)

- Watchdog Timer (WDT)

- Fail-Safe Clock Monitor (FSCM)

The LF Internal Oscillator (LTS) bit of the OSCCON register indicates whether the LFINTOSC is stable or not.

#### 3.5.4 FREQUENCY SELECT BITS (IRCF)

The output of the 8 MHz HFINTOSC and 31 kHz LFINTOSC connects to a postscaler and multiplexer (see Figure 3-1). The Internal Oscillator Frequency Select bits IRCF<2:0> of the OSCCON register select the frequency output of the internal oscillators. One of eight frequencies can be selected via software:

- 8 MHz

- 4 MHz (Default after Reset)

- 2 MHz

- 1 MHz

- 500 kHz

- 250 kHz

- 125 kHz

- 31 kHz (LFINTOSC)

| Note: | Following any Reset, the IRCF<2:0> bits  |

|-------|------------------------------------------|

|       | of the OSCCON register are set to '110'  |

|       | and the frequency selection is set to    |

|       | 4 MHz. The user can modify the IRCF bits |

|       | to select a different frequency.         |

#### 3.5.5 HFINTOSC AND LFINTOSC CLOCK SWITCH TIMING

When switching between the LFINTOSC and the HFINTOSC, the new oscillator may already be shut down to save power (see Figure 3-6). If this is the case, there is a delay after the IRCF<2:0> bits of the OSCCON register are modified before the frequency selection takes place. The LTS and HTS bits of the OSCCON register will reflect the current active status of the LFINTOSC and HFINTOSC oscillators. The timing of a frequency selection is as follows:

- 1. IRCF<2:0> bits of the OSCCON register are modified.

- 2. If the new clock is shut down, a clock start-up delay is started.

- 3. Clock switch circuitry waits for a falling edge of the current clock.

- 4. CLKOUT is held low and the clock switch circuitry waits for a rising edge in the new clock.

- CLKOUT is now connected with the new clock. LTS and HTS bits of the OSCCON register are updated as required.

- 6. Clock switch is complete.

See Figure 3-1 for more details.

If the internal oscillator speed selected is between 8 MHz and 125 kHz, there is no start-up delay before the new frequency is selected. This is because the old and new frequencies are derived from the HFINTOSC via the postscaler and multiplexer.

Start-up delay specifications are located in the oscillator tables of **Section 17.0** "**Electrical Specifications**".

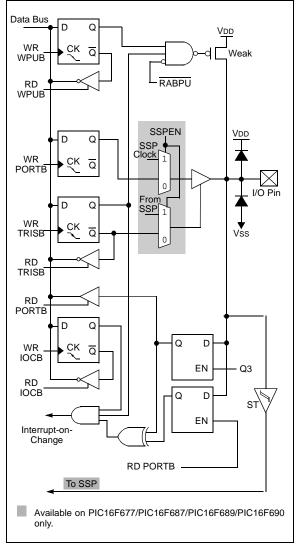

#### 4.4.3.3 RB6/SCK/SCL

Figure 4-9 shows the diagram for this pin. The RB6/ SCK/SCL<sup>(1)</sup> pin is configurable to function as one of the following:

- a general purpose I/O

- a SPI clock

- an l<sup>2</sup>C<sup>™</sup> clock

| Note 1: | SCK   | and    | SCL    | are   | available | on |

|---------|-------|--------|--------|-------|-----------|----|

|         | PIC16 | F677/  | PIC16F | 687/F | IC16F689/ |    |

|         | PIC16 | F690 ( | only.  |       |           |    |

#### FIGURE 4-9:

#### **BLOCK DIAGRAM OF RB6**

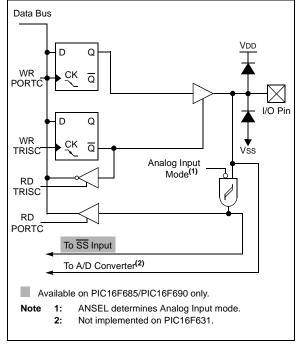

#### 4.5 PORTC and TRISC Registers

PORTC is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISC (Register 4-10). Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 4-4 shows how to initialize PORTC. Reading the PORTC register (Register 4-9) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch.

The TRISC register controls the PORTC pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISC register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

| Note: | The ANSEL and ANSELH registers must         |

|-------|---------------------------------------------|

|       | be initialized to configure an analog       |

|       | channel as a digital input. Pins configured |

|       | as analog inputs will read '0'.             |

#### EXAMPLE 4-4: INITIALIZING PORTC

| BCF   | STATUS, RPO | ;Bank 0                |

|-------|-------------|------------------------|

| BCF   | STATUS, RP1 | ;                      |

| CLRF  | PORTC       | ;Init PORTC            |

| BSF   | STATUS, RP1 | ;Bank 2                |

| CLRF  | ANSEL       | ;digital I/O           |

| BSF   | STATUS, RPO | ;Bank 1                |

| BCF   | STATUS, RP1 | i                      |

| MOVLW | 0Ch         | ;Set RC<3:2> as inputs |

| MOVWF | TRISC       | ;and set RC<5:4,1:0>   |

|       |             | ;as outputs            |

| BCF   | STATUS, RPO | ;Bank 0                |

|       |             |                        |

#### REGISTER 4-11: PORTC: PORTC REGISTER

| R/W-0 | R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| RC7   | RC6   | RC5   | RC4   | RC3   | RC2   | RC1   | RC0   |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 7-0

**RC<7:0>:** PORTC General Purpose I/O Pin bit 1 = Port pin is > VIH

0 = Port pin is < VIL

#### REGISTER 4-12: TRISC: PORTC TRI-STATE REGISTER

| R/W-1  | R/W-1  | R/W-1  | R/W-1  | R-1    | R/W-1  | R/W-1  | R/W-1  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 7-0

TRISC<7:0>: PORTC Tri-State Control bit

1 = PORTC pin configured as an input (tri-stated)

0 = PORTC pin configured as an output

#### 4.5.7 RC6/AN8/SS

The RC6/AN8/ $\overline{SS}^{(1,2)}$  is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC (except PIC16F631)

- a slave select input

| Note 1: | SS is available on PIC16F687/PIC16F689/ |

|---------|-----------------------------------------|

|         | PIC16F690 only.                         |

2: AN8 is not implemented on PIC16F631.

#### FIGURE 4-15: BLOCK DIAGRAM OF RC6

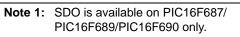

#### 4.5.8 RC7/AN9/SDO

The RC7/AN9/SDO $^{(1,2)}$  is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC (except PIC16F631)

- a serial data output

2: AN9 is not implemented on PIC16F631.

#### FIGURE 4-16: BLOCK DIAGRAM OF RC7

### 5.1.3 SOFTWARE PROGRAMMABLE PRESCALER

A single software programmable prescaler is available for use with either Timer0 or the Watchdog Timer (WDT), but not both simultaneously. The prescaler assignment is controlled by the PSA bit of the OPTION register. To assign the prescaler to Timer0, the PSA bit must be cleared to a '0'.

There are eight prescaler options for the Timer0 module ranging from 1:2 to 1:256. The prescale values are selectable via the PS<2:0> bits of the OPTION register. In order to have a 1:1 prescaler value for the Timer0 module, the prescaler must be assigned to the WDT module.

The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, all instructions writing to the TMR0 register will clear the prescaler.

When the prescaler is assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT.

#### 5.1.3.1 Switching Prescaler Between Timer0 and WDT Modules

As a result of having the prescaler assigned to either Timer0 or the WDT, it is possible to generate an unintended device Reset when switching prescaler values. When changing the prescaler assignment from Timer0 to the WDT module, the instruction sequence shown in Example 5-1, must be executed.

### EXAMPLE 5-1: CHANGING PRESCALER (TIMER0 $\rightarrow$ WDT)

| BANKSEL        | TMR0                       | ;                             |

|----------------|----------------------------|-------------------------------|

| CLRWDT         |                            | ;Clear WDT                    |

| CLRF           | TMR0                       | ;Clear TMR0 and               |

|                |                            | ;prescaler                    |

| BANKSEL        | OPTION_REG                 | ;                             |

| BSF            | OPTION_REG,                | PSA;Select WDT                |

| CLRWDT         |                            | ;                             |

|                |                            |                               |

|                |                            | i                             |

| MOVLW          | b'11111000'                | ;<br>;Mask prescaler          |

| MOVLW<br>ANDWF | b'11111000'<br>OPTION_REG, | -                             |

|                | OPTION_REG,                | -                             |

| ANDWF          | OPTION_REG,                | W; bits<br>;Set WDT prescaler |

When changing the prescaler assignment from the WDT to the Timer0 module, the following instruction sequence must be executed (see Example 5-2).

### EXAMPLE 5-2: CHANGING PRESCALER (WDT $\rightarrow$ TIMER0)

| CLRWDT  | ;Clear WDT and                   |

|---------|----------------------------------|

|         | ;prescaler                       |

| BANKSEL | OPTION_REG ;                     |

| MOVLW   | b'11110000';Mask TMR0 select and |

| ANDWF   | OPTION_REG,W; prescaler bits     |

| IORLW   | b'00000011';Set prescale to 1:16 |

| MOVWF   | OPTION_REG ;                     |

|         |                                  |

#### 5.1.4 TIMER0 INTERRUPT

Timer0 will generate an interrupt when the TMR0 register overflows from FFh to 00h. The T0IF interrupt flag bit of the INTCON register is set every time the TMR0 register overflows, regardless of whether or not the Timer0 interrupt is enabled. The T0IF bit must be cleared in software. The Timer0 interrupt enable is the T0IE bit of the INTCON register.

| Note: | The Timer0 interrupt cannot wake the    |  |

|-------|-----------------------------------------|--|

|       | processor from Sleep since the timer is |  |

|       | frozen during Sleep.                    |  |

### 5.1.5 USING TIMER0 WITH AN EXTERNAL CLOCK

When Timer0 is in Counter mode, the synchronization of the T0CKI input and the Timer0 register is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, the high and low periods of the external clock source must meet the timing requirements as shown in Section 17.0 "Electrical Specifications". Note: TMR1GE bit of the <u>T1CON</u> register must be set to use either <u>T1G</u> or C2OUT as the Timer1 gate source. See the CM2CON1 register (Register 8-3) for more information on selecting the Timer1 gate source.

Timer1 gate can be inverted using the T1GINV bit of the T1CON register, whether it originates from the T1G pin or Comparator C2 output. This configures Timer1 to measure either the active-high or active-low time between events.

#### 6.7 Timer1 Interrupt

The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit of the PIR1 register is set. To enable the interrupt on rollover, you must set these bits:

- TMR10N bit of the T1CON register

- TMR1IE bit of the PIE1 register

- PEIE bit of the INTCON register

- GIE bit of the INTCON register

The interrupt is cleared by clearing the TMR1IF bit in the Interrupt Service Routine.

Note: The TMR1H:TTMR1L register pair and the TMR1IF bit should be cleared before enabling interrupts.

#### 6.8 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- TMR1ON bit of the T1CON register must be set

- TMR1IE bit of the PIE1 register must be set

- PEIE bit of the INTCON register must be set

- T1SYNC bit of the T1CON register must be set

- TMR1CS bit of the T1CON register must be set

- T1OSCEN bit of the T1CON register (can be set)

The device will wake-up on an overflow and execute the next instructions. If the GIE bit of the INTCON register is set, the device will call the Interrupt Service Routine (0004h).

#### 6.9 ECCP Capture/Compare Time Base

The ECCP module uses the TMR1H:TMR1L register pair as the time base when operating in Capture or Compare mode.

In Capture mode, the value in the TMR1H:TMR1L register pair is copied into the CCPR1H:CCPR1L register pair on a configured event.

In Compare mode, an event is triggered when the value CCPR1H:CCPR1L register pair matches the value in the TMR1H:TMR1L register pair. This event can be a Special Event Trigger.

For more information, see Section 11.0 "Enhanced Capture/Compare/PWM Module".

#### 6.10 ECCP Special Event Trigger

When the ECCP is configured to trigger a special event, the trigger will clear the TMR1H:TMR1L register pair. This special event does not cause a Timer1 interrupt. The ECCP module may still be configured to generate a ECCP interrupt.

In this mode of operation, the CCPR1H:CCPR1L register pair becomes the period register for Timer1.

Timer1 should be synchronized to the FOSC to utilize the Special Event Trigger. Asynchronous operation of Timer1 can cause a Special Event Trigger to be missed.

In the event that a write to TMR1H or TMR1L coincides with a Special Event Trigger from the ECCP, the write will take precedence.

For more information, see **Section 11.2.4** "Special **Event Trigger**".

#### 6.11 Comparator Synchronization

The same clock used to increment Timer1 can also be used to synchronize the comparator output. This feature is enabled in the Comparator module.

When using the comparator for Timer1 gate, the comparator output should be synchronized to Timer1. This ensures Timer1 does not miss an increment if the comparator changes.

For more information, see Section 8.8.2 "Synchronizing Comparator C2 output to Timer1".

| U-0              | R/W-0                                                                                                                                                                                                                                                     | R/W-0            | R/W-0 | U-0                                | U-0  | U-0             | U-0   |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------|------------------------------------|------|-----------------|-------|

| —                | ADCS2                                                                                                                                                                                                                                                     | ADCS1            | ADCS0 | —                                  | —    | —               | _     |

| bit 7            |                                                                                                                                                                                                                                                           |                  |       |                                    |      |                 | bit 0 |

|                  |                                                                                                                                                                                                                                                           |                  |       |                                    |      |                 |       |

| Legend:          |                                                                                                                                                                                                                                                           |                  |       |                                    |      |                 |       |

| R = Readable     | bit                                                                                                                                                                                                                                                       | W = Writable     | bit   | U = Unimplemented bit, read as '0' |      |                 |       |

| -n = Value at F  | POR                                                                                                                                                                                                                                                       | '1' = Bit is set |       | '0' = Bit is cle                   | ared | x = Bit is unkn | nown  |

| bit 7<br>bit 6-4 | Unimplemented: Read as '0'<br>ADCS<2:0>: A/D Conversion Clock Select bits<br>000 = Fosc/2<br>001 = Fosc/8<br>010 = Fosc/32<br>x11 = FRC (clock derived from a dedicated internal oscillator = 500 kHz m<br>100 = Fosc/4<br>101 = Fosc/16<br>110 = Fosc/64 |                  |       | max)                               |      |                 |       |

| bit 3-0          | Unimplemen                                                                                                                                                                                                                                                | ted: Read as '   | 0'    |                                    |      |                 |       |

|                  |                                                                                                                                                                                                                                                           |                  |       |                                    |      |                 |       |

#### REGISTER 9-2: ADCON1: A/D CONTROL REGISTER 1

#### 10.0 DATA EEPROM AND FLASH PROGRAM MEMORY CONTROL

Data EEPROM memory is readable and writable and the Flash program memory (PIC16F685/PIC16F689/ PIC16F690 only) is readable during normal operation (full VDD range). These memories are not directly mapped in the register file space. Instead, they are indirectly addressed through the Special Function Registers (SFRs). There are six SFRs used to access these memories:

- EECON1

- EECON2

- EEDAT

- EEDATH (PIC16F685/PIC16F689/PIC16F690 only)

- EEADR

- EEADRH (PIC16F685/PIC16F689/PIC16F690 only)

When interfacing the data memory block, EEDAT holds the 8-bit data for read/write, and EEADR holds the address of the EEDAT location being accessed. These devices, except for the PIC16F631, have 256 bytes of data EEPROM with an address range from 0h to 0FFh. The PIC16F631 has 128 bytes of data EEPROM with an address range from 0h to 07Fh.

When accessing the program memory block of the PIC16F685/PIC16F689/PIC16F690 devices, the EEDAT and EEDATH registers form a 2-byte word that holds the 14-bit data for read/write, and the EEADR and EEADRH registers form a 2-byte word that holds the 12-bit address of the EEPROM location being read. These devices (PIC16F685/PIC16F689/PIC16F690) have 4K words of program EEPROM with an address range from 0h to 0FFFh. The program memory allows one-word reads.

The EEPROM data memory allows byte read and write. A byte write automatically erases the location and writes the new data (erase before write).

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the voltage range of the device for byte or word operations.

When the device is code-protected, the CPU may continue to read and write the data EEPROM memory and read the program memory. When code-protected, the device programmer can no longer access data or program memory.

#### 10.1 EEADR and EEADRH Registers

The EEADR and EEADRH registers can address up to a maximum of 256 bytes of data EEPROM or up to a maximum of 4K words of program EEPROM.

When selecting a program address value, the MSB of the address is written to the EEADRH register and the LSB is written to the EEADR register. When selecting a data address value, only the LSB of the address is written to the EEADR register.

#### 10.1.1 EECON1 AND EECON2 REGISTERS

EECON1 is the control register for EE memory accesses.

Control bit EEPGD (PIC16F685/PIC16F689/PIC16F690) determines if the access will be a program or data memory access. When clear, as it is when reset, any subsequent operations will operate on the data memory. When set, any subsequent operations will operate on the program memory. Program memory can only be read.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation to data EEPROM. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a  $\overline{\text{MCLR}}$  or a WDT Time-out Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and rewrite the location.

Interrupt flag bit EEIF of the PIR2 register is set when write is complete. It must be cleared in the software.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the data EEPROM write sequence.

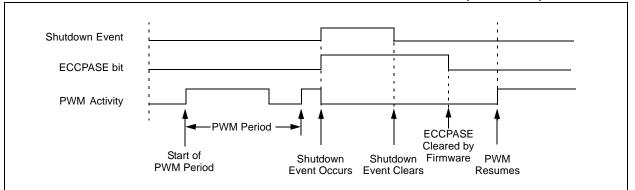

#### FIGURE 11-15: PWM AUTO-SHUTDOWN WITH FIRMWARE RESTART (PRSEN = 0)

#### 11.4.5 AUTO-RESTART MODE

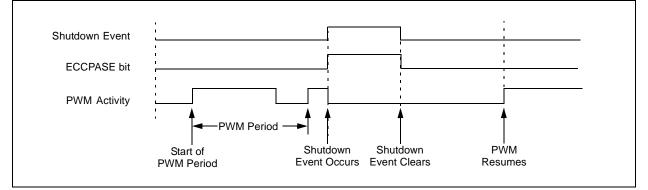

The Enhanced PWM can be configured to automatically restart the PWM signal once the auto-shutdown condition has been removed. Auto-restart is enabled by setting the PRSEN bit in the PWM1CON register.

If auto-restart is enabled, the ECCPASE bit will remain set as long as the auto-shutdown condition is active. When the auto-shutdown condition is removed, the ECCPASE bit will be cleared via hardware and normal operation will resume.

#### FIGURE 11-16: PWM AUTO-SHUTDOWN WITH AUTO-RESTART ENABLED (PRSEN = 1)

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b < 7 \end{array}$                                                                                                                                                |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                            |

| Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next<br>instruction is discarded and a NOP<br>is executed instead, making this a<br>2-cycle instruction. |

| CLRWDT           | Clear Watchdog Timer                                                                                                                                                     |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [label] CLRWDT                                                                                                                                                           |  |  |

| Operands:        | None                                                                                                                                                                     |  |  |

| Operation:       | $\begin{array}{l} \text{00h} \rightarrow \text{WDT} \\ 0 \rightarrow \text{WDT prescaler,} \\ 1 \rightarrow \overline{\text{TO}} \\ 1 \rightarrow \text{PD} \end{array}$ |  |  |

| Status Affected: | TO, PD                                                                                                                                                                   |  |  |

| Description:     | CLRWDT instruction resets the<br>Watchdog Timer. It also resets the<br>prescaler of the WDT.<br>Status bits TO and PD are set.                                           |  |  |

| CALL             | Call Subroutine                                                                                                                                                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                 |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                                                                      |

| Operation:       | (PC)+ 1 $\rightarrow$ TOS,<br>k $\rightarrow$ PC<10:0>,<br>(PCLATH<4:3>) $\rightarrow$ PC<12:11>                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                                                                    |

| Description:     | Call Subroutine. First, return<br>address (PC + 1) is pushed onto<br>the stack. The 11-bit immediate<br>address is loaded into PC bits<br><10:0>. The upper bits of the PC<br>are loaded from PCLATH. CALL is<br>a 2-cycle instruction. |

| COMF             | Complement f                                                                                                                                                   |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [ <i>label</i> ] COMF f,d                                                                                                                                      |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                |  |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                                     |  |

| Status Affected: | Z                                                                                                                                                              |  |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is '0', the<br>result is stored in W. If 'd' is '1',<br>the result is stored back in<br>register 'f'. |  |

| CLRF             | Clear f                                                               |  |

|------------------|-----------------------------------------------------------------------|--|

| Syntax:          | [ label ] CLRF f                                                      |  |

| Operands:        | $0 \leq f \leq 127$                                                   |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |  |

| Status Affected: | Z                                                                     |  |

| Description:     | The contents of register 'f' are<br>cleared and the Z bit is set.     |  |

| CLRW             | Clear W                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [ label ] CLRW                                                        |

| Operands:        | None                                                                  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | W register is cleared. Zero bit (Z) is set.                           |

| DECF             | Decrement f                                                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] DECF f,d                                                                                                                                |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                   |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                               |

| Status Affected: | Z                                                                                                                                                 |

| Description:     | Decrement register 'f'. If 'd' is '0',<br>the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |

© 2005-2015 Microchip Technology Inc.

| SUBWF            | Subtract W from f                                                                                                                                                                           |       |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|

| Syntax:          | [ <i>label</i> ] SUBWF f,d                                                                                                                                                                  |       |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                             |       |  |

| Operation:       | (f) - (W) $\rightarrow$ (destination)                                                                                                                                                       |       |  |

| Status Affected: | C, DC, Z                                                                                                                                                                                    |       |  |

| Description:     | Subtract (2's complement method)<br>W register from register 'f'. If 'd' is<br>'0', the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |       |  |

|                  | <b>C</b> = 0                                                                                                                                                                                | W > f |  |

**C** = 1

DC = 0

**DC** = 1

$W \leq f$

W<3:0> > f<3:0>

W<3:0> ≤ f<3:0>

| XORLW            | Exclusive OR literal with W                                                                                            |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                               |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |  |  |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                          |  |  |  |  |  |

| Status Affected: | Z                                                                                                                      |  |  |  |  |  |

| Description:     | The contents of the W register<br>are XOR'ed with the 8-bit<br>literal 'k'. The result is placed in<br>the W register. |  |  |  |  |  |

| SWAPF            | Swap Nibbles in f                                                                                                                                                      |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] SWAPF f,d                                                                                                                                                      |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                            |  |  |  |  |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                |  |  |  |  |

| Status Affected: | None                                                                                                                                                                   |  |  |  |  |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed in register 'f'. |  |  |  |  |

| XORWF            | Exclusive OR W with f                                                                                                                                                           |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] XORWF f,d                                                                                                                                                               |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                               |  |  |  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                       |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                               |  |  |  |  |  |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |  |  |  |  |  |  |

#### 17.4 DC Characteristics: PIC16F631/677/685/687/689/690-I (Industrial) PIC16F631/677/685/687/689/690-E (Extended)

| DC CHARACTERISTICS |      | Standard Operating Cone<br>Operating temperature |                | ditions (unless otherwise stated)<br>-40°C $\leq$ TA $\leq$ +85°C for industrial<br>-40°C $\leq$ TA $\leq$ +125°C for extended |          |       |                                                                                                     |

|--------------------|------|--------------------------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------|----------|-------|-----------------------------------------------------------------------------------------------------|

| Param<br>No.       | Sym. | Characteristic                                   | Min.           | Тур†                                                                                                                           | Max.     | Units | Conditions                                                                                          |

|                    | VIL  | Input Low Voltage                                |                |                                                                                                                                |          |       |                                                                                                     |

|                    |      | I/O Port:                                        |                |                                                                                                                                |          |       |                                                                                                     |

| D030               |      | with TTL buffer                                  | Vss            | —                                                                                                                              | 0.8      | V     | $4.5V \leq V \text{DD} \leq 5.5V$                                                                   |

| D030A              |      |                                                  | Vss            | —                                                                                                                              | 0.15 Vdd | V     | $2.0V \leq V\text{DD} \leq 4.5V$                                                                    |

| D031               |      | with Schmitt Trigger buffer                      | Vss            | —                                                                                                                              | 0.2 Vdd  | V     | $2.0V \le VDD \le 5.5V$                                                                             |

| D032               |      | MCLR, OSC1 (RC mode) <sup>(1)</sup>              | Vss            | —                                                                                                                              | 0.2 Vdd  | V     |                                                                                                     |

| D033               |      | OSC1 (XT and LP modes)                           | Vss            | _                                                                                                                              | 0.3      | V     |                                                                                                     |

| D033A              |      | OSC1 (HS mode)                                   | Vss            | —                                                                                                                              | 0.3 Vdd  | V     |                                                                                                     |

|                    | VIH  | Input High Voltage                               |                |                                                                                                                                |          |       |                                                                                                     |

|                    |      | I/O Ports:                                       |                | _                                                                                                                              |          |       |                                                                                                     |

| D040               |      | with TTL buffer                                  | 2.0            | _                                                                                                                              | Vdd      | V     | $4.5V \le VDD \le 5.5V$                                                                             |

| D040A              |      |                                                  | 0.25 VDD + 0.8 | —                                                                                                                              | Vdd      | V     | $2.0V \le VDD \le 4.5V$                                                                             |

| D041               |      | with Schmitt Trigger buffer                      | 0.8 Vdd        | _                                                                                                                              | Vdd      | V     | $2.0V \le VDD \le 5.5V$                                                                             |

| D042               |      | MCLR                                             | 0.8 Vdd        | _                                                                                                                              | Vdd      | V     |                                                                                                     |

| D043               |      | OSC1 (XT and LP modes)                           | 1.6            | _                                                                                                                              | Vdd      | V     |                                                                                                     |

| D043A              |      | OSC1 (HS mode)                                   | 0.7 Vdd        | —                                                                                                                              | Vdd      | V     |                                                                                                     |

| D043B              |      | OSC1 (RC mode)                                   | 0.9 Vdd        | _                                                                                                                              | Vdd      | V     | (Note 1)                                                                                            |

|                    | lı∟  | Input Leakage Current <sup>(2)</sup>             |                |                                                                                                                                |          |       |                                                                                                     |

| D060               |      | I/O ports                                        | _              | ± 0.1                                                                                                                          | ± 1      | μA    | $Vss \le VPIN \le VDD,$ Pin at high-impedance                                                       |

| D061               |      | MCLR <sup>(3)</sup>                              | —              | ± 0.1                                                                                                                          | .1 ±5 μ  |       | $VSS \leq VPIN \leq VDD$                                                                            |

| D063               |      | OSC1                                             | _              | ± 0.1                                                                                                                          | ± 5      | μA    | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP oscillator configuration                                  |

| D070*              | IPUR | PORTA Weak Pull-up Current                       | 50             | 250                                                                                                                            | 400      | μΑ    | VDD = 5.0V, VPIN = VSS                                                                              |

|                    | Vol  | Output Low Voltage <sup>(5)</sup>                |                |                                                                                                                                |          |       |                                                                                                     |

| D080               |      | I/O ports                                        | —              | —                                                                                                                              | 0.6      | V     | IOL = 8.5 mA, VDD = 4.5V (Ind.)                                                                     |

|                    | Voh  | Output High Voltage <sup>(5)</sup>               |                |                                                                                                                                |          |       |                                                                                                     |

| D090               |      | I/O ports                                        | Vdd - 0.7      | -                                                                                                                              | —        | V     | IOH = -3.0 mA, VDD = 4.5V (Ind.)                                                                    |

| D100               | IULP | Ultra Low-Power Wake-up<br>Current               | _              | 200                                                                                                                            | _        | nA    | See Application Note AN879,<br>"Using the Microchip Ultra<br>Low-Power Wake-up Module"<br>(DS00879) |

|                    |      | Capacitive Loading Specs on<br>Output Pins       |                |                                                                                                                                |          |       |                                                                                                     |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

2: Negative current is defined as current sourced by the pin.

3: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

4: See Section 10.2.1 "Using the Data EEPROM" for additional information.

5: Including OSC2 in CLKOUT mode.

#### 17.7 AC Characteristics: PIC16F631/677/685/687/689/690 (Industrial, Extended)

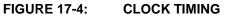

#### TABLE 17-1: CLOCK OSCILLATOR TIMING REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |       |                                         |      |        |          |       |                    |

|----------------------------------------------------------------------------------------------------------------------|-------|-----------------------------------------|------|--------|----------|-------|--------------------|

| Param<br>No.                                                                                                         | Sym.  | Characteristic                          | Min. | Тур†   | Max.     | Units | Conditions         |

| OS01                                                                                                                 | Fosc  | External CLKIN Frequency <sup>(1)</sup> | DC   | _      | 37       | kHz   | LP Oscillator mode |

|                                                                                                                      |       |                                         | DC   | —      | 4        | MHz   | XT Oscillator mode |

|                                                                                                                      |       |                                         | DC   | —      | 20       | MHz   | HS Oscillator mode |

|                                                                                                                      |       |                                         | DC   | —      | 20       | MHz   | EC Oscillator mode |

|                                                                                                                      |       | Oscillator Frequency <sup>(1)</sup>     | _    | 32.768 | _        | kHz   | LP Oscillator mode |

|                                                                                                                      |       |                                         | 0.1  | —      | 4        | MHz   | XT Oscillator mode |

|                                                                                                                      |       |                                         | 1    | —      | 20       | MHz   | HS Oscillator mode |

|                                                                                                                      |       |                                         | DC   | —      | 4        | MHz   | RC Oscillator mode |

| OS02                                                                                                                 | Tosc  | External CLKIN Period <sup>(1)</sup>    | 27   | _      | ×        | μS    | LP Oscillator mode |

|                                                                                                                      |       |                                         | 250  | —      | ×        | ns    | XT Oscillator mode |

|                                                                                                                      |       |                                         | 50   | —      | ×        | ns    | HS Oscillator mode |

|                                                                                                                      |       |                                         | 50   | —      | $\infty$ | ns    | EC Oscillator mode |

|                                                                                                                      |       | Oscillator Period <sup>(1)</sup>        | _    | 30.5   | _        | μS    | LP Oscillator mode |

|                                                                                                                      |       |                                         | 250  | —      | 10,000   | ns    | XT Oscillator mode |

|                                                                                                                      |       |                                         | 50   | —      | 1,000    | ns    | HS Oscillator mode |

|                                                                                                                      |       |                                         | 250  | —      | —        | ns    | RC Oscillator mode |

| OS03                                                                                                                 | TCY   | Instruction Cycle Time <sup>(1)</sup>   | 200  | TCY    | DC       | ns    | Tcy = 4/Fosc       |

| OS04*                                                                                                                | TosH, | External CLKIN High,                    | 2    | —      | —        | μS    | LP oscillator      |

|                                                                                                                      | TosL  | External CLKIN Low                      | 100  | —      | —        | ns    | XT oscillator      |

|                                                                                                                      |       |                                         | 20   | —      | —        | ns    | HS oscillator      |

| OS05*                                                                                                                | TosR, | External CLKIN Rise,                    | 0    | _      | ×        | ns    | LP oscillator      |

|                                                                                                                      | TosF  | External CLKIN Fall                     | 0    | —      | ×        | ns    | XT oscillator      |

|                                                                                                                      |       |                                         | 0    | —      | $\infty$ | ns    | HS oscillator      |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at 'min' values with an external clock applied to OSC1 pin. When an external clock input is used, the 'max' cycle time limit is 'DC' (no clock) for all devices.

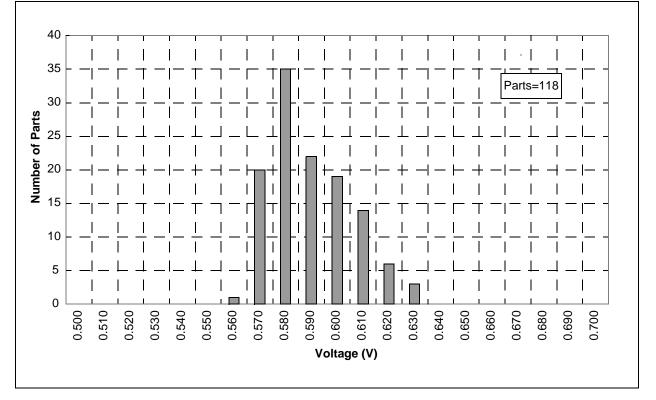

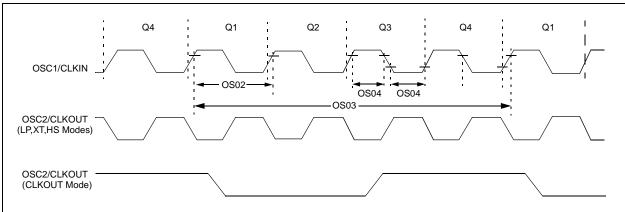

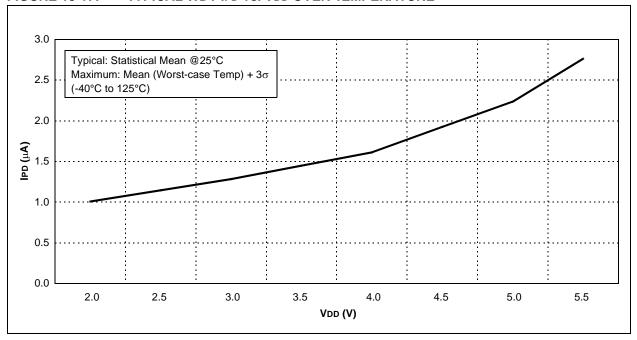

BOR IPD vs. VDD OVER TEMPERATURE

FIGURE 18-16:

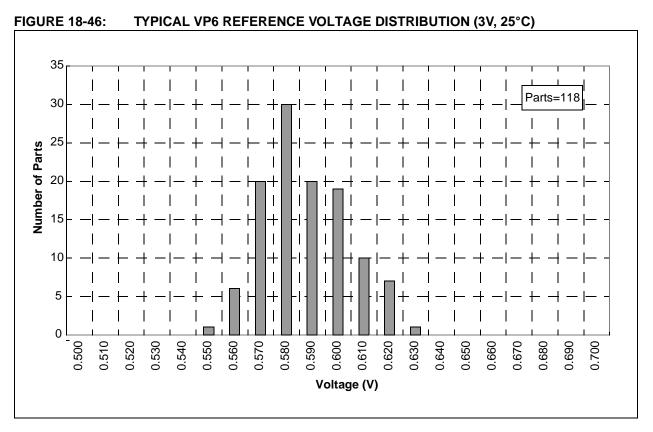

FIGURE 18-47: TYPICAL VP6 REFERENCE VOLTAGE DISTRIBUTION (3V, 85°C)