# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | -                                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                        |

| Number of I/O              | 18                                                                      |

| Program Memory Size        | 1.75KB (1K x 14)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 128 x 8                                                                 |

| RAM Size                   | 64 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                               |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                 |

| Supplier Device Package    | 20-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f631-i-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

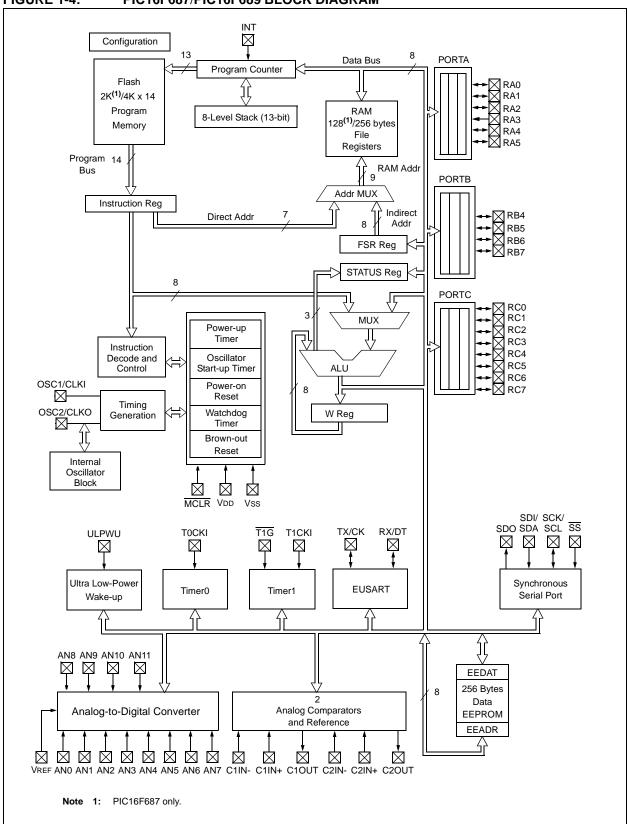

### FIGURE 1-4: PIC16F687/PIC16F689 BLOCK DIAGRAM

| Name            | Function | Input<br>Type | Output<br>Type | Description                                                                                        |

|-----------------|----------|---------------|----------------|----------------------------------------------------------------------------------------------------|

| RB7             | RB7      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-change.<br>Individually enabled pull-up. |

| RC0/AN4/C2IN+   | RC0      | ST            | CMOS           | General purpose I/O.                                                                               |

|                 | AN4      | AN            | —              | A/D Channel 4 input.                                                                               |

|                 | C2IN+    | AN            | —              | Comparator C2 non-inverting input.                                                                 |

| RC1/AN5/C12IN1- | RC1      | ST            | CMOS           | General purpose I/O.                                                                               |

|                 | AN5      | AN            | —              | A/D Channel 5 input.                                                                               |

|                 | C12IN1-  | AN            | —              | Comparator C1 or C2 inverting input.                                                               |

| RC2/AN6/C12IN2- | RC2      | ST            | CMOS           | General purpose I/O.                                                                               |

|                 | AN6      | AN            | —              | A/D Channel 6 input.                                                                               |

|                 | C12IN2-  | AN            | —              | Comparator C1 or C2 inverting input.                                                               |

| RC3/AN7/C12IN3- | RC3      | ST            | CMOS           | General purpose I/O.                                                                               |

|                 | AN7      | AN            | —              | A/D Channel 7 input.                                                                               |

|                 | C12IN3-  | AN            | —              | Comparator C1 or C2 inverting input.                                                               |

| RC4/C2OUT       | RC4      | ST            | CMOS           | General purpose I/O.                                                                               |

|                 | C2OUT    | —             | CMOS           | Comparator C2 output.                                                                              |

| RC5             | RC5      | ST            | CMOS           | General purpose I/O.                                                                               |

| RC6/AN8/SS      | RC6      | ST            | CMOS           | General purpose I/O.                                                                               |

|                 | AN8      | AN            | —              | A/D Channel 8 input.                                                                               |

|                 | SS       | ST            | —              | Slave Select input.                                                                                |

| RC7/AN9/SDO     | RC7      | ST            | CMOS           | General purpose I/O.                                                                               |

|                 | AN9      | AN            | —              | A/D Channel 9 input.                                                                               |

|                 | SDO      | —             | CMOS           | SPI data output.                                                                                   |

| Vss             | Vss      | Power         | _              | Ground reference.                                                                                  |

| Vdd             | Vdd      | Power         | _              | Positive supply.                                                                                   |

### TABLE 1-2: PINOUT DESCRIPTION – PIC16F677 (CONTINUED)

**Legend:** AN = Analog input or output

TTL = TTL compatible input

HV = High Voltage

XTAL= Crystal

CMOS=CMOS compatible input or output

ST= Schmitt Trigger input with CMOS levels

| Addr | Name                     | Bit 7                            | Bit 6                                 | Bit 5               | Bit 4               | Bit 3                | Bit 2                 | Bit 1                 | Bit 0                | Value on<br>POR, BOR | Page    |

|------|--------------------------|----------------------------------|---------------------------------------|---------------------|---------------------|----------------------|-----------------------|-----------------------|----------------------|----------------------|---------|

| Bank | 0                        |                                  |                                       |                     |                     |                      |                       |                       |                      |                      |         |

| 00h  | INDF                     | Addressing                       | this location                         | uses conten         | ts of FSR to a      | address data         | memory (no            | t a physical r        | egister)             | xxxx xxxx            | 43,200  |

| 01h  | TMR0                     | Timer0 Mod                       | lule Register                         |                     |                     |                      |                       |                       |                      | xxxx xxxx            | 79,200  |

| 02h  | PCL                      | Program Co                       | ounter's (PC)                         | Least Signif        | icant Byte          |                      |                       |                       |                      | 0000 0000            | 43,200  |

| 03h  | STATUS                   | IRP                              | RP1                                   | RP0                 | TO                  | PD                   | Z                     | DC                    | С                    | 0001 1xxx            | 35,200  |

| 04h  | FSR                      | Indirect Dat                     | a Memory A                            | ddress Pointe       | ər                  |                      |                       |                       |                      | xxxx xxxx            | 43,200  |

| 05h  | PORTA <sup>(7)</sup>     | _                                | _                                     | RA5                 | RA4                 | RA3                  | RA2                   | RA1                   | RA0                  | xx xxxx              | 57,200  |

| 06h  | PORTB <sup>(7)</sup>     | RB7                              | RB6                                   | RB5                 | RB4                 | _                    | _                     | _                     | _                    | xxxx                 | 67,200  |

| 07h  | PORTC <sup>(7)</sup>     | RC7                              | RC6                                   | RC5                 | RC4                 | RC3                  | RC2                   | RC1                   | RC0                  | xxxx xxxx            | 74,200  |

| 08h  | —                        | Unimpleme                        | nted                                  |                     |                     |                      |                       |                       |                      | —                    | —       |

| 09h  | —                        | Unimpleme                        | nted                                  |                     |                     |                      |                       |                       |                      | —                    | —       |

| 0Ah  | PCLATH                   |                                  | _                                     |                     | Write Buffer        | for upper 5 l        | oits of Progra        | am Counter            |                      | 0 0000               | 43,200  |

| 0Bh  | INTCON                   | GIE                              | PEIE                                  | TOIE                | INTE                | RABIE                | TOIF                  | INTF                  | RABIF <sup>(1)</sup> | 0000 000x            | 37,200  |

| 0Ch  | PIR1                     | _                                | ADIF <sup>(4)</sup>                   | RCIF <sup>(2)</sup> | TXIF <sup>(2)</sup> | SSPIF <sup>(5)</sup> | CCP1IF <sup>(3)</sup> | TMR2IF <sup>(3)</sup> | TMR1IF               | -000 0000            | 40,200  |

| 0Dh  | PIR2                     | OSFIF                            | C2IF                                  | C1IF                | EEIF                | —                    | —                     | _                     | _                    | 0000                 | 41,200  |

| 0Eh  | TMR1L                    | Holding Re                       | gister for the                        | Least Signifi       | cant Byte of        | the 16-bit TM        | R1 Register           |                       |                      | xxxx xxxx            | 85,200  |

| 0Fh  | TMR1H                    | Holding Re                       | gister for the                        | Most Signific       | cant Byte of t      | he 16-bit TM         | R1 Register           |                       |                      | xxxx xxxx            | 85,200  |

| 10h  | T1CON                    | T1GINV                           | TMR1GE                                | T1CKPS1             | T1CKPS0             | T1OSCEN              | T1SYNC                | TMR1CS                | TMR10N               | 0000 0000            | 87,200  |

| 11h  | TMR2 <sup>(3)</sup>      | Timer2 Mod                       | ule Register                          |                     |                     |                      |                       |                       |                      | 0000 0000            | 89,200  |

| 12h  | T2CON <sup>(3)</sup>     | -                                | TOUTPS3                               | TOUTPS2             | TOUTPS1             | TOUTPS0              | TMR2ON                | T2CKPS1               | T2CKPS0              | -000 0000            | 90,200  |

| 13h  | SSPBUF <sup>(5)</sup>    | Synchronou                       | us Serial Port                        | Receive But         | ffer/Transmit       | Register             |                       |                       |                      | xxxx xxxx            | 178,200 |

| 14h  | SSPCON <sup>(5, 6)</sup> | WCOL                             | SSPOV                                 | SSPEN               | CKP                 | SSPM3                | SSPM2                 | SSPM1                 | SSPM0                | 0000 0000            | 177,200 |

| 15h  | CCPR1L <sup>(3)</sup>    | Capture/Co                       | mpare/PWM                             | Register 1 (I       | LSB)                |                      |                       |                       |                      | xxxx xxxx            | 126,200 |

| 16h  | CCPR1H <sup>(3)</sup>    | Capture/Co                       | mpare/PWM                             | Register 1 (I       | MSB)                |                      |                       |                       |                      | xxxx xxxx            | 126,200 |

| 17h  | CCP1CON <sup>(3)</sup>   | P1M1                             | P1M0                                  | DC1B1               | DC1B0               | CCP1M3               | CCP1M2                | CCP1M1                | CCP1M0               | 0000 0000            | 125,200 |

| 18h  | RCSTA <sup>(2)</sup>     | SPEN                             | RX9                                   | SREN                | CREN                | ADDEN                | FERR                  | OERR                  | RX9D                 | 0000 000x            | 158,200 |

| 19h  | TXREG <sup>(2)</sup>     | EUSART T                         | EUSART Transmit Data Register 0000 00 |                     |                     |                      |                       |                       | 0000 0000            | 150                  |         |

| 1Ah  | RCREG <sup>(2)</sup>     | EUSART Receive Data Register 000 |                                       |                     |                     |                      |                       | 0000 0000             | 155                  |                      |         |

| 1Bh  | _                        | Unimplemented —                  |                                       |                     |                     |                      |                       | _                     | _                    |                      |         |

| 1Ch  | PWM1CON <sup>(3)</sup>   | PRSEN                            | PDC6                                  | PDC5                | PDC4                | PDC3                 | PDC2                  | PDC1                  | PDC0                 | 0000 0000            | 143,200 |

| 1Dh  | ECCPAS <sup>(3)</sup>    | ECCPASE                          | ECCPAS2                               | ECCPAS1             | ECCPAS0             | PSSAC1               | PSSAC0                | PSSBD1                | PSSBD0               | 0000 0000            | 140,200 |

| 1Eh  | ADRESH <sup>(4)</sup>    | A/D Result                       | Register Hig                          | h Byte              |                     |                      |                       |                       |                      | xxxx xxxx            | 113,200 |

| 1Fh  | ADCON0 <sup>(4)</sup>    | ADFM                             | VCFG                                  | CHS3                | CHS2                | CHS1                 | CHS0                  | GO/DONE               | ADON                 | 0000 0000            | 111,200 |

| TABLE 2-1: | PIC16F631/677/685/687/689/690 SPECIAL FUNCTION REGISTERS SUMMARY BANK 0 |

|------------|-------------------------------------------------------------------------|

|------------|-------------------------------------------------------------------------|

Legend:- = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplementedNote1:MCLR and WDT Reset do not affect the previous value data latch. The RABIF bit will be cleared upon Reset but will set again if the

mismatch exists.

2: PIC16F687/PIC16F689/PIC16F690 only.

3: PIC16F685/PIC16F690 only.

4: PIC16F677/PIC16F685/PIC16F687/PIC16F689/PIC16F690 only.

5: PIC16F677/PIC16F687/PIC16F689/PIC16F690 only.

6: When SSPCON register bits SSPM<3:0> = 1001, any reads or writes to the SSPADD SFR address are accessed through the SSPMSK register. See Registers 13-2 and 13-3 for more detail.

7: Port pins with analog functions controlled by the ANSEL and ANSELH registers will read '0' immediately after a Reset even though the data latches are either undefined (POR) or unchanged (other Resets).

## 2.2.2.2 OPTION Register

The OPTION register, shown in Register 2-2, is a readable and writable register, which contains various control bits to configure:

- Timer0/WDT prescaler

- External RA2/INT interrupt

- Timer0

- Weak pull-ups on PORTA/PORTB

Note: To achieve a 1:1 prescaler assignment for Timer0, assign the prescaler to the WDT by setting PSA bit of the OPTION register to '1'. See Section 6.3 "Timer1 Prescaler".

## REGISTER 2-2: OPTION\_REG: OPTION REGISTER

| R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|--------|-------|-------|-------|-------|-------|-------|

| RABPU | INTEDG | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   |

| bit 7 |        |       |       |       |       |       | bit 0 |

| Legend:    |                |                                     |                                  |            |                                    |                    |  |  |  |

|------------|----------------|-------------------------------------|----------------------------------|------------|------------------------------------|--------------------|--|--|--|

| R = Reada  | ble bit        | VV = V                              | Writable bit                     |            | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value | at POR         | '1' =                               | Bit is set                       |            | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

|            |                |                                     |                                  |            |                                    |                    |  |  |  |

| bit 7      |                |                                     | ORTB Pull-up                     |            | t                                  |                    |  |  |  |

|            |                |                                     | pull-ups are pull-ups are        |            | y individual PORT latch            | values             |  |  |  |

| bit 6      | INTED          | G: Interrupt E                      | Edge Select b                    | it         |                                    |                    |  |  |  |

|            |                |                                     | ng edge of RA                    |            |                                    |                    |  |  |  |

| bit 5      | T0CS:          | Timer0 Clocl                        | Source Sele                      | ect bit    |                                    |                    |  |  |  |

|            | 1 <b>= Tra</b> | 1 = Transition on RA2/T0CKI pin     |                                  |            |                                    |                    |  |  |  |

|            | 0 = Inte       | rnal instructi                      | on cycle clocl                   | k (Fosc/4) |                                    |                    |  |  |  |

| bit 4      | T0SE:          | Timer0 Sour                         | ce Edge Sele                     | ct bit     |                                    |                    |  |  |  |

|            |                |                                     | •                                |            | RA2/T0CKI pin<br>RA2/T0CKI pin     |                    |  |  |  |

| bit 3      |                | rescaler Ass                        | -                                |            |                                    |                    |  |  |  |

|            |                |                                     | igned to the V<br>igned to the T |            | dule                               |                    |  |  |  |

| bit 2-0    | PS<2:0         | PS<2:0>: Prescaler Rate Select bits |                                  |            |                                    |                    |  |  |  |

|            |                | Bit Value                           | Timer0 Rate                      | WDT Rate   | 9                                  |                    |  |  |  |

|            |                | 000                                 | 1:2                              | 1:1        | -                                  |                    |  |  |  |

|            |                | 001                                 | 1:4                              | 1:2        |                                    |                    |  |  |  |

|            |                | 010<br>011                          | 1:8<br>1:16                      | 1:4<br>1:8 |                                    |                    |  |  |  |

|            |                |                                     |                                  | 1          |                                    |                    |  |  |  |

100

101

110 111 1:32

1 : 64 1 : 128

1:256

1:16 1:32

1:64

1:128

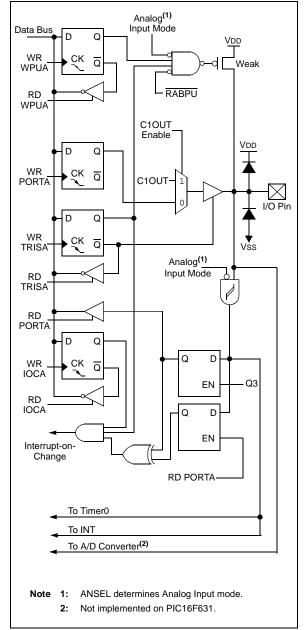

## 4.2.5.2 RA1/AN1/C12IN0-/VREF/ICSPCLK

Figure 4-2 shows the diagram for this pin. The RA1/ AN1/C12IN0-/VREF/ICSPCLK pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC (except PIC16F631)

- an analog input to Comparator C1 or C2

- a voltage reference input for the ADC

- In-Circuit Serial Programming clock

#### **BLOCK DIAGRAM OF RA1** FIGURE 4-2: Analog(1) Input Mode Data Bus D Q VDD WR CK Q Weak WPU RABPU RD WPU/ Vdd D Q WR СК Q PORTA I/O Pin D G Vss WR СК Q TRIS Analog<sup>(1)</sup> Input Mode RD TRIS/ RD PORT/ D Q D Q WR Q IOCA ΕN Q3 RD IOCA Q D ΕN Interrupt-on-Change **RD PORTA** To Comparator To A/D Converter(2) ANSEL determines Analog Input mode. Note 1: Not implemented on PIC16F631. 2:

## 4.2.5.3 RA2/AN2/T0CKI/INT/C1OUT

Figure 4-3 shows the diagram for this pin. The RA2/AN2/ T0CKI/INT/C1OUT pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC (except PIC16F631)

- the clock input for Timer0

- an external edge triggered interrupt

- a digital output from Comparator C1

## FIGURE 4-3: BLOCK DIAGRAM OF RA2

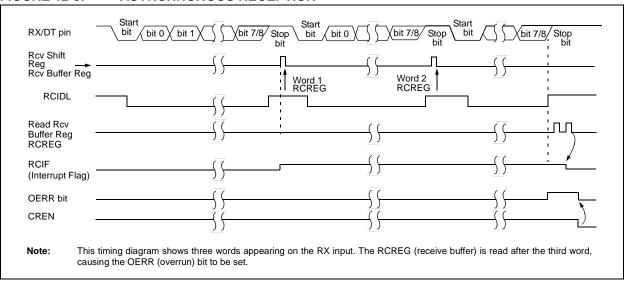

### 12.1.2.8 Asynchronous Reception Set-up:

- Initialize the SPBRGH, SPBRG register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 12.3 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. If 9-bit reception is desired, set the RX9 bit.

- 5. Enable reception by setting the CREN bit.

- 6. The RCIF interrupt flag bit will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 7. Read the RCSTA register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

- 8. Get the received 8 Least Significant data bits from the receive buffer by reading the RCREG register.

- 9. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

### 12.1.2.9 9-bit Address Detection Mode Set-up

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPBRGH, SPBRG register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 12.3 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. Enable 9-bit reception by setting the RX9 bit.

- 5. Enable address detection by setting the ADDEN bit.

- 6. Enable reception by setting the CREN bit.

- 7. The RCIF interrupt flag bit will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 8. Read the RCSTA register to get the error flags. The ninth data bit will always be set.

- 9. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register. Software determines if this is the device's address.

- 10. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 11. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

## FIGURE 12-5: ASYNCHRONOUS RECEPTION

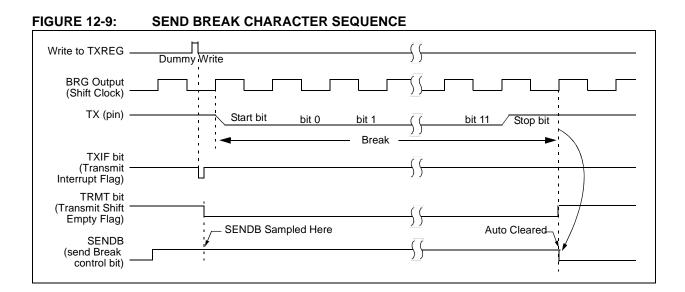

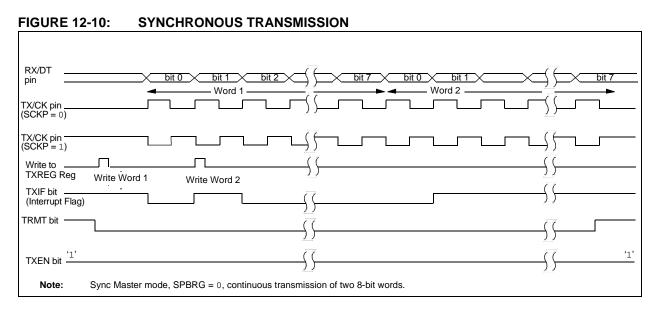

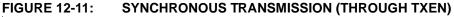

### TABLE 12-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Name    | Bit 7                         | Bit 6      | Bit 5       | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-------------------------------|------------|-------------|--------|-------|--------|--------|--------|----------------------|---------------------------------|

| BAUDCTL | ABDOVF                        | RCIDL      | _           | SCKP   | BRG16 | _      | WUE    | ABDEN  | 01-0 0-00            | 01-0 0-00                       |

| INTCON  | GIE                           | PEIE       | TOIE        | INTE   | RABIE | T0IF   | INTF   | RABIF  | 0000 000x            | 0000 000x                       |

| PIE1    | _                             | ADIE       | RCIE        | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | -000 0000            | -000 0000                       |

| PIR1    | _                             | ADIF       | RCIF        | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | -000 0000            | -000 0000                       |

| RCREG   | EUSART F                      | Receive Da | ta Register |        |       |        |        |        | 0000 0000            | 0000 0000                       |

| RCSTA   | SPEN                          | RX9        | SREN        | CREN   | ADDEN | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| SPBRG   | BRG7                          | BRG6       | BRG5        | BRG4   | BRG3  | BRG2   | BRG1   | BRG0   | 0000 0000            | 0000 0000                       |

| SPBRGH  | BRG15                         | BRG14      | BRG13       | BRG12  | BRG11 | BRG10  | BRG9   | BRG8   | 0000 0000            | 0000 0000                       |

| TRISB   | TRISB7                        | TRISB6     | TRISB5      | TRISB4 |       |        |        |        | 1111                 | 1111                            |

| TXREG   | EUSART Transmit Data Register |            |             |        |       |        |        |        | 0000 0000            | 0000 0000                       |

| TXSTA   | CSRC                          | TX9        | TXEN        | SYNC   | SENDB | BRGH   | TRMT   | TX9D   | 0000 0010            | 0000 0010                       |

| Logond: | erand:upknownupknownupknown   |            |             |        |       |        |        |        |                      |                                 |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Master Transmission.

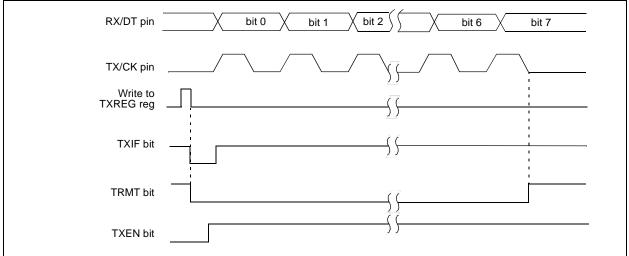

#### 14.2 Reset

The PIC16F631/677/685/687/689/690 differentiates between various kinds of Reset:

- a) Power-on Reset (POR)

- b) WDT Reset during normal operation

- WDT Reset during Sleep C)

- MCLR Reset during normal operation d)

- e) MCLR Reset during Sleep

- f) Brown-out Reset (BOR)

Some registers are not affected in any Reset condition; their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on:

- · Power-on Reset

- MCLR Reset

- MCLR Reset during Sleep

- WDT Reset

**FIGURE 14-1:**

Brown-out Reset (BOR)

They are not affected by a WDT Wake-up since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different Reset situations, as indicated in Table 14-2. These bits are used in software to determine the nature of the Reset. See Table 14-4 for a full description of Reset states of all registers.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 14-1.

The MCLR Reset path has a noise filter to detect and ignore small pulses. See Section 17.0 "Electrical Specifications" for pulse-width specifications.

## External Reset MCLR/VPP pin

SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

## 14.2.1 POWER-ON RESET (POR)

The on-chip POR circuit holds the chip in Reset until VDD has reached a high enough level for proper operation. A maximum rise time for VDD is required. See **Section 17.0 "Electrical Specifications"** for details. If the BOR is enabled, the maximum rise time specification does not apply. The BOR circuitry will keep the device in Reset until VDD reaches VBOR (see **Section 14.2.4** "**Brown-out Reset (BOR)**").

Note: The POR circuit does not produce an internal Reset when VDD declines. To reenable the POR, VDD must reach Vss for a minimum of 100 μs.

When the device starts normal operation (exits the Reset condition), device operating parameters (i.e., voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

For additional information, refer to Application Note AN607, *"Power-up Trouble Shooting"* (DS00607).

## 14.2.2 MCLR

$\mathsf{PIC16F631}/677/685/687/689/690$  has a noise filter in the  $\overline{\mathsf{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive  $\overline{\text{MCLR}}$  pin low.

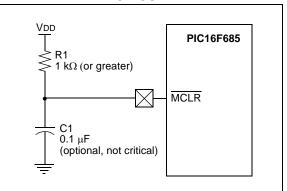

The behavior of the ESD protection on the MCLR pin has been altered from early devices of this family. Voltages applied to the pin that exceed its specification can result in both MCLR Resets and excessive current beyond the device specification during the ESD event. For this reason, Microchip recommends that the MCLR pin no longer be tied directly to VDD. The use of an RC network, as shown in Figure 14-2, is suggested.

An internal  $\overline{\text{MCLR}}$  option is enabled by clearing the  $\overline{\text{MCLRE}}$  bit in the Configuration Word register. When  $\overline{\text{MCLRE}} = 0$ , the Reset signal to the chip is generated internally. When the  $\overline{\text{MCLRE}} = 1$ , the RA3/MCLR pin becomes an external Reset input. In this mode, the RA3/MCLR pin has a weak pull-up to VDD. However, for robustness in noisy environments, the circuit shown in Figure 14-2 is still recommended.

### FIGURE 14-2:

###

## 14.2.3 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 64 ms (nominal) time-out on power-up only, from POR or Brown-out Reset. The Power-up Timer operates from the 31 kHz LFINTOSC oscillator. For more information, see **Section 3.5 "Internal Clock Modes"**. The chip is kept in Reset as long as PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level. A Configuration bit, PWRTE, can disable (if set) or enable (if cleared or programmed) the Power-up Timer. The Power-up Timer should be enabled when Brown-out Reset is enabled, although it is not required.

The Power-up Timer delay will vary from chip-to-chip and vary due to:

- VDD variation

- Temperature variation

- Process variation

See DC parameters for details (Section 17.0 "Electrical Specifications").

| Register   | Address               | Power-on Reset | MCLR Reset<br>WDT Reset<br>Brown-out Reset <sup>(1)</sup> | Wake-up from Sleep<br>through Interrupt<br>Wake-up from Sleep<br>through WDT Time-out |

|------------|-----------------------|----------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------|

| W          | —                     | XXXX XXXX      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| INDF       | 00h/80h/<br>100h/180h | XXXX XXXX      | XXXX XXXX                                                 | սսսս սսսս                                                                             |

| TMR0       | 01h/101h              | xxxx xxxx      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| PCL        | 02h/82h/<br>102h/182h | 0000 0000      | 0000 0000                                                 | PC + 1 <sup>(3)</sup>                                                                 |

| STATUS     | 03h/83h/<br>103h/183h | 0001 1xxx      | 000q quuu <sup>(4)</sup>                                  | uuuq quuu <sup>(4)</sup>                                                              |

| FSR        | 04h/84h/<br>104h184h  | XXXX XXXX      | սսսս սսսս                                                 | นนนน นนนน                                                                             |

| PORTA      | 05h/105h              | xx xxxx        | uu uuuu                                                   | uu uuuu                                                                               |

| PORTB      | 06h/106h              | xxxx           | uuuu                                                      | uuuu                                                                                  |

| PORTC      | 07h/107h              | XXXX XXXX      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| PCLATH     | 0Ah/8Ah/<br>10Ah/18Ah | 0 0000         | 0 0000                                                    | u uuuu                                                                                |

| INTCON     | 0Bh/8Bh/<br>10Bh/18Bh | 0000 000x      | 0000 000u                                                 | uuuu uuuu <sup>(2)</sup>                                                              |

| PIR1       | 0Ch                   | -000 0000      | -000 0000                                                 | -uuu uuuu <sup>(2)</sup>                                                              |

| PIR2       | 0Dh                   | 0000           | 0000                                                      | uuuu <b>(2)</b>                                                                       |

| TMR1L      | 0Eh                   | xxxx xxxx      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| TMR1H      | 0Fh                   | XXXX XXXX      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| T1CON      | 10h                   | 0000 0000      | uuuu uuuu                                                 | <u>uuuu</u> uuuu                                                                      |

| TMR2       | 11h                   | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                             |

| T2CON      | 12h                   | -000 0000      | -000 0000                                                 | -uuu uuuu                                                                             |

| SSPBUF     | 13h                   | xxxx xxxx      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| SSPCON     | 14h                   | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                             |

| CCPR1L     | 15h                   | xxxx xxxx      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| CCPR1H     | 16h                   | xxxx xxxx      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| CCP1CON    | 17h                   | 0000 0000      | 0000 0000                                                 | սսսս սսսս                                                                             |

| RCSTA      | 18h                   | 0000 000x      | 0000 000x                                                 | uuuu uuuu                                                                             |

| TXREG      | 19h                   | 0000 0000      | 0000 0000                                                 | սսսս սսսս                                                                             |

| RCREG      | 1Ah                   | 0000 0000      | 0000 0000                                                 | սսսս սսսս                                                                             |

| PWM1CON    | 1Ch                   | 0000 0000      | 0000 0000                                                 | սսսս սսսս                                                                             |

| ECCPAS     | 1Dh                   | 0000 0000      | 0000 0000                                                 | սսսս սսսս                                                                             |

| ADRESH     | 1Eh                   | xxxx xxxx      | uuuu uuuu                                                 | սսսս սսսս                                                                             |

| ADCON0     | 1Fh                   | 0000 0000      | 0000 0000                                                 | սսսս սսսս                                                                             |

| OPTION_REG | 81h/181h              | 1111 1111      | 1111 1111                                                 | սսսս սսսս                                                                             |

| TRISA      | 85h/185h              | 11 1111        | 11 1111                                                   | uu uuuu                                                                               |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

3: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

4: See Table 14-5 for Reset value for specific condition.

5: If Reset was due to brown-out, then bit 0 = 0. All other Resets will cause bit 0 = u.

**6:** Accessible only when SSPM < 3:0 > = 1001.

| Condition                          | Program<br>Counter    | Status<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 010x             |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | 0uuu             |

| MCLR Reset during Sleep            | 000h                  | 0001 Ouuu          | 0uuu             |

| WDT Reset                          | 000h                  | 0000 uuuu          | 0uuu             |

| WDT Wake-up                        | PC + 1                | uuu0 Ouuu          | uuuu             |

| Brown-out Reset                    | 000h                  | 0001 luuu          | 01u0             |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | uuuu             |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Interrupt Enable bit, GIE, is set, the PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

## 14.3 Interrupts

The PIC16F631/677/685/687/689/690 have multiple sources of interrupt:

- External Interrupt RA2/INT

- TMR0 Overflow Interrupt

- PORTA/PORTB Change Interrupts

- 2 Comparator Interrupts

- A/D Interrupt (except PIC16F631)

- Timer1 Overflow Interrupt

- Timer2 Match Interrupt (PIC16F685/PIC16F690 only)

- EEPROM Data Write Interrupt

- Fail-Safe Clock Monitor Interrupt

- Enhanced CCP Interrupt (PIC16F685/PIC16F690 only)

- EUSART Receive and Transmit interrupts (PIC16F687/PIC16F689/PIC16F690 only)

The Interrupt Control register (INTCON) and Peripheral Interrupt Request Register 1 (PIR1) record individual interrupt requests in flag bits. The INTCON register also has individual and global interrupt enable bits.

A Global Interrupt Enable bit, GIE (INTCON<7>), enables (if set) all unmasked interrupts, or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in the INTCON, PIE1 and PIE2 registers, respectively. GIE is cleared on Reset.

The Return from Interrupt instruction, RETFIE, exits the interrupt routine, as well as sets the GIE bit, which re-enables unmasked interrupts.

The following interrupt flags are contained in the INTCON register:

- INT Pin Interrupt

- PORTA/PORTB Change Interrupts

- TMR0 Overflow Interrupt

The peripheral interrupt flags are contained in the PIR1 and PIR2 registers. The corresponding interrupt enable bits are contained in PIE1 and PIE2 registers.

The following interrupt flags are contained in the PIR1 register:

- A/D Interrupt

- EUSART Receive and Transmit Interrupts

- Timer1 Overflow Interrupt

- Synchronous Serial Port (SSP) Interrupt

- Enhanced CCP1 Interrupt

- Timer1 Overflow Interrupt

- Timer2 Match Interrupt

The following interrupt flags are contained in the PIR2 register:

- Fail-Safe Clock Monitor Interrupt

- 2 Comparator Interrupts

- EEPROM Data Write Interrupt

When an interrupt is serviced:

- The GIE is cleared to disable any further interrupt.

- The return address is pushed onto the stack.

- The PC is loaded with 0004h.

For external interrupt events, such as the INT pin, PORTA/PORTB change interrupts, the interrupt latency will be three or four instruction cycles. The exact latency depends upon when the interrupt event occurs (see Figure 14-8). The latency is the same for one or 2-cycle instructions. Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests.

Note 1: Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit or the GIE bit.

2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The interrupts, which were ignored, are still pending to be serviced when the GIE bit is set again.

For additional information on Timer1, Timer2, comparators, A/D, data EEPROM, EUSART, SSP or Enhanced CCP modules, refer to the respective peripheral section.

## 14.3.1 RA2/INT INTERRUPT

External interrupt on RA2/INT pin is edge-triggered; either rising if the INTEDG bit (OPTION\_REG<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the RA2/INT pin, the INTF bit (INTCON<1>) is set. This interrupt can be disabled by clearing the INTE control bit (INTCON<4>). The INTF bit must be cleared in software in the Interrupt Service Routine before re-enabling this interrupt. The RA2/INT interrupt can wake-up the processor from Sleep, if the INTE bit was set prior to going into Sleep. The status of the GIE bit decides whether or not the processor branches to the interrupt vector following wake-up (0004h). See Section 14.6 "Power-Down Mode (Sleep)" for details on Sleep and Figure 14-10 for timing of wake-up from Sleep through RA2/INT interrupt.

Note: The ANSEL and CM2CON0 registers must be initialized to configure an analog channel as a digital input. Pins configured as analog inputs will read '0'.

| SUBWF            | Subtract W                                                                                                                                                                                 | from f   |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|--|

| Syntax:          | [label] SU                                                                                                                                                                                 | JBWF f,d |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                          |          |  |  |  |

| Operation:       | (f) - (W) $\rightarrow$ (destination)                                                                                                                                                      |          |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                                   |          |  |  |  |

| Description:     | Subtract (2's complement method<br>W register from register 'f'. If 'd' is<br>'0', the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |          |  |  |  |

|                  | <b>C</b> = 0                                                                                                                                                                               | W > f    |  |  |  |

**C** = 1

DC = 0

**DC** = 1

$W \leq f$

W<3:0> > f<3:0>

W<3:0> ≤ f<3:0>

| XORLW            | Exclusive OR literal with W                                                                                            |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                               |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                      |  |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                          |  |  |  |  |

| Status Affected: | Z                                                                                                                      |  |  |  |  |

| Description:     | The contents of the W register<br>are XOR'ed with the 8-bit<br>literal 'k'. The result is placed in<br>the W register. |  |  |  |  |

| SWAPF            | Swap Nibbles in f                                                                                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SWAPF f,d                                                                                                                                                      |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                            |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                |

| Status Affected: | None                                                                                                                                                                   |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed in register 'f'. |

| XORWF            | Exclusive OR W with f                                                                                                                                                           |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] XORWF f,d                                                                                                                                                               |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                 |  |  |  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                       |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                               |  |  |  |  |  |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |  |  |  |  |  |  |

## 17.3 DC Characteristics: PIC16F631/677/685/687/689/690-E (Extended)

| DC CHARACTERISTICS |                             |      | rd Opera<br>ng tempe |      | ditions (unless otherwise stated)<br>-40°C $\leq$ TA $\leq$ +85°C for industrial<br>-40°C $\leq$ TA $\leq$ +125°C for extended |            |                                               |  |

|--------------------|-----------------------------|------|----------------------|------|--------------------------------------------------------------------------------------------------------------------------------|------------|-----------------------------------------------|--|

| Param              | Device Characteristics      | Min. | Тур†                 | Max. | Units                                                                                                                          | Conditions |                                               |  |

| No.                |                             |      |                      |      |                                                                                                                                | Vdd        | Note                                          |  |

| D020E              | Power-down Base             |      | 0.05                 | 9    | μA                                                                                                                             | 2.0        | WDT, BOR, Comparators, VREF and               |  |

|                    | Current(IPD) <sup>(2)</sup> |      | 0.15                 | 11   | μA                                                                                                                             | 3.0        | T1OSC disabled                                |  |

|                    |                             |      | 0.35                 | 15   | μA                                                                                                                             | 5.0        |                                               |  |

|                    |                             |      | 90                   | 500  | nA                                                                                                                             | 3.0        | $-40^{\circ}C \le TA \le +25^{\circ}C$        |  |

| D021E              |                             | _    | 1.0                  | 17.5 | μA                                                                                                                             | 2.0        | WDT Current <sup>(1)</sup>                    |  |

|                    |                             |      | 2.0                  | 19   | μA                                                                                                                             | 3.0        |                                               |  |

|                    |                             | —    | 3.0                  | 22   | μA                                                                                                                             | 5.0        |                                               |  |

| D022E              |                             | _    | 42                   | 65   | μA                                                                                                                             | 3.0        | BOR Current <sup>(1)</sup>                    |  |

|                    |                             |      | 85                   | 127  | μA                                                                                                                             | 5.0        |                                               |  |

| D023E              |                             | —    | 32                   | 45   | μA                                                                                                                             | 2.0        | Comparator Current <sup>(1)</sup> , both      |  |

|                    |                             | —    | 60                   | 78   | μA                                                                                                                             | 3.0        | comparators enabled                           |  |

|                    |                             | —    | 120                  | 160  | μA                                                                                                                             | 5.0        |                                               |  |

| D024E              |                             | —    | 30                   | 70   | μA                                                                                                                             | 2.0        | CVREF Current <sup>(1)</sup> (high range)     |  |

|                    |                             | —    | 45                   | 90   | μΑ                                                                                                                             | 3.0        |                                               |  |

|                    |                             | —    | 75                   | 120  | μΑ                                                                                                                             | 5.0        |                                               |  |

| D024AE*            |                             | —    | 39                   | 91   | μA                                                                                                                             | 2.0        | CVREF Current <sup>(1)</sup> (low range)      |  |

|                    |                             | —    | 59                   | 117  | μΑ                                                                                                                             | 3.0        |                                               |  |

|                    |                             | —    | 98                   | 156  | μA                                                                                                                             | 5.0        |                                               |  |

| D025E              |                             |      | 2.0                  | 18   | μΑ                                                                                                                             | 2.0        | T1OSC Current                                 |  |

|                    |                             |      | 2.5                  | 21   | μΑ                                                                                                                             | 3.0        |                                               |  |

|                    |                             |      | 3.0                  | 24   | μA                                                                                                                             | 5.0        |                                               |  |

| D026E              |                             |      | 0.30                 | 12   | μΑ                                                                                                                             | 3.0        | A/D Current <sup>(1)</sup> , no conversion in |  |

|                    |                             | —    | 0.36                 | 16   | μA                                                                                                                             | 5.0        | progress                                      |  |

| D027E              |                             | —    | 90                   | 130  | μA                                                                                                                             | 3.0        | VP6 Current                                   |  |

|                    |                             | _    | 125                  | 170  | μΑ                                                                                                                             | 5.0        |                                               |  |

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The test conditions for all IDD measurements in Active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

**3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in kΩ.

4: The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral ∆ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

5: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

## 17.4 DC Characteristics: PIC16F631/677/685/687/689/690-I (Industrial) PIC16F631/677/685/687/689/690-E (Extended)

| DC CHARACTERISTICS |                    | Standard Operat                            | ditions (unless otherwise stated)<br>-40°C $\leq$ TA $\leq$ +85°C for industrial<br>-40°C $\leq$ TA $\leq$ +125°C for extended |       |          |       |                                                                                                     |

|--------------------|--------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------|----------|-------|-----------------------------------------------------------------------------------------------------|

| Param<br>No.       | Sym Characteristic |                                            | Min.                                                                                                                           | Тур†  | Max.     | Units | Conditions                                                                                          |

|                    | VIL                | Input Low Voltage                          |                                                                                                                                |       |          |       |                                                                                                     |

|                    |                    | I/O Port:                                  |                                                                                                                                |       |          |       |                                                                                                     |

| D030               |                    | with TTL buffer                            | Vss                                                                                                                            | —     | 0.8      | V     | $4.5V \leq V \text{DD} \leq 5.5V$                                                                   |

| D030A              |                    |                                            | Vss                                                                                                                            | —     | 0.15 Vdd | V     | $2.0V \leq V\text{DD} \leq 4.5V$                                                                    |

| D031               |                    | with Schmitt Trigger buffer                | Vss                                                                                                                            | —     | 0.2 Vdd  | V     | $2.0V \le VDD \le 5.5V$                                                                             |

| D032               |                    | MCLR, OSC1 (RC mode) <sup>(1)</sup>        | Vss                                                                                                                            | —     | 0.2 Vdd  | V     |                                                                                                     |

| D033               |                    | OSC1 (XT and LP modes)                     | Vss                                                                                                                            | _     | 0.3      | V     |                                                                                                     |

| D033A              |                    | OSC1 (HS mode)                             | Vss                                                                                                                            | —     | 0.3 Vdd  | V     |                                                                                                     |

|                    | VIH                | Input High Voltage                         |                                                                                                                                |       |          |       |                                                                                                     |

|                    |                    | I/O Ports:                                 |                                                                                                                                | _     |          |       |                                                                                                     |

| D040               |                    | with TTL buffer                            | 2.0                                                                                                                            | _     | Vdd      | V     | $4.5V \le VDD \le 5.5V$                                                                             |

| D040A              |                    |                                            | 0.25 VDD + 0.8                                                                                                                 | —     | Vdd      | V     | $2.0V \le VDD \le 4.5V$                                                                             |

| D041               |                    | with Schmitt Trigger buffer                | 0.8 Vdd                                                                                                                        | _     | Vdd      | V     | $2.0V \le VDD \le 5.5V$                                                                             |

| D042               |                    | MCLR                                       | 0.8 Vdd                                                                                                                        | _     | Vdd      | V     |                                                                                                     |

| D043               |                    | OSC1 (XT and LP modes)                     | 1.6                                                                                                                            | _     | Vdd      | V     |                                                                                                     |

| D043A              |                    | OSC1 (HS mode)                             | 0.7 Vdd                                                                                                                        | —     | Vdd      | V     |                                                                                                     |

| D043B              |                    | OSC1 (RC mode)                             | 0.9 Vdd                                                                                                                        | _     | Vdd      | V     | (Note 1)                                                                                            |

|                    | lı∟                | Input Leakage Current <sup>(2)</sup>       |                                                                                                                                |       |          |       |                                                                                                     |

| D060               |                    | I/O ports                                  | _                                                                                                                              | ± 0.1 | ± 1      | μA    | $Vss \le VPIN \le VDD,$ Pin at high-impedance                                                       |

| D061               |                    | MCLR <sup>(3)</sup>                        | —                                                                                                                              | ± 0.1 | ± 5      | μA    | $VSS \leq VPIN \leq VDD$                                                                            |

| D063               |                    | OSC1                                       | _                                                                                                                              | ± 0.1 | ± 5      | μA    | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP oscillator configuration                                  |

| D070*              | IPUR               | PORTA Weak Pull-up Current                 | 50                                                                                                                             | 250   | 400      | μΑ    | VDD = 5.0V, VPIN = VSS                                                                              |

|                    | Vol                | Output Low Voltage <sup>(5)</sup>          |                                                                                                                                |       |          |       |                                                                                                     |

| D080               |                    | I/O ports                                  | —                                                                                                                              | —     | 0.6      | V     | IOL = 8.5 mA, VDD = 4.5V (Ind.)                                                                     |

|                    | Voh                | Output High Voltage <sup>(5)</sup>         |                                                                                                                                |       |          |       |                                                                                                     |

| D090               |                    | I/O ports                                  | Vdd - 0.7                                                                                                                      | -     | —        | V     | IOH = -3.0 mA, VDD = 4.5V (Ind.)                                                                    |

| D100               | IULP               | Ultra Low-Power Wake-up<br>Current         | _                                                                                                                              | 200   | _        | nA    | See Application Note AN879,<br>"Using the Microchip Ultra<br>Low-Power Wake-up Module"<br>(DS00879) |

|                    |                    | Capacitive Loading Specs on<br>Output Pins |                                                                                                                                |       |          |       |                                                                                                     |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

2: Negative current is defined as current sourced by the pin.

3: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

4: See Section 10.2.1 "Using the Data EEPROM" for additional information.

5: Including OSC2 in CLKOUT mode.

## 17.6 Timing Parameter Symbology

The timing parameter symbols have been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

| 2. Tpp5 |                                       | i   |                |  |

|---------|---------------------------------------|-----|----------------|--|

| т       |                                       |     |                |  |

| F       | Frequency                             | Т   | Time           |  |

| Lowerc  | case letters (pp) and their meanings: |     |                |  |

| рр      |                                       |     |                |  |

| сс      | CCP1                                  | OSC | OSC1           |  |

| ck      | CLKOUT                                | rd  | RD             |  |

| CS      | CS                                    | rw  | RD or WR       |  |

| di      | SDI                                   | sc  | SCK            |  |

| do      | SDO                                   | SS  | SS             |  |

| dt      | Data in                               | tO  | TOCKI          |  |

| io      | I/O Port                              | t1  | T1CKI          |  |

| mc      | MCLR                                  | wr  | WR             |  |

| Upperc  | case letters and their meanings:      |     |                |  |

| S       |                                       |     |                |  |

| F       | Fall                                  | Р   | Period         |  |

| н       | High                                  | R   | Rise           |  |

| I       | Invalid (High-impedance)              | V   | Valid          |  |

| L       | Low                                   | Z   | High-impedance |  |

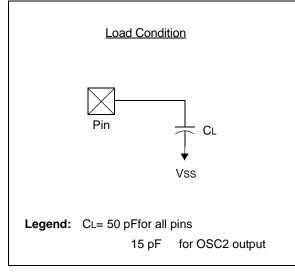

### FIGURE 17-3: LOAD CONDITIONS

## TABLE 17-2: OSCILLATOR PARAMETERS

| Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                                   |                                                        |                    |      |      |      |                                                                   |                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------------------------------------------------|--------------------|------|------|------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.                                                                                                         | Sym.                              | Characteristic                                         | Freq.<br>Tolerance | Min. | Тур† | Max. | Units                                                             | Conditions                                                                                                                                                                      |