# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                         |

| Number of I/O              | 18                                                                       |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 64 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 20-SSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f631-i-ss |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## PIC16F685 Pin Diagram

| 20-pin PDIP, SOIC, SSOP                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $VDD \longrightarrow \begin{bmatrix} 1\\ RA5/T1CKI/OSC1/CLKIN & \\ 2\\ RA4/AN3/T1G/OSC2/CLKOUT & \\ 3\\ RA3/MCLR/VPP \longrightarrow \begin{bmatrix} 4\\ RC5/CCP1/P1A & \\ 5\\ RC4/C2OUT/P1B & \\ 6\\ RC3/AN7/C12IN3-/P1C & \\ 7\\ RC6/AN8 & \\ 8\\ RC7/AN9 & \\ 9\\ RB7 & \\ 10\\ \end{bmatrix}$ | 20<br>4 Vss<br>19<br>4 RA0/AN0/C1IN+/ICSPDAT/ULPWU<br>18<br>4 RA1/AN1/C12IN0-/VREF/ICSPCLK<br>50<br>17<br>4 RA2/AN2/T0CKI/INT/C1OUT<br>16<br>4 RC0/AN4/C2IN+<br>15<br>4 RC0/AN4/C2IN+<br>15<br>4 RC1/AN5/C12IN1-<br>14<br>4 RC2/AN6/C12IN2-/P1D<br>13<br>4 RB4/AN10<br>12<br>4 RB5/AN11<br>11<br>4 RB6 |

#### TABLE 3: PIC16F685 PIN SUMMARY

| I/O | Pin | Analog    | Comparators | Timers | ECCP     | Interrupt | Pull-up | Basic       |

|-----|-----|-----------|-------------|--------|----------|-----------|---------|-------------|

| RA0 | 19  | AN0/ULPWU | C1IN+       | _      | _        | IOC       | Y       | ICSPDAT     |

| RA1 | 18  | AN1/VREF  | C12IN0-     | _      | —        | IOC       | Y       | ICSPCLK     |

| RA2 | 17  | AN2       | C1OUT       | T0CKI  | —        | IOC/INT   | Y       | —           |

| RA3 | 4   | —         | —           | _      | —        | IOC       | Y(1)    | MCLR/Vpp    |

| RA4 | 3   | AN3       | —           | T1G    | —        | IOC       | Y       | OSC2/CLKOUT |

| RA5 | 2   |           | —           | T1CKI  | —        | IOC       | Y       | OSC1/CLKIN  |

| RB4 | 13  | AN10      | —           | —      | —        | IOC       | Y       | —           |

| RB5 | 12  | AN11      | —           |        | —        | IOC       | Y       | —           |

| RB6 | 11  |           | —           |        | —        | IOC       | Y       | —           |

| RB7 | 10  |           | —           |        | _        | IOC       | Y       | —           |

| RC0 | 16  | AN4       | C2IN+       | —      | _        |           |         | —           |

| RC1 | 15  | AN5       | C12IN1-     |        | _        |           |         | —           |

| RC2 | 14  | AN6       | C12IN2-     |        | P1D      |           |         | —           |

| RC3 | 7   | AN7       | C12IN3-     | _      | P1C      |           |         | —           |

| RC4 | 6   |           | C2OUT       | _      | P1B      |           |         | —           |

| RC5 | 5   | _         | —           | _      | CCP1/P1A |           | _       | —           |

| RC6 | 8   | AN8       | —           | —      | —        | _         | —       | —           |

| RC7 | 9   | AN9       |             |        | _        | _         | _       | —           |

| —   | 1   |           | _           |        |          | _         | _       | Vdd         |

| —   | 20  |           | _           | _      | _        | _         | _       | Vss         |

**Note 1:** Pull-up activated only with external MCLR configuration.

## 3.3 Clock Source Modes

Clock Source modes can be classified as external or internal.

- External Clock modes rely on external circuitry for the clock source. Examples are: Oscillator modules (EC mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes) and Resistor-Capacitor (RC) mode circuits.

- Internal clock sources are contained internally within the Oscillator module. The Oscillator module has two internal oscillators: the 8 MHz High-Frequency Internal Oscillator (HFINTOSC) and the 31 kHz Low-Frequency Internal Oscillator (LFINTOSC).

The system clock can be selected between external or internal clock sources via the System Clock Select (SCS) bit of the OSCCON register. See **Section 3.6 "Clock Switching"** for additional information.

### 3.4 External Clock Modes

### 3.4.1 OSCILLATOR START-UP TIMER (OST)

If the Oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) counts 1024 oscillations from OSC1. This occurs following a Power-on Reset (POR) and when the Power-up Timer (PWRT) has expired (if configured), or a wake-up from Sleep. During this time, the program counter does not increment and program execution is suspended. The OST ensures that the oscillator circuit, using a quartz crystal resonator or ceramic resonator, has started and is providing a stable system clock to the Oscillator module. When switching between clock sources, a delay is required to allow the new clock to stabilize. These oscillator delays are shown in Table 3-1.

In order to minimize latency between external oscillator start-up and code execution, the Two-Speed Clock Start-up mode can be selected (see Section 3.7 "Two-Speed Clock Start-up Mode").

| Switch From       | Switch To            | Frequency                  | Oscillator Delay                |  |

|-------------------|----------------------|----------------------------|---------------------------------|--|

| Sleep/POR         | LFINTOSC<br>HFINTOSC | 31 kHz<br>125 kHz to 8 MHz | Oscillator Warm-up Delay (TWARM |  |

| Sleep/POR         | EC, RC               | DC – 20 MHz                | 2 cycles                        |  |

| LFINTOSC (31 kHz) | EC, RC               | DC – 20 MHz                | 1 cycle of each                 |  |

| Sleep/POR         | LP, XT, HS           | 32 kHz to 20 MHz           | 1024 Clock Cycles (OST)         |  |

| LFINTOSC (31 kHz) | HFINTOSC             | 125 kHz to 8 MHz           | 1 μs (approx.)                  |  |

#### TABLE 3-1: OSCILLATOR DELAY EXAMPLES

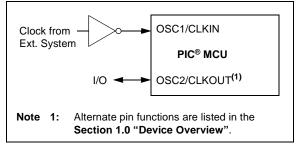

#### 3.4.2 EC MODE

The External Clock (EC) mode allows an externally generated logic level as the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input and the OSC2 is available for general purpose I/O. Figure 3-2 shows the pin connections for EC mode.

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

#### FIGURE 3-2:

#### EXTERNAL CLOCK (EC) MODE OPERATION

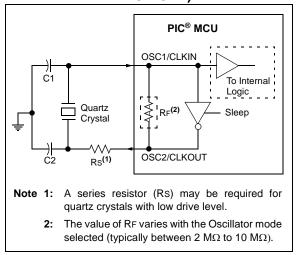

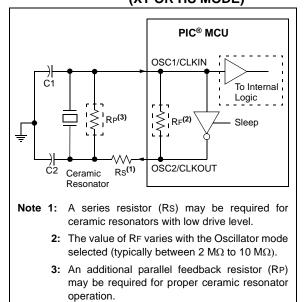

### 3.4.3 LP, XT, HS MODES

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 3-3). The mode selects a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

LP Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 3-3 and Figure 3-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

- **Note 1:** Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- **2:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC<sup>®</sup> Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

## FIGURE 3-3: QUARTZ CRYSTAL

#### OPERATION (LP, XT OR HS MODE)

#### CERAMIC RESONATOR OPERATION (XT OR HS MODE)

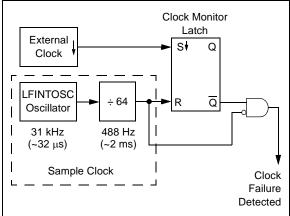

## 3.8 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the device to continue operating should the external oscillator fail. The FSCM can detect oscillator failure any time after the Oscillator Start-up Timer (OST) has expired. The FSCM is enabled by setting the FCMEN bit in the Configuration Word register (CONFIG). The FSCM is applicable to all external Oscillator modes (LP, XT, HS, EC, RC and RCIO).

FIGURE 3-8: FSCM BLOCK DIAGRAM

### 3.8.1 FAIL-SAFE DETECTION

The FSCM module detects a failed oscillator by comparing the external oscillator to the FSCM sample clock. The sample clock is generated by dividing the LFINTOSC by 64. See Figure 3-8. Inside the fail detector block is a latch. The external clock sets the latch on each falling edge of the external clock. The sample clock clears the latch on each rising edge of the sample clock. A failure is detected when an entire half-cycle of the sample clock elapses before the primary clock goes low.

### 3.8.2 FAIL-SAFE OPERATION

When the external clock fails, the FSCM switches the device clock to an internal clock source and sets the bit flag OSFIF of the PIR2 register. Setting this flag will generate an interrupt if the OSFIE bit of the PIE2 register is also set. The device firmware can then take steps to mitigate the problems that may arise from a failed clock. The system clock will continue to be sourced from the internal clock source until the device firmware successfully restarts the external oscillator and switches back to external operation.

The internal clock source chosen by the FSCM is determined by the IRCF<2:0> bits of the OSCCON register. This allows the internal oscillator to be configured before a failure occurs.

### 3.8.3 FAIL-SAFE CONDITION CLEARING

The Fail-Safe condition is cleared after a Reset, executing a SLEEP instruction or toggling the SCS bit of the OSCCON register. When the SCS bit is toggled, the OST is restarted. While the OST is running, the device continues to operate from the INTOSC selected in OSCCON. When the OST times out, the Fail-Safe condition is cleared and the device will be operating from the external clock source. The Fail-Safe condition must be cleared before the OSFIF flag can be cleared.

#### 3.8.4 RESET OR WAKE-UP FROM SLEEP

The FSCM is designed to detect an oscillator failure after the Oscillator Start-up Timer (OST) has expired. The OST is used after waking up from Sleep and after any type of Reset. The OST is not used with the EC or RC Clock modes so that the FSCM will be active as soon as the Reset or wake-up has completed. When the FSCM is enabled, the Two-Speed Start-up is also enabled. Therefore, the device will always be executing code while the OST is operating.

Note: Due to the wide range of oscillator start-up times, the Fail-Safe circuit is not active during oscillator start-up (i.e., after exiting Reset or Sleep). After an appropriate amount of time, the user should check the OSTS bit of the OSCCON register to verify the oscillator start-up and that the system clock switchover has successfully completed.

### 6.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected the TMR1H:TMR1L register pair will increment on multiples of Fosc as determined by the Timer1 prescaler.

#### 6.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When counting, Timer1 is incremented on the rising edge of the external clock input T1CKI. In addition, the Counter mode clock can be synchronized to the microcontroller system clock or run asynchronously.

If an external clock oscillator is needed (and the microcontroller is using the INTOSC without CLKOUT), Timer1 can use the LP oscillator as a clock source.

| Note 1: | In Counter mode, a falling edge must be<br>registered by the counter prior to the first<br>incrementing rising edge after any one or<br>more of the following conditions: |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | •Timer1 enabled after POR reset<br>•Write to TMR1H or TMR1L                                                                                                               |

|         | •Timer1 is disabled                                                                                                                                                       |

|         | •Timer1 is disabled (TMR1ON 0) when<br>T1CKI is high then Timer1 is<br>enabled (TMR1ON=1) when T1CKI<br>is low.                                                           |

| 2:      | See Figure 6-2                                                                                                                                                            |

### 6.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

## 6.4 Timer1 Oscillator

A low-power 32.768 kHz crystal oscillator is built-in between pins OSC1 (input) and OSC2 (amplifier output). The oscillator is enabled by setting the T1OSCEN control bit of the T1CON register. The oscillator will continue to run during Sleep.

The Timer1 oscillator is shared with the system LP oscillator. Thus, Timer1 can use this mode only when the primary system clock is derived from the internal oscillator or when the oscillator is in the LP mode. The user must provide a software time delay to ensure proper oscillator start-up.

TRISA5 and TRISA4 bits are set when the Timer1 oscillator is enabled. RA5 and RA4 bits read as '0' and TRISA5 and TRISA4 bits read as '1'.

| Note: | The oscillator requires a start-up and   |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|

|       | stabilization time before use. Thus,     |  |  |  |  |  |  |

|       | T1OSCEN should be set and a suitable     |  |  |  |  |  |  |

|       | delay observed prior to enabling Timer1. |  |  |  |  |  |  |

### 6.5 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 6.5.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

| Note: | When switching from synchronous to        |

|-------|-------------------------------------------|

|       | asynchronous operation, it is possible to |

|       | skip an increment. When switching from    |

|       | asynchronous to synchronous operation,    |

|       | it is possible to produce an additional   |

|       | increment.                                |

#### 6.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

## 6.6 Timer1 Gate

The Timer1 gate (when enabled) allows Timer1 to count when Timer1 gate is active. Timer1 gate source is software configurable to be the T1G pin or the output of Comparator C2. This allows the device to directly time external events using T1G or analog events using Comparator C2. See the CM2CON1 register (Register 8-3) for selecting the Timer1 gate source. This feature can simplify the software for a Delta-Sigma A/D converter and many other applications. Note: TMR1GE bit of the <u>T1CON</u> register must be set to use either <u>T1G</u> or C2OUT as the Timer1 gate source. See the CM2CON1 register (Register 8-3) for more information on selecting the Timer1 gate source.

Timer1 gate can be inverted using the T1GINV bit of the T1CON register, whether it originates from the T1G pin or Comparator C2 output. This configures Timer1 to measure either the active-high or active-low time between events.

## 6.7 Timer1 Interrupt

The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit of the PIR1 register is set. To enable the interrupt on rollover, you must set these bits:

- TMR10N bit of the T1CON register

- TMR1IE bit of the PIE1 register

- PEIE bit of the INTCON register

- GIE bit of the INTCON register

The interrupt is cleared by clearing the TMR1IF bit in the Interrupt Service Routine.

Note: The TMR1H:TTMR1L register pair and the TMR1IF bit should be cleared before enabling interrupts.

### 6.8 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- TMR1ON bit of the T1CON register must be set

- TMR1IE bit of the PIE1 register must be set

- PEIE bit of the INTCON register must be set

- T1SYNC bit of the T1CON register must be set

- TMR1CS bit of the T1CON register must be set

- T1OSCEN bit of the T1CON register (can be set)

The device will wake-up on an overflow and execute the next instructions. If the GIE bit of the INTCON register is set, the device will call the Interrupt Service Routine (0004h).

## 6.9 ECCP Capture/Compare Time Base

The ECCP module uses the TMR1H:TMR1L register pair as the time base when operating in Capture or Compare mode.

In Capture mode, the value in the TMR1H:TMR1L register pair is copied into the CCPR1H:CCPR1L register pair on a configured event.

In Compare mode, an event is triggered when the value CCPR1H:CCPR1L register pair matches the value in the TMR1H:TMR1L register pair. This event can be a Special Event Trigger.

For more information, see Section 11.0 "Enhanced Capture/Compare/PWM Module".

## 6.10 ECCP Special Event Trigger

When the ECCP is configured to trigger a special event, the trigger will clear the TMR1H:TMR1L register pair. This special event does not cause a Timer1 interrupt. The ECCP module may still be configured to generate a ECCP interrupt.

In this mode of operation, the CCPR1H:CCPR1L register pair becomes the period register for Timer1.

Timer1 should be synchronized to the FOSC to utilize the Special Event Trigger. Asynchronous operation of Timer1 can cause a Special Event Trigger to be missed.

In the event that a write to TMR1H or TMR1L coincides with a Special Event Trigger from the ECCP, the write will take precedence.

For more information, see **Section 11.2.4** "Special **Event Trigger**".

### 6.11 Comparator Synchronization

The same clock used to increment Timer1 can also be used to synchronize the comparator output. This feature is enabled in the Comparator module.

When using the comparator for Timer1 gate, the comparator output should be synchronized to Timer1. This ensures Timer1 does not miss an increment if the comparator changes.

For more information, see Section 8.8.2 "Synchronizing Comparator C2 output to Timer1".

## TABLE 9-1:ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES (VDD $\geq$ 3.0V,<br/>VREF $\geq$ 2.5V)

| ADC Clock F      | Period (TAD) | Device Frequency (Fosc) |                         |                         |                         |  |

|------------------|--------------|-------------------------|-------------------------|-------------------------|-------------------------|--|

| ADC Clock Source | ADCS<2:0>    | 20 MHz                  | 20 MHz 8 MHz 4 MH       |                         | 1 MHz                   |  |

| Fosc/2           | 000          | 100 ns <sup>(2)</sup>   | 250 ns <sup>(2)</sup>   | 500 ns <sup>(2)</sup>   | 2.0 μs                  |  |

| Fosc/4           | 100          | 200 ns <sup>(2)</sup>   | 500 ns <sup>(2)</sup>   | 1.0 μs <sup>(2)</sup>   | 4.0 μs                  |  |

| Fosc/8           | 001          | 400 ns <sup>(2)</sup>   | 1.0 μs <sup>(2)</sup>   | 2.0 μs                  | 8.0 μs <sup>(3)</sup>   |  |

| Fosc/16          | 101          | 800 ns <sup>(2)</sup>   | 2.0 μs                  | 4.0 μs                  | 16.0 μs <b>(3)</b>      |  |

| Fosc/32          | 010          | 1.6 μs                  | 4.0 μs                  | 8.0 μs <sup>(3)</sup>   | 32.0 μs <sup>(3)</sup>  |  |

| Fosc/64          | 110          | 3.2 μs                  | 8.0 μs <sup>(3)</sup>   | 16.0 μs <sup>(3)</sup>  | 64.0 μs <sup>(3)</sup>  |  |

| Frc              | x11          | 2-6 μs <sup>(1,4)</sup> | 2-6 μs <sup>(1,4)</sup> | 2-6 μs <sup>(1,4)</sup> | 2-6 μs <sup>(1,4)</sup> |  |

Legend: Shaded cells are outside of recommended range.

- **Note 1:** The FRC source has a typical TAD time of 4  $\mu$ s for VDD > 3.0V.

- 2: These values violate the minimum required TAD time.

- **3:** For faster conversion times, the selection of another clock source is recommended.

- 4: When the device frequency is greater than 1 MHz, the FRC clock source is only recommended if the conversion will be performed during Sleep.

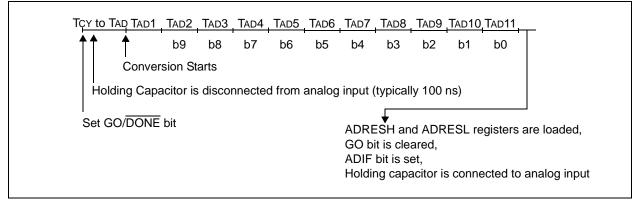

#### FIGURE 9-2: ANALOG-TO-DIGITAL CONVERSION TAD CYCLES

#### 9.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC interrupt flag is the ADIF bit in the PIR1 register. The ADC interrupt enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

| Note: | The ADIF bit is set at the completion of |

|-------|------------------------------------------|

|       | every conversion, regardless of whether  |

|       | or not the ADC interrupt is enabled.     |

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the global interrupt must be disabled. If the global interrupt is enabled, execution will switch to the interrupt service routine. Please see **Section 9.1.5** "Interrupts" for more information.

## **REGISTER 10-4:** EEADRH: EEPROM ADDRESS HIGH BYTE REGISTER<sup>(1)</sup> (CONTINUED)

Note 1: PIC16F685/PIC16F689/PIC16F690 only.

#### REGISTER 10-5: EECON1: EEPROM CONTROL REGISTER

| R/W-x                | U-0                                                                                                                                          | U-0                                                                                             | U-0     | R/W-x              | R/W-0           | R/S-0           | R/S-0 |  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------|--------------------|-----------------|-----------------|-------|--|

| EEPGD <sup>(1)</sup> |                                                                                                                                              |                                                                                                 | _       | WRERR              | WREN            | WR              | RD    |  |

| bit 7                |                                                                                                                                              |                                                                                                 |         |                    |                 |                 | bit C |  |

|                      |                                                                                                                                              |                                                                                                 |         |                    |                 |                 |       |  |

| Legend:              |                                                                                                                                              |                                                                                                 |         |                    |                 |                 |       |  |

| S = Bit can or       | ly be set                                                                                                                                    |                                                                                                 |         |                    |                 |                 |       |  |

| R = Readable         | bit                                                                                                                                          | W = Writable b                                                                                  | pit     | U = Unimpler       | nented bit, rea | d as '0'        |       |  |

| -n = Value at I      | POR                                                                                                                                          | '1' = Bit is set                                                                                |         | '0' = Bit is cle   | ared            | x = Bit is unkr | nown  |  |

|                      |                                                                                                                                              |                                                                                                 |         |                    |                 |                 |       |  |

| bit 7                |                                                                                                                                              | gram/Data EEPF                                                                                  |         | bit <sup>(1)</sup> |                 |                 |       |  |

|                      |                                                                                                                                              | s program mem                                                                                   | ory     |                    |                 |                 |       |  |

| bit 6-4              |                                                                                                                                              | s data memory                                                                                   | ,       |                    |                 |                 |       |  |

|                      | -                                                                                                                                            | ted: Read as '0                                                                                 |         |                    |                 |                 |       |  |

| bit 3                | <b>WRERR:</b> EEPROM Error Flag bit                                                                                                          |                                                                                                 |         |                    |                 |                 |       |  |

|                      | <ul> <li>1 = A write operation is prematurely terminated (any MCLR Reset, any WDT Reset during<br/>normal operation or BOR Reset)</li> </ul> |                                                                                                 |         |                    |                 |                 |       |  |

|                      |                                                                                                                                              | operation com                                                                                   |         |                    |                 |                 |       |  |

| bit 2                | WREN: EEPF                                                                                                                                   | ROM Write Enat                                                                                  | ole bit |                    |                 |                 |       |  |

|                      | 1 = Allows wr                                                                                                                                |                                                                                                 |         |                    |                 |                 |       |  |

|                      | 0 = Inhibits w                                                                                                                               | rite to the data E                                                                              | EPROM   |                    |                 |                 |       |  |

| bit 1                | WR: Write Co                                                                                                                                 | ontrol bit                                                                                      |         |                    |                 |                 |       |  |

|                      | $\underline{EEPGD} = 1$                                                                                                                      |                                                                                                 |         |                    |                 |                 |       |  |

|                      | This bit is ignored<br>EEPGD = 0 :                                                                                                           |                                                                                                 |         |                    |                 |                 |       |  |

|                      | 1 =  Initiates a write cycle (The bit is cleared by hardware once write is complete. The WR bit can only                                     |                                                                                                 |         |                    |                 |                 |       |  |

|                      | be set, not cleared, in software.)                                                                                                           |                                                                                                 |         |                    |                 |                 |       |  |

|                      | 0 = Write cycle to the data EEPROM is complete                                                                                               |                                                                                                 |         |                    |                 |                 |       |  |

| bit 0                | RD: Read Control bit                                                                                                                         |                                                                                                 |         |                    |                 |                 |       |  |

|                      |                                                                                                                                              | 1 = Initiates a memory read (the RD is cleared in hardware and can only be set, not cleared, in |         |                    |                 |                 |       |  |

|                      | software.)<br>0 = Does not initiate a memory read                                                                                            |                                                                                                 |         |                    |                 |                 |       |  |

|                      |                                                                                                                                              |                                                                                                 | ny ieau |                    |                 |                 |       |  |

Note 1: PIC16F685/PIC16F689/PIC16F690 only.

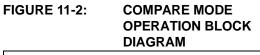

## 11.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the CCP module may:

- Toggle the CCP1 output

- Set the CCP1 output

- Clear the CCP1 output

- Generate a Special Event Trigger

- Generate a Software Interrupt

The action on the pin is based on the value of the CCP1M<3:0> control bits of the CCP1CON register.

All Compare modes can generate an interrupt.

Special Event Trigger Will:

- Clear TMR1H and TMR1L registers.

- NOT set interrupt flag bit TMR1IF of the PIR1 register.

- Set the GO/DONE bit to start the ADC conversion.

#### 11.2.1 CCP1 PIN CONFIGURATION

The user must configure the CCP1 pin as an output by clearing the associated TRIS bit.

| Note: | Clearing the CCP1CON register will force    |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|

|       | the CCP1 compare output latch to the        |  |  |  |  |  |  |

|       | default low level. This is not the port I/O |  |  |  |  |  |  |

|       | data latch.                                 |  |  |  |  |  |  |

#### 11.2.2 TIMER1 MODE SELECTION

In Compare mode, Timer1 must be running in either Timer mode or Synchronized Counter mode. The compare operation may not work in Asynchronous Counter mode.

#### 11.2.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen (CCP1M<3:0> = 1010), the CCP module does not assert control of the CCP1 pin (see the CCP1CON register).

#### 11.2.4 SPECIAL EVENT TRIGGER

When Special Event Trigger mode is chosen (CCP1M<3:0> = 1011), the CCP module does the following:

- Resets Timer1

- Starts an ADC conversion if ADC is enabled

The CCP module does not assert control of the CCP1 pin in this mode (see the CCP1CON register).

The Special Event Trigger output of the CCP occurs immediately upon a match between the TMR1H, TMR1L register pair and the CCPR1H, CCPR1L register pair. The TMR1H, TMR1L register pair is not reset until the next rising edge of the Timer1 clock. This allows the CCPR1H, CCPR1L register pair to effectively provide a 16-bit programmable period register for Timer1.

- Note 1: The Special Event Trigger from the CCP module does not set interrupt flag bit TMR1IF of the PIR1 register.

- 2: Removing the match condition by changing the contents of the CCPR1H and CCPR1L register pair, between the clock edge that generates the Special Event Trigger and the clock edge that generates the Timer1 Reset, will preclude the Reset from occurring.

## 12.5 EUSART Operation During Sleep

The EUSART WILL remain active during Sleep only in the Synchronous Slave mode. All other modes require the system clock and therefore cannot generate the necessary signals to run the Transmit or Receive Shift registers during Sleep.

Synchronous Slave mode uses an externally generated clock to run the Transmit and Receive Shift registers.

#### 12.5.1 SYNCHRONOUS RECEIVE DURING SLEEP

To receive during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for Synchronous Slave Reception (see Section 12.4.2.4 "Synchronous Slave Reception Set-up:").

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- The RCIF interrupt flag must be cleared by reading RCREG to unload any pending characters in the receive buffer.

Upon entering Sleep mode, the device will be ready to accept data and clocks on the RX/DT and TX/CK pins, respectively. When the data word has been completely clocked in by the external device, the RCIF interrupt flag bit of the PIR1 register will be set. Thereby, waking the processor from Sleep.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the GIE Global Interrupt Enable bit of the INTCON register is also set, then the Interrupt Service Routine at address 004h will be called.

#### 12.5.2 SYNCHRONOUS TRANSMIT DURING SLEEP

To transmit during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for Synchronous Slave Transmission (see Section 12.4.2.2 "Synchronous Slave Transmission Set-up:").

- The TXIF interrupt flag must be cleared by writing the output data to the TXREG, thereby filling the TSR and transmit buffer.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the PEIE bit of the INTCON register.

- Interrupt enable bits TXIE of the PIE1 register and PEIE of the INTCON register must set.

Upon entering Sleep mode, the device will be ready to accept clocks on TX/CK pin and transmit data on the RX/DT pin. When the data word in the TSR has been completely clocked out by the external device, the pending byte in the TXREG will transfer to the TSR and the TXIF flag will be set. Thereby, waking the processor from Sleep. At this point, the TXREG is available to accept another character for transmission, which will clear the TXIF flag.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the GIE Global Interrupt Enable bit is also set then the Interrupt Service Routine at address 0004h will be called.

#### 13.12.3 SSP MASK REGISTER

An SSP Mask (SSPMSK) register is available in  $I^2C$ Slave mode as a mask for the value held in the SSPSR register during an address comparison operation. A zero ('0') bit in the SSPMSK register has the effect of making the corresponding bit in the SSPSR register a 'don't care'.

This register is reset to all '1's upon any Reset condition and, therefore, has no effect on standard SSP operation until written with a mask value.

This register must be initiated prior to setting SSPM<3:0> bits to select the  $I^2C$  Slave mode (7-bit or 10-bit address).

This register can only be accessed when the appropriate mode is selected by bits (SSPM<3:0> of SSPCON).

The SSP Mask register is active during:

- 7-bit Address mode: address compare of A<7:1>.

- 10-bit Address mode: address compare of A<7:0> only. The SSP mask has no effect during the reception of the first (high) byte of the address.

### REGISTER 13-3: SSPMSK: SSP MASK REGISTER<sup>(1)</sup>

| R/W-1               |

|-------|-------|-------|-------|-------|-------|-------|---------------------|

| MSK7  | MSK6  | MSK5  | MSK4  | MSK3  | MSK2  | MSK1  | MSK0 <sup>(2)</sup> |

| bit 7 |       |       |       |       |       |       | bit 0               |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-1 MSK<7:1>: Mask bits

- 1 = The received address bit n is compared to SSPADD<n> to detect  $I^2C$  address match

- 0 = The received address bit n is not used to detect I<sup>2</sup>C address match

#### bit 0 MSK<0>: Mask bit for I<sup>2</sup>C Slave mode, 10-bit Address<sup>(2)</sup>

- I<sup>2</sup>C Slave mode, 10-bit Address (SSPM<3:0> = 0111):

- 1 = The received address bit 0 is compared to SSPADD<0> to detect  $I^2C$  address match

- 0 = The received address bit 0 is not used to detect  $I^2C$  address match

- **Note 1:** When SSPCON bits SSPM<3:0> = 1001, any reads or writes to the SSPADD SFR address are accessed through the SSPMSK register. The SSPEN bit of the SSPCON register should be zero when accessing the SSPMSK register.

- 2: In all other SSP modes, this bit has no effect.

| Condition                          | Program<br>Counter    | Status<br>Register | PCON<br>Register |  |

|------------------------------------|-----------------------|--------------------|------------------|--|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 010x             |  |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | 0uuu             |  |

| MCLR Reset during Sleep            | 000h                  | 0001 Ouuu          | 0uuu             |  |

| WDT Reset                          | 000h                  | 0000 uuuu          | 0uuu             |  |

| WDT Wake-up                        | PC + 1                | uuu0 Ouuu          | uuuu             |  |

| Brown-out Reset                    | 000h                  | 0001 luuu          | 01u0             |  |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | uuuu             |  |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Interrupt Enable bit, GIE, is set, the PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

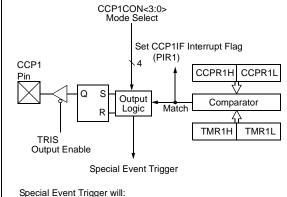

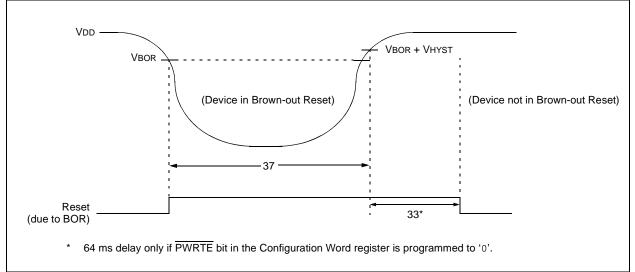

## FIGURE 17-6: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

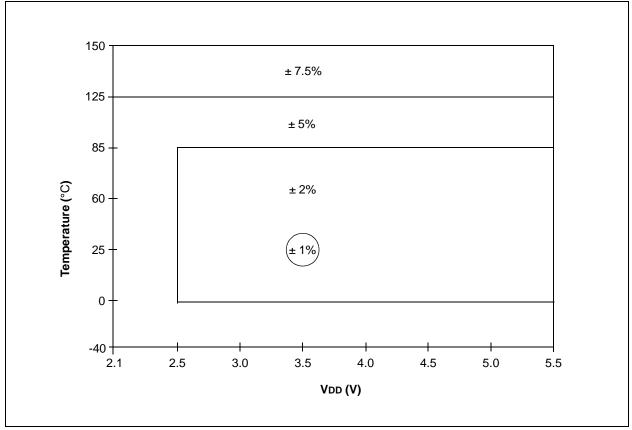

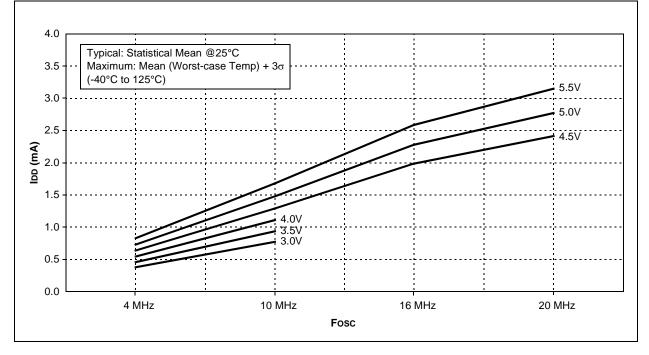

### FIGURE 17-21: HFINTOSC FREQUENCY ACCURACY OVER DEVICE VDD AND TEMPERATURE

© 2005-2015 Microchip Technology Inc.

| Param  | Device          | Units M | M2   | Min. Typ. |      | Condition |                                                 |  |

|--------|-----------------|---------|------|-----------|------|-----------|-------------------------------------------------|--|

| No.    | Characteristics |         | win. |           | Max. | Vdd       | Note                                            |  |

| D020E  | Power Down Base | —       |      | 27        | μA   | 2.1       | IPD Base: WDT, BOR,                             |  |

|        | Current (IPD)   | —       |      | 29        |      | 3.0       | Comparators, VREF and                           |  |

|        |                 | —       |      | 32        |      | 5.0       | T10sc disabled                                  |  |

| D021E  |                 | —       | _    | 55        |      | 2.1       |                                                 |  |

|        |                 | —       |      | 59        | μA   | 3.0       | WDT Current                                     |  |

|        |                 | —       |      | 69        |      | 5.0       |                                                 |  |

| D022E  |                 | —       | —    | 75        |      | 3.0       | BOR Current                                     |  |

|        |                 | _       | _    | 147       | μA   | 5.0       |                                                 |  |

| D023E  |                 | —       |      | 73        |      | 2.1       |                                                 |  |

|        |                 | —       | —    | 117       | μA   | 3.0       | Comparator current, both<br>comparators enabled |  |

|        |                 | _       | _    | 235       |      | 5.0       |                                                 |  |

| D024E  |                 | —       |      | 102       | μΑ   | 2.1       |                                                 |  |

|        |                 | —       | _    | 128       |      | 3.0       | CVREF current, high range                       |  |

|        |                 | —       |      | 170       |      | 5.0       |                                                 |  |

| D024AE |                 | —       | _    | 133       | μΑ   | 2.1       |                                                 |  |

|        |                 | _       |      | 167       |      | 3.0       | CVREF current, low range                        |  |

|        |                 | —       |      | 222       |      | 5.0       |                                                 |  |

| D025E  |                 | —       | _    | 36        |      | 2.1       |                                                 |  |

|        |                 | —       | _    | 41        | μΑ   | 3.0       | T1osc current, 32 kHz                           |  |

|        |                 | —       |      | 47        |      | 5.0       |                                                 |  |

| D026E  |                 | _       | _    | 22        | μA   | 3.0       | Analog-to-Digital current,                      |  |

|        |                 |         | —    | 24        |      | 5.0       | no conversion in progress                       |  |

| D027E  |                 |         |      | 189       | μA   | 3.0       | VP6 current (Fixed Voltage                      |  |

|        |                 |         |      | 250       |      | 5.0       | Reference)                                      |  |

## TABLE 17-20: DC CHARACTERISTICS FOR IPD SPECIFICATIONS FOR PIC16F685/687/689/690-H (High Temp.) (High Temp.)

#### TABLE 17-21: LEAKAGE CURRENT SPECIFICATIONS FOR PIC16F685/687/689/690-H (High Temp.)

| Param<br>No. | Sym. | Characteristic                                     | Min. | Тур. | Max. | Units | Conditions               |

|--------------|------|----------------------------------------------------|------|------|------|-------|--------------------------|

| D061         | lı∟  | Input Leakage Current <sup>(1)</sup><br>(RA3/MCLR) | _    | ±0.5 | ±5.0 | μA    | $VSS \leq VPIN \leq VDD$ |

| D062         | lı∟  | Input Leakage Current <sup>(2)</sup><br>(RA3/MCLR) | 50   | 250  | 400  | μA    | VDD = 5.0V               |

**Note 1:** This specification applies when RA3/MCLR is configured as an input with the pull-up disabled. The leakage current for the RA3/MCLR pin is higher than for the standard I/O port pins.

2: This specification applies when RA3/MCLR is configured as the MCLR reset pin function with the weak pull-up enabled.

#### TABLE 17-22: DATA EEPROM MEMORY ENDURANCE SPECIFICATIONS FOR PIC16F685/687/689/690-H (High Temp.)

| Param<br>No. | Sym. Characteristic |                | Min. | Тур. | Max. | Units | Conditions                               |

|--------------|---------------------|----------------|------|------|------|-------|------------------------------------------|

| D120A        | ED                  | Byte Endurance | 5K   | 50K  | _    | E/W   | $126^{\circ}C \leq TA \leq 150^{\circ}C$ |

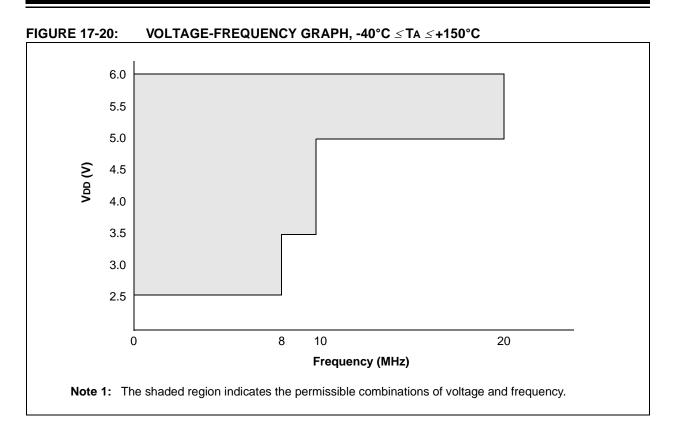

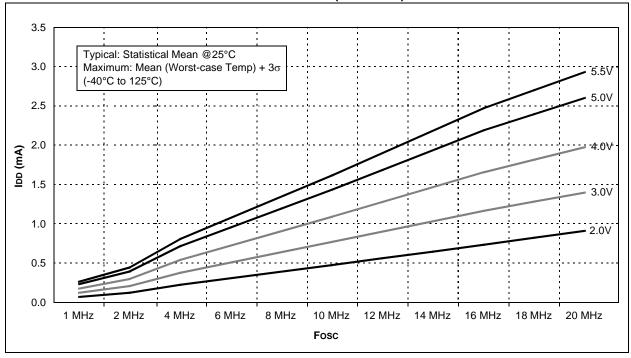

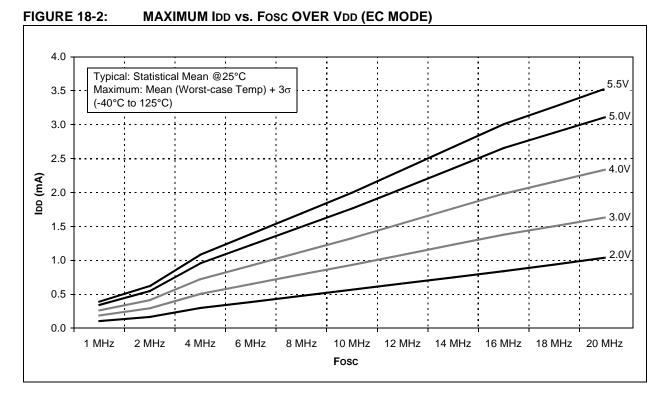

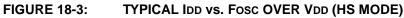

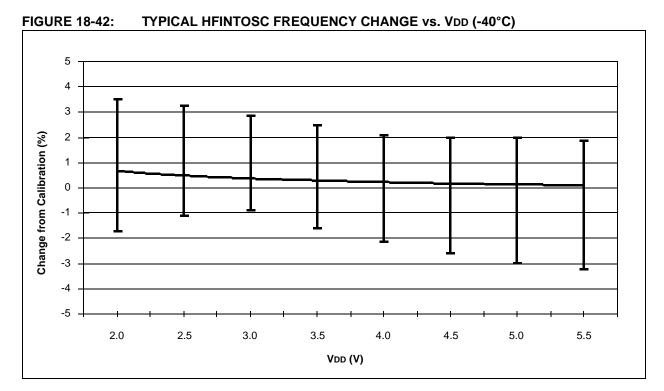

## 18.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

The graphs and tables provided in this section are for **design guidance** and are **not tested**.

In some graphs or tables, the data presented are **outside specified operating range** (i.e., outside specified VDD range). This is for **information only** and devices are ensured to operate properly only within the specified range.

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over each temperature range.

#### FIGURE 18-1: TYPICAL IDD vs. Fosc OVER VDD (EC MODE)

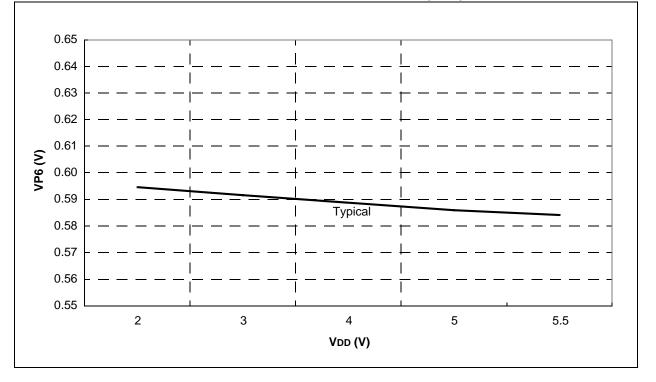

FIGURE 18-43: TYPICAL VP6 REFERENCE VOLTAGE vs. VDD (25°C)

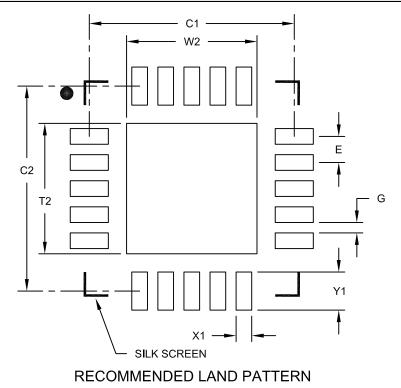

## 20-Lead Plastic Quad Flat, No Lead Package (ML) - 4x4 mm Body [QFN] With 0.40 mm Contact Length

|                            | Units |      |          | MILLIMETERS |  |  |  |  |

|----------------------------|-------|------|----------|-------------|--|--|--|--|

| Dimensior                  | MIN   | NOM  | MAX      |             |  |  |  |  |

| Contact Pitch              | E     |      | 0.50 BSC |             |  |  |  |  |

| Optional Center Pad Width  | W2    | 2.50 |          |             |  |  |  |  |

| Optional Center Pad Length | T2    |      |          | 2.50        |  |  |  |  |

| Contact Pad Spacing        | C1    |      | 3.93     |             |  |  |  |  |

| Contact Pad Spacing        | C2    |      | 3.93     |             |  |  |  |  |

| Contact Pad Width          | X1    |      |          | 0.30        |  |  |  |  |

| Contact Pad Length         | Y1    |      |          | 0.73        |  |  |  |  |

| Distance Between Pads      | G     | 0.20 |          |             |  |  |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2126A

## **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

**Chicago** Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983 Indianapolis

Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-213-7828

Taiwan - Taipei Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Germany - Pforzheim** Tel: 49-7231-424750

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

01/27/15