# Microchip Technology - PIC16F631T-I/SO Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Number of I/O              | 18                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 64 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 20-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f631t-i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Table of Contents

| 1.0   | Device Overview                                                           | 9   |

|-------|---------------------------------------------------------------------------|-----|

| 2.0   | Memory Organization                                                       | 24  |

| 3.0   | Oscillator Module (With Fail-Safe Clock Monitor)                          | 45  |

| 4.0   | I/O Ports                                                                 |     |

| 5.0   | Timer0 Module                                                             | 79  |

| 6.0   | Timer1 Module with Gate Control                                           | 82  |

| 7.0   | Timer2 Module                                                             | 89  |

| 8.0   | Comparator Module                                                         | 91  |

| 9.0   | Analog-to-Digital Converter (ADC) Module                                  |     |

| 10.0  | Data EEPROM and Flash Program Memory Control                              | 117 |

| 11.0  | Enhanced Capture/Compare/PWM Module                                       | 125 |

| 12.0  | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) | 148 |

| 13.0  | SSP Module Overview                                                       | 175 |

| 14.0  | Special Features of the CPU                                               | 193 |

| 15.0  | Instruction Set Summary                                                   | 212 |

| 16.0  | Development Support                                                       |     |

| 17.0  | Electrical Specifications                                                 |     |

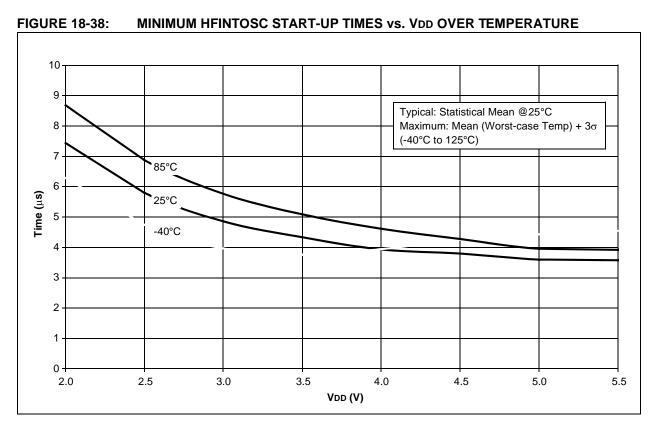

| 18.0  | DC and AC Characteristics Graphs and Tables                               | 258 |

| 19.0  | Packaging Information                                                     | 285 |

| The M | Vicrochip Web Site                                                        | 295 |

|       | omer Change Notification Service                                          |     |

| Custo | omer Support                                                              | 295 |

| Produ | uct Identification System                                                 | 296 |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via Email at **docerrors@microchip.com**. We welcome your feedback.

# Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip's Worldwide Web site; http://www.microchip.com

Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

| Addr | Name                     | Bit 7        | Bit 6               | Bit 5               | Bit 4               | Bit 3                | Bit 2                 | Bit 1                 | Bit 0                | Value on<br>POR, BOR | Page    |

|------|--------------------------|--------------|---------------------|---------------------|---------------------|----------------------|-----------------------|-----------------------|----------------------|----------------------|---------|

| Bank | 0                        |              |                     |                     |                     |                      |                       |                       |                      |                      |         |

| 00h  | INDF                     | Addressing   | this location       | uses conten         | ts of FSR to a      | address data         | memory (no            | t a physical r        | egister)             | xxxx xxxx            | 43,200  |

| 01h  | TMR0                     | Timer0 Mod   | lule Register       |                     |                     |                      |                       |                       |                      | xxxx xxxx            | 79,200  |

| 02h  | PCL                      | Program Co   | ounter's (PC)       | Least Signif        | icant Byte          |                      |                       |                       |                      | 0000 0000            | 43,200  |

| 03h  | STATUS                   | IRP          | RP1                 | RP0                 | TO                  | PD                   | Z                     | DC                    | С                    | 0001 1xxx            | 35,200  |

| 04h  | FSR                      | Indirect Dat | a Memory A          | ddress Pointe       | ər                  |                      |                       |                       |                      | xxxx xxxx            | 43,200  |

| 05h  | PORTA <sup>(7)</sup>     | _            | _                   | RA5                 | RA4                 | RA3                  | RA2                   | RA1                   | RA0                  | xx xxxx              | 57,200  |

| 06h  | PORTB <sup>(7)</sup>     | RB7          | RB6                 | RB5                 | RB4                 | _                    | _                     | _                     | _                    | xxxx                 | 67,200  |

| 07h  | PORTC <sup>(7)</sup>     | RC7          | RC6                 | RC5                 | RC4                 | RC3                  | RC2                   | RC1                   | RC0                  | xxxx xxxx            | 74,200  |

| 08h  | —                        | Unimpleme    | nted                |                     |                     |                      |                       |                       |                      | —                    | —       |

| 09h  | —                        | Unimpleme    | nted                |                     |                     |                      |                       |                       |                      | —                    | —       |

| 0Ah  | PCLATH                   |              | _                   |                     | Write Buffer        | for upper 5 l        | oits of Progra        | am Counter            |                      | 0 0000               | 43,200  |

| 0Bh  | INTCON                   | GIE          | PEIE                | TOIE                | INTE                | RABIE                | TOIF                  | INTF                  | RABIF <sup>(1)</sup> | 0000 000x            | 37,200  |

| 0Ch  | PIR1                     | _            | ADIF <sup>(4)</sup> | RCIF <sup>(2)</sup> | TXIF <sup>(2)</sup> | SSPIF <sup>(5)</sup> | CCP1IF <sup>(3)</sup> | TMR2IF <sup>(3)</sup> | TMR1IF               | -000 0000            | 40,200  |

| 0Dh  | PIR2                     | OSFIF        | C2IF                | C1IF                | EEIF                | —                    | —                     | _                     | _                    | 0000                 | 41,200  |

| 0Eh  | TMR1L                    | Holding Re   | gister for the      | Least Signifi       | cant Byte of        | the 16-bit TM        | R1 Register           |                       |                      | xxxx xxxx            | 85,200  |

| 0Fh  | TMR1H                    | Holding Re   | gister for the      | Most Signific       | cant Byte of t      | he 16-bit TM         | R1 Register           |                       |                      | xxxx xxxx            | 85,200  |

| 10h  | T1CON                    | T1GINV       | TMR1GE              | T1CKPS1             | T1CKPS0             | T1OSCEN              | T1SYNC                | TMR1CS                | TMR10N               | 0000 0000            | 87,200  |

| 11h  | TMR2 <sup>(3)</sup>      | Timer2 Mod   | ule Register        |                     |                     |                      |                       |                       |                      | 0000 0000            | 89,200  |

| 12h  | T2CON <sup>(3)</sup>     | -            | TOUTPS3             | TOUTPS2             | TOUTPS1             | TOUTPS0              | TMR2ON                | T2CKPS1               | T2CKPS0              | -000 0000            | 90,200  |

| 13h  | SSPBUF <sup>(5)</sup>    | Synchronou   | us Serial Port      | Receive But         | ffer/Transmit       | Register             |                       |                       |                      | xxxx xxxx            | 178,200 |

| 14h  | SSPCON <sup>(5, 6)</sup> | WCOL         | SSPOV               | SSPEN               | CKP                 | SSPM3                | SSPM2                 | SSPM1                 | SSPM0                | 0000 0000            | 177,200 |

| 15h  | CCPR1L <sup>(3)</sup>    | Capture/Co   | mpare/PWM           | Register 1 (I       | LSB)                |                      |                       |                       |                      | xxxx xxxx            | 126,200 |

| 16h  | CCPR1H <sup>(3)</sup>    | Capture/Co   | mpare/PWM           | Register 1 (I       | MSB)                |                      |                       |                       |                      | xxxx xxxx            | 126,200 |

| 17h  | CCP1CON <sup>(3)</sup>   | P1M1         | P1M0                | DC1B1               | DC1B0               | CCP1M3               | CCP1M2                | CCP1M1                | CCP1M0               | 0000 0000            | 125,200 |

| 18h  | RCSTA <sup>(2)</sup>     | SPEN         | RX9                 | SREN                | CREN                | ADDEN                | FERR                  | OERR                  | RX9D                 | 0000 000x            | 158,200 |

| 19h  | TXREG <sup>(2)</sup>     | EUSART T     | ransmit Data        | Register            |                     |                      |                       |                       |                      | 0000 0000            | 150     |

| 1Ah  | RCREG <sup>(2)</sup>     | EUSART R     | eceive Data         | Register            |                     |                      |                       |                       |                      | 0000 0000            | 155     |

| 1Bh  | _                        | Unimpleme    | nted                |                     |                     |                      |                       |                       |                      | _                    | _       |

| 1Ch  | PWM1CON <sup>(3)</sup>   | PRSEN        | PDC6                | PDC5                | PDC4                | PDC3                 | PDC2                  | PDC1                  | PDC0                 | 0000 0000            | 143,200 |

| 1Dh  | ECCPAS <sup>(3)</sup>    | ECCPASE      | ECCPAS2             | ECCPAS1             | ECCPAS0             | PSSAC1               | PSSAC0                | PSSBD1                | PSSBD0               | 0000 0000            | 140,200 |

| 1Eh  | ADRESH <sup>(4)</sup>    | A/D Result   | Register Hig        | h Byte              |                     |                      |                       |                       |                      | xxxx xxxx            | 113,200 |

| 1Fh  | ADCON0 <sup>(4)</sup>    | ADFM         | VCFG                | CHS3                | CHS2                | CHS1                 | CHS0                  | GO/DONE               | ADON                 | 0000 0000            | 111,200 |

| TABLE 2-1: | PIC16F631/677/685/687/689/690 SPECIAL FUNCTION REGISTERS SUMMARY BANK 0 |

|------------|-------------------------------------------------------------------------|

|------------|-------------------------------------------------------------------------|

Legend:- = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplementedNote1:MCLR and WDT Reset do not affect the previous value data latch. The RABIF bit will be cleared upon Reset but will set again if the

mismatch exists.

2: PIC16F687/PIC16F689/PIC16F690 only.

3: PIC16F685/PIC16F690 only.

4: PIC16F677/PIC16F685/PIC16F687/PIC16F689/PIC16F690 only.

5: PIC16F677/PIC16F687/PIC16F689/PIC16F690 only.

6: When SSPCON register bits SSPM<3:0> = 1001, any reads or writes to the SSPADD SFR address are accessed through the SSPMSK register. See Registers 13-2 and 13-3 for more detail.

7: Port pins with analog functions controlled by the ANSEL and ANSELH registers will read '0' immediately after a Reset even though the data latches are either undefined (POR) or unchanged (other Resets).

### 3.5.2.1 OSCTUNE Register

-n = Value at POR

The HFINTOSC is factory calibrated but can be adjusted in software by writing to the OSCTUNE register (Register 3-2).

The default value of the OSCTUNE register is '0'. The value is a 5-bit two's complement number.

When the OSCTUNE register is modified, the HFINTOSC frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

OSCTUNE does not affect the LFINTOSC frequency. Operation of features that depend on the LFINTOSC clock source frequency, such as the Power-up Timer (PWRT), Watchdog Timer (WDT), Fail-Safe Clock Monitor (FSCM) and peripherals, are *not* affected by the change in frequency.

x = Bit is unknown

### REGISTER 3-2: OSCTUNE: OSCILLATOR TUNING REGISTER

'1' = Bit is set

| U-0                               | U-0 | U-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |  |

|-----------------------------------|-----|-----|-------|------------------------------------|-------|-------|-------|--|--|

| —                                 | —   | —   | TUN4  | TUN3                               | TUN2  | TUN1  | TUN0  |  |  |

| bit 7                             |     |     |       |                                    |       |       | bit 0 |  |  |

|                                   |     |     |       |                                    |       |       |       |  |  |

| Legend:                           |     |     |       |                                    |       |       |       |  |  |

| R = Readable bit W = Writable bit |     |     | bit   | U = Unimplemented bit, read as '0' |       |       |       |  |  |

'0' = Bit is cleared

| bit 7-5 | Unimplemented: Read as '0'                                                |

|---------|---------------------------------------------------------------------------|

| bit 4-0 | TUN<4:0>: Frequency Tuning bits                                           |

|         | 01111 = Maximum frequency                                                 |

|         | 01110 =                                                                   |

|         | •                                                                         |

|         | •                                                                         |

|         | •                                                                         |

|         | 00001 =                                                                   |

|         | 00000 = Oscillator module is running at the factory-calibrated frequency. |

|         | 11111 =                                                                   |

|         | •                                                                         |

|         | •                                                                         |

|         | •                                                                         |

|         | 10000 = Minimum frequency                                                 |

|         |                                                                           |

| U-0                                                                                         | U-0                        | R/W-1              | R/W-1        | U-0              | R/W-1            | R/W-1           | R/W-1 |

|---------------------------------------------------------------------------------------------|----------------------------|--------------------|--------------|------------------|------------------|-----------------|-------|

| _                                                                                           | _                          | WPUA5              | WPUA4        |                  | WPUA2            | WPUA1           | WPUA0 |

| bit 7                                                                                       |                            |                    |              |                  |                  |                 | bit 0 |

|                                                                                             |                            |                    |              |                  |                  |                 |       |

| Legend:                                                                                     |                            |                    |              |                  |                  |                 |       |

| R = Read                                                                                    | able bit                   | W = Writable       | bit          | U = Unimpler     | mented bit, read | l as '0'        |       |

| -n = Value                                                                                  | e at POR                   | '1' = Bit is set   |              | '0' = Bit is cle | ared             | x = Bit is unki | nown  |

| bit 7-6<br>bit 5-4                                                                          | -                          | nented: Read as '( |              |                  |                  |                 |       |

| DIL 5-4                                                                                     | 1 = Pull-up<br>0 = Pull-up |                    | Register bit |                  |                  |                 |       |

| bit 3                                                                                       | Unimplem                   | nented: Read as 'o | )'           |                  |                  |                 |       |

| bit 2-0 WPUA<2:0>: Weak Pull-up Register bit<br>1 = Pull-up enabled<br>0 = Pull-up disabled |                            |                    |              |                  |                  |                 |       |

| Note 1:<br>2:                                                                               |                            | bit of the OPTION  | •            |                  |                  |                 | bled. |

#### WPUA: PORTA REGISTER **REGISTER 4-5:**

3: The RA3 pull-up is enabled when configured as MCLR and disabled as an I/O in the Configuration Word.

4: WPUA<5:4> always reads '1' in XT, HS and LP Oscillator modes.

#### **REGISTER 4-6: IOCA: INTERRUPT-ON-CHANGE PORTA REGISTER**

| Logondi |     |       |       |       |       |       |       |

|---------|-----|-------|-------|-------|-------|-------|-------|

|         |     |       |       |       |       |       |       |

| bit 7   |     |       |       |       |       |       | bit 0 |

| _       | —   | IOCA5 | IOCA4 | IOCA3 | IOCA2 | IOCA1 | IOCA0 |

| U-0     | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|         |     |       |       |       |       |       |       |

| Legena.           |                  |                        |                                    |  |  |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |  |  |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 IOCA<5:0>: Interrupt-on-change PORTA Control bit

1 = Interrupt-on-change enabled

0 = Interrupt-on-change disabled

Note 1: Global Interrupt Enable (GIE) must be enabled for individual interrupts to be recognized.

2: IOCA<5:4> always reads '1' in XT, HS and LP Oscillator modes.

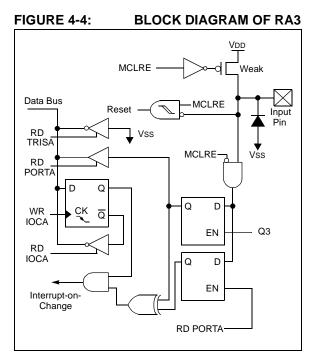

### 4.2.5.4 RA3/MCLR/VPP

Figure 4-4 shows the diagram for this pin. The RA3/ MCLR/VPP pin is configurable to function as one of the following:

- a general purpose input

- as Master Clear Reset with weak pull-up

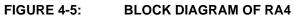

# 4.2.5.5 RA4/AN3/T1G/OSC2/CLKOUT

Figure 4-5 shows the diagram for this pin. The RA4/ AN3/T1G/OSC2/CLKOUT pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC (except PIC16F631)

- a Timer1 gate input

- a crystal/resonator connection

- · a clock output

- 2: With CLKOUT option.

- 3: ANSEL determines Analog Input mode.

- 4: Not implemented on PIC16F631.

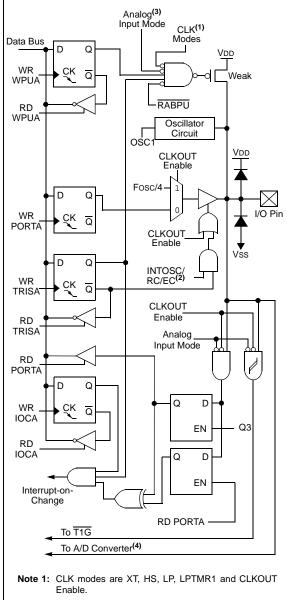

### 4.2.5.6 RA5/T1CKI/OSC1/CLKIN

Figure 4-6 shows the diagram for this pin. The RA5/ T1CKI/OSC1/CLKIN pin is configurable to function as one of the following:

- a general purpose I/O

- a Timer1 clock input

- a crystal/resonator connection

- a clock input

# FIGURE 4-6: BLOCK DIAGRAM OF RA5

| Name    | Bit 7       | Bit 6          | Bit 5         | Bit 4          | Bit 3         | Bit 2       | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-------------|----------------|---------------|----------------|---------------|-------------|--------|--------|----------------------|---------------------------------|

| CM2CON1 | MC10UT      | MC2OUT         | —             | —              | —             | —           | T1GSS  | C2SYNC | 10                   | 10                              |

| INTCON  | GIE         | PEIE           | T0IE          | INTE           | RABIE         | T0IF        | INTF   | RABIF  | 0000 0000            | 0000 0000                       |

| PIE1    | —           | ADIE           | RCIE          | TXIE           | SSPIE         | CCP1IE      | TMR2IE | TMR1IE | -000 0000            | -000 0000                       |

| PIR1    | —           | ADIF           | RCIF          | TXIF           | SSPIF         | CCP1IF      | TMR2IF | TMR1IF | -000 0000            | -000 0000                       |

| TMR1H   | Holding Reg | gister for the | Most Signific | ant Byte of th | he 16-bit TMI | R1 Register |        | •      | xxxx xxxx            | uuuu uuuu                       |

| TMR1L   | Holding Reg | gister for the |               | xxxx xxxx      | uuuu uuuu     |             |        |        |                      |                                 |

| T1CON   | T1GINV      | TMR1GE         | T1CKPS1       | T1CKPS0        | T1OSCEN       | T1SYNC      | TMR1CS | TMR10N | 0000 0000            | uuuu uuuu                       |

### TABLE 6-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER1

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

| REGISTER 10-1: EEI | DAT: EEPROM DATA REGISTER |

|--------------------|---------------------------|

|--------------------|---------------------------|

| R/W-0                              | R/W-0  | R/W-0  | R/W-0  | R/W-0                                 | R/W-0  | R/W-0  | R/W-0  |  |

|------------------------------------|--------|--------|--------|---------------------------------------|--------|--------|--------|--|

| EEDAT7                             | EEDAT6 | EEDAT5 | EEDAT4 | EEDAT3                                | EEDAT2 | EEDAT1 | EEDAT0 |  |

| bit 7                              |        |        |        |                                       |        |        | bit 0  |  |

|                                    |        |        |        |                                       |        |        |        |  |

| Legend:                            |        |        |        |                                       |        |        |        |  |

| R = Readable bit W = Writable bit  |        |        | t      | U = Unimplemented bit, read as '0'    |        |        |        |  |

| -n = Value at POR '1' = Bit is set |        |        |        | '0' = Bit is cleared x = Bit is unkno |        |        | vn     |  |

bit 7-0

EEDAT<7:0>: Eight Least Significant Address bits to Write to or Read from data EEPROM or Read from program memory

### REGISTER 10-2: EEADR: EEPROM ADDRESS REGISTER

| R/W-0                 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-----------------------|--------|--------|--------|--------|--------|--------|--------|

| EEADR7 <sup>(1)</sup> | EEADR6 | EEADR5 | EEADR4 | EEADR3 | EEADR2 | EEADR1 | EEADR0 |

| bit 7                 |        |        |        |        |        |        | bit 0  |

|                       |        |        |        |        |        |        |        |

| Legend:               |        |        |        |        |        |        |        |

| Legena.           |                  |                                                 |                    |  |  |

|-------------------|------------------|-------------------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | Writable bit U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                            | x = Bit is unknown |  |  |

|                   |                  |                                                 |                    |  |  |

bit 7-0 **EEADR<7:0>**: Eight Least Significant Address bits for EEPROM Read/Write Operation<sup>(1)</sup> or Read from program memory

Note 1: PIC16F677/PIC16F685/PIC16F687/PIC16F689/PIC16F690 only.

### REGISTER 10-3: EEDATH: EEPROM DATA HIGH BYTE REGISTER<sup>(1)</sup>

| U-0   | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | EEDATH5 | EEDATH4 | EEDATH3 | EEDATH2 | EEDATH1 | EEDATH0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:           |                  |                                |                    |

|-------------------|------------------|--------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as | '0'                |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared           | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 EEDATH<5:0>: Six Most Significant Data bits from program memory

Note 1: PIC16F685/PIC16F689/PIC16F690 only.

## REGISTER 10-4: EEADRH: EEPROM ADDRESS HIGH BYTE REGISTER<sup>(1)</sup>

| U-0   | U-0 | U-0 | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|-------|-----|-----|-----|---------|---------|---------|---------|

| —     | —   | —   | —   | EEADRH3 | EEADRH2 | EEADRH1 | EEADRH0 |

| bit 7 |     |     |     |         |         |         | bit 0   |

| Legend:           |                  |                                |                    |

|-------------------|------------------|--------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as | '0'                |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared           | x = Bit is unknown |

bit 7-4 Unimplemented: Read as '0'

bit 3-0 **EEADRH<3:0>**: Specifies the four Most Significant Address bits or high bits for program memory reads

# 11.3 PWM Mode

The PWM mode generates a Pulse-Width Modulated signal on the CCP1 pin. The duty cycle, period and resolution are determined by the following registers:

- PR2

- T2CON

- CCPR1L

- CCP1CON

In Pulse-Width Modulation (PWM) mode, the CCP module produces up to a 10-bit resolution PWM output on the CCP1 pin. Since the CCP1 pin is multiplexed with the PORT data latch, the TRIS for that pin must be cleared to enable the CCP1 pin output driver.

| Note: | Clearing   | the   | CCP1CON        | register | will |

|-------|------------|-------|----------------|----------|------|

|       | relinquish | n CCF | 1 control of t | he CCP1  | pin. |

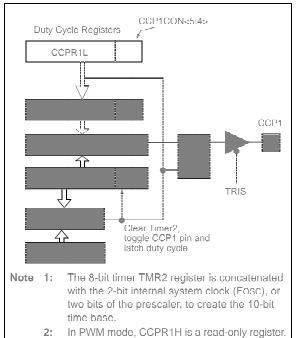

Figure 11-3 shows a simplified block diagram of PWM operation.

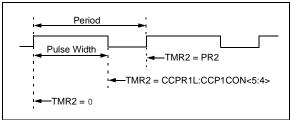

Figure 11-4 shows a typical waveform of the PWM signal.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see **Section 11.3.7** "Setup for PWM Operation".

FIGURE 11-3: SIMPLIFIED PWM BLOCK DIAGRAM

The PWM output (Figure 11-4) has a time base (period) and a time that the output stays high (duty cycle).

FIGURE 11-4: CCP PWM OUTPUT

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                  | R/W-0 | R/W-0 | R/W-0 |

|-----------------|-------|------------------|-------|----------------------------------------|-------|-------|-------|

| PRSEN           | PDC6  | PDC5             | PDC4  | PDC3                                   | PDC2  | PDC1  | PDC0  |

| bit 7           |       |                  |       |                                        |       |       | bit 0 |

|                 |       |                  |       |                                        |       |       |       |

| Legend:         |       |                  |       |                                        |       |       |       |

| R = Readable I  | bit   | W = Writable     | bit   | U = Unimplemented bit, read as '0'     |       |       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknow |       |       | nown  |

### REGISTER 11-3: PWM1CON: ENHANCED PWM CONTROL REGISTER

| bit 7   | <ul> <li>PRSEN: PWM Restart Enable bit</li> <li>1 = Upon auto-shutdown, the ECCPASE bit clears automatically once the shutdown event goes away; the PWM restarts automatically</li> <li>0 = Upon auto-shutdown, ECCPASE must be cleared in software to restart the PWM</li> </ul> |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-0 | PDC<6:0>: PWM Delay Count bits<br>PDCn =Number of Fosc/4 (4 * Tosc) cycles between the scheduled time when a PWM signal <b>should</b><br>transition active and the <b>actual</b> time it transitions active                                                                       |

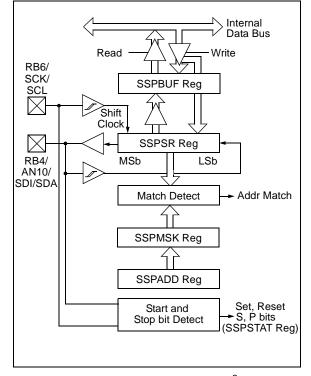

# 13.11 SSP I<sup>2</sup>C Operation

The SSP module in  $l^2$ C mode, fully implements all slave functions, except general call support, and provides interrupts on Start and Stop bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the Standard mode specifications, as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer. These are the RB6/ SCK/SCL pin, which is the clock (SCL), and the RB4/ AN10/SDI/SDA pin, which is the data (SDA).

The SSP module functions are enabled by setting SSP enable bit SSPEN (SSPCON<5>).

FIGURE 13-7: SSP BLOCK DIAGRAM (I<sup>2</sup>C™ MODE)

The SSP module has six registers for the  $I^2C$  operation, which are listed below.

- SSP Control register (SSPCON)

- SSP Status register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift register (SSPSR) Not directly accessible

- SSP Address register (SSPADD)

- SSP Mask register (SSPMSK)

The SSPCON register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address), with Start and Stop bit interrupts enabled to support Firmware Master mode

- I<sup>2</sup>C Slave mode (10-bit address), with Start and Stop bit interrupts enabled to support Firmware Master mode

- I<sup>2</sup>C Start and Stop bit interrupts enabled to support Firmware Master mode; Slave is idle

Selection of any  $I^2C$  mode with the SSPEN bit set forces the SCL and SDA pins to be open drain, provided these pins are programmed to inputs by setting the appropriate TRISB bits. Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the  $I^2C$  module.

# 13.12 Slave Mode

In Slave mode, the SCL and SDA pins must be configured as inputs (TRISB<6,4> are set). The SSP module will override the input state with the output data when required (slave-transmitter).

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge  $(\overline{ACK})$ pulse, and then load the SSPBUF register with the received value currently in the SSPSR register.

There are certain conditions that will cause the SSP module not to give this ACK pulse. They include (either or both):

- a) The Buffer Full bit BF of the SSPSTAT register was set before the transfer was received.

- b) The overflow bit SSPOV of the SSPCON register was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF of the PIR1 register is set. Table 13-3 shows the results of when a data transfer byte is received, given the status of bits BF and SSPOV. The shaded cells show the condition where user software did not properly clear the overflow condition. Flag bit BF is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low for proper operation. For high and low times of the  $I^2C$  specification, as well as the requirements of the SSP module, see **Section 17.0 "Electrical Specifications"**.

### **REGISTER 14-1: CONFIG: CONFIGURATION WORD REGISTER**

| Reserved          | Reserved                                                                                                                                                            | FCMEN                                                                                                                                                                                                       | IESO                                                                                                                      | BOREN1 <sup>(1)</sup> | BOREN0 <sup>(1)</sup>                       | CPD(2                                 |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------------------------------|---------------------------------------|

| bit 13            | Reserved                                                                                                                                                            | FCIVIEIN                                                                                                                                                                                                    | IES0                                                                                                                      | BORENT                | BORENU                                      | bit 7                                 |

| bit 13            |                                                                                                                                                                     |                                                                                                                                                                                                             |                                                                                                                           |                       |                                             | Dit 7                                 |

|                   |                                                                                                                                                                     |                                                                                                                                                                                                             |                                                                                                                           |                       |                                             |                                       |

| CP <sup>(3)</sup> | MCLRE <sup>(4)</sup>                                                                                                                                                | PWRTE                                                                                                                                                                                                       | WDTE                                                                                                                      | FOSC2                 | FOSC1                                       | FOSC0                                 |

| bit 6             |                                                                                                                                                                     |                                                                                                                                                                                                             |                                                                                                                           |                       |                                             | bit 0                                 |

|                   |                                                                                                                                                                     |                                                                                                                                                                                                             |                                                                                                                           |                       |                                             |                                       |

| Legend:           |                                                                                                                                                                     |                                                                                                                                                                                                             |                                                                                                                           |                       |                                             |                                       |

| R = Readable bit  |                                                                                                                                                                     | W = Writable bit                                                                                                                                                                                            |                                                                                                                           | P = Programmable      | ,                                           | U = Unimplemented<br>bit, read as '0' |

| -n = Value at POR | 8                                                                                                                                                                   | '1' = Bit is set                                                                                                                                                                                            |                                                                                                                           | '0' = Bit is cleared  |                                             | x = Bit is unknown                    |

| bit 13-12         | Reserved: Reserve                                                                                                                                                   | d bite. Do Not Lloo                                                                                                                                                                                         |                                                                                                                           |                       |                                             |                                       |

| bit 11            |                                                                                                                                                                     | Clock Monitor Enable                                                                                                                                                                                        | ed hit                                                                                                                    |                       |                                             |                                       |

| DICTI             | 1 = Fail-Safe Clock<br>0 = Fail-Safe Clock                                                                                                                          | Monitor is enabled                                                                                                                                                                                          |                                                                                                                           |                       |                                             |                                       |

| bit 10            |                                                                                                                                                                     | rnal Switchover bit<br>al Switchover mode i<br>al Switchover mode i                                                                                                                                         |                                                                                                                           |                       |                                             |                                       |

| bit 9-8           | 11 = BOR enabled<br>10 = BOR enabled                                                                                                                                | wn-out Reset Selecti<br>during operation and<br>d by SBOREN bit of                                                                                                                                          | d disabled in Sleep                                                                                                       |                       |                                             |                                       |

| bit 7             | CPD: Data Code P                                                                                                                                                    | rotection bit <sup>(2)</sup>                                                                                                                                                                                |                                                                                                                           |                       |                                             |                                       |

|                   |                                                                                                                                                                     | ode protection is dis<br>ode protection is ena                                                                                                                                                              |                                                                                                                           |                       |                                             |                                       |

| bit 6             | <b>CP</b> : Code Protectio<br>1 = Program memo                                                                                                                      | •                                                                                                                                                                                                           | disabled                                                                                                                  |                       |                                             |                                       |

| bit 5             | $1 = \overline{\text{MCLR}}$ pin funct                                                                                                                              | n Function Select bit <sup>(</sup><br>ion is MCLR<br>ion is digital input, M                                                                                                                                |                                                                                                                           | to VDD                |                                             |                                       |

| bit 4             | <b>PWRTE:</b> Power-up<br>1 = PWRT disabled<br>0 = PWRT enabled                                                                                                     |                                                                                                                                                                                                             |                                                                                                                           |                       |                                             |                                       |

| bit 3             | WDTE: Watchdog<br>1 = WDT enabled<br>0 = WDT disabled                                                                                                               | Fimer Enable bit                                                                                                                                                                                            |                                                                                                                           |                       |                                             |                                       |

| bit 2-0           | 110 =RCIO oscillat<br>101 =INTOSC oscill<br>I/O function<br>100 = INTOSCIO o<br>I/O function<br>011 =EC: I/O function<br>010 =HS oscillator:<br>001 = XT oscillator | CLKOUT function o<br>or: I/O function on R<br>lator: CLKOUT function<br>on RA5/OSC1/CLKI<br>scillator: I/O function<br>on RA5/OSC1/CLK<br>on on RA4/OSC2/CI<br>High-speed crystal/<br>: Crystal/resonator o | A4/OSC2/CLKOUT<br>on on RA4/OSC2/C<br>n on RA4/OSC2/CL<br>IN<br>LKOUT pin, CLKIN<br>resonator on RA4/C<br>n RA4/OSC2/CLKC |                       | SC1/CLKIN<br>IN<br>RA5/OSC1/CLKIN<br>/CLKIN |                                       |

| 2: The            | bling Brown-out Rese<br>entire data EEPROM<br>entire program memo                                                                                                   | I will be erased wher                                                                                                                                                                                       | the code protection                                                                                                       | on is turned off.     |                                             |                                       |

4: When MCLR is asserted in INTOSC or RC mode, the internal clock oscillator is disabled.

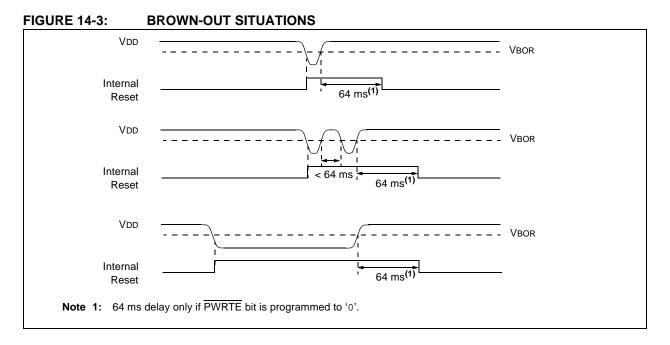

### 14.2.4 BROWN-OUT RESET (BOR)

The BOREN0 and BOREN1 bits in the Configuration Word register select one of four BOR modes. Two modes have been added to allow software or hardware control of the BOR enable. When BOREN<1:0> = 01, the SBOREN bit (PCON<4>) enables/disables the BOR allowing it to be controlled in software. By selecting BOREN<1:0>, the BOR is automatically disabled in Sleep to conserve power and enabled on wake-up. In this mode, the SBOREN bit is disabled. See Register 14-2 for the Configuration Word definition.

If VDD falls below VBOR for greater than parameter (TBOR) (see **Section 17.0 "Electrical Specifications"**), the Brown-out situation will reset the device. This will occur regardless of VDD slew rate. A Reset is not insured to occur if VDD falls below VBOR for less than parameter (TBOR).

On any Reset (Power-on, Brown-out Reset, Watchdog Timer, etc.), the chip will remain in Reset until VDD rises above VBOR (see Figure 14-3). The Power-up Timer will now be invoked, if enabled and will keep the chip in Reset an additional 64 ms.

Note: The Power-up Timer is enabled by the PWRTE bit in the Configuration Word register.

If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above VBOR, the Power-up Timer will execute a 64 ms Reset.

# 16.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

## 16.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

### 16.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

# 16.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

# 16.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

## 17.2 DC Characteristics: PIC16F631/677/685/687/689/690-I (Industrial) PIC16F631/677/685/687/689/690-E (Extended)

| DC CHA | RACTERISTICS                           |         | rd Opera<br>ng tempe |      | ditions (unless otherwise stated)<br>-40°C $\leq$ TA $\leq$ +85°C for industrial<br>-40°C $\leq$ TA $\leq$ +125°C for extended |     |                           |  |

|--------|----------------------------------------|---------|----------------------|------|--------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------|--|

| Param  | Device Characteristics                 | Min.    | Тур†                 | Max. | Units                                                                                                                          |     | Conditions                |  |

| No.    | Device Characteristics                 | IVIIII. | וקעי                 | Wax. | onits                                                                                                                          | Vdd | Note                      |  |

| D010   | Supply Current (IDD) <sup>(1, 2)</sup> | —       | 13                   | 19   | μA                                                                                                                             | 2.0 | Fosc = 32 kHz             |  |

|        |                                        | —       | 22                   | 30   | μA                                                                                                                             | 3.0 | LP Oscillator mode        |  |

|        |                                        | —       | 33                   | 60   | μA                                                                                                                             | 5.0 |                           |  |

| D011*  |                                        | —       | 140                  | 240  | μA                                                                                                                             | 2.0 | Fosc = 1 MHz              |  |

|        |                                        | —       | 220                  | 380  | μA                                                                                                                             | 3.0 | XT Oscillator mode        |  |

|        |                                        |         | 380                  | 550  | μA                                                                                                                             | 5.0 |                           |  |

| D012   |                                        | —       | 260                  | 360  | μA                                                                                                                             | 2.0 | Fosc = 4 MHz              |  |

|        |                                        | —       | 420                  | 650  | μA                                                                                                                             | 3.0 | XT Oscillator mode        |  |

|        |                                        |         | 0.8                  | 1.1  | mA                                                                                                                             | 5.0 |                           |  |

| D013*  |                                        | _       | 130                  | 220  | μA                                                                                                                             | 2.0 | Fosc = 1 MHz              |  |

|        |                                        |         | 215                  | 360  | μA                                                                                                                             | 3.0 | EC Oscillator mode        |  |

|        |                                        | —       | 360                  | 520  | μA                                                                                                                             | 5.0 |                           |  |

| D014   |                                        | _       | 220                  | 340  | μA                                                                                                                             | 2.0 | Fosc = 4 MHz              |  |

|        |                                        |         | 375                  | 550  | μA                                                                                                                             | 3.0 | EC Oscillator mode        |  |

|        |                                        |         | 0.65                 | 1.0  | mA                                                                                                                             | 5.0 |                           |  |

| D015   |                                        | _       | 8                    | 20   | μA                                                                                                                             | 2.0 | Fosc = 31 kHz             |  |

|        |                                        |         | 16                   | 40   | μA                                                                                                                             | 3.0 | LFINTOSC mode             |  |

|        |                                        | —       | 31                   | 65   | μA                                                                                                                             | 5.0 |                           |  |

| D016*  |                                        | —       | 340                  | 450  | μA                                                                                                                             | 2.0 | Fosc = 4 MHz              |  |

|        |                                        | —       | 500                  | 700  | μA                                                                                                                             | 3.0 | HFINTOSC mode             |  |

|        |                                        |         | 0.8                  | 1.2  | mA                                                                                                                             | 5.0 |                           |  |

| D017   |                                        | _       | 410                  | 650  | μA                                                                                                                             | 2.0 | Fosc = 8 MHz              |  |

|        |                                        | —       | 700                  | 950  | μA                                                                                                                             | 3.0 | HFINTOSC mode             |  |

|        |                                        |         | 1.30                 | 1.65 | mA                                                                                                                             | 5.0 |                           |  |

| D018   |                                        | _       | 230                  | 400  | μA                                                                                                                             | 2.0 | Fosc = 4 MHz              |  |

|        |                                        | —       | 400                  | 680  | μA                                                                                                                             | 3.0 | EXTRC mode <sup>(3)</sup> |  |

|        |                                        |         | 0.63                 | 1.1  | mA                                                                                                                             | 5.0 |                           |  |

| D019   |                                        | —       | 3.8                  | 5.0  | mA                                                                                                                             | 4.5 | Fosc = 20 MHz             |  |

|        |                                        | —       | 4.0                  | 5.45 | mA                                                                                                                             | 5.0 | HS Oscillator mode        |  |

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The test conditions for all IDD measurements in Active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

**3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in kΩ.

4: The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral ∆ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

5: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

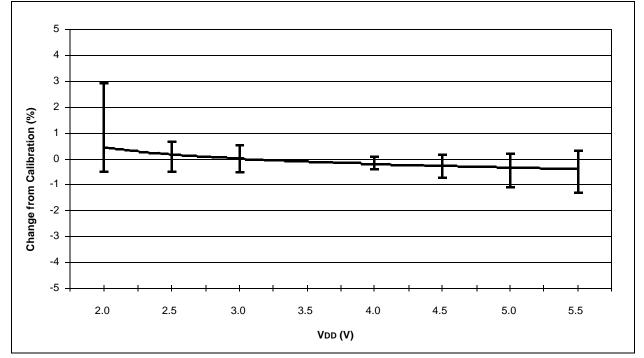

FIGURE 18-39: TYPICAL HFINTOSC FREQUENCY CHANGE vs. VDD (25°C)

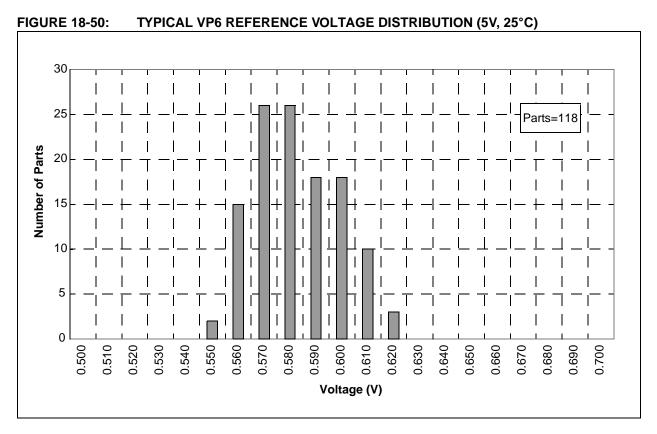

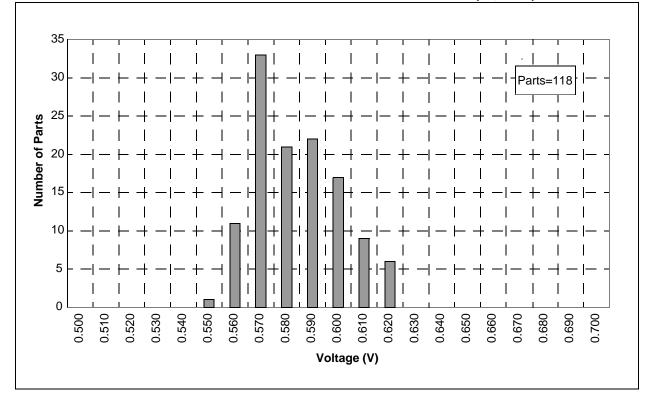

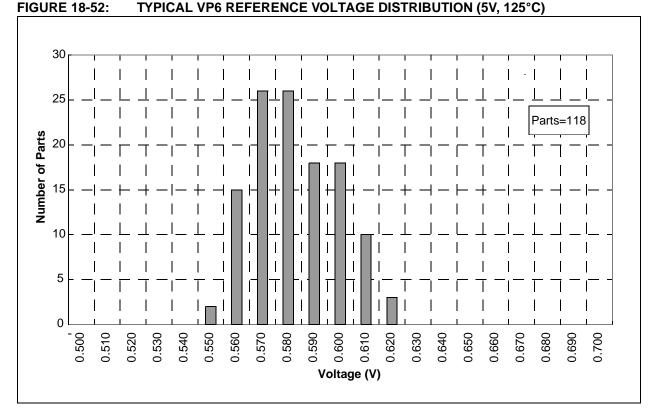

FIGURE 18-51: TYPICAL VP6 REFERENCE VOLTAGE DISTRIBUTION (5V, 85°C)

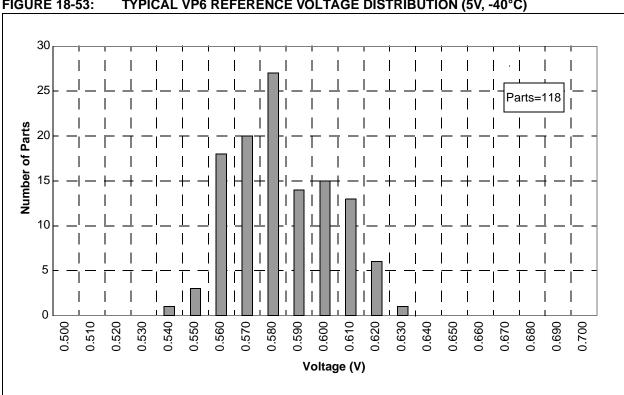

**FIGURE 18-53:** TYPICAL VP6 REFERENCE VOLTAGE DISTRIBUTION (5V, -40°C)

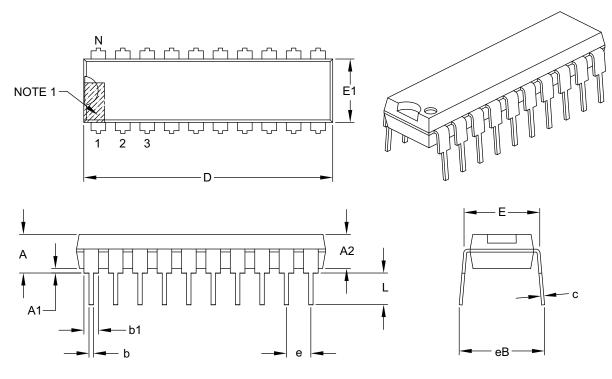

### 19.2 Package Details

The following sections give the technical details of the packages.

# 20-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

|                            | Units       |      |          |       |

|----------------------------|-------------|------|----------|-------|

| Dimens                     | sion Limits | MIN  | NOM      | MAX   |

| Number of Pins             | Ν           |      | 20       |       |

| Pitch                      | е           |      | .100 BSC |       |

| Top to Seating Plane       | Α           | -    | -        | .210  |

| Molded Package Thickness   | A2          | .115 | .130     | .195  |

| Base to Seating Plane      | A1          | .015 | -        | -     |

| Shoulder to Shoulder Width | E           | .300 | .310     | .325  |

| Molded Package Width       | E1          | .240 | .250     | .280  |

| Overall Length             | D           | .980 | 1.030    | 1.060 |

| Tip to Seating Plane       | L           | .115 | .130     | .150  |

| Lead Thickness             | С           | .008 | .010     | .015  |

| Upper Lead Width           | b1          | .045 | .060     | .070  |

| Lower Lead Width           | b           | .014 | .018     | .022  |

| Overall Row Spacing §      | eB          | -    | -        | .430  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-019B