# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I²C, SPI                                                                |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                        |

| Number of I/O              | 18                                                                      |

| Program Memory Size        | 3.5KB (2K x 14)                                                         |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 256 x 8                                                                 |

| RAM Size                   | 128 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Through Hole                                                            |

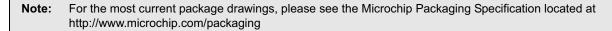

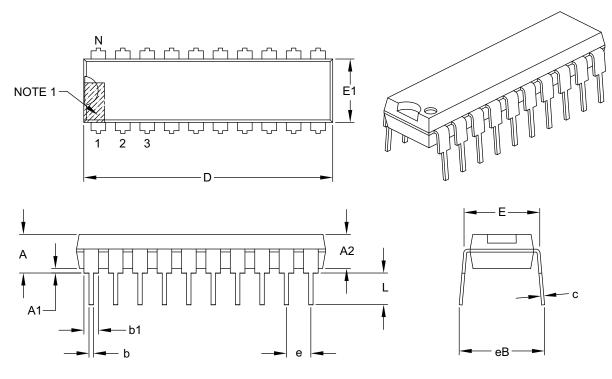

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                 |

| Supplier Device Package    | 20-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f677-e-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.2.2.1 STATUS Register

The STATUS register, shown in Register 2-1, contains:

- the arithmetic status of the ALU

- the Reset status

- the bank select bits for data memory (GPR and SFR)

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS, will clear the upper three bits and set the Z bit. This leaves the STATUS register as `000u u1uu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits, see Section 15.0 "Instruction Set Summary"

Note 1: The <u>C</u> and <u>DC</u> bits operate as a Borrow and <u>Digit</u> Borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

| R/W-0 | R/W-0 | R/W-0 | R-1 | R-1 | R/W-x | R/W-x             | R/W-x            |

|-------|-------|-------|-----|-----|-------|-------------------|------------------|

| IRP   | RP1   | RP0   | TO  | PD  | Z     | DC <sup>(1)</sup> | C <sup>(1)</sup> |

| bit 7 |       |       |     |     |       |                   | bit 0            |

| Legend:           |                                                   |                                                                                                           |                                                                                                      |                      |  |

|-------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------|--|

| R = Readable bit  |                                                   | W = Writable bit                                                                                          | U = Unimplemented bit                                                                                | , read as '0'        |  |

| -n = Value at POR |                                                   | '1' = Bit is set                                                                                          | '0' = Bit is cleared                                                                                 | x = Bit is unknown   |  |

| bit 7             | 1 <b>= Ban</b>                                    | gister Bank Select bit (used<br>k 2, 3 (100h-1FFh)<br>k 0, 1 (00h-FFh)                                    | for indirect addressing)                                                                             |                      |  |

| bit 6-5           | <b>RP&lt;1:0</b><br>00 = Ba<br>01 = Ba<br>10 = Ba | Register Bank Select bits<br>ink 0 (00h-7Fh)<br>ink 1 (80h-FFh)<br>ink 2 (100h-17Fh)<br>ink 3 (180h-1FFh) | (used for direct addressing)                                                                         |                      |  |

| bit 4             | 1 = Afte                                          | ne-out bit<br>r power-up, CLRWDT instructi<br>/DT time-out occurred                                       | ion or SLEEP instruction                                                                             |                      |  |

| bit 3             | 1 = Afte                                          | wer-down bit<br>r power-up or by the CLRWD<br>execution of the SLEEP instru                               |                                                                                                      |                      |  |

| bit 2             |                                                   | bit<br>result of an arithmetic or log<br>result of an arithmetic or log                                   | •                                                                                                    |                      |  |

| bit 1             | <b>DC:</b> Dig<br>1 = A ca                        | •                                                                                                         | DDLW , SUBLW , SUBWF instruct                                                                        | ions) <sup>(1)</sup> |  |

| bit 0             | <b>C:</b> Carry<br>1 = A ca                       | /Borrow bit <sup>(1)</sup> (ADDWF, ADDL<br>arry-out from the Most Signifi                                 | W, SUBLW, SUBWF instruction<br>cant bit of the result occurred<br>ificant bit of the result occurred |                      |  |

bit of the source register.

### 2.2.2.6 PIR1 Register

The PIR1 register contains the interrupt flag bits, as shown in Register 2-6.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

# REGISTER 2-6: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

| U-0   | R/W-0               | R-0                 | R-0                 | R/W-0                | R/W-0                 | R/W-0                 | R/W-0  |

|-------|---------------------|---------------------|---------------------|----------------------|-----------------------|-----------------------|--------|

| —     | ADIF <sup>(5)</sup> | RCIF <sup>(3)</sup> | TXIF <sup>(3)</sup> | SSPIF <sup>(4)</sup> | CCP1IF <sup>(2)</sup> | TMR2IF <sup>(1)</sup> | TMR1IF |

| bit 7 |                     |                     |                     |                      |                       |                       | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7 | Unimplemented: Read as '0'                                                                                                                          |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | ADIF: A/D Converter Interrupt Flag bit <sup>(5)</sup>                                                                                               |

|       | <ul> <li>1 = A/D conversion complete (must be cleared in software)</li> <li>0 = A/D conversion has not completed or has not been started</li> </ul> |

| bit 5 | RCIF: EUSART Receive Interrupt Flag bit <sup>(3)</sup>                                                                                              |

|       | <ul> <li>1 = The EUSART receive buffer is full (cleared by reading RCREG)</li> <li>0 = The EUSART receive buffer is not full</li> </ul>             |

| bit 4 | <b>TXIF:</b> EUSART Transmit Interrupt Flag bit <sup>(3)</sup>                                                                                      |

|       | <ul> <li>1 = The EUSART transmit buffer is empty (cleared by writing to TXREG)</li> <li>0 = The EUSART transmit buffer is full</li> </ul>           |

| bit 3 | SSPIF: Synchronous Serial Port (SSP) Interrupt Flag bit <sup>(4)</sup>                                                                              |

|       | <ul> <li>1 = The Transmission/Reception is complete (must be cleared in software)</li> <li>0 = Waiting to Transmit/Receive</li> </ul>               |

| bit 2 | CCP1IF: CCP1 Interrupt Flag bit <sup>(2)</sup>                                                                                                      |

|       | Capture mode:                                                                                                                                       |

|       | <ul> <li>1 = A TMR1 register capture occurred (must be cleared in software)</li> <li>0 = No TMR1 register capture occurred</li> </ul>               |

|       | Compare mode:                                                                                                                                       |

|       | <ul> <li>1 = A TMR1 register compare match occurred (must be cleared in software)</li> <li>0 = No TMR1 register compare match occurred</li> </ul>   |

|       | <u>PWM mode:</u>                                                                                                                                    |

|       | Unused in this mode                                                                                                                                 |

| bit 1 | TMR2IF: Timer2 to PR2 Interrupt Flag bit <sup>(1)</sup>                                                                                             |

|       | <ul> <li>1 = A Timer2 to PR2 match occurred (must be cleared in software)</li> <li>0 = No Timer2 to PR2 match occurred</li> </ul>                   |

| bit 0 | TMR1IF: Timer1 Overflow Interrupt Flag bit                                                                                                          |

|       | <ul> <li>1 = The TMR1 register overflowed (must be cleared in software)</li> <li>0 = The TMR1 register did not overflow</li> </ul>                  |

| Note  | 1: PIC16F685/PIC16F690 only.                                                                                                                        |

|       | 2: PIC16F685/PIC16F689/PIC16F690 only.                                                                                                              |

|       | 3: PIC16F687/PIC16F689/PIC16F690 only.                                                                                                              |

|       | 4: PIC16F677/PIC16F687/PIC16F689/PIC16F690 only.                                                                                                    |

|       | 5: PIC16F677/PIC16F685/PIC16F687/PIC16F689/PIC16F690 only.                                                                                          |

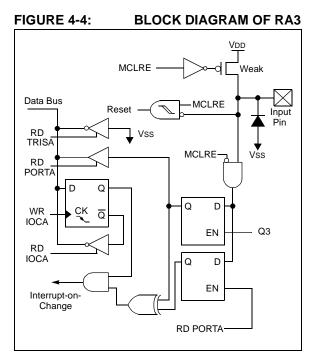

### 4.2.5.4 RA3/MCLR/VPP

Figure 4-4 shows the diagram for this pin. The RA3/ MCLR/VPP pin is configurable to function as one of the following:

- a general purpose input

- as Master Clear Reset with weak pull-up

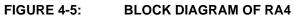

## 4.2.5.5 RA4/AN3/T1G/OSC2/CLKOUT

Figure 4-5 shows the diagram for this pin. The RA4/ AN3/T1G/OSC2/CLKOUT pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC (except PIC16F631)

- a Timer1 gate input

- a crystal/resonator connection

- · a clock output

- 2: With CLKOUT option.

- 3: ANSEL determines Analog Input mode.

- 4: Not implemented on PIC16F631.

# 6.12 Timer1 Control Register

The Timer1 Control register (T1CON), shown in Register 6-1, is used to control Timer1 and select the various features of the Timer1 module.

### REGISTER 6-1: T1CON: TIMER 1 CONTROL REGISTER

| R/W-0                    | R/W-0                                                                                             | R/W-0                                                                                         | R/W-0                  | R/W-0             | R/W-0          | R/W-0            | R/W-0      |  |  |  |

|--------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------|-------------------|----------------|------------------|------------|--|--|--|

| T1GINV <sup>(1)</sup>    | ) TMR1GE <sup>(2)</sup>                                                                           | T1CKPS1                                                                                       | T1CKPS0                | T1OSCEN           | T1SYNC         | TMR1CS           | TMR10N     |  |  |  |

| bit 7                    |                                                                                                   |                                                                                               |                        |                   |                |                  | bit 0      |  |  |  |

|                          |                                                                                                   |                                                                                               |                        |                   |                |                  |            |  |  |  |

| Legend:                  |                                                                                                   |                                                                                               |                        |                   |                |                  |            |  |  |  |

| R = Readab               |                                                                                                   | W = Writable                                                                                  |                        | U = Unimplen      |                |                  |            |  |  |  |

| -n = Value a             | IT POR                                                                                            | '1' = Bit is set                                                                              |                        | '0' = Bit is clea | ared           | x = Bit is unki  | nown       |  |  |  |

| bit 7 <b>T1GINV:</b> Tir |                                                                                                   | er1 Gate Invert                                                                               | bit(1)                 |                   |                |                  |            |  |  |  |

|                          |                                                                                                   |                                                                                               |                        | ints when Timer   | 1 gate signal  | is high)         |            |  |  |  |

|                          |                                                                                                   |                                                                                               |                        | nts when gate is  |                | 0 /              |            |  |  |  |

| bit 6                    | TMR1GE: Tin                                                                                       | ner1 Gate Ena                                                                                 | ble bit <sup>(2)</sup> |                   |                |                  |            |  |  |  |

|                          | If TMR1ON =                                                                                       |                                                                                               |                        |                   |                |                  |            |  |  |  |

|                          | This bit is igno                                                                                  |                                                                                               |                        |                   |                |                  |            |  |  |  |

|                          | <u>If TMR1ON =</u><br>1 = Timer1 co                                                               |                                                                                               | olled by the Ti        | mer1 Gate fund    | tion           |                  |            |  |  |  |

|                          |                                                                                                   | always countir                                                                                |                        |                   |                |                  |            |  |  |  |

| bit 5-4                  | T1CKPS<1:0                                                                                        | >: Timer1 Inpu                                                                                | t Clock Presca         | ale Select bits   |                |                  |            |  |  |  |

|                          | 11 = 1:8 Pres                                                                                     | 11 = 1:8 Prescale Value                                                                       |                        |                   |                |                  |            |  |  |  |

|                          |                                                                                                   | 10 = 1:4 Prescale Value                                                                       |                        |                   |                |                  |            |  |  |  |

|                          | 01 = 1:2 Prescale Value<br>00 = 1:1 Prescale Value                                                |                                                                                               |                        |                   |                |                  |            |  |  |  |

| bit 3                    |                                                                                                   | P Oscillator En                                                                               | able Control b         | it                |                |                  |            |  |  |  |

|                          | If INTOSC wit                                                                                     | If INTOSC without CLKOUT oscillator is active:                                                |                        |                   |                |                  |            |  |  |  |

|                          |                                                                                                   | tor is enabled                                                                                | for Timer1 cloc        | ck                |                |                  |            |  |  |  |

|                          | 0 = LP oscilla<br><u>Else:</u>                                                                    | 0 = LP oscillator is off                                                                      |                        |                   |                |                  |            |  |  |  |

|                          | This bit is igno                                                                                  | ored                                                                                          |                        |                   |                |                  |            |  |  |  |

| bit 2                    | 0                                                                                                 |                                                                                               | lock Input Syr         | hchronization Co  | ontrol bit     |                  |            |  |  |  |

|                          |                                                                                                   | <b>T1SYNC:</b> Timer1 External Clock Input Synchronization Control bit<br><u>TMR1CS = 1</u> : |                        |                   |                |                  |            |  |  |  |

|                          |                                                                                                   | 1 = Do not synchronize external clock input                                                   |                        |                   |                |                  |            |  |  |  |

|                          | 0 = Synchronize external clock input                                                              |                                                                                               |                        |                   |                |                  |            |  |  |  |

|                          | <u>TMR1CS = 0:</u><br>This bit is ign                                                             |                                                                                               | ses the interna        | al clock          |                |                  |            |  |  |  |

| bit 1                    | This bit is ignored. Timer1 uses the internal clock <b>TMR1CS:</b> Timer1 Clock Source Select bit |                                                                                               |                        |                   |                |                  |            |  |  |  |

|                          | 1 = External o                                                                                    | 1 = External clock from T1CKI pin (on the rising edge)                                        |                        |                   |                |                  |            |  |  |  |

|                          | 0 = Internal cl                                                                                   |                                                                                               |                        |                   |                |                  |            |  |  |  |

| bit 0                    | TMR1ON: Tin                                                                                       | ner1 On bit                                                                                   |                        |                   |                |                  |            |  |  |  |

|                          | 1 = Enables T                                                                                     |                                                                                               |                        |                   |                |                  |            |  |  |  |

|                          | 0 = Stops Tim                                                                                     | ner1                                                                                          |                        |                   |                |                  |            |  |  |  |

|                          | 1GINV bit inverts                                                                                 | -                                                                                             |                        |                   |                |                  |            |  |  |  |

|                          | MR1GE bit must                                                                                    |                                                                                               |                        | or C2OUT, as s    | elected by the | T1GSS bit of the | ne CM2CON1 |  |  |  |

| r                        | egister, as a Time                                                                                | eri gate source                                                                               |                        |                   |                |                  |            |  |  |  |

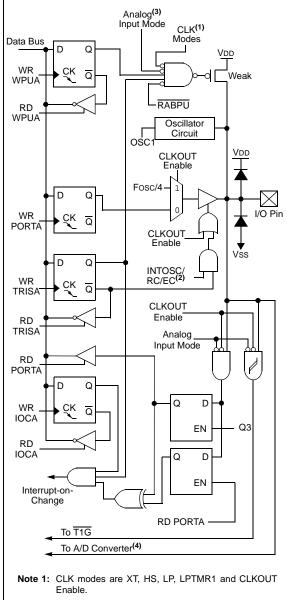

### 8.7 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 8-6. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

- Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

- 2: Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

### FIGURE 8-6: ANALOG INPUT MODEL

| R/W-0                                 | R/W-0                                                                                  | R/W-0             | R/W-0                                                                                                 | R/W-0            | R/W-0           | R/W-0            | R/W-0 |  |  |  |  |  |

|---------------------------------------|----------------------------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------|------------------|-----------------|------------------|-------|--|--|--|--|--|

| ADFM                                  | VCFG                                                                                   | CHS3              | CHS2                                                                                                  | CHS1             | CHS0            | GO/DONE          | ADON  |  |  |  |  |  |

| bit 7                                 |                                                                                        |                   |                                                                                                       |                  |                 |                  | bit 0 |  |  |  |  |  |

|                                       |                                                                                        |                   |                                                                                                       |                  |                 |                  |       |  |  |  |  |  |

| Legend:                               |                                                                                        |                   |                                                                                                       |                  |                 |                  |       |  |  |  |  |  |

| R = Readabl                           | e bit                                                                                  | W = Writable      | bit                                                                                                   | U = Unimpler     | mented bit, rea | ad as '0'        |       |  |  |  |  |  |

| R = Readable bit<br>-n = Value at POR |                                                                                        | '1' = Bit is set  |                                                                                                       | '0' = Bit is cle | ared            | x = Bit is unkn  | own   |  |  |  |  |  |

| 1 2 7                                 |                                                                                        | о · Б             |                                                                                                       | 1 41.9           |                 |                  |       |  |  |  |  |  |

| bit 7                                 |                                                                                        | Conversion Res    | sult Format Se                                                                                        | elect bit        |                 |                  |       |  |  |  |  |  |

|                                       | 1 = Right jus<br>0 = Left justi                                                        |                   |                                                                                                       |                  |                 |                  |       |  |  |  |  |  |

| bit 6                                 | VCFG: Volta                                                                            | ige Reference b   | it                                                                                                    |                  |                 |                  |       |  |  |  |  |  |

|                                       | 1 = VREF pin                                                                           | 1                 |                                                                                                       |                  |                 |                  |       |  |  |  |  |  |

|                                       | 0 = VDD                                                                                |                   |                                                                                                       |                  |                 |                  |       |  |  |  |  |  |

| bit 5-2                               | CHS<3:0>: /                                                                            | Analog Channe     | el Select bits                                                                                        |                  |                 |                  |       |  |  |  |  |  |

|                                       | 0000 = AN0                                                                             |                   |                                                                                                       |                  |                 |                  |       |  |  |  |  |  |

|                                       | 0001 = AN1                                                                             |                   |                                                                                                       |                  |                 |                  |       |  |  |  |  |  |

|                                       | 0010 = AN2                                                                             |                   |                                                                                                       |                  |                 |                  |       |  |  |  |  |  |

|                                       | 0011 = AN3                                                                             |                   |                                                                                                       |                  |                 |                  |       |  |  |  |  |  |

|                                       | 0100 = AN4                                                                             |                   |                                                                                                       |                  |                 |                  |       |  |  |  |  |  |

|                                       | 0101 = AN5                                                                             |                   |                                                                                                       |                  |                 |                  |       |  |  |  |  |  |

|                                       | 0110 = AN6<br>0111 = AN7                                                               |                   |                                                                                                       |                  |                 |                  |       |  |  |  |  |  |

|                                       | 1000 = AN8                                                                             |                   |                                                                                                       |                  |                 |                  |       |  |  |  |  |  |

|                                       | 1000 = ANS<br>1001 = ANS                                                               |                   |                                                                                                       |                  |                 |                  |       |  |  |  |  |  |

|                                       | 1010 = AN1                                                                             |                   |                                                                                                       |                  |                 |                  |       |  |  |  |  |  |

|                                       | 1011 = AN11                                                                            |                   |                                                                                                       |                  |                 |                  |       |  |  |  |  |  |

|                                       | 1100 = CVR                                                                             | EF                |                                                                                                       |                  |                 |                  |       |  |  |  |  |  |

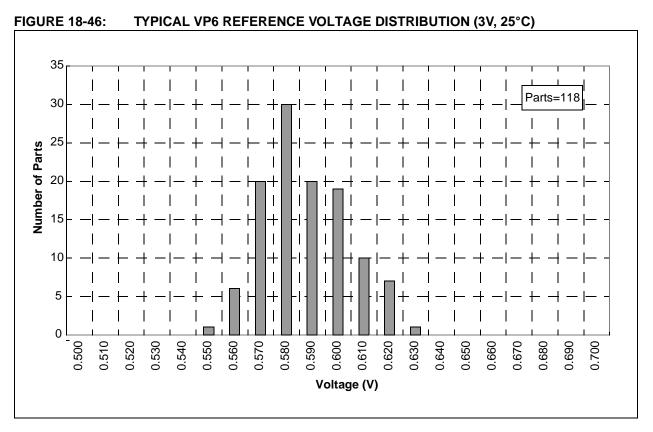

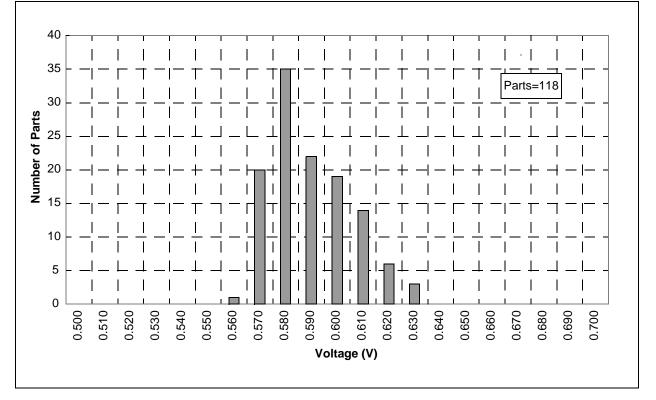

|                                       | 1101 = 0.6V                                                                            | ' Fixed Voltage I | Reference                                                                                             |                  |                 |                  |       |  |  |  |  |  |

|                                       | 1110 = Res                                                                             | erved. Do not us  | se.                                                                                                   |                  |                 |                  |       |  |  |  |  |  |

|                                       | 1111 = Res                                                                             | erved. Do not us  | se.                                                                                                   |                  |                 |                  |       |  |  |  |  |  |

| bit 1                                 | GO/DONE: A/D Conversion Status bit                                                     |                   |                                                                                                       |                  |                 |                  |       |  |  |  |  |  |

|                                       | 1 = A/D conversion cycle in progress. Setting this bit starts an A/D conversion cycle. |                   |                                                                                                       |                  |                 |                  |       |  |  |  |  |  |

|                                       |                                                                                        |                   |                                                                                                       |                  | e A/D convers   | sion has complet | ed.   |  |  |  |  |  |

|                                       | $0 = A/D \operatorname{conv}$                                                          | version complet   | ed/not in prog                                                                                        | ress             |                 |                  |       |  |  |  |  |  |

| bit 0                                 | ADON: ADC                                                                              | Enable bit        |                                                                                                       |                  |                 |                  |       |  |  |  |  |  |

|                                       | 1 = ADC is e                                                                           | enabled           |                                                                                                       |                  |                 |                  |       |  |  |  |  |  |

|                                       |                                                                                        | licoblad and an   | <ul> <li>1 = ADC is enabled</li> <li>0 = ADC is disabled and consumes no operating current</li> </ul> |                  |                 |                  |       |  |  |  |  |  |

### REGISTER 9-1: ADCON0: A/D CONTROL REGISTER 0

### 10.1.2 READING THE DATA EEPROM MEMORY

To read a data memory location, the user must write the address to the EEADR register, clear the EEPGD control bit of the EECON1 register, and then set control bit RD. The data is available at the very next cycle, in the EEDAT register; therefore, it can be read in the next instruction. EEDAT will hold this value until another read or until it is written to by the user (during a write operation).

### EXAMPLE 10-1: DATA EEPROM READ

| BANKSEL | EEADR ;     |                         |

|---------|-------------|-------------------------|

| MOVF    | DATA_EE_ADD | R, W;                   |

| MOVWF   | EEADR       | ;Data Memory            |

|         |             | ;Address to read        |

| BANKSEL | EECON1      | ;                       |

| BCF     | EECON1, EEP | GD;Point to DATA memory |

| BSF     | EECON1, RD  | ;EE Read                |

| BANKSEL | EEDAT       | ;                       |

| MOVF    | EEDAT, W    | ;W = EEDAT              |

| BANKSEL | PORTA       | ;Bank 0                 |

|         |             |                         |

# 10.1.3 WRITING TO THE DATA EEPROM MEMORY

To write an EEPROM data location, the user must first write the address to the EEADR register and the data to the EEDAT register. Then the user must follow a specific sequence to initiate the write for each byte.

The write will not initiate if the specific sequence is not followed exactly (write 55h to EECON2, write AAh to EECON2, then set WR bit) for each byte. Interrupts should be disabled during this code segment.

Additionally, the WREN bit in EECON1 must be set to enable write. This mechanism prevents accidental writes to data EEPROM due to errant (unexpected) code execution (i.e., lost programs). The user should keep the WREN bit clear at all times, except when updating EEPROM. The WREN bit is not cleared by hardware.

After a write sequence has been initiated, clearing the WREN bit will not affect this write cycle. The WR bit will be inhibited from being set unless the WREN bit is set.

At the completion of the write cycle, the WR bit is cleared in hardware and the EE Write Complete Interrupt Flag bit (EEIF) is set. The user can either enable this interrupt or poll this bit. EEIF must be cleared by software.

#### BANKSELEEADR MOVFDATA\_EE\_ADDR, W; MOVWFEEADR ;Data Memory Address to write MOVFDATA\_EE\_DATA, W; MOVWFEEDAT ;Data Memory Value to write BANKSELEECON1 ; BCF EECON1, EEPGD; Point to DATA memory BSF EECON1, WREN; Enable writes BCF INTCON, GIE ; Disable INTs. BTFSCINTCON, GIE;SEE AN576 GOTO\$-2 MOVLW55h ; Required Sequence MOVWFEECON2 ;Write 55h MOVLWAAh ; MOVWFEECON2 ;Write AAh BSF EECON1, WR ;Set WR bit to begin write BSF INTCON, GIE ; Enable INTs. SLEEP ;Wait for interrupt to signal write complete (optional) BCF EECON1, WREN; Disable writes BANKSEL0x00 ;Bank 0

### EXAMPLE 10-2: DATA EEPROM WRITE

### 12.3.1 AUTO-BAUD DETECT

The EUSART module supports automatic detection and calibration of the baud rate.

In the Auto-Baud Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX signal, the RX signal is timing the BRG. The Baud Rate Generator is used to time the period of a received 55h (ASCII "U") which is the Sync character for the LIN bus. The unique feature of this character is that it has five rising edges including the Stop bit edge.

Setting the ABDEN bit of the BAUDCTL register starts the auto-baud calibration sequence (Figure 12-6). While the ABD sequence takes place, the EUSART state machine is held in Idle. On the first rising edge of the receive line, after the Start bit, the SPBRG begins counting up using the BRG counter clock as shown in Table 12-6. The fifth rising edge will occur on the RX pin at the end of the eighth bit period. At that time, an accumulated value totaling the proper BRG period is left in the SPBRGH, SPBRG register pair, the ABDEN bit is automatically cleared and the RCIF interrupt flag is set. The value in the RCREG needs to be read to clear the RCIF interrupt. RCREG content should be discarded. When calibrating for modes that do not use the SPBRGH register the user can verify that the SPBRG register did not overflow by checking for 00h in the SPBRGH register.

The BRG auto-baud clock is determined by the BRG16 and BRGH bits as shown in Table 12-6. During ABD, both the SPBRGH and SPBRG registers are used as a 16-bit counter, independent of the BRG16 bit setting. While calibrating the baud rate period, the SPBRGH and SPBRG registers are clocked at 1/8th the BRG base clock rate. The resulting byte measurement is the average bit time when clocked at full speed.

- Note 1: If the WUE bit is set with the ABDEN bit, auto-baud detection will occur on the byte following the Break character (see Section 12.3.2 "Auto-Wake-up on Break").

- 2: It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible.

- During the auto-baud process, the autobaud counter starts counting at 1. Upon completion of the auto-baud sequence, to achieve maximum accuracy, subtract 1 from the SPBRGH:SPBRG register pair.

### TABLE 12-6: BRG COUNTER CLOCK RATES

| BRG16 | BRGH | BRG Base<br>Clock | BRG ABD<br>Clock |

|-------|------|-------------------|------------------|

| 0     | 0    | Fosc/64           | Fosc/512         |

| 0     | 1    | Fosc/16           | Fosc/128         |

| 1     | 0    | Fosc/16           | Fosc/128         |

| 1     | 1    | Fosc/4            | Fosc/32          |

|       |      |                   |                  |

**Note:** During the ABD sequence, SPBRG and SPBRGH registers are both used as a 16-bit counter, independent of BRG16 setting.

### FIGURE 12-6: AUTOMATIC BAUD RATE CALIBRATION

| BRG Value               | XXXXh         | 0000h |         | 001Ch              |

|-------------------------|---------------|-------|---------|--------------------|

| RX pin                  |               | Start |         | Edge #5<br>top bit |

| BRG Clock               |               | www.  |         |                    |

| ABDEN bit               | Set by User — |       |         | — Auto Cleared     |

| RCIDL                   |               |       |         |                    |

| RCIF bit<br>(Interrupt) |               |       |         |                    |

| Read<br>RCREG           |               |       |         | <u>`</u>           |

| SPBRG                   |               |       | XXh X_  | 1Ch                |

| SPBRGH                  |               |       | XXh XXh | 00h                |

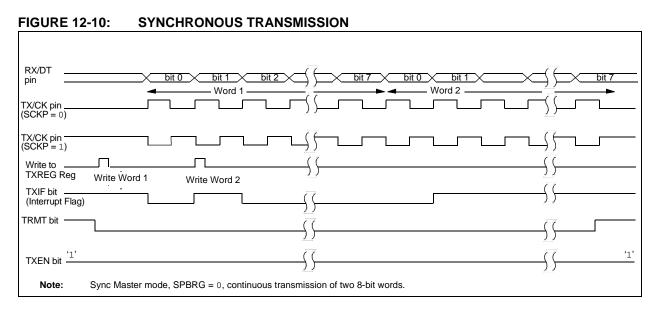

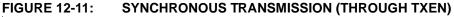

#### TABLE 12-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Name    | Bit 7                              | Bit 6      | Bit 5       | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|------------------------------------|------------|-------------|--------|-------|--------|--------|--------|----------------------|---------------------------------|

| BAUDCTL | ABDOVF                             | RCIDL      | _           | SCKP   | BRG16 | _      | WUE    | ABDEN  | 01-0 0-00            | 01-0 0-00                       |

| INTCON  | GIE                                | PEIE       | TOIE        | INTE   | RABIE | T0IF   | INTF   | RABIF  | 0000 000x            | 0000 000x                       |

| PIE1    | _                                  | ADIE       | RCIE        | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | -000 0000            | -000 0000                       |

| PIR1    | _                                  | ADIF       | RCIF        | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | -000 0000            | -000 0000                       |

| RCREG   | EUSART F                           | Receive Da | ta Register |        |       |        |        |        | 0000 0000            | 0000 0000                       |

| RCSTA   | SPEN                               | RX9        | SREN        | CREN   | ADDEN | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| SPBRG   | BRG7                               | BRG6       | BRG5        | BRG4   | BRG3  | BRG2   | BRG1   | BRG0   | 0000 0000            | 0000 0000                       |

| SPBRGH  | BRG15                              | BRG14      | BRG13       | BRG12  | BRG11 | BRG10  | BRG9   | BRG8   | 0000 0000            | 0000 0000                       |

| TRISB   | TRISB7                             | TRISB6     | TRISB5      | TRISB4 |       |        |        |        | 1111                 | 1111                            |

| TXREG   | XREG EUSART Transmit Data Register |            |             |        |       |        |        |        |                      | 0000 0000                       |

| TXSTA   | CSRC                               | TX9        | TXEN        | SYNC   | SENDB | BRGH   | TRMT   | TX9D   | 0000 0010            | 0000 0010                       |

| Logondu | Logand:                            |            |             |        |       |        |        |        |                      |                                 |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Master Transmission.

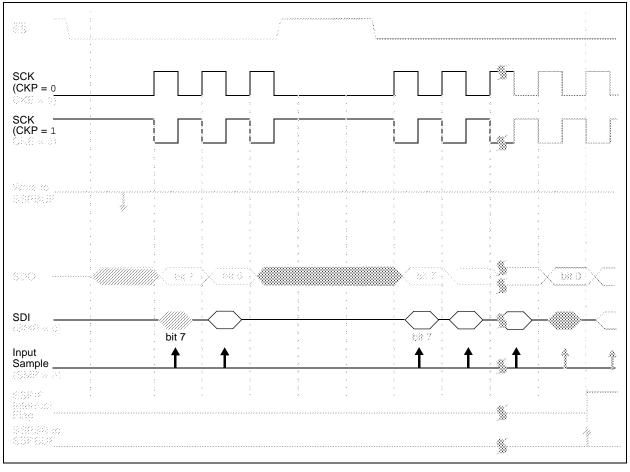

| FIGURE 12-12:                                   | SYNCHRONOUS RECEPTION (MASTER MODE, SREN)                                 |

|-------------------------------------------------|---------------------------------------------------------------------------|

| RX/DT<br>pin<br>TX/CK pin<br>(SCKP = 0)         |                                                                           |

| TX/CK pin<br>(SCKP = 1)<br>Write to<br>bit SREN |                                                                           |

| SREN bit                                        | ʻ0'                                                                       |

| RCIF bit<br>(Interrupt) ———<br>Read             |                                                                           |

| RXREG                                           | diagram demonstrates Sync Master mode with bit SREN = 1 and bit BRGH = 0. |

### TABLE 12-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

| Name    | Bit 7                         | Bit 6      | Bit 5       | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-------------------------------|------------|-------------|--------|-------|--------|--------|--------|----------------------|---------------------------------|

| BAUDCTL | ABDOVF                        | RCIDL      |             | SCKP   | BRG16 | —      | WUE    | ABDEN  | 01-0 0-00            | 01-0 0-00                       |

| INTCON  | GIE                           | PEIE       | TOIE        | INTE   | RABIE | T0IF   | INTF   | RABIF  | x000 000x            | 0000 000x                       |

| PIE1    | _                             | ADIE       | RCIE        | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | -000 0000            | -000 0000                       |

| PIR1    | _                             | ADIF       | RCIF        | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | -000 0000            | -000 0000                       |

| RCREG   | EUSART F                      | Receive Da | ta Register |        |       |        |        |        | 0000 0000            | 0000 0000                       |

| RCSTA   | SPEN                          | RX9        | SREN        | CREN   | ADDEN | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| SPBRG   | BRG7                          | BRG6       | BRG5        | BRG4   | BRG3  | BRG2   | BRG1   | BRG0   | 0000 0000            | 0000 0000                       |

| SPBRGH  | BRG15                         | BRG14      | BRG13       | BRG12  | BRG11 | BRG10  | BRG9   | BRG8   | 0000 0000            | 0000 0000                       |

| TRISB   | TRISB7                        | TRISB6     | TRISB5      | TRISB4 |       |        |        |        | 1111                 | 1111                            |

| TXREG   | EUSART Transmit Data Register |            |             |        |       |        |        |        | 0000 0000            | 0000 0000                       |

| TXSTA   | CSRC                          | TX9        | TXEN        | SYNC   | SENDB | BRGH   | TRMT   | TX9D   | 0000 0010            | 0000 0010                       |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Master Reception.

### 12.4.2 SYNCHRONOUS SLAVE MODE

The following bits are used to configure the EUSART for Synchronous slave operation:

- SYNC = 1

- CSRC = 0

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Clearing the CSRC bit of the TXSTA register configures the device as a slave. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the EUSART. If the RX/DT or TX/CK pins are shared with an analog peripheral the analog I/O functions must be disabled by clearing the corresponding ANSEL bits.

### 12.4.2.1 EUSART Synchronous Slave Transmit

The operation of the Synchronous Master and Slave modes are identical (see **Section 12.4.1.3 "Synchronous Master Transmission")**, except in the case of the Sleep mode. If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- 1. The first character will immediately transfer to the TSR register and transmit.

- 2. The second word will remain in TXREG register.

- 3. The TXIF bit will not be set.

- 4. After the first character has been shifted out of TSR, the TXREG register will transfer the second character to the TSR and the TXIF bit will now be set.

- 5. If the PEIE and TXIE bits are set, the interrupt will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will call the Interrupt Service Routine.

- 12.4.2.2 Synchronous Slave Transmission Set-up:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the CREN and SREN bits.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. If 9-bit transmission is desired, set the TX9 bit.

- 5. Enable transmission by setting the TXEN bit.

- 6. If 9-bit transmission is selected, insert the Most Significant bit into the TX9D bit.

- 7. Start transmission by writing the Least Significant eight bits to the TXREG register.

| Name    | Bit 7                         | Bit 6      | Bit 5       | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-------------------------------|------------|-------------|--------|-------|--------|--------|--------|----------------------|---------------------------------|

| BAUDCTL | ABDOVF                        | RCIDL      | —           | SCKP   | BRG16 | —      | WUE    | ABDEN  | 01-0 0-00            | 01-0 0-00                       |

| INTCON  | GIE                           | PEIE       | TOIE        | INTE   | RABIE | T0IF   | INTF   | RABIF  | x000 000x            | 0000 000x                       |

| PIE1    | —                             | ADIE       | RCIE        | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | -000 0000            | -000 0000                       |

| PIR1    | —                             | ADIF       | RCIF        | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | -000 0000            | -000 0000                       |

| RCREG   | EUSART F                      | Receive Da | ta Register |        |       |        |        |        | 0000 0000            | 0000 0000                       |

| RCSTA   | SPEN                          | RX9        | SREN        | CREN   | ADDEN | FERR   | OERR   | RX9D   | x000 000x            | 0000 000x                       |

| SPBRG   | BRG7                          | BRG6       | BRG5        | BRG4   | BRG3  | BRG2   | BRG1   | BRG0   | 0000 0000            | 0000 0000                       |

| SPBRGH  | BRG15                         | BRG14      | BRG13       | BRG12  | BRG11 | BRG10  | BRG9   | BRG8   | 0000 0000            | 0000 0000                       |

| TRISB   | TRISB7                        | TRISB6     | TRISB5      | TRISB4 |       |        |        |        | 1111                 | 1111                            |

| TXREG   | EUSART Transmit Data Register |            |             |        |       |        |        |        | 0000 0000            | 0000 0000                       |

| TXSTA   | CSRC                          | TX9        | TXEN        | SYNC   | SENDB | BRGH   | TRMT   | TX9D   | 0000 0010            | 0000 0010                       |

|         |                               |            |             |        |       |        |        |        |                      |                                 |

### TABLE 12-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Slave Transmission.

### 12.4.2.3 EUSART Synchronous Slave Reception

The operation of the Synchronous Master and Slave modes is identical (Section 12.4.1.5 "Synchronous Master Reception"), with the following exceptions:

- Sleep

- CREN bit is always set, therefore the receiver is never Idle

- SREN bit, which is a "don't care" in Slave mode

A character may be received while in Sleep mode by setting the CREN bit prior to entering Sleep. Once the word is received, the RSR register will transfer the data to the RCREG register. If the RCIE enable bit is set, the interrupt generated will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will branch to the interrupt vector.

- 12.4.2.4 Synchronous Slave Reception Setup:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 3. If 9-bit reception is desired, set the RX9 bit.

- 4. Set the CREN bit to enable reception.

- The RCIF bit will be set when reception is complete. An interrupt will be generated if the RCIE bit was set.

- 6. If 9-bit mode is enabled, retrieve the Most Significant bit from the RX9D bit of the RCSTA register.

- 7. Retrieve the eight Least Significant bits from the receive FIFO by reading the RCREG register.

- 8. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

| Name    | Bit 7                         | Bit 6      | Bit 5       | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-------------------------------|------------|-------------|--------|-------|--------|--------|--------|----------------------|---------------------------------|

| BAUDCTL | ABDOVF                        | RCIDL      | —           | SCKP   | BRG16 | —      | WUE    | ABDEN  | 01-0 0-00            | 01-0 0-00                       |

| INTCON  | GIE                           | PEIE       | TOIE        | INTE   | RABIE | T0IF   | INTF   | RABIF  | x000 000x            | 0000 000x                       |

| PIE1    | —                             | ADIE       | RCIE        | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | -000 0000            | -000 0000                       |

| PIR1    | —                             | ADIF       | RCIF        | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | -000 0000            | -000 0000                       |

| RCREG   | EUSART F                      | Receive Da | ta Register |        |       |        |        |        | 0000 0000            | 0000 0000                       |

| RCSTA   | SPEN                          | RX9        | SREN        | CREN   | ADDEN | FERR   | OERR   | RX9D   | x000 000x            | 0000 000x                       |

| SPBRG   | BRG7                          | BRG6       | BRG5        | BRG4   | BRG3  | BRG2   | BRG1   | BRG0   | 0000 0000            | 0000 0000                       |

| SPBRGH  | BRG15                         | BRG14      | BRG13       | BRG12  | BRG11 | BRG10  | BRG9   | BRG8   | 0000 0000            | 0000 0000                       |

| TRISB   | TRISB7                        | TRISB6     | TRISB5      | TRISB4 |       |        |        |        | 1111                 | 1111                            |

| TXREG   | EUSART Transmit Data Register |            |             |        |       |        |        |        | 0000 0000            | 0000 0000                       |

| TXSTA   | CSRC                          | TX9        | TXEN        | SYNC   | SENDB | BRGH   | TRMT   | TX9D   | 0000 0010            | 0000 0010                       |

### TABLE 12-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Slave Reception.

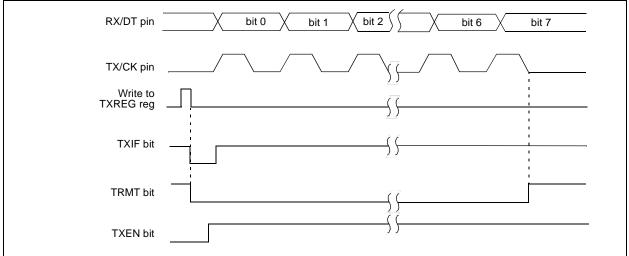

# 13.6 Slave Mode

In Slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched, the SSPIF interrupt flag bit is set.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. When a byte is received, the device will wake-up from Sleep.

# 13.7 Slave Select Synchronization

The  $\overline{SS}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with  $\overline{SS}$  pin control enabled (SSPCON<3:0> = 04h). The pin must not be driven low for the  $\overline{SS}$  pin to function as an input. The data latch must be high. When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven. When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven,

even if in the middle of a transmitted byte, and becomes a floating output. External pull-up/pull-down resistors may be desirable, depending on the application.

- Note 1: When the SPI is in Slave mode with  $\overline{SS}$ pin control enabled (SSPCON<3:0> = 0100), the SPI module will reset if the  $\overline{SS}$ pin is set to VDD.

- 2: If the SPI is used in Slave Mode with CKE set, then the SS pin control must be enabled.

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the  $\overline{SS}$  pin to a high level or clearing the SSPEN bit.

To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver, the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function) since it cannot create a bus conflict.

FIGURE 13-4: SLAVE SYNCHRONIZATION WAVEFORM

### 13.12.4 TRANSMISSION

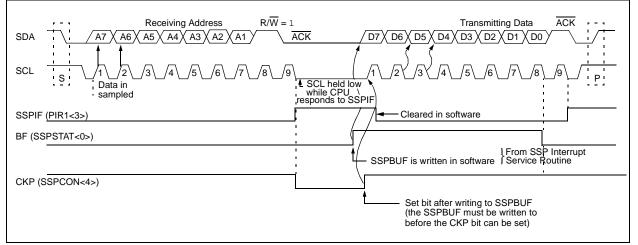

When the  $R/\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The  $\overline{ACK}$  pulse will be sent on the ninth bit, and pin RB6/SCK/SCL is held low. The transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then, pin RB6/SCK/SCL should be enabled by setting bit CKP (SSPCON<4>). The master must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 13-10). An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF must be cleared in software, and the SSPSTAT register is used to determine the status of the byte. Flag bit SSPIF is set on the falling edge of the ninth clock pulse.

As a slave-transmitter, the ACK pulse from the master receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line was high (not ACK), then the data transfer is complete. When the ACK is latched by the slave, the slave logic is reset (resets SSPSTAT register) and the slave then monitors for another occurrence of the Start bit. If the SDA line was low (ACK), the transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then pin RB6/SCK/SCL should be enabled by setting bit CKP.

### 13.13 Master Mode

Master mode of operation is supported in firmware using interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the SSP module is disabled. The Stop (P) and Start (S) bits will toggle based on the Start and Stop conditions. Control of the I<sup>2</sup>C bus may be taken when the P bit is set or the bus is idle and both the S and P bits are clear.

In Master mode, the SCL and SDA lines are manipulated by clearing the corresponding TRISB<6,4> bit(s). The output level is always low, irrespective of the value(s) in PORTB<6,4>. So when transmitting data, a '1' data bit must have the TRISB<4> bit set (input) and a '0' data bit must have the TRISB<4> bit cleared (output). The same scenario is true for the SCL line with the TRISB<6> bit. Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the I<sup>2</sup>C module.

The following events will cause the SSP Interrupt Flag bit, SSPIF, to be set (SSP Interrupt will occur if enabled):

- Start condition

- Stop condition

- Data transfer byte transmitted/received

Master mode of operation can be done with either the Slave mode idle (SSPM<3:0> = 1011), or with the Slave active. When both Master and Slave modes are enabled, the software needs to differentiate the source(s) of the interrupt.

### 13.14 Multi-Master Mode

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions, allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the SSP module is disabled. The Stop (P) and Start (S) bits will toggle based on the Start and Stop conditions. Control of the  $I^2C$  bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is idle and both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the Stop condition occurs.

In Multi-Master operation, the SDA line must be monitored to see if the signal level is the expected output level. This check only needs to be done when a high level is output. If a high level is expected and a low level is present, the device needs to release the SDA and SCL lines (set TRISB<6,4>). There are two stages where this arbitration can be lost, these are:

- Address Transfer

- Data Transfer

When the slave logic is enabled, the slave continues to receive. If arbitration was lost during the address transfer stage, communication to the device may be in progress. If addressed, an ACK pulse will be generated. If arbitration was lost during the data transfer stage, the device will need to re-transfer the data at a later time.

### 13.14.1 CLOCK SYNCHRONIZATION AND THE CKP BIT

When the CKP bit is cleared, the SCL output is forced to '0'; however, setting the CKP bit will not assert the SCL output low until the SCL output is already sampled low. Therefore, the CKP bit will not assert the SCL line until an external  $I^2C$  master device has already asserted the SCL line. The SCL output will remain low until the CKP bit is set and all other devices on the  $I^2C$  bus have deasserted SCL. This ensures that a write to the CKP bit will not violate the minimum high time requirement for SCL (see Figure 13-12).

### 14.2.4 BROWN-OUT RESET (BOR)

The BOREN0 and BOREN1 bits in the Configuration Word register select one of four BOR modes. Two modes have been added to allow software or hardware control of the BOR enable. When BOREN<1:0> = 01, the SBOREN bit (PCON<4>) enables/disables the BOR allowing it to be controlled in software. By selecting BOREN<1:0>, the BOR is automatically disabled in Sleep to conserve power and enabled on wake-up. In this mode, the SBOREN bit is disabled. See Register 14-2 for the Configuration Word definition.

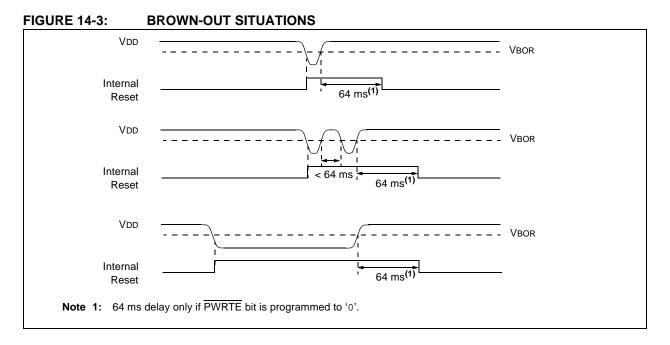

If VDD falls below VBOR for greater than parameter (TBOR) (see **Section 17.0 "Electrical Specifications"**), the Brown-out situation will reset the device. This will occur regardless of VDD slew rate. A Reset is not insured to occur if VDD falls below VBOR for less than parameter (TBOR).

On any Reset (Power-on, Brown-out Reset, Watchdog Timer, etc.), the chip will remain in Reset until VDD rises above VBOR (see Figure 14-3). The Power-up Timer will now be invoked, if enabled and will keep the chip in Reset an additional 64 ms.

Note: The Power-up Timer is enabled by the PWRTE bit in the Configuration Word register.

If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above VBOR, the Power-up Timer will execute a 64 ms Reset.

# 14.3 Interrupts

The PIC16F631/677/685/687/689/690 have multiple sources of interrupt:

- External Interrupt RA2/INT

- TMR0 Overflow Interrupt

- PORTA/PORTB Change Interrupts

- 2 Comparator Interrupts

- A/D Interrupt (except PIC16F631)

- Timer1 Overflow Interrupt

- Timer2 Match Interrupt (PIC16F685/PIC16F690 only)

- EEPROM Data Write Interrupt

- Fail-Safe Clock Monitor Interrupt

- Enhanced CCP Interrupt (PIC16F685/PIC16F690 only)

- EUSART Receive and Transmit interrupts (PIC16F687/PIC16F689/PIC16F690 only)

The Interrupt Control register (INTCON) and Peripheral Interrupt Request Register 1 (PIR1) record individual interrupt requests in flag bits. The INTCON register also has individual and global interrupt enable bits.

A Global Interrupt Enable bit, GIE (INTCON<7>), enables (if set) all unmasked interrupts, or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in the INTCON, PIE1 and PIE2 registers, respectively. GIE is cleared on Reset.

The Return from Interrupt instruction, RETFIE, exits the interrupt routine, as well as sets the GIE bit, which re-enables unmasked interrupts.

The following interrupt flags are contained in the INTCON register:

- INT Pin Interrupt

- PORTA/PORTB Change Interrupts

- TMR0 Overflow Interrupt

The peripheral interrupt flags are contained in the PIR1 and PIR2 registers. The corresponding interrupt enable bits are contained in PIE1 and PIE2 registers.

The following interrupt flags are contained in the PIR1 register:

- A/D Interrupt

- EUSART Receive and Transmit Interrupts

- Timer1 Overflow Interrupt

- Synchronous Serial Port (SSP) Interrupt

- Enhanced CCP1 Interrupt

- Timer1 Overflow Interrupt

- Timer2 Match Interrupt

The following interrupt flags are contained in the PIR2 register:

- Fail-Safe Clock Monitor Interrupt

- 2 Comparator Interrupts

- EEPROM Data Write Interrupt

When an interrupt is serviced:

- The GIE is cleared to disable any further interrupt.

- The return address is pushed onto the stack.

- The PC is loaded with 0004h.

For external interrupt events, such as the INT pin, PORTA/PORTB change interrupts, the interrupt latency will be three or four instruction cycles. The exact latency depends upon when the interrupt event occurs (see Figure 14-8). The latency is the same for one or 2-cycle instructions. Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests.

Note 1: Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit or the GIE bit.

2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The interrupts, which were ignored, are still pending to be serviced when the GIE bit is set again.

For additional information on Timer1, Timer2, comparators, A/D, data EEPROM, EUSART, SSP or Enhanced CCP modules, refer to the respective peripheral section.

### 14.3.1 RA2/INT INTERRUPT

External interrupt on RA2/INT pin is edge-triggered; either rising if the INTEDG bit (OPTION\_REG<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the RA2/INT pin, the INTF bit (INTCON<1>) is set. This interrupt can be disabled by clearing the INTE control bit (INTCON<4>). The INTF bit must be cleared in software in the Interrupt Service Routine before re-enabling this interrupt. The RA2/INT interrupt can wake-up the processor from Sleep, if the INTE bit was set prior to going into Sleep. The status of the GIE bit decides whether or not the processor branches to the interrupt vector following wake-up (0004h). See Section 14.6 "Power-Down Mode (Sleep)" for details on Sleep and Figure 14-10 for timing of wake-up from Sleep through RA2/INT interrupt.

Note: The ANSEL and CM2CON0 registers must be initialized to configure an analog channel as a digital input. Pins configured as analog inputs will read '0'.

| TABLE 17-14: | I <sup>2</sup> C <sup>™</sup> BUS DATA REQUIREMEN <sup>™</sup> | ΓS |

|--------------|----------------------------------------------------------------|----|

|--------------|----------------------------------------------------------------|----|

| Param.<br>No. | Symbol  | Characte                   | eristic      | Min.       | Max. | Units | Conditions                                  |

|---------------|---------|----------------------------|--------------|------------|------|-------|---------------------------------------------|

| 100* Тнібн    |         | Clock high time            | 100 kHz mode | 4.0        |      | μS    | Device must operate at a minimum of 1.5 MHz |

|               |         |                            | 400 kHz mode | 0.6        |      | μS    | Device must operate at a minimum of 10 MHz  |

|               |         |                            | SSP Module   | 1.5TCY     | _    |       |                                             |

| 101*          | TLOW    | Clock low time             | 100 kHz mode | 4.7        |      | μS    | Device must operate at a minimum of 1.5 MHz |

|               |         |                            | 400 kHz mode | 1.3        |      | μS    | Device must operate at a minimum of 10 MHz  |

|               |         |                            | SSP Module   | 1.5TCY     | _    |       |                                             |

| 102*          | TR      | SDA and SCL rise           | 100 kHz mode | —          | 1000 | ns    |                                             |

|               |         | time                       | 400 kHz mode | 20 + 0.1Св | 300  | ns    | CB is specified to be from 10-400 pF        |

| 103*          | TF      | SDA and SCL fall           | 100 kHz mode | —          | 300  | ns    |                                             |

|               |         | time                       | 400 kHz mode | 20 + 0.1Св | 300  | ns    | CB is specified to be from 10-400 pF        |

| 90*           | TSU:STA | Start condition setup time | 100 kHz mode | 4.7        |      | μS    | Only relevant for                           |

|               |         |                            | 400 kHz mode | 0.6        |      | μS    | Repeated Start condition                    |

| 91*           | THD:STA | Start condition hold       | 100 kHz mode | 4.0        | _    | μS    | After this period the first                 |

|               |         | time                       | 400 kHz mode | 0.6        |      | μS    | clock pulse is generated                    |

| 106*          | THD:DAT | Data input hold time       | 100 kHz mode | 0          | _    | ns    |                                             |

|               |         |                            | 400 kHz mode | 0          | 0.9  | μS    |                                             |