Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI                                                    |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                         |

| Number of I/O              | 18                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 128 x 8                                                                  |

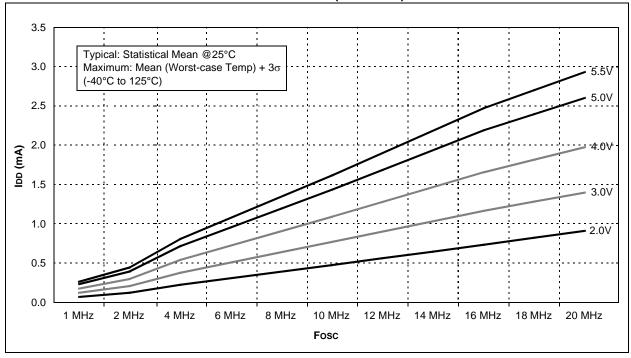

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 20-SSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f677-e-ss |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

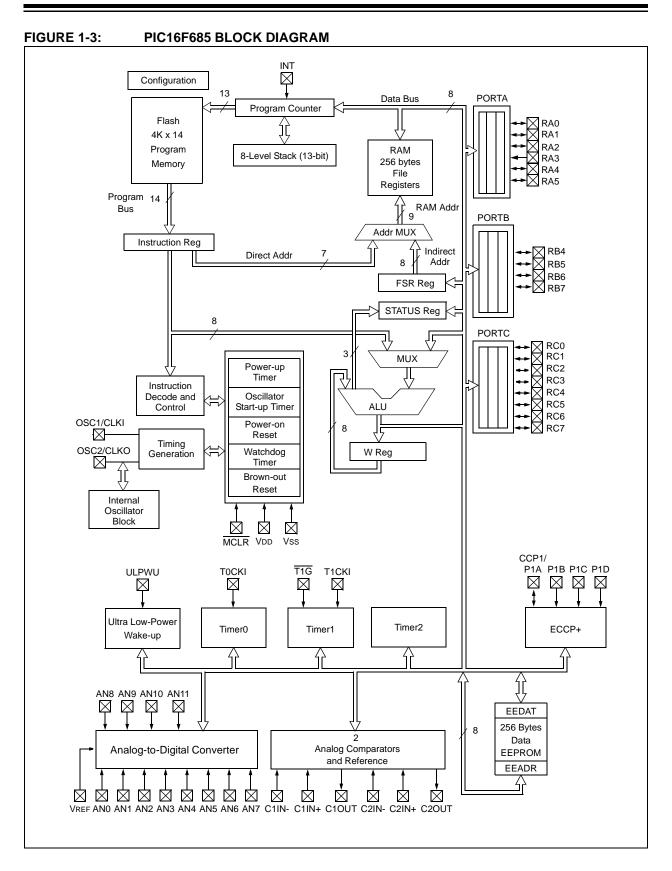

# PIC16F631/677/685/687/689/690

| Device    | Program<br>Memory | Data N          | lemory            | I/O | 10-bit A/D | Comparators | Timers   | SSP          | ECCP+ | EUSART |

|-----------|-------------------|-----------------|-------------------|-----|------------|-------------|----------|--------------|-------|--------|

| Device    | Flash<br>(words)  | SRAM<br>(bytes) | EEPROM<br>(bytes) | 1/0 | (ch)       | Comparators | 8/16-bit | 3 <b>5</b> F | ECCFŦ | EUSARI |

| PIC16F631 | 1024              | 64              | 128               | 18  | —          | 2           | 1/1      | No           | No    | No     |

| PIC16F677 | 2048              | 128             | 256               | 18  | 12         | 2           | 1/1      | Yes          | No    | No     |

| PIC16F685 | 4096              | 256             | 256               | 18  | 12         | 2           | 2/1      | No           | Yes   | No     |

| PIC16F687 | 2048              | 128             | 256               | 18  | 12         | 2           | 1/1      | Yes          | No    | Yes    |

| PIC16F689 | 4096              | 256             | 256               | 18  | 12         | 2           | 1/1      | Yes          | No    | Yes    |

| PIC16F690 | 4096              | 256             | 256               | 18  | 12         | 2           | 2/1      | Yes          | Yes   | Yes    |

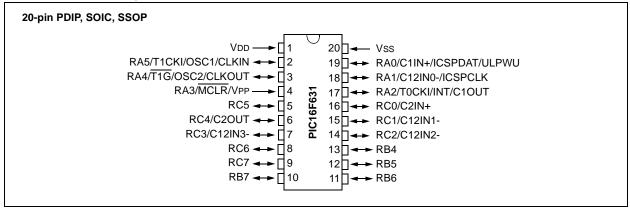

### PIC16F631 Pin Diagram

#### TABLE 1: PIC16F631 PIN SUMMARY

| I/O | Pin | Analog    | Comparators | Timers | Interrupt | Pull-up | Basic       |

|-----|-----|-----------|-------------|--------|-----------|---------|-------------|

| RA0 | 19  | AN0/ULPWU | C1IN+       | —      | IOC       | Y       | ICSPDAT     |

| RA1 | 18  | AN1       | C12IN0-     |        | IOC       | Y       | ICSPCLK     |

| RA2 | 17  | _         | C1OUT       | T0CKI  | IOC/INT   | Y       | —           |

| RA3 | 4   | —         | —           | —      | IOC       | Y(1)    | MCLR/Vpp    |

| RA4 | 3   | —         | —           | T1G    | IOC       | Y       | OSC2/CLKOUT |

| RA5 | 2   |           | —           | T1CKI  | IOC       | Y       | OSC1/CLKIN  |

| RB4 | 13  |           | —           | —      | IOC       | Y       | —           |

| RB5 | 12  | —         | —           | —      | IOC       | Y       | —           |

| RB6 | 11  | —         | —           | —      | IOC       | Y       | —           |

| RB7 | 10  |           | —           | _      | IOC       | Y       | —           |

| RC0 | 16  | AN4       | C2IN+       | —      | _         | —       | —           |

| RC1 | 15  | AN5       | C12IN1-     | _      |           |         | —           |

| RC2 | 14  | AN6       | C12IN2-     | —      |           | _       | —           |

| RC3 | 7   | AN7       | C12IN3-     |        |           |         | —           |

| RC4 | 6   |           | C2OUT       | —      |           |         | —           |

| RC5 | 5   |           | —           |        |           |         | —           |

| RC6 | 8   | —         |             | —      | _         | —       | —           |

| RC7 | 9   |           |             |        |           | _       | —           |

| —   | 1   |           |             | _      |           | _       | Vdd         |

| —   | 20  | _         |             | _      |           | _       | Vss         |

**Note 1:** Pull-up enabled only with external MCLR configuration.

# PIC16F631/677/685/687/689/690

### TABLE 1-3: PINOUT DESCRIPTION – PIC16F685

| ULPWU                                                                                                                                                                                                          | RA0<br>AN0<br>C1IN+<br>CSPDAT<br>JLPWU<br>RA1<br>AN1<br>C12IN0-<br>VREF<br>CSPCLK | TTL<br>AN<br>AN<br>TTL<br>AN<br>TTL<br>AN<br>AN | CMOS<br>—<br>CMOS<br>—<br>CMOS | General purpose I/O. Individually controlled interrupt-on-<br>change. Individually enabled pull-up.<br>A/D Channel 0 input.<br>Comparator C1 positive input.<br>ICSP™ Data I/O.<br>Ultra Low-Power Wake-up input.<br>General purpose I/O. Individually controlled interrupt-on-<br>change. Individually enabled pull-up. |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C           IC:           UU           RA1/AN1/C12IN0-/VREF/ICSPCLK           C           C           RA2/AN2/T0CKI/INT/C1OUT           T           C           RA3/MCLR/VPP           RA4/AN3/T1G/OSC2/CLKOUT | C1IN+<br>CSPDAT<br>JLPWU<br>RA1<br>AN1<br>C12IN0-<br>VREF<br>CSPCLK               | AN<br>TTL<br>AN<br>TTL<br>AN                    | —<br>CMOS<br>—                 | Comparator C1 positive input.<br>ICSP™ Data I/O.<br>Ultra Low-Power Wake-up input.<br>General purpose I/O. Individually controlled interrupt-on-                                                                                                                                                                         |

| IC:         UI         RA1/AN1/C12IN0-/VREF/ICSPCLK         C         C:         RA2/AN2/T0CKI/INT/C1OUT         T         C         RA3/MCLR/VPP         RA4/AN3/T1G/OSC2/CLKOUT                              | AN1<br>AN1<br>C12INO-<br>VREF<br>CSPCLK                                           | TTL<br>AN<br>TTL<br>AN                          | CMOS                           | ICSP™ Data I/O.<br>Ultra Low-Power Wake-up input.<br>General purpose I/O. Individually controlled interrupt-on-                                                                                                                                                                                                          |

| RA1/AN1/C12IN0-/VREF/ICSPCLK                                                                                                                                                                                   | AN1<br>AN1<br>C12INO-<br>VREF<br>CSPCLK                                           | AN<br>TTL<br>AN                                 | _                              | Ultra Low-Power Wake-up input.<br>General purpose I/O. Individually controlled interrupt-on-                                                                                                                                                                                                                             |

| RA1/AN1/C12IN0-/VREF/ICSPCLK C C C RA2/AN2/T0CKI/INT/C1OUT C RA3/MCLR/VPP N RA4/AN3/T1G/OSC2/CLKOUT                                                                                                            | RA1<br>AN1<br>C12IN0-<br>VREF<br>CSPCLK                                           | TTL<br>AN                                       | <br>CMOS                       | General purpose I/O. Individually controlled interrupt-on-                                                                                                                                                                                                                                                               |

| RA2/AN2/T0CKI/INT/C1OUT                                                                                                                                                                                        | AN1<br>C12IN0-<br>VREF<br>CSPCLK                                                  | AN                                              | CMOS                           |                                                                                                                                                                                                                                                                                                                          |

| RA2/AN2/T0CKI/INT/C1OUT                                                                                                                                                                                        | C12IN0-<br>VREF<br>CSPCLK                                                         |                                                 |                                | change. marriadany enabled pan-ap.                                                                                                                                                                                                                                                                                       |

| RA2/AN2/T0CKI/INT/C1OUT                                                                                                                                                                                        | VREF<br>SPCLK                                                                     | AN                                              | —                              | A/D Channel 1 input.                                                                                                                                                                                                                                                                                                     |

| IC:         RA2/AN2/T0CKI/INT/C1OUT         I         T         C         RA3/MCLR/VPP         I         RA4/AN3/T1G/OSC2/CLKOUT                                                                               | SPCLK                                                                             |                                                 | _                              | Comparator C1 or C2 negative input.                                                                                                                                                                                                                                                                                      |

| RA2/AN2/T0CKI/INT/C1OUT                                                                                                                                                                                        |                                                                                   | AN                                              | _                              | External Voltage Reference for A/D.                                                                                                                                                                                                                                                                                      |

| RA3/MCLR/Vpp                                                                                                                                                                                                   |                                                                                   | ST                                              | _                              | ICSP™ clock.                                                                                                                                                                                                                                                                                                             |

| RA3/MCLR/Vpp                                                                                                                                                                                                   | RA2                                                                               | ST                                              | CMOS                           | General purpose I/O. Individually controlled interrupt-on-<br>change. Individually enabled pull-up.                                                                                                                                                                                                                      |

| RA3/MCLR/VPP                                                                                                                                                                                                   | AN2                                                                               | AN                                              | _                              | A/D Channel 2 input.                                                                                                                                                                                                                                                                                                     |

| RA3/MCLR/Vpp                                                                                                                                                                                                   | T0CKI                                                                             | ST                                              |                                | Timer0 clock input.                                                                                                                                                                                                                                                                                                      |

| RA3/MCLR/Vpp                                                                                                                                                                                                   | INT                                                                               | ST                                              | _                              | External interrupt pin.                                                                                                                                                                                                                                                                                                  |

| RA4/AN3/T1G/OSC2/CLKOUT                                                                                                                                                                                        | C1OUT                                                                             |                                                 | CMOS                           | Comparator C1 output.                                                                                                                                                                                                                                                                                                    |

| RA4/AN3/T1G/OSC2/CLKOUT                                                                                                                                                                                        | RA3                                                                               | TTL                                             | _                              | General purpose input. Individually controlled interrupt-on-<br>change.                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                | MCLR                                                                              | ST                                              | _                              | Master Clear with internal pull-up.                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                | Vpp                                                                               | ΗV                                              | _                              | Programming voltage.                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                | RA4                                                                               | TTL                                             | CMOS                           | General purpose I/O. Individually controlled interrupt-on-<br>change. Individually enabled pull-up.                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                | AN3                                                                               | AN                                              | _                              | A/D Channel 3 input.                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                | T1G                                                                               | ST                                              | _                              | Timer1 gate input.                                                                                                                                                                                                                                                                                                       |

| (                                                                                                                                                                                                              | OSC2                                                                              |                                                 | XTAL                           | Crystal/Resonator.                                                                                                                                                                                                                                                                                                       |

| CL                                                                                                                                                                                                             | LKOUT                                                                             | _                                               | CMOS                           | Fosc/4 output.                                                                                                                                                                                                                                                                                                           |

| RA5/T1CKI/OSC1/CLKIN                                                                                                                                                                                           | RA5                                                                               | TTL                                             | CMOS                           | General purpose I/O. Individually controlled interrupt-on-<br>change. Individually enabled pull-up.                                                                                                                                                                                                                      |

| Т                                                                                                                                                                                                              | T1CKI                                                                             | ST                                              | _                              | Timer1 clock input.                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                | OSC1                                                                              | XTAL                                            |                                | Crystal/Resonator.                                                                                                                                                                                                                                                                                                       |

| C                                                                                                                                                                                                              | CLKIN                                                                             | ST                                              |                                | External clock input/RC oscillator connection.                                                                                                                                                                                                                                                                           |

| RB4/AN10                                                                                                                                                                                                       | RB4                                                                               | TTL                                             | CMOS                           | General purpose I/O. Individually controlled interrupt-on-<br>change. Individually enabled pull-up.                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                | AN10                                                                              | AN                                              | —                              | A/D Channel 10 input.                                                                                                                                                                                                                                                                                                    |

| RB5/AN11                                                                                                                                                                                                       | RB5                                                                               | TTL                                             | CMOS                           | General purpose I/O. Individually controlled interrupt-on-<br>change. Individually enabled pull-up.                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                | AN11                                                                              | AN                                              |                                | A/D Channel 11 input.                                                                                                                                                                                                                                                                                                    |

| RB6                                                                                                                                                                                                            | RB6                                                                               | TTL                                             | CMOS                           | General purpose I/O. Individually controlled interrupt-on-<br>change. Individually enabled pull-up.                                                                                                                                                                                                                      |

| RB7                                                                                                                                                                                                            | RB7                                                                               | TTL                                             | CMOS                           | General purpose I/O. Individually controlled interrupt-on-<br>change. Individually enabled pull-up.                                                                                                                                                                                                                      |

| RC0/AN4/C2IN+                                                                                                                                                                                                  | RC0                                                                               | ST                                              | CMOS                           | General purpose I/O.                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                | AN4                                                                               | AN                                              | _                              | A/D Channel 4 input.                                                                                                                                                                                                                                                                                                     |

| C                                                                                                                                                                                                              | C2IN+                                                                             | AN                                              | _                              | Comparator C2 positive input.                                                                                                                                                                                                                                                                                            |

| Legend: AN = Analog input or ou                                                                                                                                                                                | utput                                                                             | CMOS=                                           | CMOS co                        | mpatible input or output                                                                                                                                                                                                                                                                                                 |

#### 2.2.2.3 INTCON Register

The INTCON register, shown in Register 2-3, is a readable and writable register, which contains the various enable and flag bits for TMR0 register overflow, PORTA change and external RA2/AN2/T0CKI/INT/C1OUT pin interrupts.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### REGISTER 2-3: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0                  | R/W-0               | R/W-0 | R/W-x |

|-------|-------|-------|-------|------------------------|---------------------|-------|-------|

| GIE   | PEIE  | TOIE  | INTE  | RABIE <sup>(1,3)</sup> | T0IF <sup>(2)</sup> | INTF  | RABIF |

| bit 7 |       |       |       |                        |                     |       | bit 0 |

| Legend:                                                              |                  |                      |                    |

|----------------------------------------------------------------------|------------------|----------------------|--------------------|

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |                      |                    |

| -n = Value at POR                                                    | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| bit 7   | GIE: Global Interrupt Enable bit                                                                                                                                                                                                                                               |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul><li>1 = Enables all unmasked interrupts</li><li>0 = Disables all interrupts</li></ul>                                                                                                                                                                                      |

| bit 6   | <b>PEIE:</b> Peripheral Interrupt Enable bit<br>1 = Enables all unmasked peripheral interrupts<br>0 = Disables all peripheral interrupts                                                                                                                                       |

| bit 5   | <b>T0IE:</b> Timer0 Overflow Interrupt Enable bit<br>1 = Enables the Timer0 interrupt<br>0 = Disables the Timer0 interrupt                                                                                                                                                     |

| bit 4   | INTE: RA2/INT External Interrupt Enable bit<br>1 = Enables the RA2/INT external interrupt<br>0 = Disables the RA2/INT external interrupt                                                                                                                                       |

| bit 3   | <b>RABIE:</b> PORTA/PORTB Change Interrupt Enable bit <sup>(1,3)</sup><br>1 = Enables the PORTA/PORTB change interrupt<br>0 = Disables the PORTA/PORTB change interrupt                                                                                                        |

| bit 2   | <b>T0IF:</b> Timer0 Overflow Interrupt Flag bit <sup>(2)</sup><br>1 = TMR0 register has overflowed (must be cleared in software)<br>0 = TMR0 register did not overflow                                                                                                         |

| bit 1   | INTF: RA2/INT External Interrupt Flag bit<br>1 = The RA2/INT external interrupt occurred (must be cleared in software)<br>0 = The RA2/INT external interrupt did not occur                                                                                                     |

| bit 0   | <ul> <li>RABIF: PORTA/PORTB Change Interrupt Flag bit</li> <li>1 = When at least one of the PORTA or PORTB general purpose I/O pins changed state (must be cleared in software)</li> <li>0 = None of the PORTA or PORTB general purpose I/O pins have changed state</li> </ul> |

| Note 1: | IOCA or IOCB register must also be enabled.                                                                                                                                                                                                                                    |

- 2: T0IF bit is set when Timer0 rolls over. Timer0 is unchanged on Reset and should be initialized before clearing T0IF bit.

- **3:** Includes ULPWU interrupt.

#### 2.2.2.7 PIR2 Register

The PIR2 register contains the interrupt flag bits, as shown in Register 2-7.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 2-7: PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 2

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | U-0 | U-0 | U-0 | U-0 |

|-------------|-------|-------|-------|-----|-----|-----|-----|

| OSFIF       | C2IF  | C1IF  | EEIF  | —   | —   |     | —   |

| bit 7 bit 0 |       |       |       |     |     |     |     |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | OSFIF: Oscillator Fail Interrupt Flag bit                                                                                                                  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = System oscillator failed, clock input has changed to INTOSC (must be cleared in software)</li> <li>0 = System clock operating</li> </ul>      |

| bit 6   | C2IF: Comparator C2 Interrupt Flag bit                                                                                                                     |

|         | <ul> <li>1 = Comparator output (C2OUT bit) has changed (must be cleared in software)</li> <li>0 = Comparator output (C2OUT bit) has not changed</li> </ul> |

| bit 5   | C1IF: Comparator C1 Interrupt Flag bit                                                                                                                     |

|         | <ul> <li>1 = Comparator output (C1OUT bit) has changed (must be cleared in software)</li> <li>0 = Comparator output (C1OUT bit) has not changed</li> </ul> |

| bit 4   | EEIF: EE Write Operation Interrupt Flag bit                                                                                                                |

|         | <ul> <li>1 = Write operation completed (must be cleared in software)</li> <li>0 = Write operation has not completed or has not started</li> </ul>          |

| bit 3-0 | Unimplemented: Read as '0'                                                                                                                                 |

## 3.2 Oscillator Control

The Oscillator Control (OSCCON) register (Figure 3-1) controls the system clock and frequency selection options. The OSCCON register contains the following bits:

- Frequency selection bits (IRCF)

- Frequency Status bits (HTS, LTS)

- System clock control bits (OSTS, SCS)

#### REGISTER 3-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0     | R/W-1 | R/W-1 | R/W-0 | R-1                 | R-0 | R-0 | R/W-0 |

|---------|-------|-------|-------|---------------------|-----|-----|-------|

| —       | IRCF2 | IRCF1 | IRCF0 | OSTS <sup>(1)</sup> | HTS | LTS | SCS   |

| bit 7   |       |       |       |                     |     |     | bit 0 |

|         |       |       |       |                     |     |     |       |

| Legend: |       |       |       |                     |     |     |       |

| Logona.           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 7   | Unimplemented: Read as '0'                                                                                                                                                                                                           |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-4 | IRCF<2:0>: Internal Oscillator Frequency Select bits<br>111 = 8 MHz<br>110 = 4 MHz (default)<br>101 = 2 MHz<br>100 = 1 MHz<br>011 = 500 kHz<br>010 = 250 kHz<br>001 = 125 kHz<br>000 = 31 kHz (LFINTOSC)                             |

| bit 3   | <b>OSTS:</b> Oscillator Start-up Time-out Status bit <sup>(1)</sup><br>1 = Device is running from the clock defined by FOSC<2:0> of the CONFIG register<br>0 = Device is running from the internal oscillator (HFINTOSC or LFINTOSC) |

| bit 2   | <ul> <li>HTS: HFINTOSC Status bit (High Frequency – 8 MHz to 125 kHz)</li> <li>1 = HFINTOSC is stable</li> <li>0 = HFINTOSC is not stable</li> </ul>                                                                                 |

| bit 1   | LTS: LFINTOSC Stable bit (Low Frequency – 31 kHz)<br>1 = LFINTOSC is stable<br>0 = LFINTOSC is not stable                                                                                                                            |

| bit 0   | <ul> <li>SCS: System Clock Select bit</li> <li>1 = Internal oscillator is used for system clock</li> <li>0 = Clock source defined by FOSC&lt;2:0&gt; of the CONFIG register</li> </ul>                                               |

| Note 1. | Discrete to (o) with Two Greed Oters up and LD VT or LIC collected on the Opeillater mode on Feil                                                                                                                                    |

**Note 1:** Bit resets to '0' with Two-Speed Start-up and LP, XT or HS selected as the Oscillator mode or Fail-Safe mode is enabled.

## 3.6 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the System Clock Select (SCS) bit of the OSCCON register.

## 3.6.1 SYSTEM CLOCK SELECT (SCS) BIT

The System Clock Select (SCS) bit of the OSCCON register selects the system clock source that is used for the CPU and peripherals.

- When the SCS bit of the OSCCON register = 0, the system clock source is determined by configuration of the FOSC<2:0> bits in the Configuration Word register (CONFIG).

- When the SCS bit of the OSCCON register = 1, the system clock source is chosen by the internal oscillator frequency selected by the IRCF<2:0> bits of the OSCCON register. After a Reset, the SCS bit of the OSCCON register is always cleared.

- Note: Any automatic clock switch, which may occur from Two-Speed Start-up or Fail-Safe Clock Monitor, does not update the SCS bit of the OSCCON register. The user can monitor the OSTS bit of the OSCCON register to determine the current system clock source.

# 3.6.2 OSCILLATOR START-UP TIME-OUT STATUS (OSTS) BIT

The Oscillator Start-up Time-out Status (OSTS) bit of the OSCCON register indicates whether the system clock is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Word register (CONFIG), or from the internal clock source. In particular, OSTS indicates that the Oscillator Start-up Timer (OST) has timed out for LP, XT or HS modes.

## 3.7 Two-Speed Clock Start-up Mode

Two-Speed Start-up mode provides additional power savings by minimizing the latency between external oscillator start-up and code execution. In applications that make heavy use of the Sleep mode, Two-Speed Start-up will remove the external oscillator start-up time from the time spent awake and can reduce the overall power consumption of the device.

This mode allows the application to wake-up from Sleep, perform a few instructions using the INTOSC as the clock source and go back to Sleep without waiting for the primary oscillator to become stable.

Note: Executing a SLEEP instruction will abort the oscillator start-up time and will cause the OSTS bit of the OSCCON register to remain clear. When the Oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) is enabled (see **Section 3.4.1 "Oscillator Start-up Timer (OST)"**). The OST will suspend program execution until 1024 oscillations are counted. Two-Speed Start-up mode minimizes the delay in code execution by operating from the internal oscillator as the OST is counting. When the OST count reaches 1024 and the OSTS bit of the OSCCON register is set, program execution switches to the external oscillator.

# 3.7.1 TWO-SPEED START-UP MODE CONFIGURATION

Two-Speed Start-up mode is configured by the following settings:

- IESO (of the Configuration Word register) = 1; Internal/External Switchover bit (Two-Speed Startup mode enabled).

- SCS (of the OSCCON register) = 0.

- FOSC<2:0> bits in the Configuration Word register (CONFIG) configured for LP, XT or HS mode.

Two-Speed Start-up mode is entered after:

- Power-on Reset (POR) and, if enabled, after Power-up Timer (PWRT) has expired, or

- Wake-up from Sleep.

If the external clock oscillator is configured to be anything other than LP, XT or HS mode, then Twospeed Start-up is disabled. This is because the external clock oscillator does not require any stabilization time after POR or an exit from Sleep.

### 3.7.2 TWO-SPEED START-UP SEQUENCE

- 1. Wake-up from Power-on Reset or Sleep.

- Instructions begin execution by the internal oscillator at the frequency set in the IRCF<2:0> bits of the OSCCON register.

- 3. OST enabled to count 1024 clock cycles.

- 4. OST timed out, wait for falling edge of the internal oscillator.

- 5. OSTS is set.

- 6. System clock held low until the next falling edge of new clock (LP, XT or HS mode).

- 7. System clock is switched to external clock source.

## 3.8 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the device to continue operating should the external oscillator fail. The FSCM can detect oscillator failure any time after the Oscillator Start-up Timer (OST) has expired. The FSCM is enabled by setting the FCMEN bit in the Configuration Word register (CONFIG). The FSCM is applicable to all external Oscillator modes (LP, XT, HS, EC, RC and RCIO).

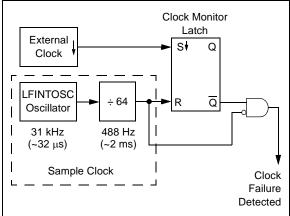

FIGURE 3-8: FSCM BLOCK DIAGRAM

## 3.8.1 FAIL-SAFE DETECTION

The FSCM module detects a failed oscillator by comparing the external oscillator to the FSCM sample clock. The sample clock is generated by dividing the LFINTOSC by 64. See Figure 3-8. Inside the fail detector block is a latch. The external clock sets the latch on each falling edge of the external clock. The sample clock clears the latch on each rising edge of the sample clock. A failure is detected when an entire half-cycle of the sample clock elapses before the primary clock goes low.

## 3.8.2 FAIL-SAFE OPERATION

When the external clock fails, the FSCM switches the device clock to an internal clock source and sets the bit flag OSFIF of the PIR2 register. Setting this flag will generate an interrupt if the OSFIE bit of the PIE2 register is also set. The device firmware can then take steps to mitigate the problems that may arise from a failed clock. The system clock will continue to be sourced from the internal clock source until the device firmware successfully restarts the external oscillator and switches back to external operation.

The internal clock source chosen by the FSCM is determined by the IRCF<2:0> bits of the OSCCON register. This allows the internal oscillator to be configured before a failure occurs.

## 3.8.3 FAIL-SAFE CONDITION CLEARING

The Fail-Safe condition is cleared after a Reset, executing a SLEEP instruction or toggling the SCS bit of the OSCCON register. When the SCS bit is toggled, the OST is restarted. While the OST is running, the device continues to operate from the INTOSC selected in OSCCON. When the OST times out, the Fail-Safe condition is cleared and the device will be operating from the external clock source. The Fail-Safe condition must be cleared before the OSFIF flag can be cleared.

### 3.8.4 RESET OR WAKE-UP FROM SLEEP

The FSCM is designed to detect an oscillator failure after the Oscillator Start-up Timer (OST) has expired. The OST is used after waking up from Sleep and after any type of Reset. The OST is not used with the EC or RC Clock modes so that the FSCM will be active as soon as the Reset or wake-up has completed. When the FSCM is enabled, the Two-Speed Start-up is also enabled. Therefore, the device will always be executing code while the OST is operating.

Note: Due to the wide range of oscillator start-up times, the Fail-Safe circuit is not active during oscillator start-up (i.e., after exiting Reset or Sleep). After an appropriate amount of time, the user should check the OSTS bit of the OSCCON register to verify the oscillator start-up and that the system clock switchover has successfully completed.

| TABLE 4-1: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTA |

|------------|--------------------------------------------|

|------------|--------------------------------------------|

| Name       | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------------|--------|--------|---------|---------|---------|--------|---------|--------|----------------------|---------------------------------|

| ADCON0     | ADFM   | VCFG   | CHS3    | CHS2    | CHS1    | CHS0   | GO/DONE | ADON   | 0000 0000            | 0000 0000                       |

| ANSEL      | ANS7   | ANS6   | ANS5    | ANS4    | ANS3    | ANS2   | ANS1    | ANS0   | 1111 1111            | 1111 1111                       |

| CM1CON0    | C1ON   | C1OUT  | C1OE    | C1POL   | _       | C1R    | C1CH1   | C1CH0  | 0000 -000            | 0000 -000                       |

| INTCON     | GIE    | PEIE   | T0IE    | INTE    | RABIE   | T0IF   | INTF    | RABIF  | 0000 000x            | 0000 000x                       |

| IOCA       | _      | _      | IOCA5   | IOCA4   | IOCA3   | IOCA2  | IOCA1   | IOCA0  | 00 0000              | 00 0000                         |

| OPTION_REG | RABPU  | INTEDG | TOCS    | T0SE    | PSA     | PS2    | PS1     | PS0    | 1111 1111            | 1111 1111                       |

| PORTA      | _      | _      | RA5     | RA4     | RA3     | RA2    | RA1     | RA0    | xx xxxx              | uu uuuu                         |

| SSPCON     | WCOL   | SSPOV  | SSPEN   | CKP     | SSPM3   | SSPM2  | SSPM1   | SSPM0  | 0000 0000            | 0000 0000                       |

| T1CON      | T1GINV | TMR1GE | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS  | TMR10N | 0000 0000            | uuuu uuuu                       |

| TRISA      |        | _      | TRISA5  | TRISA4  | TRISA3  | TRISA2 | TRISA1  | TRISA0 | 11 1111              | 11 1111                         |

| WPUA       | _      | —      | WPUA5   | WPUA4   | —       | WPUA2  | WPUA1   | WPUA0  | 11 -111              | 11 -111                         |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

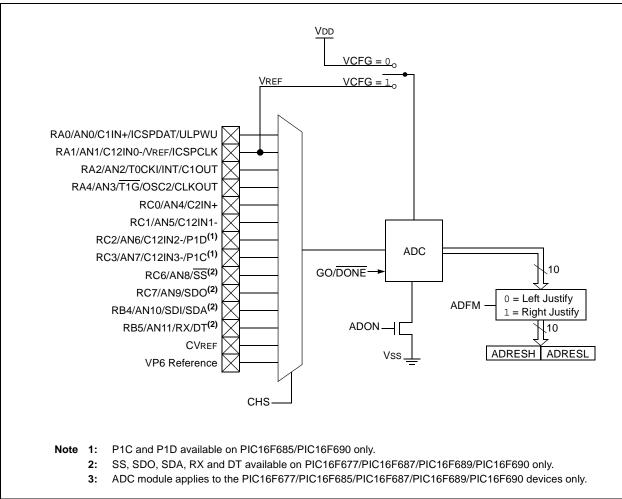

## 9.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 10-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 10-bit binary result via successive approximation and stores the conversion result into the ADC result registers (ADRESL and ADRESH).

Note: The ADC module applies to PIC16F677/ PIC16F685/PIC16F687/PIC16F689/ PIC16F690 devices only.

The ADC voltage reference is software selectable to be either internally generated or externally supplied.

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

## FIGURE 9-1: ADC BLOCK DIAGRAM

Figure 9-1 shows the block diagram of the ADC.

| Name   | Bit 7                           | Bit 6        | Bit 5   | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|---------------------------------|--------------|---------|--------|--------|--------|---------|--------|----------------------|---------------------------------|

| ADCON0 | ADFM                            | VCFG         | CHS3    | CHS2   | CHS1   | CHS0   | GO/DONE | ADON   | 0000 0000            | 0000 0000                       |

| ADCON1 | —                               | ADCS2        | ADCS1   | ADCS0  | _      | _      | _       | -      | -000                 | -000                            |

| ANSEL  | ANS7                            | ANS6         | ANS5    | ANS4   | ANS3   | ANS2   | ANS1    | ANS0   | 1111 1111            | 1111 1111                       |

| ANSELH | —                               | —            | —       | —      | ANS11  | ANS10  | ANS9    | ANS8   | 1111                 | 1111                            |

| ADRESH | H A/D Result Register High Byte |              |         |        |        |        |         |        |                      | uuuu uuuu                       |

| ADRESL | A/D Resul                       | t Register L | ow Byte |        |        |        |         |        | xxxx xxxx            | uuuu uuuu                       |

| INTCON | GIE                             | PEIE         | TOIE    | INTE   | RABIE  | T0IF   | INTF    | RABIF  | 0000 000x            | x000 000x                       |

| PIE1   | —                               | ADIE         | RCIE    | TXIE   | SSPIE  | CCP1IE | TMR2IE  | TMR1IE | -000 0000            | -000 0000                       |

| PIR1   | _                               | ADIF         | RCIF    | TXIF   | SSPIF  | CCP1IF | TMR2IF  | TMR1IF | -000 0000            | -000 0000                       |

| PORTA  | —                               | —            | RA5     | RA4    | RA3    | RA2    | RA1     | RA0    | xx xxxx              | uu uuuu                         |

| PORTB  | RB7                             | RB6          | RB5     | RB4    | _      | _      | _       | -      | xxxx                 | uuuu                            |

| PORTC  | RC7                             | RC6          | RC5     | RC4    | RC3    | RC2    | RC1     | RC0    | xxxx xxxx            | uuuu uuuu                       |

| TRISA  | —                               | _            | TRISA5  | TRISA4 | TRISA3 | TRISA2 | TRISA1  | TRISA0 | 11 1111              | 11 1111                         |

| TRISB  | TRISB7                          | TRISB6       | TRISB5  | TRISB4 | —      | —      | —       | —      | 1111                 | 1111                            |

| TRISC  | TRISC7                          | TRISC6       | TRISC5  | TRISC4 | TRISC3 | TRISC2 | TRISC1  | TRISC0 | 1111 1111            | 1111 1111                       |

### TABLE 9-2: SUMMARY OF ASSOCIATED ADC REGISTERS

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for ADC module.

|        |                   | SYNC = 0, BRGH = 0, BRG16 = 0 |                             |                |            |                             |                |            |                             |                |            |                             |  |  |  |  |

|--------|-------------------|-------------------------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|--|--|--|--|

| BAUD   | Fosc = 20.000 MHz |                               |                             | Fosc           | ; = 18.43  | 2 MHz                       | Fosc           | = 11.059   | 92 MHz                      | Fos            | c = 8.000  | ) MHz                       |  |  |  |  |

| RATE   | Actual<br>Rate    | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |  |

| 300    | _                 |                               | _                           |                | _          | _                           | _              | _          | _                           | _              | _          | _                           |  |  |  |  |

| 1200   | 1221              | 1.73                          | 255                         | 1200           | 0.00       | 239                         | 1200           | 0.00       | 143                         | 1202           | 0.16       | 103                         |  |  |  |  |

| 2400   | 2404              | 0.16                          | 129                         | 2400           | 0.00       | 119                         | 2400           | 0.00       | 71                          | 2404           | 0.16       | 51                          |  |  |  |  |

| 9600   | 9470              | -1.36                         | 32                          | 9600           | 0.00       | 29                          | 9600           | 0.00       | 17                          | 9615           | 0.16       | 12                          |  |  |  |  |

| 10417  | 10417             | 0.00                          | 29                          | 10286          | -1.26      | 27                          | 10165          | -2.42      | 16                          | 10417          | 0.00       | 11                          |  |  |  |  |

| 19.2k  | 19.53k            | 1.73                          | 15                          | 19.20k         | 0.00       | 14                          | 19.20k         | 0.00       | 8                           | _              | _          | _                           |  |  |  |  |

| 57.6k  | —                 | —                             | _                           | 57.60k         | 0.00       | 7                           | 57.60k         | 0.00       | 2                           | —              | —          | —                           |  |  |  |  |

| 115.2k | —                 |                               | _                           | —              | _          | _                           | _              |            | _                           | —              | _          | _                           |  |  |  |  |

#### TABLE 12-5: BAUD RATES FOR ASYNCHRONOUS MODES

|        | SYNC = 0, BRGH = 0, BRG16 = 0 |            |                             |                |            |                             |                |            |                             |                |            |                             |  |

|--------|-------------------------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|--|

| BAUD   | Fos                           | c = 4.000  | ) MHz                       | Fosc           | = 3.686    | 4 MHz                       | Fos            | c = 2.00   | 0 MHz                       | Fos            | c = 1.000  | ) MHz                       |  |

| RATE   | Actual<br>Rate                | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 300    | 300                           | 0.16       | 207                         | 300            | 0.00       | 191                         | 300            | 0.16       | 103                         | 300            | 0.16       | 51                          |  |

| 1200   | 1202                          | 0.16       | 51                          | 1200           | 0.00       | 47                          | 1202           | 0.16       | 25                          | 1202           | 0.16       | 12                          |  |

| 2400   | 2404                          | 0.16       | 25                          | 2400           | 0.00       | 23                          | 2404           | 0.16       | 12                          | —              | _          | —                           |  |

| 9600   | —                             | _          | _                           | 9600           | 0.00       | 5                           | _              | _          | _                           | —              | _          | —                           |  |

| 10417  | 10417                         | 0.00       | 5                           | —              | _          | _                           | 10417          | 0.00       | 2                           | _              | —          | _                           |  |

| 19.2k  | —                             | _          | _                           | 19.20k         | 0.00       | 2                           | _              | _          | _                           | —              | _          | —                           |  |

| 57.6k  | —                             | —          | —                           | 57.60k         | 0.00       | 0                           | —              | —          | —                           | —              | —          | —                           |  |

| 115.2k | —                             | —          | _                           | —              | _          | —                           | —              | —          | _                           | _              | —          | —                           |  |

|        | SYNC = 0, BRGH = 1, BRG16 = 0 |            |                             |                |            |                             |                |            |                             |                |            |                             |  |  |

|--------|-------------------------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|--|--|

| BAUD   | Fosc = 20.000 MHz             |            |                             | Fosc           | : = 18.43  | 2 MHz                       | Fosc           | = 11.059   | 92 MHz                      | Fos            | c = 8.000  | ) MHz                       |  |  |

| RATE   | Actual<br>Rate                | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |

| 300    | —                             |            | _                           | _              |            | _                           |                | —          | _                           |                | —          |                             |  |  |

| 1200   | —                             | —          | —                           | —              | _          | —                           | —              | —          | _                           | —              | —          | —                           |  |  |

| 2400   | _                             | _          | _                           | —              | _          | _                           | —              | _          | _                           | 2404           | 0.16       | 207                         |  |  |

| 9600   | 9615                          | 0.16       | 129                         | 9600           | 0.00       | 119                         | 9600           | 0.00       | 71                          | 9615           | 0.16       | 51                          |  |  |

| 10417  | 10417                         | 0.00       | 119                         | 10378          | -0.37      | 110                         | 10473          | 0.53       | 65                          | 10417          | 0.00       | 47                          |  |  |

| 19.2k  | 19.23k                        | 0.16       | 64                          | 19.20k         | 0.00       | 59                          | 19.20k         | 0.00       | 35                          | 19231          | 0.16       | 25                          |  |  |

| 57.6k  | 56.82k                        | -1.36      | 21                          | 57.60k         | 0.00       | 19                          | 57.60k         | 0.00       | 11                          | 55556          | -3.55      | 8                           |  |  |

| 115.2k | 113.64k                       | -1.36      | 10                          | 115.2k         | 0.00       | 9                           | 115.2k         | 0.00       | 5                           | —              | —          | _                           |  |  |

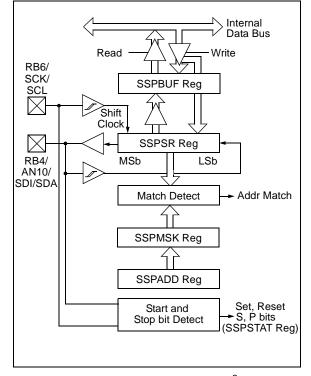

## 13.11 SSP I<sup>2</sup>C Operation

The SSP module in  $l^2$ C mode, fully implements all slave functions, except general call support, and provides interrupts on Start and Stop bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the Standard mode specifications, as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer. These are the RB6/ SCK/SCL pin, which is the clock (SCL), and the RB4/ AN10/SDI/SDA pin, which is the data (SDA).

The SSP module functions are enabled by setting SSP enable bit SSPEN (SSPCON<5>).

FIGURE 13-7: SSP BLOCK DIAGRAM (I<sup>2</sup>C™ MODE)

The SSP module has six registers for the  $I^2C$  operation, which are listed below.

- SSP Control register (SSPCON)

- SSP Status register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift register (SSPSR) Not directly accessible

- SSP Address register (SSPADD)

- SSP Mask register (SSPMSK)

The SSPCON register allows control of the  $l^2C$  operation. Four mode selection bits (SSPCON<3:0>) allow one of the following  $l^2C$  modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address), with Start and Stop bit interrupts enabled to support Firmware Master mode

- I<sup>2</sup>C Slave mode (10-bit address), with Start and Stop bit interrupts enabled to support Firmware Master mode

- I<sup>2</sup>C Start and Stop bit interrupts enabled to support Firmware Master mode; Slave is idle

Selection of any  $I^2C$  mode with the SSPEN bit set forces the SCL and SDA pins to be open drain, provided these pins are programmed to inputs by setting the appropriate TRISB bits. Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the  $I^2C$  module.

## 13.12 Slave Mode

In Slave mode, the SCL and SDA pins must be configured as inputs (TRISB<6,4> are set). The SSP module will override the input state with the output data when required (slave-transmitter).

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge  $(\overline{ACK})$ pulse, and then load the SSPBUF register with the received value currently in the SSPSR register.

There are certain conditions that will cause the SSP module not to give this ACK pulse. They include (either or both):

- a) The Buffer Full bit BF of the SSPSTAT register was set before the transfer was received.

- b) The overflow bit SSPOV of the SSPCON register was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF of the PIR1 register is set. Table 13-3 shows the results of when a data transfer byte is received, given the status of bits BF and SSPOV. The shaded cells show the condition where user software did not properly clear the overflow condition. Flag bit BF is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low for proper operation. For high and low times of the  $I^2C$  specification, as well as the requirements of the SSP module, see **Section 17.0 "Electrical Specifications"**.

## 14.0 SPECIAL FEATURES OF THE CPU

The PIC16F631/677/685/687/689/690 have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving features and offer code protection.

These features are:

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- Oscillator selection

- Sleep

- Code protection

- ID Locations

- In-Circuit Serial Programming

The PIC16F631/677/685/687/689/690 have two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 64 ms (nominal) on power-up only, designed to keep the part in Reset while the power supply stabilizes. There is also circuitry to reset the device if a brown-out occurs, which can use the Power-up Timer to provide at least a 64 ms Reset. With these three functions-on-chip, most applications need no external Reset circuitry.

The Sleep mode is designed to offer a very low-current Power-down mode. The user can wake-up from Sleep through:

- External Reset

- Watchdog Timer Wake-up

- An interrupt

Several oscillator options are also made available to allow the part to fit the application. The INTOSC option saves system cost while the LP crystal option saves power. A set of Configuration bits are used to select various options (see Register 14-2).

## 14.1 Configuration Bits

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1') to select various device configurations as shown in Register 14-2. These bits are mapped in program memory location 2007h.

Note: Address 2007h is beyond the user program memory space. It belongs to the special configuration memory space (2000h-3FFFh), which can be accessed only during programming. See "PIC12F6XX/16F6XX Memory Programming Specification" (DS41204) for more information.

## 14.6 Power-Down Mode (Sleep)

The Power-Down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If the Watchdog Timer is enabled:

- WDT will be cleared but keeps running.

- PD bit in the STATUS register is cleared.

- TO bit is set.

- Oscillator driver is turned off.

- I/O ports maintain the status they had before SLEEP was executed (driving high, low or highimpedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD or Vss, with no external circuitry drawing current from the I/O pin and the comparators and CVREF should be disabled. I/O pins that are highimpedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or Vss for lowest current consumption. The contribution from on-chip pullups on PORTA should be considered.

The  $\overline{\text{MCLR}}$  pin must be at a logic high level.

Note: It should be noted that a Reset generated by a WDT time-out does not drive MCLR pin low.

### 14.6.1 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on  $\overline{\text{MCLR}}$  pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. Interrupt from RA2/INT pin, PORTA change or a peripheral interrupt.

The first event will cause a device Reset. The two latter events are considered a continuation of program execution. The TO and PD bits in the STATUS register can be used to determine the cause of device Reset. The PD bit, which is set on power-up, is cleared when Sleep is invoked. TO bit is cleared if WDT Wake-up occurred.

The following peripheral interrupts can wake the device from Sleep:

- 1. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 2. ECCP Capture mode interrupt.

- 3. A/D conversion (when A/D clock source is FRC).

- 4. EEPROM write operation completion.

- 5. Comparator output changes state.

- 6. Interrupt-on-change.

- 7. External Interrupt from INT pin.

- 8. EUSART Break detect, I<sup>2</sup>C slave.

Other peripherals cannot generate interrupts since during Sleep, no on-chip clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up occurs regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction, then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

| Note: | If the global interrupts are disabled (GIE is |  |  |  |  |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | cleared), but any interrupt source has both   |  |  |  |  |  |  |  |  |  |

|       | its interrupt enable bit and the              |  |  |  |  |  |  |  |  |  |

|       | corresponding interrupt flag bits set, the    |  |  |  |  |  |  |  |  |  |

|       | device will immediately wake-up from          |  |  |  |  |  |  |  |  |  |

|       | Sleep. The SLEEP instruction is completely    |  |  |  |  |  |  |  |  |  |

|       | executed.                                     |  |  |  |  |  |  |  |  |  |

The WDT is cleared when the device wakes up from Sleep, regardless of the source of wake-up.

#### 14.6.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs before the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT prescaler and postscaler (if enabled) will not be cleared, the TO bit will not be set and the PD bit will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake-up from Sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT prescaler and postscaler (if enabled) will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.