Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI                                                    |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                         |

| Number of I/O              | 18                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 20-VFQFN Exposed Pad                                                     |

| Supplier Device Package    | 20-QFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f677-i-ml |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

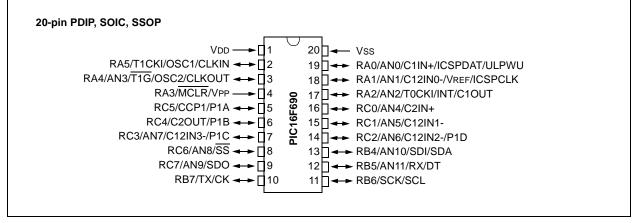

# PIC16F677 Pin Diagram

| 20-pin PDIP, SOIC, SSOP |                             |

|-------------------------|-----------------------------|

| VDD                     | 15 <b>→</b> RC1/AN5/C12IN1- |

#### TABLE 2: PIC16F631 PIN SUMMARY

| I/O | Pin | Analog    | Comparators | Timers | Interrupt | Pull-up | Basic       |  |  |

|-----|-----|-----------|-------------|--------|-----------|---------|-------------|--|--|

| RA0 | 19  | AN0/ULPWU | C1IN+       | —      | IOC       | Y       | ICSPDAT     |  |  |

| RA1 | 18  | AN1       | C12IN0-     |        | IOC       | Y       | ICSPCLK     |  |  |

| RA2 | 17  | —         | C1OUT       | T0CKI  | IOC/INT   | Y       | —           |  |  |

| RA3 | 4   | —         | —           | —      | IOC       | Y(1)    | MCLR/VPP    |  |  |

| RA4 | 3   | —         | —           | T1G    | IOC       | Y       | OSC2/CLKOUT |  |  |

| RA5 | 2   | —         | —           | T1CKI  | IOC       | Y       | OSC1/CLKIN  |  |  |

| RB4 | 13  |           | —           | —      | IOC       | Y       | —           |  |  |

| RB5 | 12  | _         | —           | —      | IOC       | Y       | —           |  |  |

| RB6 | 11  |           | —           | —      | IOC       | Y       | —           |  |  |

| RB7 | 10  |           | —           |        | IOC       | Y       | —           |  |  |

| RC0 | 16  | AN4       | C2IN+       | —      |           |         | —           |  |  |

| RC1 | 15  | AN5       | C12IN1-     |        |           |         | —           |  |  |

| RC2 | 14  | AN6       | C12IN2-     |        |           |         | —           |  |  |

| RC3 | 7   | AN7       | C12IN3-     |        |           |         | —           |  |  |

| RC4 | 6   | _         | C2OUT       | _      | _         | _       | —           |  |  |

| RC5 | 5   |           | —           |        |           |         | —           |  |  |

| RC6 | 8   |           | _           | _      |           | _       | _           |  |  |

| RC7 | 9   | _         |             |        |           | —       | —           |  |  |

|     | 1   |           |             |        |           | -       | Vdd         |  |  |

| _   | 20  |           |             | _      | _         | _       | Vss         |  |  |

**Note 1:** Pull-up enabled only with external MCLR configuration.

# PIC16F690 Pin Diagram (PDIP, SOIC, SSOP)

| TABL   | E 5:   | PIC16F            | 690 PIN SUM        | MARY    |              |        |         |           |         |             |

|--------|--------|-------------------|--------------------|---------|--------------|--------|---------|-----------|---------|-------------|

| I/O    | Pin    | Analog            | Comparators        | Timers  | ECCP         | EUSART | SSP     | Interrupt | Pull-up | Basic       |

| RA0    | 19     | AN0/ULPWU         | C1IN+              | —       | —            | _      | —       | IOC       | Y       | ICSPDAT     |

| RA1    | 18     | AN1/VREF          | C12IN0-            | —       | _            | _      | —       | IOC       | Y       | ICSPCLK     |

| RA2    | 17     | AN2               | C1OUT              | T0CKI   | _            | _      | —       | IOC/INT   | Y       |             |

| RA3    | 4      | —                 | —                  | —       | _            |        | _       | IOC       | Y(1)    | MCLR/VPP    |

| RA4    | 3      | AN3               | —                  | T1G     | _            | —      | —       | IOC       | Y       | OSC2/CLKOUT |

| RA5    | 2      | —                 | —                  | T1CKI   | _            | _      | —       | IOC       | Y       | OSC1/CLKIN  |

| RB4    | 13     | AN10              | —                  | —       | _            | —      | SDI/SDA | IOC       | Y       | —           |

| RB5    | 12     | AN11              | —                  | —       | _            | RX/DT  | —       | IOC       | Y       |             |

| RB6    | 11     | —                 | —                  | —       | _            |        | SCL/SCK | IOC       | Y       |             |

| RB7    | 10     | —                 | —                  | —       |              | TX/CK  | _       | IOC       | Y       |             |

| RC0    | 16     | AN4               | C2IN+              | _       | _            |        | _       |           | _       |             |

| RC1    | 15     | AN5               | C12IN1-            | —       | _            | _      | —       | _         | _       | _           |

| RC2    | 14     | AN6               | C12IN2-            | —       | P1D          |        | _       |           | _       |             |

| RC3    | 7      | AN7               | C12IN3-            | —       | P1C          | _      | —       | -         | _       | _           |

| RC4    | 6      |                   | C2OUT              | —       | P1B          | _      | —       | _         | _       | _           |

| RC5    | 5      |                   | —                  | —       | CCP1/P1A     | _      | —       | _         | _       | _           |

| RC6    | 8      | AN8               | —                  | —       | —            | —      | SS      | —         | —       | —           |

| RC7    | 9      | AN9               |                    | —       | _            | _      | SDO     | _         | _       |             |

|        | 1      |                   |                    | —       | _            | _      | —       | _         |         | Vdd         |

| _      | 20     | _                 | _                  | —       | _            | _      | —       | _         | —       | Vss         |

| Note 1 | I: Pul | I-up activated on | ly with external I | MCLR co | nfiguration. |        |         |           |         |             |

# 2.2.2.2 OPTION Register

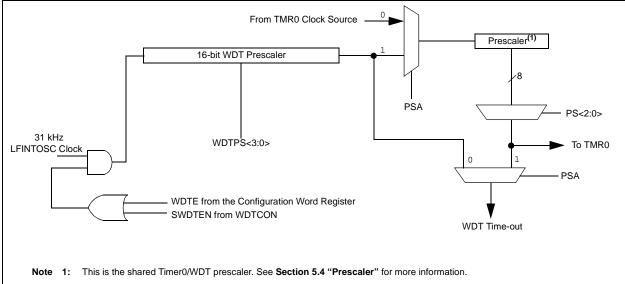

The OPTION register, shown in Register 2-2, is a readable and writable register, which contains various control bits to configure:

- Timer0/WDT prescaler

- External RA2/INT interrupt

- Timer0

- Weak pull-ups on PORTA/PORTB

Note: To achieve a 1:1 prescaler assignment for Timer0, assign the prescaler to the WDT by setting PSA bit of the OPTION register to '1'. See Section 6.3 "Timer1 Prescaler".

# REGISTER 2-2: OPTION\_REG: OPTION REGISTER

| R/W-1 | R/W-1            | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|------------------|-------|-------|-------|-------|-------|-------|

| RABPU | PU INTEDG TOCS 1 |       | TOSE  | PSA   | PS2   | PS1   | PS0   |

| bit 7 |                  |       |       |       |       |       | bit 0 |

| Legend:    |                                                                                                                  |                                                                                                                                                |                           |            |                         |                    |  |  |  |  |  |

|------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------|-------------------------|--------------------|--|--|--|--|--|

| R = Reada  | ble bit                                                                                                          | VV = V                                                                                                                                         | Writable bit              |            | U = Unimplemented bit   | , read as '0'      |  |  |  |  |  |

| -n = Value | at POR                                                                                                           | '1' =                                                                                                                                          | Bit is set                |            | '0' = Bit is cleared    | x = Bit is unknown |  |  |  |  |  |

|            |                                                                                                                  |                                                                                                                                                |                           |            |                         |                    |  |  |  |  |  |

| bit 7      |                                                                                                                  |                                                                                                                                                | ORTB Pull-up              |            | t                       |                    |  |  |  |  |  |

|            |                                                                                                                  |                                                                                                                                                | pull-ups are pull-ups are |            | y individual PORT latch | values             |  |  |  |  |  |

| bit 6      | INTED                                                                                                            | G: Interrupt E                                                                                                                                 | Edge Select b             | it         |                         |                    |  |  |  |  |  |

|            |                                                                                                                  |                                                                                                                                                | ng edge of RA             |            |                         |                    |  |  |  |  |  |

| bit 5      | T0CS:                                                                                                            | TOCS: Timer0 Clock Source Select bit                                                                                                           |                           |            |                         |                    |  |  |  |  |  |

|            | 1 <b>= Tra</b>                                                                                                   | 1 = Transition on RA2/T0CKI pin                                                                                                                |                           |            |                         |                    |  |  |  |  |  |

|            | 0 = Inte                                                                                                         | 0 = Internal instruction cycle clock (Fosc/4)                                                                                                  |                           |            |                         |                    |  |  |  |  |  |

| bit 4      | T0SE:                                                                                                            | T0SE: Timer0 Source Edge Select bit                                                                                                            |                           |            |                         |                    |  |  |  |  |  |

|            |                                                                                                                  | <ul> <li>1 = Increment on high-to-low transition on RA2/T0CKI pin</li> <li>0 = Increment on low-to-high transition on RA2/T0CKI pin</li> </ul> |                           |            |                         |                    |  |  |  |  |  |

| bit 3      |                                                                                                                  | <b>PSA:</b> Prescaler Assignment bit                                                                                                           |                           |            |                         |                    |  |  |  |  |  |

|            | <ul> <li>1 = Prescaler is assigned to the WDT</li> <li>0 = Prescaler is assigned to the Timer0 module</li> </ul> |                                                                                                                                                |                           |            |                         |                    |  |  |  |  |  |

| bit 2-0    | PS<2:0                                                                                                           | PS<2:0>: Prescaler Rate Select bits                                                                                                            |                           |            |                         |                    |  |  |  |  |  |

|            |                                                                                                                  | Bit Value                                                                                                                                      | Timer0 Rate               | WDT Rate   | e                       |                    |  |  |  |  |  |

|            |                                                                                                                  | 000                                                                                                                                            | 1:2                       | 1:1        | -                       |                    |  |  |  |  |  |

|            |                                                                                                                  | 001                                                                                                                                            | 1:4                       | 1:2        |                         |                    |  |  |  |  |  |

|            |                                                                                                                  | 010<br>011                                                                                                                                     | 1:8<br>1:16               | 1:4<br>1:8 |                         |                    |  |  |  |  |  |

|            |                                                                                                                  |                                                                                                                                                |                           | 1          |                         |                    |  |  |  |  |  |

100

101

110 111 1:32

1 : 64 1 : 128

1:256

1 : 16 1 : 32

1:64

1:128

# 4.2 Additional Pin Functions

Every PORTA pin on this device family has an interrupton-change option and a weak pull-up option. RA0 also has an Ultra Low-Power Wake-up option. The next three sections describe these functions.

# 4.2.1 ANSEL AND ANSELH REGISTERS

The ANSEL and ANSELH registers are used to disable the input buffers of I/O pins, which allow analog voltages to be applied to those pins without causing excessive current. Setting the ANSx bit of a corresponding pin will cause all digital reads of that pin to return '0' and also permit analog functions of that pin to operate correctly.

The state of the ANSx bit has no effect on the digital output function of its corresponding pin. A pin with the TRISx bit clear and ANSx bit set will operate as a digital output, together with the analog input function of that pin. Pins with the ANSx bit set always read '0', which can cause unexpected behavior when executing read or write operations on the port due to the read-modifywrite sequence of all such operations.

# 4.2.2 WEAK PULL-UPS

Each of the PORTA pins, except RA3, has an individually configurable internal weak pull-up. Control bits WPUAx enable or disable each pull-up. Refer to Register 4-4. Each weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset by the RABPU bit of the OPTION register. A weak pull-up is automatically enabled for RA3 when configured as MCLR and disabled when RA3 is an I/O. There is no software control of the MCLR pull-up.

# 4.2.3 INTERRUPT-ON-CHANGE

Each PORTA pin is individually configurable as an interrupt-on-change pin. Control bits IOCAx enable or disable the interrupt function for each pin. Refer to Register 4-6. The interrupt-on-change is disabled on a Power-on Reset.

For enabled interrupt-on-change pins, the values are compared with the old value latched on the last read of PORTA. The 'mismatch' outputs of the last read are OR'd together to set the PORTA Change Interrupt Flag bit (RABIF) in the INTCON register (Register 2-6).

This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, clears the interrupt by:

- a) Any read or write of PORTA. This will end the mismatch condition, then,

- b) Clear the flag bit RABIF.

A mismatch condition will continue to set flag bit RABIF. Reading PORTA will end the mismatch condition and allow flag bit RABIF to be cleared. The latch holding the last read value is not affected by a MCLR nor BOR Reset. After these Resets, the RABIF flag will continue to be set if a mismatch is present.

**Note:** If a change on the I/O pin should occur when the read operation is being executed (start of the Q2 cycle), then the RABIF interrupt flag may not get set.

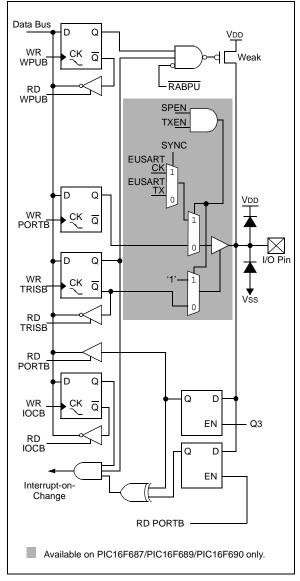

# 4.3 PORTB and TRISB Registers

PORTB is a 4-bit wide, bidirectional port. The corresponding data direction register is TRISB (Register 4-6). Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 4-3 shows how to initialize PORTB. Reading the PORTB register (Register 4-5) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch.

The TRISB register controls the PORTB pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISB register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

EXAMPLE 4-3: INITIALIZING PORTB

| BCF   | STATUS, RPO | ;Bank 0                |

|-------|-------------|------------------------|

| BCF   | STATUS, RP1 | ;                      |

| CLRF  | PORTB       | ;Init PORTB            |

| BSF   | STATUS, RPO | ;Bank 1                |

| MOVLW | FFh         | ;Set RB<7:4> as inputs |

| MOVWF | TRISB       | ;                      |

| BCF   | STATUS, RPO | ;Bank 0                |

|       |             |                        |

Note: The ANSELH register must be initialized to configure an analog channel as a digital input. Pins configured as analog inputs will read '0'.

# 4.4 Additional PORTB Pin Functions

PORTB pins RB<7:4> on the device family device have an interrupt-on-change option and a weak pull-up option. The following three sections describe these PORTB pin functions.

# REGISTER 4-7: PORTB: PORTB REGISTER

# 4.4.1 WEAK PULL-UPS

Each of the PORTB pins has an individually configurable internal weak pull-up. Control bits WPUB<7:4> enable or disable each pull-up (see Register 4-9). Each weak pull up is automatically turned off when the port pin is configured as an output. <u>All pull-ups</u> are disabled on a Power-on Reset by the RABPU bit of the OPTION register.

# 4.4.2 INTERRUPT-ON-CHANGE

Four of the PORTB pins are individually configurable as an interrupt-on-change pin. Control bits IOCB<7:4> enable or disable the interrupt function for each pin. Refer to Register 4-10. The interrupt-on-change feature is disabled on a Power-on Reset.

For enabled interrupt-on-change pins, the present value is compared with the old value latched on the last read of PORTB to determine which bits have changed or mismatch the old value. The 'mismatch' outputs are OR'd together to set the PORTB Change Interrupt flag bit (RABIF) in the INTCON register (Register 2-3).

This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, clears the interrupt by:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear the flag bit RABIF.

A mismatch condition will continue to set flag bit RABIF. Reading or writing PORTB will end the mismatch condition and allow flag bit RABIF to be cleared. The latch holding the last read value is not affected by a MCLR nor Brown-out Reset. After these Resets, the RABIF flag will continue to be set if a mismatch is present.

| Note: | If a change on the I/O pin should occur<br>when the read operation is being executed<br>(start of the Q2 cycle), then the RABIF<br>interrupt flag may not get set. Furthermore,<br>since a read or write on a port affects all bits<br>of that port, care must be taken when using<br>multiple pins in Interrupt-on-Change mode.<br>Changes on one pin may not be seen while<br>servicing changes on another pin. |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                                                                                                                                                                                                                                                                                                                                                                                                                   |

| R/W-x            | R/W-x                                                                 | R/W-x            | R/W-x | U-0                                     | U-0 | U-0 | U-0   |  |  |

|------------------|-----------------------------------------------------------------------|------------------|-------|-----------------------------------------|-----|-----|-------|--|--|

| RB7              | RB6                                                                   | RB5              | RB4   | —                                       | —   | —   | _     |  |  |

| bit 7            | •                                                                     |                  |       |                                         |     |     | bit ( |  |  |

|                  |                                                                       |                  |       |                                         |     |     |       |  |  |

| Legend:          |                                                                       |                  |       |                                         |     |     |       |  |  |

| R = Readable bi  | t                                                                     | W = Writable bit |       | U = Unimplemented bit, read as '0'      |     |     |       |  |  |

| -n = Value at PO | R                                                                     | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |     |     |       |  |  |

|                  |                                                                       |                  |       |                                         |     |     |       |  |  |

| bit 7-4          | <b>RB&lt;7:4&gt;</b> : PORT<br>1 = Port pin is ><br>0 = Port pin is < | Vih              |       |                                         |     |     |       |  |  |

| bit 3-0          | Unimplemented                                                         | I Read as '0'    |       |                                         |     |     |       |  |  |

# 4.4.3.4 RB7/TX/CK

Figure 4-10 shows the diagram for this pin. The RB7/  $TX/CK^{(1)}$  pin is configurable to function as one of the following:

- a general purpose I/O

- an asynchronous serial output

- a synchronous clock I/O

Note 1: TX and CK are available on PIC16F687/ PIC16F689/PIC16F690 only.

### FIGURE 4-10: BLOCK DIAGRAM OF RB7

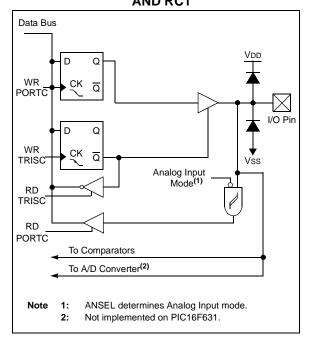

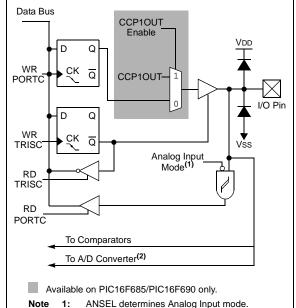

#### 4.5.1 RC0/AN4/C2IN+

The RC0 is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC (except PIC16F631)

- an analog input to Comparator C2

#### 4.5.2 RC1/AN5/C12IN1-

The RC1 is configurable to function as one of the following:

- a general purpose I/O

- · an analog input for the ADC

- an analog input to Comparator C1 or C2

# FIGURE 4-11:

#### **BLOCK DIAGRAM OF RC0** AND RC1

#### RC2/AN6/C12IN2-/P1D 4.5.3

The RC2/AN6/P1D<sup>(1)</sup> is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC (except PIC16F631)

- · a PWM output

- an analog input to Comparator C1 or C2

Note 1: P1D is available on PIC16F685/ PIC16F690 only.

#### 4.5.4 RC3/AN7/C12IN3-/P1C

The RC3/AN7/P1C<sup>(1)</sup> is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC (except PIC16F631)

- · a PWM output

- · a PWM output

- an analog input to Comparator C1 or C2

Note 1: P1C is available on PIC16F685/ PIC16F690 only.

# **FIGURE 4-12:**

#### **BLOCK DIAGRAM OF RC2** AND RC3

1: ANSEL determines Analog Input mode.

2: Not implemented on PIC16F631.

| TABLE 4-3: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTC |

|------------|--------------------------------------------|

|------------|--------------------------------------------|

| Name                   | Bit 7  | Bit 6  | Bit 5  | Bit 4   | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|--------|--------|--------|---------|--------|--------|--------|--------|----------------------|---------------------------------|

| ANSEL                  | ANS7   | ANS6   | ANS5   | ANS4    | ANS3   | ANS2   | ANS1   | ANS0   | 1111 1111            | 1111 1111                       |

| ANSELH                 | _      | _      | _      |         | ANS11  | ANS10  | ANS9   | ANS8   | 1111                 | 1111                            |

| CCP1CON <sup>(2)</sup> | P1M1   | P1M0   | DC1B1  | DC1B0   | CCP1M3 | CCP1M2 | CCP1M1 | CCP1M0 | 0000 0000            | 0000 0000                       |

| CM2CON0                | C2ON   | C2OUT  | C2OE   | C2POL   | —      | C2R    | C2CH1  | C2CH0  | 0000 -000            | 0000 -000                       |

| CM2CON1                | MC10UT | MC2OUT | _      | -       | _      | _      | T1GSS  | C2SYNC | 0010                 | 0010                            |

| PORTC                  | RC7    | RC6    | RC5    | RC4     | RC3    | RC2    | RC1    | RC0    | XXXX XXXX            | uuuu uuuu                       |

| PSTRCON                | _      | _      | _      | STRSYNC | STRD   | STRC   | STRB   | STRA   | 0 0001               | 0 0001                          |

| SRCON                  | SR1    | SR0    | C1SEN  | C2REN   | PULSS  | PULSR  | _      | _      | 0000 00              | 0000 00                         |

| SSPCON <sup>(1)</sup>  | WCOL   | SSPOV  | SSPEN  | CKP     | SSPM3  | SSPM2  | SSPM1  | SSPM0  | 0000 0000            | 0000 0000                       |

| TRISC                  | TRISC7 | TRISC6 | TRISC5 | TRISC4  | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                       |

| VRCON                  | C1VREN | C2VREN | VRR    | VP6EN   | VR3    | VR2    | VR1    | VR0    | 0000 0000            | 0000 0000                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTC.

Note 1: PIC16F687/PIC16F689/PIC16F690 only.

2: PIC16F685/PIC16F690 only.

# 5.1.3 SOFTWARE PROGRAMMABLE PRESCALER

A single software programmable prescaler is available for use with either Timer0 or the Watchdog Timer (WDT), but not both simultaneously. The prescaler assignment is controlled by the PSA bit of the OPTION register. To assign the prescaler to Timer0, the PSA bit must be cleared to a '0'.

There are eight prescaler options for the Timer0 module ranging from 1:2 to 1:256. The prescale values are selectable via the PS<2:0> bits of the OPTION register. In order to have a 1:1 prescaler value for the Timer0 module, the prescaler must be assigned to the WDT module.

The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, all instructions writing to the TMR0 register will clear the prescaler.

When the prescaler is assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT.

### 5.1.3.1 Switching Prescaler Between Timer0 and WDT Modules

As a result of having the prescaler assigned to either Timer0 or the WDT, it is possible to generate an unintended device Reset when switching prescaler values. When changing the prescaler assignment from Timer0 to the WDT module, the instruction sequence shown in Example 5-1, must be executed.

# EXAMPLE 5-1: CHANGING PRESCALER (TIMER0 $\rightarrow$ WDT)

| BANKSEL        | TMR0                       | ;                             |

|----------------|----------------------------|-------------------------------|

| CLRWDT         |                            | ;Clear WDT                    |

| CLRF           | TMR0                       | ;Clear TMR0 and               |

|                |                            | ;prescaler                    |

| BANKSEL        | OPTION_REG                 | ;                             |

| BSF            | OPTION_REG,                | PSA;Select WDT                |

| CLRWDT         |                            | ;                             |

|                |                            |                               |

|                |                            | i                             |

| MOVLW          | b'11111000'                | ;<br>;Mask prescaler          |

| MOVLW<br>ANDWF | b'11111000'<br>OPTION_REG, | -                             |

|                | OPTION_REG,                | -                             |

| ANDWF          | OPTION_REG,                | W; bits<br>;Set WDT prescaler |

When changing the prescaler assignment from the WDT to the Timer0 module, the following instruction sequence must be executed (see Example 5-2).

# EXAMPLE 5-2: CHANGING PRESCALER (WDT $\rightarrow$ TIMER0)

| CLRWDT  | ;Clear WDT and                   |

|---------|----------------------------------|

|         | ;prescaler                       |

| BANKSEL | OPTION_REG ;                     |

| MOVLW   | b'11110000';Mask TMR0 select and |

| ANDWF   | OPTION_REG,W; prescaler bits     |

| IORLW   | b'00000011';Set prescale to 1:16 |

| MOVWF   | OPTION_REG ;                     |

|         |                                  |

### 5.1.4 TIMER0 INTERRUPT

Timer0 will generate an interrupt when the TMR0 register overflows from FFh to 00h. The T0IF interrupt flag bit of the INTCON register is set every time the TMR0 register overflows, regardless of whether or not the Timer0 interrupt is enabled. The T0IF bit must be cleared in software. The Timer0 interrupt enable is the T0IE bit of the INTCON register.

| Note: | The Timer0 interrupt cannot wake the    |  |  |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|--|--|

|       | processor from Sleep since the timer is |  |  |  |  |  |  |

|       | frozen during Sleep.                    |  |  |  |  |  |  |

# 5.1.5 USING TIMER0 WITH AN EXTERNAL CLOCK

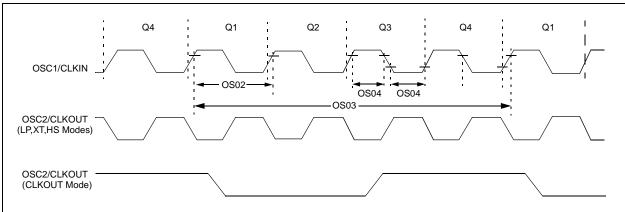

When Timer0 is in Counter mode, the synchronization of the T0CKI input and the Timer0 register is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, the high and low periods of the external clock source must meet the timing requirements as shown in Section 17.0 "Electrical Specifications".

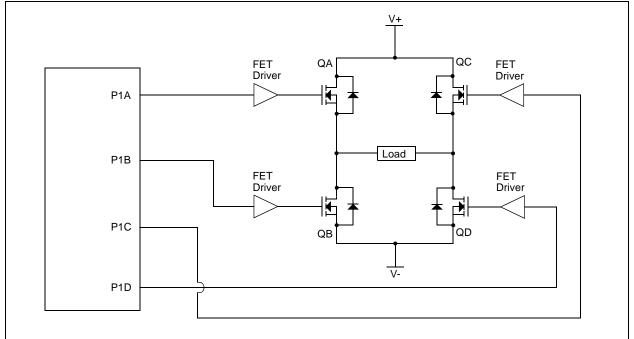

### 11.4.2 FULL-BRIDGE MODE

In Full-Bridge mode, all four pins are used as outputs. An example of Full-Bridge application is shown in Figure 11-10.

In the Forward mode, pin CCP1/P1A is driven to its active state, pin P1D is modulated, while P1B and P1C will be driven to their inactive state as shown in Figure 11-11.

In the Reverse mode, P1C is driven to its active state, pin P1B is modulated, while P1A and P1D will be driven to their inactive state as shown Figure 11-11.

P1A, P1B, P1C and P1D outputs are multiplexed with the PORT data latches. The associated TRIS bits must be cleared to configure the P1A, P1B, P1C and P1D pins as outputs.

# FIGURE 11-10: EXAMPLE OF FULL-BRIDGE APPLICATION

### 11.4.7 PULSE STEERING MODE

In Single Output mode, pulse steering allows any of the PWM pins to be the modulated signal. Additionally, the same PWM signal can be simultaneously available on multiple pins.

Once the Single Output mode is selected (CCP1M<3:2> = 11 and P1M<1:0> = 00 of the CCP1CON register), the user firmware can bring out the same PWM signal to one, two, three or four output pins by setting the appropriate STR<D:A> bits of the PSTRCON register, as shown in Figure 11-19.

Note: The associated TRIS bits must be set to output ('0') to enable the pin output driver in order to see the PWM signal on the pin.

While the PWM Steering mode is active, CCP1M<1:0> bits of the CCP1CON register select the PWM output polarity for the P1<D:A> pins.

The PWM auto-shutdown operation also applies to PWM Steering mode as described in **Section 11.4.4** "**Enhanced PWM Auto-shutdown mode**". An autoshutdown event will only affect pins that have PWM outputs enabled.

# **REGISTER 11-4: PSTRCON: PULSE STEERING CONTROL REGISTER<sup>(1)</sup>**

| U-0          | U-0                                                                    | U-0                         | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-1 |  |

|--------------|------------------------------------------------------------------------|-----------------------------|------------------|------------------|------------------|-----------------|-------|--|

| _            |                                                                        | _                           | STRSYNC          | STRD             | STRC             | STRB            | STRA  |  |

| bit 7        |                                                                        | ·                           |                  |                  |                  |                 | bit ( |  |

| Legend:      |                                                                        |                             |                  |                  |                  |                 |       |  |

| R = Readat   | ole bit                                                                | W = Writable                | bit              | U = Unimpler     | nented bit, read | d as '0'        |       |  |

| -n = Value a | at POR                                                                 | '1' = Bit is se             | t                | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |  |

|              |                                                                        |                             |                  |                  |                  |                 |       |  |

| bit 7-5      | Unimpleme                                                              | ented: Read as              | '0'              |                  |                  |                 |       |  |

| bit 4        | STRSYNC:                                                               | Steering Sync I             | pit              |                  |                  |                 |       |  |

|              | 1 = Output                                                             | steering update             | occurs on next   | PWM period       |                  |                 |       |  |

|              | 0 = Output                                                             | steering update             | occurs at the be | eginning of the  | instruction cyc  | le boundary     |       |  |

| bit 3        | STRD: Stee                                                             | ering Enable bit            | D                |                  |                  |                 |       |  |

|              |                                                                        | has the PWM                 |                  | olarity control  | from CCP1M<      | 1:0>            |       |  |

|              | 0 = P1D pir                                                            | n is assigned to            | port pin         |                  |                  |                 |       |  |

| bit 2        | STRC: Stee                                                             | ering Enable bit            | С                |                  |                  |                 |       |  |

|              | 1 = P1C pir                                                            | has the PWM                 | waveform with p  | olarity control  | from CCP1M<      | 1:0>            |       |  |

|              | 0 = P1C pir                                                            | n is assigned to            | port pin         |                  |                  |                 |       |  |

| bit 1        | STRB: Stee                                                             | ering Enable bit            | В                |                  |                  |                 |       |  |

|              | 1 = P1B pin has the PWM waveform with polarity control from CCP1M<1:0> |                             |                  |                  |                  |                 |       |  |

|              | 0 = P1B pin is assigned to port pin                                    |                             |                  |                  |                  |                 |       |  |

| bit 0        | STRA: Stee                                                             | STRA: Steering Enable bit A |                  |                  |                  |                 |       |  |

|              | 1 = P1A pin has the PWM waveform with polarity control from CCP1M<1:0> |                             |                  |                  |                  |                 |       |  |

|              | 0 = P1A pir                                                            | n is assigned to            | port pin         |                  |                  |                 |       |  |

Note 1: The PWM Steering mode is available only when the CCP1CON register bits CCP1M<3:2> = 11 and P1M<1:0> = 00.

## 12.4.1.5 Synchronous Master Reception

Data is received at the RX/DT pin. The RX/DT pin output driver is automatically disabled when the EUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCSTA register) or the Continuous Receive Enable bit (CREN of the RCSTA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence.

To initiate reception, set either SREN or CREN. Data is sampled at the RX/DT pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCIF bit is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCREG. The RCIF bit remains set as long as there are un-read characters in the receive FIFO.

### 12.4.1.6 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TX/CK line. The TX/ CK pin output driver is automatically disabled when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

### 12.4.1.7 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCREG is read to access the FIFO. When this happens the OERR bit of the RCSTA register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCREG. If the overrun occurred when the CREN bit is set then the error condition is cleared by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

### 12.4.1.8 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set the EUSART will shift 9-bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth, and Most Significant, data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

#### 12.4.1.9 Synchronous Master Reception Setup:

- 1. Initialize the SPBRGH, SPBRG register pair for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- 4. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit reception is desired, set bit RX9.

- 6. Start reception by setting the SREN bit or for continuous reception, set the CREN bit.

- 7. Interrupt flag bit RCIF will be set when reception of a character is complete. An interrupt will be generated if the enable bit RCIE was set.

- 8. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREG register.

- 10. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

# REGISTER 13-1: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER<sup>(1)</sup>

| R/W-0            | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R-0                                                                           | R-0                                               | R-0                | R-0                | R-0                 | R-0           |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|---------------------------------------------------|--------------------|--------------------|---------------------|---------------|

| SMP              | CKE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | D/A                                                                           | Р                                                 | S                  | R/W                | UA                  | BF            |

| bit 7            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                               |                                                   |                    |                    |                     | bit (         |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                               |                                                   |                    |                    |                     |               |

| Legend:          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                               |                                                   |                    |                    | ( <b>a</b> )        |               |

| R = Readable b   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | W = Writable bit                                                              |                                                   |                    | nented bit, read a |                     |               |

| -n = Value at PC | DR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | '1' = Bit is set                                                              |                                                   | '0' = Bit is clea  | ared               | x = Bit is unkno    | wn            |

| bit 7            | SPI Master mo<br>1 = Input data =<br>0 = Input data =<br>SPI Slave mod<br>SMP must be o<br>$I^2C^{TM}$ mode:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | sampled at end of sampled at middle                                           | data output ti<br>of data outpu<br>is used in Sla | ut time (Microwire | e)                 |                     |               |

| bit 6            | CKE: SPI Clock Edge Select bit         SPI mode. CKP = 0:         1 = Data transmitted on rising edge of SCK (Microwire alternate)         0 = Data transmitted on falling edge of SCK         SPI mode. CKP = 1:         1 = Data transmitted on falling edge of SCK (Microwire default)         0 = Data transmitted on falling edge of SCK (Microwire default)         0 = Data transmitted on rising edge of SCK (Microwire default)         0 = Data transmitted on rising edge of SCK (Microwire default)         0 = Data transmitted on rising edge of SCK (Microwire default)         0 = Data transmitted on rising edge of SCK (Microwire default)         0 = Data transmitted on rising edge of SCK (Microwire default)         0 = Data transmitted on rising edge of SCK (Microwire default)         0 = Data transmitted on rising edge of SCK (Microwire default)         0 = Data transmitted on rising edge of SCK (Microwire default)         0 = Data transmitted on rising edge of SCK (Microwire default)         0 = Data transmitted on rising edge of SCK (Microwire default)         0 = Data transmitted on rising edge of SCK (Microwire default) |                                                                               |                                                   |                    |                    |                     |               |

| bit 5            | 1 = Indicates the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | DRESS bit (I <sup>2</sup> C m<br>nat the last byte re<br>nat the last byte re | eceived or trar                                   |                    |                    |                     |               |

| bit 4            | SSPEN is clea<br>1 = Indicates th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | red when the SSP                                                              | been detected                                     |                    |                    | tected last.        |               |

| bit 3            | SSPEN is clea<br>1 = Indicates th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | red when the SSP                                                              | been detected                                     |                    |                    | tected last.        |               |

| bit 2            | This bit holds th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | RITE bit Information<br>ne R/W bit informa<br>rt bit, Stop bit or A           | tion following                                    |                    | match. This bit is | only valid from the | address match |

| bit 1            | 1 = Indicates th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ldress bit (10-bit l <sup>2</sup><br>nat the user needs<br>bes not need to be | s to update the                                   |                    | SSPADD registe     | r                   |               |

| bit 0            | 1 = Receive co<br>0 = Receive no<br><u>Transmit (<math>I^2Cr</math></u><br>1 = Transmit in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | and I <sup>2</sup> C modes):<br>omplete, SSPBUF<br>ot complete, SSPE          | BUF is empty<br>JF is full                        |                    |                    |                     |               |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 689/PIC16F690 or                                                              | •                                                 |                    |                    |                     |               |

2: Does not update if receive was ignored.

## 13.12.2 RECEPTION

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address <u>byte</u> overflow condition exists, then no Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF of the SSPSTAT register is set, or bit SSPOV of the SSPCON register is set. This is an error condition due to the user's firmware.

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF of the PIR1 register must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

| FIGURE 13-8: | I <sup>2</sup> C <sup>™</sup> WAVEFORMS FOR RECEPTION (7-BIT ADDRESS) |

|--------------|-----------------------------------------------------------------------|

|              |                                                                       |

| - R/                                                         | $\overline{V} = 0$ |                                                            |                               |                                       |

|--------------------------------------------------------------|--------------------|------------------------------------------------------------|-------------------------------|---------------------------------------|

| Receiving Address                                            | ACK Receivin       | g Data ACK                                                 | Receiving Data                | ACK                                   |

| SDA I A7 A6 A5 A4 A3 A2 A1                                   | /D7XD6XD5XD4X      | $D3 \langle D2 \rangle D1 \langle D0 \rangle / D7 \rangle$ | D6\D5\D4\D3\D2\D1             |                                       |

|                                                              |                    |                                                            |                               |                                       |

| SCL <u>'IS</u> ! <u>1</u> 2 <u>3</u> 4 <u>5</u> 6 <u>7</u> 8 | 9 + 1 2 3 4        |                                                            |                               | _/8 <del>\</del> /9\_/ <sup>+</sup> ⊢ |

|                                                              |                    |                                                            |                               |                                       |

|                                                              |                    |                                                            |                               | i   T                                 |

| SSPIF (PIR1<3>)                                              | Cleared            | in software                                                |                               | Bus Master                            |

|                                                              |                    | I I                                                        |                               | terminates<br>transfer                |

| BF (SSPSTAT<0>)                                              | SSPBUF re          | nister is read                                             |                               |                                       |

|                                                              |                    | gister is read                                             |                               |                                       |

|                                                              |                    |                                                            |                               | 1                                     |

| SSPOV (SSPCON<6>)                                            |                    |                                                            |                               |                                       |

|                                                              | Dit (              |                                                            |                               |                                       |

|                                                              | Bit S              | SPOV is set because the                                    | SSPBUF register is still full | . <b></b>                             |

|                                                              |                    |                                                            | ACK is not ser                | nt                                    |

|                                                              |                    |                                                            |                               |                                       |

# 14.4 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (e.g., W and STATUS registers). This must be implemented in software.

Since the upper 16 bytes of all GPR banks are common in the PIC16F631/677/685/687/689/690 (see Figures 2-2 and 2-3), temporary holding registers, W\_TEMP and STATUS\_TEMP, should be placed in here. These 16 locations do not require banking and therefore, make it easier to context save and restore. The same code shown in Example 14-1 can be used to:

- Store the W register

- Store the STATUS register

- Execute the ISR code

- Restore the Status (and Bank Select Bit register)

- Restore the W register

Note: The PIC16F631/677/685/687/689/690 normally does not require saving the PCLATH. However, if computed GOTO's are used in the ISR and the main code, the PCLATH must be saved and restored in the ISR.

### EXAMPLE 14-1: SAVING STATUS AND W REGISTERS IN RAM

| MOVWF<br>SWAPF<br>CLRF<br>MOVWF<br>: | STATUS,W<br>STATUS | ;Copy W to TEMP register<br>;Swap status to be saved into W<br>;bank 0, regardless of current bank, Clears IRP,RP1,RP0<br>;Save status to bank zero STATUS_TEMP register |

|--------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| :(ISR<br>:                           | )                  | ;Insert user code here                                                                                                                                                   |

| SWAPF                                | STATUS_TEMP,W      | ;Swap STATUS_TEMP register into W<br>;(sets bank to original state)                                                                                                      |

| MOVWF                                | STATUS             | ;Move W into STATUS register                                                                                                                                             |

| SWAPF                                | W_TEMP,F           | ;Swap W_TEMP                                                                                                                                                             |

| SWAPF                                | W_TEMP,W           | ;Swap W_TEMP into W                                                                                                                                                      |

WDT CONTROL

enable it and clearing the bit will disable it.

register. When set, the WDT runs continuously.