# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I²C, SPI                                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                         |

| Number of I/O              | 18                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 128 × 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 20-SSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f677-i-ss |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 1-5: PINOUT DESCRIPTION – PIC16F690

| Name                            | Function | Input<br>Type | Output<br>Type | Description                                                                                         |  |  |

|---------------------------------|----------|---------------|----------------|-----------------------------------------------------------------------------------------------------|--|--|

| RA0/AN0/C1IN+/ICSPDAT/<br>ULPWU | RA0      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-<br>change. Individually enabled pull-up. |  |  |

|                                 | AN0      | AN            | —              | A/D Channel 0 input.                                                                                |  |  |

|                                 | C1IN+    | AN            | —              | Comparator C1 positive input.                                                                       |  |  |

|                                 | ICSPDAT  | TTL           | CMOS           | ICSP™ Data I/O.                                                                                     |  |  |

|                                 | ULPWU    | AN            | —              | Ultra Low-Power Wake-up input.                                                                      |  |  |

| RA1/AN1/C12IN0-/VREF/ICSPCLK    | RA1      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-<br>change. Individually enabled pull-up. |  |  |

|                                 | AN1      | AN            | —              | A/D Channel 1 input.                                                                                |  |  |

|                                 | C12IN0-  | AN            | —              | Comparator C1 or C2 negative input.                                                                 |  |  |

|                                 | VREF     | AN            | —              | External Voltage Reference for A/D.                                                                 |  |  |

|                                 | ICSPCLK  | ST            | —              | ICSP™ clock.                                                                                        |  |  |

| RA2/AN2/T0CKI/INT/C1OUT         | RA2      | ST            | CMOS           | General purpose I/O. Individually controlled interrupt-on-<br>change. Individually enabled pull-up. |  |  |

|                                 | AN2      | AN            | —              | A/D Channel 2 input.                                                                                |  |  |

|                                 | T0CKI    | ST            | _              | Timer0 clock input.                                                                                 |  |  |

|                                 | INT      | ST            | —              | External interrupt.                                                                                 |  |  |

|                                 | C1OUT    | _             | CMOS           | Comparator C1 output.                                                                               |  |  |

| RA3/MCLR/Vpp                    | RA3      | TTL           | —              | General purpose input. Individually controlled interrupt-on-<br>change.                             |  |  |

|                                 | MCLR     | ST            | —              | Master Clear with internal pull-up.                                                                 |  |  |

|                                 | Vpp      | ΗV            | —              | Programming voltage.                                                                                |  |  |

| RA4/AN3/T1G/OSC2/CLKOUT         | RA4      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-<br>change. Individually enabled pull-up. |  |  |

|                                 | AN3      | AN            | —              | A/D Channel 3 input.                                                                                |  |  |

|                                 | T1G      | ST            | _              | Timer1 gate input.                                                                                  |  |  |

|                                 | OSC2     |               | XTAL           | Crystal/Resonator.                                                                                  |  |  |

|                                 | CLKOUT   | _             | CMOS           | Fosc/4 output.                                                                                      |  |  |

| RA5/T1CKI/OSC1/CLKIN            | RA5      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-<br>change. Individually enabled pull-up. |  |  |

|                                 | T1CKI    | ST            | —              | Timer1 clock input.                                                                                 |  |  |

|                                 | OSC1     | XTAL          | _              | Crystal/Resonator.                                                                                  |  |  |

|                                 | CLKIN    | ST            | _              | External clock input/RC oscillator connection.                                                      |  |  |

| RB4/AN10/SDI/SDA                | RB4      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-<br>change. Individually enabled pull-up. |  |  |

|                                 | AN10     | AN            | _              | A/D Channel 10 input.                                                                               |  |  |

|                                 | SDI      | ST            | _              | SPI data input.                                                                                     |  |  |

|                                 | SDA      | ST            | OD             | I <sup>2</sup> C™ data input/output.                                                                |  |  |

| RB5/AN11/RX/DT                  | RB5      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-<br>change. Individually enabled pull-up. |  |  |

|                                 | AN11     | AN            | —              | A/D Channel 11 input.                                                                               |  |  |

|                                 | RX       | ST            | _              | EUSART asynchronous input.                                                                          |  |  |

|                                 | 10/      | -             |                |                                                                                                     |  |  |

XTAL= Crystal

### 2.2.2.1 STATUS Register

The STATUS register, shown in Register 2-1, contains:

- the arithmetic status of the ALU

- the Reset status

- the bank select bits for data memory (GPR and SFR)

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS, will clear the upper three bits and set the Z bit. This leaves the STATUS register as `000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits, see Section 15.0 "Instruction Set Summary"

Note 1: The <u>C</u> and <u>DC</u> bits operate as a Borrow and <u>Digit</u> Borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

| R/W-0 | R/W-0 | R/W-0 | R-1 | R-1 | R/W-x | R/W-x             | R/W-x            |

|-------|-------|-------|-----|-----|-------|-------------------|------------------|

| IRP   | RP1   | RP0   | TO  | PD  | Z     | DC <sup>(1)</sup> | C <sup>(1)</sup> |

| bit 7 |       |       |     |     |       |                   | bit 0            |

| Legend:          |                                                   |                                                                                                           |                                                                                                      |                      |

|------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------|

| R = Readable bit |                                                   | W = Writable bit                                                                                          | U = Unimplemented bit                                                                                | , read as '0'        |

| -n = Value       | /alue at POR '1' = Bit is set                     |                                                                                                           | '0' = Bit is cleared                                                                                 | x = Bit is unknown   |

| bit 7            | 1 <b>= Ban</b>                                    | gister Bank Select bit (used<br>k 2, 3 (100h-1FFh)<br>k 0, 1 (00h-FFh)                                    | for indirect addressing)                                                                             |                      |

| bit 6-5          | <b>RP&lt;1:0</b><br>00 = Ba<br>01 = Ba<br>10 = Ba | Register Bank Select bits<br>ink 0 (00h-7Fh)<br>ink 1 (80h-FFh)<br>ink 2 (100h-17Fh)<br>ink 3 (180h-1FFh) | (used for direct addressing)                                                                         |                      |

| bit 4            | 1 = Afte                                          | ne-out bit<br>r power-up, CLRWDT instructi<br>/DT time-out occurred                                       | ion or SLEEP instruction                                                                             |                      |

| bit 3            | 1 = Afte                                          | wer-down bit<br>r power-up or by the CLRWD<br>execution of the SLEEP instru                               |                                                                                                      |                      |

| bit 2            |                                                   | bit<br>result of an arithmetic or log<br>result of an arithmetic or log                                   | •                                                                                                    |                      |

| bit 1            | <b>DC:</b> Dig<br>1 = A ca                        | •                                                                                                         | DDLW , SUBLW , SUBWF instruct                                                                        | ions) <sup>(1)</sup> |

| bit 0            | <b>C:</b> Carry<br>1 = A ca                       | /Borrow bit <sup>(1)</sup> (ADDWF, ADDL<br>arry-out from the Most Signifi                                 | W, SUBLW, SUBWF instruction<br>cant bit of the result occurred<br>ificant bit of the result occurred |                      |

bit of the source register.

### 2.2.2.5 PIE2 Register

The PIE2 register contains the interrupt enable bits, as shown in Register 2-5.

Note: Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

### REGISTER 2-5: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-------|-------|-----|-----|-----|-------|

| OSFIE | C2IE  | C1IE  | EEIE  | —   | —   | —   | —     |

| bit 7 |       |       |       |     |     |     | bit 0 |

| Legend:         |                                   |                                                                                            |                                    |                    |  |  |  |

|-----------------|-----------------------------------|--------------------------------------------------------------------------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable    | bit                               | W = Writable bit                                                                           | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at F | POR                               | '1' = Bit is set                                                                           | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| bit 7           | 1 = Enables                       | llator Fail Interrupt Enable b<br>oscillator fail interrupt<br>s oscillator fail interrupt | it                                 |                    |  |  |  |

| bit 6           | <b>C2IE:</b> Compa<br>1 = Enables | arator C2 Interrupt Enable b<br>Comparator C2 interrupt<br>Comparator C2 interrupt         | it                                 |                    |  |  |  |

| bit 5           | 1 = Enables                       | arator C1 Interrupt Enable b<br>Comparator C1 interrupt<br>Comparator C1 interrupt         | it                                 |                    |  |  |  |

| bit 4           | 1 = Enables                       | rite Operation Interrupt Enab<br>write operation interrupt<br>write operation interrupt    | le bit                             |                    |  |  |  |

| bit 3-0         | Unimpleme                         | nted: Read as '0'                                                                          |                                    |                    |  |  |  |

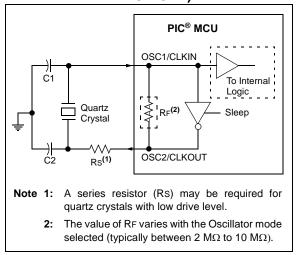

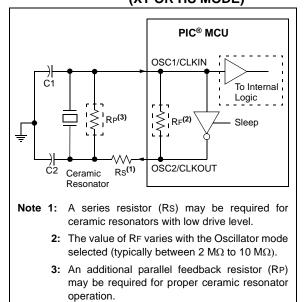

# 3.4.3 LP, XT, HS MODES

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 3-3). The mode selects a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

LP Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 3-3 and Figure 3-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

- **Note 1:** Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- **2:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC<sup>®</sup> Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

# FIGURE 3-3: QUARTZ CRYSTAL

#### OPERATION (LP, XT OR HS MODE)

#### CERAMIC RESONATOR OPERATION (XT OR HS MODE)

# 3.8 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the device to continue operating should the external oscillator fail. The FSCM can detect oscillator failure any time after the Oscillator Start-up Timer (OST) has expired. The FSCM is enabled by setting the FCMEN bit in the Configuration Word register (CONFIG). The FSCM is applicable to all external Oscillator modes (LP, XT, HS, EC, RC and RCIO).

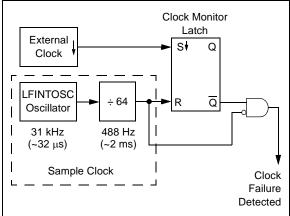

FIGURE 3-8: FSCM BLOCK DIAGRAM

# 3.8.1 FAIL-SAFE DETECTION

The FSCM module detects a failed oscillator by comparing the external oscillator to the FSCM sample clock. The sample clock is generated by dividing the LFINTOSC by 64. See Figure 3-8. Inside the fail detector block is a latch. The external clock sets the latch on each falling edge of the external clock. The sample clock clears the latch on each rising edge of the sample clock. A failure is detected when an entire half-cycle of the sample clock elapses before the primary clock goes low.

# 3.8.2 FAIL-SAFE OPERATION

When the external clock fails, the FSCM switches the device clock to an internal clock source and sets the bit flag OSFIF of the PIR2 register. Setting this flag will generate an interrupt if the OSFIE bit of the PIE2 register is also set. The device firmware can then take steps to mitigate the problems that may arise from a failed clock. The system clock will continue to be sourced from the internal clock source until the device firmware successfully restarts the external oscillator and switches back to external operation.

The internal clock source chosen by the FSCM is determined by the IRCF<2:0> bits of the OSCCON register. This allows the internal oscillator to be configured before a failure occurs.

# 3.8.3 FAIL-SAFE CONDITION CLEARING

The Fail-Safe condition is cleared after a Reset, executing a SLEEP instruction or toggling the SCS bit of the OSCCON register. When the SCS bit is toggled, the OST is restarted. While the OST is running, the device continues to operate from the INTOSC selected in OSCCON. When the OST times out, the Fail-Safe condition is cleared and the device will be operating from the external clock source. The Fail-Safe condition must be cleared before the OSFIF flag can be cleared.

## 3.8.4 RESET OR WAKE-UP FROM SLEEP

The FSCM is designed to detect an oscillator failure after the Oscillator Start-up Timer (OST) has expired. The OST is used after waking up from Sleep and after any type of Reset. The OST is not used with the EC or RC Clock modes so that the FSCM will be active as soon as the Reset or wake-up has completed. When the FSCM is enabled, the Two-Speed Start-up is also enabled. Therefore, the device will always be executing code while the OST is operating.

Note: Due to the wide range of oscillator start-up times, the Fail-Safe circuit is not active during oscillator start-up (i.e., after exiting Reset or Sleep). After an appropriate amount of time, the user should check the OSTS bit of the OSCCON register to verify the oscillator start-up and that the system clock switchover has successfully completed.

| R/W-1                              | R/W-1 | R/W-1 | R/W-1                                   | R/W-1                              | R/W-1 | R/W-1 | R/W-1 |  |

|------------------------------------|-------|-------|-----------------------------------------|------------------------------------|-------|-------|-------|--|

| ANS7                               | ANS6  | ANS5  | ANS4                                    | ANS3                               | ANS2  | ANS1  | ANS0  |  |

| bit 7                              | •     |       |                                         |                                    | •     |       | bit 0 |  |

|                                    |       |       |                                         |                                    |       |       |       |  |

| Legend:                            |       |       |                                         |                                    |       |       |       |  |

| R = Readable bit W = Writable bit  |       |       | bit                                     | U = Unimplemented bit, read as '0' |       |       |       |  |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cleared x = Bit is unknown |                                    |       |       |       |  |

#### REGISTER 4-3: ANSEL: ANALOG SELECT REGISTER

bit 7-0 ANS<7:0>: Analog Select bits Analog select between analog or digital function on pins AN<7:0>, respectively. 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. 0 = Digital I/O. Pin is assigned to port or special function.

## REGISTER 4-4: ANSELH: ANALOG SELECT HIGH REGISTER<sup>(2)</sup>

| U-0   | U-0 | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-----|-----|-------|-------|-------|-------|

| —     | —   | —   | —   | ANS11 | ANS10 | ANS9  | ANS8  |

| bit 7 |     |     |     |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 3-0 ANS<11:8>: Analog Select bits

Analog select between analog or digital function on pins AN<7:0>, respectively.

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>.

0 = Digital I/O. Pin is assigned to port or special function.

**Note 1:** Setting a pin to an analog input automatically disables the digital input circuitry, weak pull-ups and interrupt-on-change if available. The corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

2: PIC16F677/PIC16F685/PIC16F687/PIC16F689/PIC16F690 only.

**Note 1:** Setting a pin to an analog input automatically disables the digital input circuitry, weak pull-ups and interrupt-on-change if available. The corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

| U-0                | U-0                                             | R/W-1              | R/W-1        | U-0              | R/W-1            | R/W-1           | R/W-1 |

|--------------------|-------------------------------------------------|--------------------|--------------|------------------|------------------|-----------------|-------|

| _                  | —                                               | WPUA5              | WPUA4        |                  | WPUA2            | WPUA1           | WPUA0 |

| bit 7              | ł                                               |                    |              |                  |                  |                 | bit 0 |

|                    |                                                 |                    |              |                  |                  |                 |       |

| Legend:            |                                                 |                    |              |                  |                  |                 |       |

| R = Read           | able bit                                        | W = Writable       | bit          | U = Unimpler     | mented bit, read | l as '0'        |       |

| -n = Value         | e at POR                                        | '1' = Bit is set   |              | '0' = Bit is cle | ared             | x = Bit is unki | nown  |

| bit 7-6<br>bit 5-4 | -                                               | nented: Read as '( |              |                  |                  |                 |       |

| DIL 5-4            | 1 = Pull-up<br>0 = Pull-up                      |                    | Register bit |                  |                  |                 |       |

| bit 3              | Unimplem                                        | nented: Read as 'o | )'           |                  |                  |                 |       |

| bit 2-0            | <b>WPUA&lt;2:</b><br>1 = Pull-up<br>0 = Pull-up |                    | Register bit |                  |                  |                 |       |

| Note 1:<br>2:      |                                                 | bit of the OPTION  | •            |                  |                  |                 | bled. |

#### WPUA: PORTA REGISTER **REGISTER 4-5:**

3: The RA3 pull-up is enabled when configured as MCLR and disabled as an I/O in the Configuration Word.

4: WPUA<5:4> always reads '1' in XT, HS and LP Oscillator modes.

#### **REGISTER 4-6: IOCA: INTERRUPT-ON-CHANGE PORTA REGISTER**

| Logondi |     |       |       |       |       |       |       |

|---------|-----|-------|-------|-------|-------|-------|-------|

|         |     |       |       |       |       |       |       |

| bit 7   |     |       |       |       |       |       | bit 0 |

| _       | —   | IOCA5 | IOCA4 | IOCA3 | IOCA2 | IOCA1 | IOCA0 |

| U-0     | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|         |     |       |       |       |       |       |       |

| Legena.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 IOCA<5:0>: Interrupt-on-change PORTA Control bit

1 = Interrupt-on-change enabled

0 = Interrupt-on-change disabled

Note 1: Global Interrupt Enable (GIE) must be enabled for individual interrupts to be recognized.

2: IOCA<5:4> always reads '1' in XT, HS and LP Oscillator modes.

## 4.2.5.2 RA1/AN1/C12IN0-/VREF/ICSPCLK

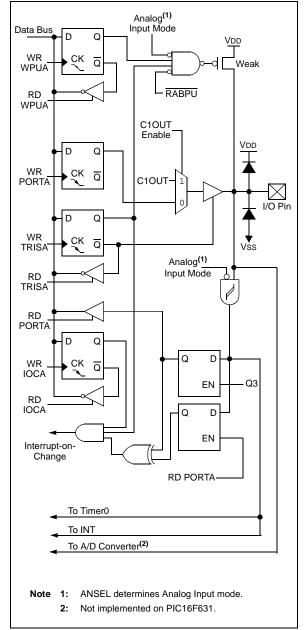

Figure 4-2 shows the diagram for this pin. The RA1/ AN1/C12IN0-/VREF/ICSPCLK pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC (except PIC16F631)

- an analog input to Comparator C1 or C2

- a voltage reference input for the ADC

- In-Circuit Serial Programming clock

#### **BLOCK DIAGRAM OF RA1** FIGURE 4-2: Analog(1) Input Mode Data Bus D Q Vdd WR CK Q Weak WPU RABPU RD WPU/ Vdd D Q WR СК Q PORTA I/O Pin D G Vss WR СК Q TRIS Analog<sup>(1)</sup> Input Mode RD TRIS/ RD PORT/ D Q D Q WR Q IOCA ΕN Q3 RD IOCA Q D ΕN Interrupt-on-Change **RD PORTA** To Comparator To A/D Converter(2) ANSEL determines Analog Input mode. Note 1: Not implemented on PIC16F631. 2:

## 4.2.5.3 RA2/AN2/T0CKI/INT/C1OUT

Figure 4-3 shows the diagram for this pin. The RA2/AN2/ T0CKI/INT/C1OUT pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC (except PIC16F631)

- the clock input for Timer0

- an external edge triggered interrupt

- a digital output from Comparator C1

## FIGURE 4-3: BLOCK DIAGRAM OF RA2

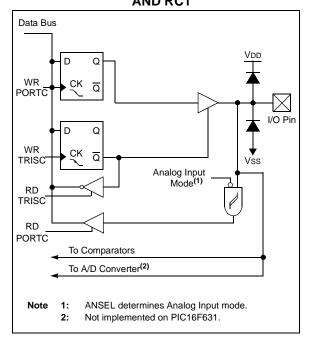

#### 4.5.1 RC0/AN4/C2IN+

The RC0 is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC (except PIC16F631)

- an analog input to Comparator C2

#### 4.5.2 RC1/AN5/C12IN1-

The RC1 is configurable to function as one of the following:

- a general purpose I/O

- · an analog input for the ADC

- an analog input to Comparator C1 or C2

# FIGURE 4-11:

#### **BLOCK DIAGRAM OF RC0** AND RC1

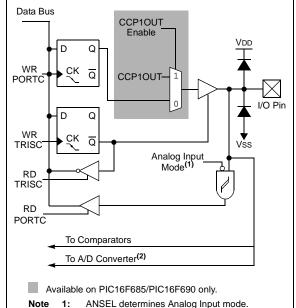

#### RC2/AN6/C12IN2-/P1D 4.5.3

The RC2/AN6/P1D<sup>(1)</sup> is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC (except PIC16F631)

- · a PWM output

- an analog input to Comparator C1 or C2

Note 1: P1D is available on PIC16F685/ PIC16F690 only.

#### 4.5.4 RC3/AN7/C12IN3-/P1C

The RC3/AN7/P1C<sup>(1)</sup> is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC (except PIC16F631)

- · a PWM output

- · a PWM output

- an analog input to Comparator C1 or C2

Note 1: P1C is available on PIC16F685/ PIC16F690 only.

# **FIGURE 4-12:**

#### **BLOCK DIAGRAM OF RC2** AND RC3

1: ANSEL determines Analog Input mode.

2: Not implemented on PIC16F631.

# 6.12 Timer1 Control Register

The Timer1 Control register (T1CON), shown in Register 6-1, is used to control Timer1 and select the various features of the Timer1 module.

## REGISTER 6-1: T1CON: TIMER 1 CONTROL REGISTER

| R/W-0                | R/W-0                                | R/W-0                      | R/W-0                  | R/W-0             | R/W-0          | R/W-0            | R/W-0      |  |

|----------------------|--------------------------------------|----------------------------|------------------------|-------------------|----------------|------------------|------------|--|

| T1GINV <sup>(1</sup> | ) TMR1GE <sup>(2)</sup>              | T1CKPS1                    | T1CKPS0                | T1OSCEN           | T1SYNC         | TMR1CS           | TMR10N     |  |

| bit 7                |                                      |                            |                        |                   |                |                  |            |  |

|                      |                                      |                            |                        |                   |                |                  |            |  |

| Legend:              |                                      |                            |                        |                   |                |                  |            |  |

| R = Readat           |                                      | W = Writable               |                        | U = Unimplen      |                |                  |            |  |

| -n = Value a         | at POR                               | '1' = Bit is set           |                        | '0' = Bit is clea | ared           | x = Bit is unki  | known      |  |

| bit 7                | T1GINV: Time                         | er1 Gate Invert            | bit(1)                 |                   |                |                  |            |  |

|                      |                                      |                            |                        | ints when Timer   | 1 gate signal  | is high)         |            |  |

|                      |                                      |                            |                        | nts when gate is  |                | 0 /              |            |  |

| bit 6                | TMR1GE: Tin                          | ner1 Gate Ena              | ble bit <sup>(2)</sup> |                   |                |                  |            |  |

|                      | If TMR1ON =                          |                            |                        |                   |                |                  |            |  |

|                      | This bit is igno                     |                            |                        |                   |                |                  |            |  |

|                      | <u>If TMR1ON =</u><br>1 = Timer1 co  |                            | olled by the Ti        | mer1 Gate fund    | tion           |                  |            |  |

|                      |                                      | always countir             |                        |                   |                |                  |            |  |

| bit 5-4              | T1CKPS<1:0                           | >: Timer1 Inpu             | t Clock Presca         | ale Select bits   |                |                  |            |  |

|                      | 11 = 1:8 Pres                        | cale Value                 |                        |                   |                |                  |            |  |

|                      | 10 = 1:4 Pres                        |                            |                        |                   |                |                  |            |  |

|                      | 01 = 1:2 Pres<br>00 = 1:1 Pres       |                            |                        |                   |                |                  |            |  |

| bit 3                |                                      | P Oscillator Er            | able Control b         | it                |                |                  |            |  |

|                      | If INTOSC wit                        | thout CLKOUT               | oscillator is a        | <u>ctive:</u>     |                |                  |            |  |

|                      |                                      | tor is enabled             | for Timer1 cloc        | ck                |                |                  |            |  |

|                      | 0 = LP oscilla<br><u>Else:</u>       | tor is off                 |                        |                   |                |                  |            |  |

|                      | This bit is igno                     | ored                       |                        |                   |                |                  |            |  |

| bit 2                |                                      |                            | lock Input Syr         | hchronization Co  | ontrol bit     |                  |            |  |

|                      | TMR1CS = 1:                          |                            |                        |                   |                |                  |            |  |

|                      |                                      | nchronize exte             |                        | ıt                |                |                  |            |  |

|                      |                                      | ize external clo           | ock input              |                   |                |                  |            |  |

|                      | <u>TMR1CS = 0</u><br>This bit is ign | <u>.</u><br>ored. Timer1 u | ses the interna        | al clock          |                |                  |            |  |

| bit 1                | 0                                    | ner1 Clock Sou             |                        |                   |                |                  |            |  |

|                      |                                      | clock from T1C             |                        | risina edae)      |                |                  |            |  |

|                      | 0 = Internal cl                      |                            | I V                    | 0 0 /             |                |                  |            |  |

| bit 0                | TMR1ON: Tin                          | ner1 On bit                |                        |                   |                |                  |            |  |

|                      | 1 = Enables T                        |                            |                        |                   |                |                  |            |  |

|                      | 0 = Stops Tim                        | ner1                       |                        |                   |                |                  |            |  |

| Note 1: 7            | T1GINV bit inverts                   | the Timer1 ga              | te logic, regar        | dless of source   |                |                  |            |  |

|                      | MR1GE bit must                       |                            |                        | or C2OUT, as se   | elected by the | T1GSS bit of the | ne CM2CON1 |  |

| r                    | egister, as a Time                   | er1 gate source            | ).                     |                   |                |                  |            |  |

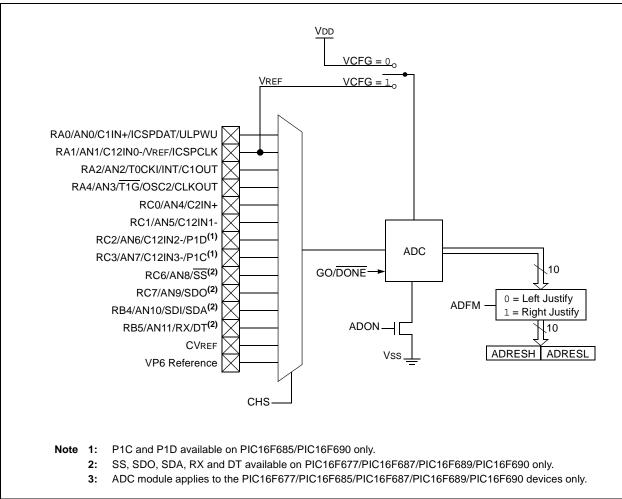

# 9.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 10-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 10-bit binary result via successive approximation and stores the conversion result into the ADC result registers (ADRESL and ADRESH).

Note: The ADC module applies to PIC16F677/ PIC16F685/PIC16F687/PIC16F689/ PIC16F690 devices only.

The ADC voltage reference is software selectable to be either internally generated or externally supplied.

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

# FIGURE 9-1: ADC BLOCK DIAGRAM

Figure 9-1 shows the block diagram of the ADC.

# TABLE 9-1:ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES (VDD $\geq$ 3.0V,<br/>VREF $\geq$ 2.5V)

| ADC Clock F                | Period (TAD) | Device Frequency (Fosc) |                         |                         |                         |  |  |

|----------------------------|--------------|-------------------------|-------------------------|-------------------------|-------------------------|--|--|

| ADC Clock Source ADCS<2:0> |              | 20 MHz                  | 20 MHz 8 MHz            |                         | 1 MHz                   |  |  |

| Fosc/2                     | 000          | 100 ns <sup>(2)</sup>   | 250 ns <sup>(2)</sup>   | 500 ns <sup>(2)</sup>   | 2.0 μs                  |  |  |

| Fosc/4                     | 100          | 200 ns <sup>(2)</sup>   | 500 ns <sup>(2)</sup>   | 1.0 μs <sup>(2)</sup>   | 4.0 μs                  |  |  |

| Fosc/8                     | 001          | 400 ns <sup>(2)</sup>   | 1.0 μs <sup>(2)</sup>   | 2.0 μs                  | 8.0 μs <sup>(3)</sup>   |  |  |

| Fosc/16                    | 101          | 800 ns <sup>(2)</sup>   | 2.0 μs                  | 4.0 μs                  | 16.0 μs <b>(3)</b>      |  |  |

| Fosc/32                    | 010          | 1.6 μs                  | 4.0 μs                  | 8.0 μs <sup>(3)</sup>   | 32.0 μs <sup>(3)</sup>  |  |  |

| Fosc/64                    | 110          | 3.2 μs                  | 8.0 μs <sup>(3)</sup>   | 16.0 μs <sup>(3)</sup>  | 64.0 μs <sup>(3)</sup>  |  |  |

| Frc                        | x11          | 2-6 μs <sup>(1,4)</sup> | 2-6 μs <sup>(1,4)</sup> | 2-6 μs <sup>(1,4)</sup> | 2-6 μs <sup>(1,4)</sup> |  |  |

Legend: Shaded cells are outside of recommended range.

- **Note 1:** The FRC source has a typical TAD time of 4  $\mu$ s for VDD > 3.0V.

- 2: These values violate the minimum required TAD time.

- **3:** For faster conversion times, the selection of another clock source is recommended.

- 4: When the device frequency is greater than 1 MHz, the FRC clock source is only recommended if the conversion will be performed during Sleep.

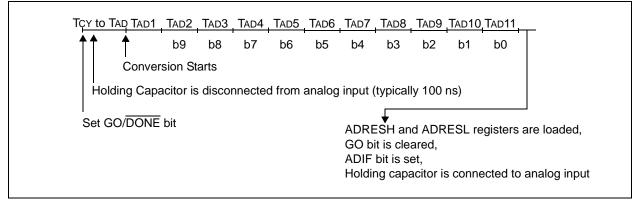

### FIGURE 9-2: ANALOG-TO-DIGITAL CONVERSION TAD CYCLES

## 9.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC interrupt flag is the ADIF bit in the PIR1 register. The ADC interrupt enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

| Note: | The ADIF bit is set at the completion of |

|-------|------------------------------------------|

|       | every conversion, regardless of whether  |

|       | or not the ADC interrupt is enabled.     |

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the global interrupt must be disabled. If the global interrupt is enabled, execution will switch to the interrupt service routine. Please see **Section 9.1.5** "Interrupts" for more information.

| U-0              | R/W-0                                                                                                                                                                                                                                                        | R/W-0            | R/W-0 | U-0              | U-0              | U-0             | U-0   |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------|------------------|------------------|-----------------|-------|--|--|

| _                | ADCS2                                                                                                                                                                                                                                                        | ADCS1            | ADCS0 | —                |                  | —               | _     |  |  |

| bit 7            |                                                                                                                                                                                                                                                              |                  |       |                  |                  |                 | bit 0 |  |  |

|                  |                                                                                                                                                                                                                                                              |                  |       |                  |                  |                 |       |  |  |

| Legend:          |                                                                                                                                                                                                                                                              |                  |       |                  |                  |                 |       |  |  |

| R = Readable     | bit                                                                                                                                                                                                                                                          | W = Writable     | bit   | U = Unimpler     | nented bit, read | d as '0'        |       |  |  |

| -n = Value at P  | OR                                                                                                                                                                                                                                                           | '1' = Bit is set |       | '0' = Bit is cle | ared             | x = Bit is unkn | iown  |  |  |

| bit 7<br>bit 6-4 | Unimplemented: Read as '0'<br>ADCS<2:0>: A/D Conversion Clock Select bits<br>000 = Fosc/2<br>001 = Fosc/8<br>010 = Fosc/32<br>x11 = FRC (clock derived from a dedicated internal oscillator = 500 kHz max)<br>100 = Fosc/4<br>101 = Fosc/16<br>110 = Fosc/64 |                  |       |                  |                  |                 |       |  |  |

| bit 3-0          | Unimplemen                                                                                                                                                                                                                                                   | ted: Read as '   | 0'    |                  |                  |                 |       |  |  |

|                  |                                                                                                                                                                                                                                                              |                  |       |                  |                  |                 |       |  |  |

# REGISTER 9-2: ADCON1: A/D CONTROL REGISTER 1

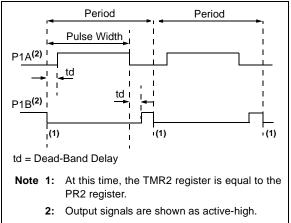

# 11.4.1 HALF-BRIDGE MODE

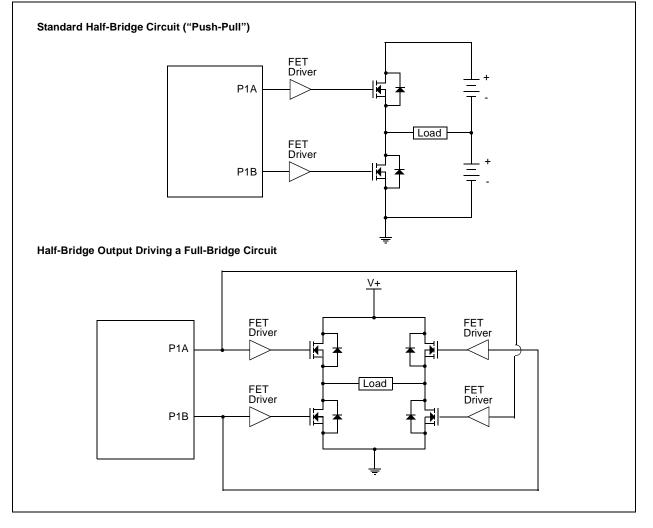

In Half-Bridge mode, two pins are used as outputs to drive push-pull loads. The PWM output signal is output on the CCP1/P1A pin, while the complementary PWM output signal is output on the P1B pin (see Figure 11-6). This mode can be used for Half-Bridge applications, as shown in Figure 11-9, or for Full-Bridge applications, where four power switches are being modulated with two PWM signals.

In Half-Bridge mode, the programmable dead-band delay can be used to prevent shoot-through current in Half-Bridge power devices. The value of the PDC<6:0> bits of the PWM1CON register sets the number of instruction cycles before the output is driven active. If the value is greater than the duty cycle, the corresponding output remains inactive during the entire cycle. See **Section 11.4.6 "Programmable Dead-Band Delay mode"** for more details of the dead-band delay operations. Since the P1A and P1B outputs are multiplexed with the PORT data latches, the associated TRIS bits must be cleared to configure P1A and P1B as outputs.

# FIGURE 11-9: EXAMPLE OF HALF-BRIDGE APPLICATIONS

# 12.1 EUSART Asynchronous Mode

The EUSART transmits and receives data using the standard non-return-to-zero (NRZ) format. NRZ is implemented with two levels: a VOH mark state which represents a '1' data bit, and a VOL space state which represents a '0' data bit. NRZ refers to the fact that consecutively transmitted data bits of the same value stay at the output level of that bit without returning to a neutral level between each bit transmission. An NRZ transmission port idles in the mark state. Each character transmission consists of one Start bit followed by eight or nine data bits and is always terminated by one or more Stop bits. The Start bit is always a space and the Stop bits are always marks. The most common data format is 8 bits. Each transmitted bit persists for a period of 1/(Baud Rate). An on-chip dedicated 8-bit/16-bit Baud Rate Generator is used to derive standard baud rate frequencies from the system oscillator. See Table 12-5 for examples of baud rate configurations.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent, but share the same data format and baud rate. Parity is not supported by the hardware, but can be implemented in software and stored as the ninth data bit.

### 12.1.1 EUSART ASYNCHRONOUS TRANSMITTER

The EUSART transmitter block diagram is shown in Figure 12-1. The heart of the transmitter is the serial Transmit Shift Register (TSR), which is not directly accessible by software. The TSR obtains its data from the transmit buffer, which is the TXREG register.

#### 12.1.1.1 Enabling the Transmitter

The EUSART transmitter is enabled for asynchronous operations by configuring the following three control bits:

- TXEN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the TXEN bit of the TXSTA register enables the transmitter circuitry of the EUSART. Clearing the SYNC bit of the TXSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the EUSART and automatically configures the TX/CK I/O pin as an output. If the TX/CK pin is shared with an analog peripheral the analog I/O function must be disabled by clearing the corresponding ANSEL bit.

- Note 1: When the SPEN bit is set the RX/DT I/O pin is automatically configured as an input, regardless of the state of the corresponding TRIS bit and whether or not the EUSART receiver is enabled. The RX/DT pin data can be read via a normal PORT read but PORT latch data output is precluded.

- 2: The TXIF transmitter interrupt flag is set when the TXEN enable bit is set.

### 12.1.1.2 Transmitting Data

A transmission is initiated by writing a character to the TXREG register. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXREG is immediately transferred to the TSR register. If the TSR still contains all or part of a previous character, the new character data is held in the TXREG until the Stop bit of the previous character has been transmitted. The pending character in the TXREG is then transferred to the TSR in one TCY immediately following the Stop bit sequence commences immediately following the transfer of the data to the TSR from the TXREG.

#### 12.1.1.3 Transmit Interrupt Flag

The TXIF interrupt flag bit of the PIR1 register is set whenever the EUSART transmitter is enabled and no character is being held for transmission in the TXREG. In other words, the TXIF bit is only clear when the TSR is busy with a character and a new character has been queued for transmission in the TXREG. The TXIF flag bit is not cleared immediately upon writing TXREG. TXIF becomes valid in the second instruction cycle following the write execution. Polling TXIF immediately following the TXREG write will return invalid results. The TXIF bit is read-only, it cannot be set or cleared by software.

The TXIF interrupt can be enabled by setting the TXIE interrupt enable bit of the PIE1 register. However, the TXIF flag bit will be set whenever the TXREG is empty, regardless of the state of TXIE enable bit.

To use interrupts when transmitting data, set the TXIE bit only when there is more data to send. Clear the TXIE interrupt enable bit upon writing the last character of the transmission to the TXREG.

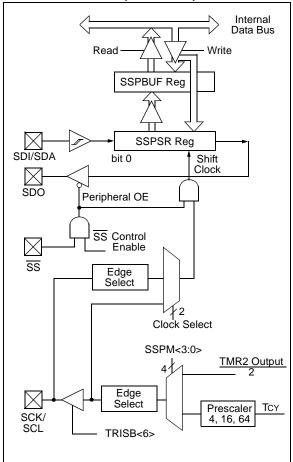

# 13.0 SSP MODULE OVERVIEW

The Synchronous Serial Port (SSP) module is a serial interface used to communicate with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The SSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)

Refer to Application Note AN578, "Use of the SSP Module in the Multi-Master Environment" (DS00578).

# 13.1 SPI Mode

This section contains register definitions and operational characteristics of the SPI module.

The SPI mode allows eight bits of data to be synchronously transmitted and received simultaneously. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO)

- Serial Data In (SDI)

- Serial Clock (SCK)

Additionally, a fourth pin may be used when in a Slave mode of operation:

- Slave Select (SS)

- Note 1: When the SPI is in Slave mode with SS pin control enabled (SSPM<3:0> bits of the SSPCON register = 0100), the SPI module will reset if the SS pin is set to VDD.

- **2:** If the SPI is used in Slave mode with CKE = 1, then the  $\overline{SS}$  pin control must be enabled.

- 3: When the SPI is in Slave mode with SS pin control enabled (SSPM<3:0> bits of the SSPCON register = 0100), the state of the SS pin can affect the state read back from the TRISC<4> bit. The peripheral OE signal from the SSP module into PORTC controls the state that is read back from the TRISC<4> bit "Electrical (see Section 17.0 Specifications" for information on read-write-modify PORTC). lf instructions, such as BSF, are performed on the TRISC register while the  $\overline{SS}$  pin is high, this will cause the TRISC<7> bit to be set, thus disabling the SDO output.

#### FIGURE 13-1: S

#### SSP BLOCK DIAGRAM (SPI MODE)

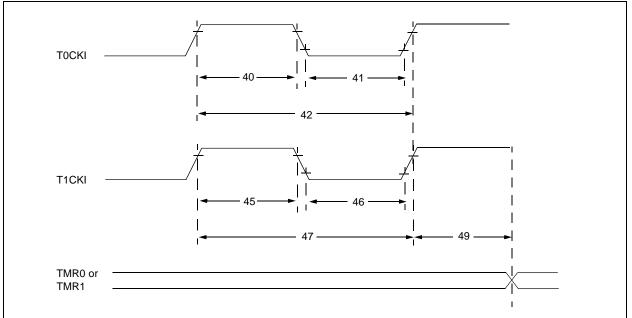

## FIGURE 17-8: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

### TABLE 17-5: TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Sym.                                     |                                      | Characterist                                                | ic                                        | Min.                                      | Тур†   | Max.   | Units                              | Conditions                         |

|--------------|------------------------------------------|--------------------------------------|-------------------------------------------------------------|-------------------------------------------|-------------------------------------------|--------|--------|------------------------------------|------------------------------------|

| 40*          | T⊤0H                                     | T0CKI High F                         | Pulse Width No Prescaler                                    |                                           | 0.5 TCY + 20                              | _      | _      | ns                                 |                                    |

|              |                                          | With Prescaler                       |                                                             | 10                                        | _                                         | _      | ns     |                                    |                                    |

| 41*          | TT0L                                     | T0CKI Low P                          | ulse Width                                                  | No Prescaler                              | 0.5 TCY + 20                              | —      | _      | ns                                 |                                    |

|              |                                          |                                      |                                                             | With Prescaler                            | 10                                        | —      | _      | ns                                 |                                    |

| 42*          | Тт0Р                                     | T0CKI Period                         | 1                                                           |                                           | Greater of:<br>20 or <u>Tcy + 40</u><br>N | _      | _      | ns                                 | N = prescale value<br>(2, 4,, 256) |

| 45*          | TT1H                                     | T1CKI High Synchronous, No Prescaler |                                                             |                                           | 0.5 TCY + 20                              | —      | _      | ns                                 |                                    |

|              |                                          | Time                                 | Synchronous,<br>with Prescaler                              |                                           | 15                                        | _      | _      | ns                                 |                                    |

|              |                                          |                                      | Asynchronous                                                |                                           | 30                                        | —      | _      | ns                                 |                                    |

| 46*          | TT1L                                     | T1CKI Low Synchronous, No Prescaler  |                                                             | No Prescaler                              | 0.5 TCY + 20                              | —      | _      | ns                                 |                                    |

|              |                                          | Time                                 | Synchronous,<br>with Prescaler                              |                                           | 15                                        | —      | _      | ns                                 |                                    |

|              |                                          |                                      | Asynchronous                                                |                                           | 30                                        | —      | _      | ns                                 |                                    |

| 47*          | * TT1P T1CKI Input Synchronous<br>Period |                                      |                                                             | Greater of:<br>30 or <u>Tcy + 40</u><br>N | —                                         | _      | ns     | N = prescale value<br>(1, 2, 4, 8) |                                    |

|              |                                          |                                      | Asynchronous                                                |                                           | 60                                        | —      | _      | ns                                 |                                    |

| 48           | F⊤1                                      |                                      | ator Input Frequency Range<br>abled by setting bit T1OSCEN) |                                           | -                                         | 32.768 | —      | kHz                                |                                    |

| 49*          | TCKEZTMR1                                | Delay from E<br>Increment            | elay from External Clock Edge to Timer                      |                                           |                                           | —      | 7 Tosc | -                                  | Timers in Sync<br>mode             |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

| Param | Device               |      |      |      | Condition |        |                                |

|-------|----------------------|------|------|------|-----------|--------|--------------------------------|

| No.   | Characteristics      | Min. | Тур. | Max. | Units     | Vdd    | Note                           |

| D001  | Vdd                  | 2.1  | _    | 5.5  | V         | _      | Fosc ≤ 8 MHz: HFINTOSC, EC     |

|       |                      | 2.1  | _    | 5.5  | V         | _      | Fosc ≤ 4 MHz                   |

| D010  | Supply Current (IDD) | _    |      | 47   |           | 2.1    | E 00.111                       |

|       |                      | —    | _    | 69   | μA        | 3.0    | Fosc = 32 kHz<br>LP Oscillator |

|       |                      |      |      | 108  |           | 5.0    |                                |

| D011  |                      | —    | _    | 357  |           | 2.1    |                                |

|       |                      | —    | _    | 533  | μA        | 3.0    | Fosc = 1 MHz<br>XT Oscillator  |

|       |                      | —    | _    | 729  |           | 5.0    |                                |

| D012  |                      | —    | _    | 535  | μA        | 2.1    |                                |

|       |                      | —    | _    | 875  | μΛ        | 3.0    | Fosc = 4 MHz<br>XT Oscillator  |

|       |                      | —    |      | 1.32 | mA        | 5.0    |                                |

| D013  |                      | —    | _    | 336  |           | 2.1    |                                |

|       |                      | —    | _    | 477  | μA        | μΑ 3.0 | Fosc = 1 MHz<br>EC Oscillator  |

|       |                      | —    | _    | 777  |           | 5.0    |                                |

| D014  |                      | —    | _    | 505  | μA        | 2.1    |                                |

|       |                      | —    | _    | 724  | μι        | 3.0    | Fosc = 4 MHz<br>EC Oscillator  |

|       |                      | —    | _    | 1.30 | mA        | 5.0    |                                |

| D015  |                      | _    |      | 51   | μA        | 2.1    |                                |

|       |                      | —    | _    | 92   | μι        | 3.0    | Fosc = 31 kHz<br>LFINTOSC      |

|       |                      | —    |      | 117  | mA        | 5.0    |                                |

| D016  |                      | —    | _    | 665  | μA        | 2.1    |                                |

|       |                      | —    | _    | 970  | μΛ        | 3.0    | Fosc = 4 MHz<br>HFINTOSC       |

|       |                      | —    | _    | 1.56 | mA        | 5.0    |                                |

| D017  |                      | —    | _    | 936  | μΑ        | 2.1    |                                |

|       |                      | —    | _    | 1.34 | mA        | 3.0    | Fosc = 8 MHz<br>HFINTOSC       |

|       |                      | —    | _    | 2.27 |           | 5.0    |                                |

| D018  |                      | —    | _    | 605  | μA        | 2.1    |                                |

|       |                      |      | _    | 903  |           | 3.0    | Fosc = 4 MHz<br>EXTRC          |

|       |                      |      |      | 1.43 | mA        | 5.0    |                                |

| D019  |                      | —    | —    | 6.61 | mA        | 4.5    | Fosc = 20 MHz                  |

|       |                      |      |      | 7.81 |           | 5.0    | HS Oscillator                  |

# TABLE 17-19: DC CHARACTERISTICS FOR IDD SPECIFICATIONS FOR PIC16F685/687/689/690-H (High Temp.)

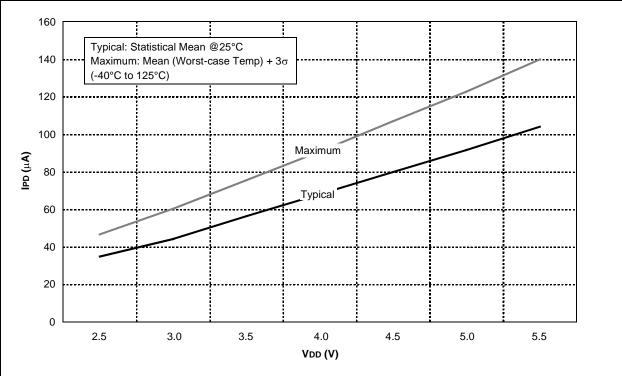

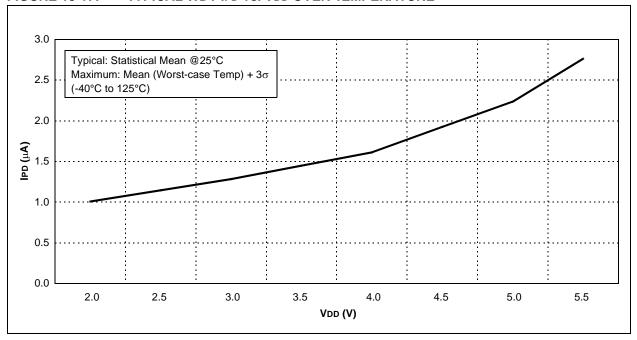

BOR IPD vs. VDD OVER TEMPERATURE

FIGURE 18-16: