Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Number of I/O              | 18                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

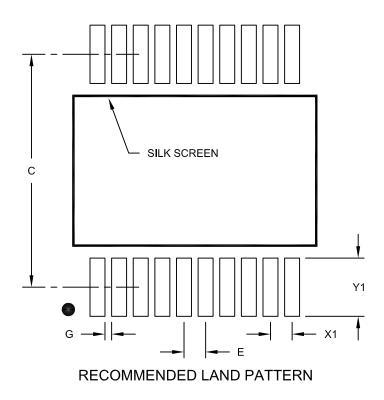

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 20-QFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f677t-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### FIGURE 2-6: PIC16F685 SPECIAL FUNCTION REGISTERS

|                   | File    |                    | File    |                 | File    |                       | File   |

|-------------------|---------|--------------------|---------|-----------------|---------|-----------------------|--------|

|                   | Address |                    | Address | · · · · · · (1) | Address |                       | Addres |

| ndirect addr. (1) | 00h     | Indirect addr. (1) | 80h     |                 | 100h    | Indirect addr. (1)    | 180h   |

| TMR0              | 01h     | OPTION_REG         | 81h     | TMR0            | 101h    | OPTION_REG            | 181h   |

| PCL               | 02h     | PCL                | 82h     | PCL             | 102h    | PCL                   | 182h   |

| STATUS            | 03h     | STATUS             | 83h     | STATUS          | 103h    | STATUS                | 183h   |

| FSR               | 04h     | FSR                | 84h     | FSR             | 104h    | FSR                   | 184h   |

| PORTA             | 05h     | TRISA              | 85h     | PORTA           | 105h    | TRISA                 | 185h   |

| PORTB             | 06h     | TRISB              | 86h     | PORTB           | 106h    | TRISB                 | 186h   |

| PORTC             | 07h     | TRISC              | 87h     | PORTC           | 107h    | TRISC                 | 187h   |

|                   | 08h     |                    | 88h     |                 | 108h    |                       | 188h   |

|                   | 09h     |                    | 89h     |                 | 109h    |                       | 189h   |

| PCLATH            | 0Ah     | PCLATH             | 8Ah     | PCLATH          | 10Ah    | PCLATH                | 18Ah   |

| INTCON            | 0Bh     | INTCON             | 8Bh     | INTCON          | 10Bh    | INTCON                | 18Bh   |

| PIR1              | 0Ch     | PIE1               | 8Ch     | EEDAT           | 10Ch    | EECON1                | 18Ch   |

| PIR2              | 0Dh     | PIE2               | 8Dh     | EEADR           | 10Dh    | EECON2 <sup>(1)</sup> | 18Dh   |

| TMR1L             | 0Eh     | PCON               | 8Eh     | EEDATH          | 10Eh    |                       | 18Eh   |

| TMR1H             | 0Fh     | OSCCON             | 8Fh     | EEADRH          | 10Fh    |                       | 18Fh   |

| T1CON             | 10h     | OSCTUNE            | 90h     |                 | 110h    |                       | 190h   |

| TMR2              | 11h     |                    | 91h     |                 | 111h    |                       | 191h   |

| T2CON             | 12h     | PR2                | 92h     |                 | 112h    |                       | 192h   |

|                   | 13h     |                    | 93h     |                 | 113h    |                       | 193h   |

|                   | 14h     |                    | 94h     |                 | 114h    |                       | 194h   |

| CCPR1L            | 15h     | WPUA               | 95h     | WPUB            | 115h    |                       | 195h   |

| CCPR1H            | 16h     | IOCA               | 96h     | IOCB            | 116h    |                       | 196h   |

| CCP1CON           | 17h     | WDTCON             | 97h     |                 | 117h    |                       | 197h   |

|                   | 18h     |                    | 98h     | VRCON           | 118h    |                       | 198h   |

|                   | 19h     |                    | 99h     | CM1CON0         | 119h    |                       | 199h   |

|                   | 1Ah     |                    | 9Ah     | CM2CON0         | 11Ah    |                       | 19Ah   |

|                   | 1Bh     |                    | 9Bh     | CM2CON1         | 11Bh    |                       | 19Bh   |

| PWM1CON           | 1Ch     |                    | 9Ch     |                 | 11Ch    |                       | 19Ch   |

| ECCPAS            | 1Dh     |                    | 9Dh     |                 | 11Dh    | PSTRCON               | 19Dh   |

| ADRESH            | 1Eh     | ADRESL             | 9Eh     | ANSEL           | 11Eh    | SRCON                 | 19Eh   |

| ADCON0            | 1Fh     | ADCON1             | 9Fh     | ANSELH          | 11Fh    |                       | 19Fh   |

|                   | 20h     |                    | A0h     |                 | 120h    |                       | 1A0h   |

|                   |         | General            |         | General         |         |                       |        |

| General           |         | Purpose            |         | Purpose         |         |                       |        |

| Purpose           |         | Register           |         | Register        |         |                       |        |

| Register          |         |                    |         |                 |         |                       |        |

| OG Dutoo          |         | 80 Bytes           |         | 80 Bytes        |         |                       |        |

| 96 Bytes          |         |                    | EFh     | ļ               | 16Fh    |                       |        |

|                   |         |                    | F0h     |                 | 170h    |                       | 1F0h   |

|                   | 7Fh     | 70h-7Fh            | FFh     | 70h-7Fh         | 17Fh    | 70h-7Fh               | 1FFh   |

| Bank 0            |         | Bank 1             |         | Bank 2          |         | Bank 3                |        |

**Note 1:** Not a physical register.

| Addr   | Name                   | Bit 7                | Bit 6                                               | Bit 5        | Bit 4          | Bit 3        | Bit 2           | Bit 1        | Bit 0                | Value on<br>POR, BOR | Page    |

|--------|------------------------|----------------------|-----------------------------------------------------|--------------|----------------|--------------|-----------------|--------------|----------------------|----------------------|---------|

| Bank 3 |                        |                      |                                                     |              |                |              |                 |              |                      |                      |         |

| 180h   | INDF                   | Addressing           | this location                                       | n uses conte | ents of FSR to | address da   | ata memory      | (not a physi | cal register)        | xxxx xxxx            | 43,200  |

| 181h   | OPTION_REG             | RABPU                | INTEDG                                              | TOCS         | TOSE           | PSA          | PS2             | PS1          | PS0                  | 1111 1111            | 36,200  |

| 182h   | PCL                    | Program C            | ounter's (PC                                        | C) Least Sig | nificant Byte  |              |                 |              |                      | 0000 0000            | 43,200  |

| 183h   | STATUS                 | IRP                  | RP1                                                 | RP0          | TO             | PD           | Z               | DC           | С                    | 0001 1xxx            | 35,200  |

| 184h   | FSR                    | Indirect Dat         | ta Memory A                                         | Address Poir | nter           |              |                 |              |                      | xxxx xxxx            | 43,200  |

| 185h   | TRISA                  | _                    | —                                                   | TRISA5       | TRISA4         | TRISA3       | TRISA2          | TRISA1       | TRISA0               | 11 1111              | 57,200  |

| 186h   | TRISB                  | TRISB7               | TRISB6                                              | TRISB5       | TRISB4         | _            | _               | _            | _                    | 1111                 | 68,201  |

| 187h   | TRISC                  | TRISC7               | TRISC6                                              | TRISC5       | TRISC4         | TRISC3       | TRISC2          | TRISC1       | TRISC0               | 1111 1111            | 74,201  |

| 188h   | —                      | Unimpleme            | ented                                               |              |                |              |                 |              |                      | —                    | _       |

| 189h   | —                      | Unimpleme            | ented                                               |              |                |              |                 |              |                      | _                    | —       |

| 18Ah   | PCLATH                 | _                    |                                                     |              | Write Buffer   | for the uppe | er 5 bits of th | ne Program   | Counter              | 0 0000               | 43,200  |

| 18Bh   | INTCON                 | GIE                  | PEIE                                                | TOIE         | INTE           | RABIE        | T0IF            | INTF         | RABIF <sup>(1)</sup> | 0000 000x            | 37,200  |

| 18Ch   | EECON1                 | EEPGD <sup>(2)</sup> | _                                                   | _            | _              | WRERR        | WREN            | WR           | RD                   | x x000               | 119,201 |

| 18Dh   | EECON2                 | EEPROM (             | EEPROM Control Register 2 (not a physical register) |              |                |              |                 |              |                      |                      | 117,201 |

| 18Eh   | _                      | Unimpleme            | ented                                               |              |                |              |                 |              |                      | —                    | _       |

| 18Fh   | —                      | Unimpleme            | ented                                               |              |                |              |                 |              |                      | —                    | _       |

| 190h   | —                      | Unimpleme            | ented                                               |              |                |              |                 |              |                      | _                    | —       |

| 191h   | —                      | Unimpleme            | ented                                               |              |                |              |                 |              |                      | —                    | _       |

| 192h   | —                      | Unimpleme            | ented                                               |              |                |              |                 |              |                      | —                    | _       |

| 193h   | —                      | Unimpleme            | ented                                               |              |                |              |                 |              |                      | —                    | _       |

| 194h   | _                      | Unimpleme            | ented                                               |              |                |              |                 |              |                      | —                    | —       |

| 195h   | _                      | Unimpleme            | ented                                               |              |                |              |                 |              |                      | —                    | —       |

| 196h   | _                      | Unimpleme            | ented                                               |              |                |              |                 |              |                      | —                    | —       |

| 197h   | _                      | Unimpleme            | ented                                               |              |                |              |                 |              |                      | —                    | —       |

| 198h   | _                      | Unimpleme            | ented                                               |              |                |              |                 |              |                      | —                    | —       |

| 199h   | —                      | Unimpleme            | ented                                               |              |                |              |                 |              |                      | _                    | _       |

| 19Ah   | —                      | Unimpleme            | ented                                               |              |                |              |                 |              |                      | _                    | —       |

| 19Bh   | —                      | Unimpleme            | ented                                               |              |                |              |                 |              |                      | -                    | _       |

| 19Ch   | —                      | Unimpleme            | ented                                               |              |                |              |                 |              |                      | _                    | _       |

| 19Dh   | PSTRCON <sup>(2)</sup> | _                    | _                                                   | _            | STRSYNC        | STRD         | STRC            | STRB         | STRA                 | 0 0001               | 144,201 |

| 19Eh   | SRCON                  | SR1                  | SR0                                                 | C1SEN        | C2REN          | PULSS        | PULSR           | —            | —                    | 0000 00              | 101,201 |

| 19Fh   | —                      | Unimpleme            | ented                                               |              |                |              |                 |              |                      | —                    | _       |

# TABLE 2-4: PIC16F631/677/685/687/689/690 SPECIAL FUNCTION REGISTERS SUMMARY BANK 3

Legend: -= Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

Note 1: MCLR and WDT Reset does not affect the previous value data latch. The RABIF bit will be cleared upon Reset but will set again if the mismatch exists.

2: PIC16F685/PIC16F690 only.

### 2.2.2.6 PIR1 Register

The PIR1 register contains the interrupt flag bits, as shown in Register 2-6.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

# REGISTER 2-6: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

| U-0   | R/W-0               | R-0                 | R-0                 | R/W-0                | R/W-0                 | R/W-0                 | R/W-0  |

|-------|---------------------|---------------------|---------------------|----------------------|-----------------------|-----------------------|--------|

| —     | ADIF <sup>(5)</sup> | RCIF <sup>(3)</sup> | TXIF <sup>(3)</sup> | SSPIF <sup>(4)</sup> | CCP1IF <sup>(2)</sup> | TMR2IF <sup>(1)</sup> | TMR1IF |

| bit 7 |                     |                     |                     |                      |                       |                       | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7 | Unimplemented: Read as '0'                                                                                                                          |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | ADIF: A/D Converter Interrupt Flag bit <sup>(5)</sup>                                                                                               |

|       | <ul> <li>1 = A/D conversion complete (must be cleared in software)</li> <li>0 = A/D conversion has not completed or has not been started</li> </ul> |

| bit 5 | RCIF: EUSART Receive Interrupt Flag bit <sup>(3)</sup>                                                                                              |

|       | <ul> <li>1 = The EUSART receive buffer is full (cleared by reading RCREG)</li> <li>0 = The EUSART receive buffer is not full</li> </ul>             |

| bit 4 | <b>TXIF:</b> EUSART Transmit Interrupt Flag bit <sup>(3)</sup>                                                                                      |

|       | <ul> <li>1 = The EUSART transmit buffer is empty (cleared by writing to TXREG)</li> <li>0 = The EUSART transmit buffer is full</li> </ul>           |

| bit 3 | SSPIF: Synchronous Serial Port (SSP) Interrupt Flag bit <sup>(4)</sup>                                                                              |

|       | <ul> <li>1 = The Transmission/Reception is complete (must be cleared in software)</li> <li>0 = Waiting to Transmit/Receive</li> </ul>               |

| bit 2 | CCP1IF: CCP1 Interrupt Flag bit <sup>(2)</sup>                                                                                                      |

|       | Capture mode:                                                                                                                                       |

|       | <ul> <li>1 = A TMR1 register capture occurred (must be cleared in software)</li> <li>0 = No TMR1 register capture occurred</li> </ul>               |

|       | Compare mode:                                                                                                                                       |

|       | <ul> <li>1 = A TMR1 register compare match occurred (must be cleared in software)</li> <li>0 = No TMR1 register compare match occurred</li> </ul>   |

|       | <u>PWM mode:</u>                                                                                                                                    |

|       | Unused in this mode                                                                                                                                 |

| bit 1 | TMR2IF: Timer2 to PR2 Interrupt Flag bit <sup>(1)</sup>                                                                                             |

|       | <ul> <li>1 = A Timer2 to PR2 match occurred (must be cleared in software)</li> <li>0 = No Timer2 to PR2 match occurred</li> </ul>                   |

| bit 0 | TMR1IF: Timer1 Overflow Interrupt Flag bit                                                                                                          |

|       | <ul> <li>1 = The TMR1 register overflowed (must be cleared in software)</li> <li>0 = The TMR1 register did not overflow</li> </ul>                  |

| Note  | 1: PIC16F685/PIC16F690 only.                                                                                                                        |

|       | 2: PIC16F685/PIC16F689/PIC16F690 only.                                                                                                              |

|       | 3: PIC16F687/PIC16F689/PIC16F690 only.                                                                                                              |

|       | 4: PIC16F677/PIC16F687/PIC16F689/PIC16F690 only.                                                                                                    |

|       | 5: PIC16F677/PIC16F685/PIC16F687/PIC16F689/PIC16F690 only.                                                                                          |

# 3.3 Clock Source Modes

Clock Source modes can be classified as external or internal.

- External Clock modes rely on external circuitry for the clock source. Examples are: Oscillator modules (EC mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes) and Resistor-Capacitor (RC) mode circuits.

- Internal clock sources are contained internally within the Oscillator module. The Oscillator module has two internal oscillators: the 8 MHz High-Frequency Internal Oscillator (HFINTOSC) and the 31 kHz Low-Frequency Internal Oscillator (LFINTOSC).

The system clock can be selected between external or internal clock sources via the System Clock Select (SCS) bit of the OSCCON register. See **Section 3.6 "Clock Switching"** for additional information.

# 3.4 External Clock Modes

# 3.4.1 OSCILLATOR START-UP TIMER (OST)

If the Oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) counts 1024 oscillations from OSC1. This occurs following a Power-on Reset (POR) and when the Power-up Timer (PWRT) has expired (if configured), or a wake-up from Sleep. During this time, the program counter does not increment and program execution is suspended. The OST ensures that the oscillator circuit, using a quartz crystal resonator or ceramic resonator, has started and is providing a stable system clock to the Oscillator module. When switching between clock sources, a delay is required to allow the new clock to stabilize. These oscillator delays are shown in Table 3-1.

In order to minimize latency between external oscillator start-up and code execution, the Two-Speed Clock Start-up mode can be selected (see Section 3.7 "Two-Speed Clock Start-up Mode").

| Switch From       | Switch To            | Frequency                  | Oscillator Delay                 |

|-------------------|----------------------|----------------------------|----------------------------------|

| Sleep/POR         | LFINTOSC<br>HFINTOSC | 31 kHz<br>125 kHz to 8 MHz | Oscillator Warm-up Delay (Twarm) |

| Sleep/POR         | EC, RC               | DC – 20 MHz                | 2 cycles                         |

| LFINTOSC (31 kHz) | EC, RC               | DC – 20 MHz                | 1 cycle of each                  |

| Sleep/POR         | LP, XT, HS           | 32 kHz to 20 MHz           | 1024 Clock Cycles (OST)          |

| LFINTOSC (31 kHz) | HFINTOSC             | 125 kHz to 8 MHz           | 1 μs (approx.)                   |

# TABLE 3-1: OSCILLATOR DELAY EXAMPLES

# 3.4.2 EC MODE

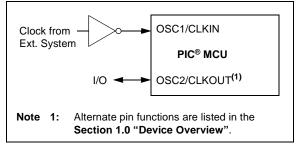

The External Clock (EC) mode allows an externally generated logic level as the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input and the OSC2 is available for general purpose I/O. Figure 3-2 shows the pin connections for EC mode.

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

# FIGURE 3-2:

### EXTERNAL CLOCK (EC) MODE OPERATION

| U-0                | U-0                                             | R/W-1              | R/W-1        | U-0              | R/W-1            | R/W-1           | R/W-1 |

|--------------------|-------------------------------------------------|--------------------|--------------|------------------|------------------|-----------------|-------|

| _                  | —                                               | WPUA5              | WPUA4        |                  | WPUA2            | WPUA1           | WPUA0 |

| bit 7              |                                                 |                    |              |                  |                  |                 | bit 0 |

|                    |                                                 |                    |              |                  |                  |                 |       |

| Legend:            |                                                 |                    |              |                  |                  |                 |       |

| R = Read           | able bit                                        | W = Writable       | bit          | U = Unimpler     | mented bit, read | l as '0'        |       |

| -n = Value         | e at POR                                        | '1' = Bit is set   |              | '0' = Bit is cle | ared             | x = Bit is unki | nown  |

| bit 7-6<br>bit 5-4 | -                                               | nented: Read as '( |              |                  |                  |                 |       |

| DIL 5-4            | 1 = Pull-up<br>0 = Pull-up                      |                    | Register bit |                  |                  |                 |       |

| bit 3              | Unimplem                                        | nented: Read as 'o | )'           |                  |                  |                 |       |

| bit 2-0            | <b>WPUA&lt;2:</b><br>1 = Pull-up<br>0 = Pull-up |                    | Register bit |                  |                  |                 |       |

| Note 1:<br>2:      |                                                 | bit of the OPTION  | •            |                  |                  |                 | bled. |

#### WPUA: PORTA REGISTER **REGISTER 4-5:**

3: The RA3 pull-up is enabled when configured as MCLR and disabled as an I/O in the Configuration Word.

4: WPUA<5:4> always reads '1' in XT, HS and LP Oscillator modes.

#### **REGISTER 4-6: IOCA: INTERRUPT-ON-CHANGE PORTA REGISTER**

| Logondi |     |       |       |       |       |       |       |

|---------|-----|-------|-------|-------|-------|-------|-------|

|         |     |       |       |       |       |       |       |

| bit 7   |     |       |       |       |       |       | bit 0 |

| _       | —   | IOCA5 | IOCA4 | IOCA3 | IOCA2 | IOCA1 | IOCA0 |

| U-0     | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|         |     |       |       |       |       |       |       |

| Legena.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 IOCA<5:0>: Interrupt-on-change PORTA Control bit

1 = Interrupt-on-change enabled

0 = Interrupt-on-change disabled

Note 1: Global Interrupt Enable (GIE) must be enabled for individual interrupts to be recognized.

2: IOCA<5:4> always reads '1' in XT, HS and LP Oscillator modes.

#### 4.4.3 PIN DESCRIPTIONS AND DIAGRAMS

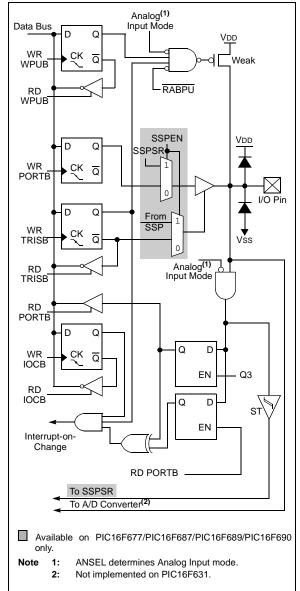

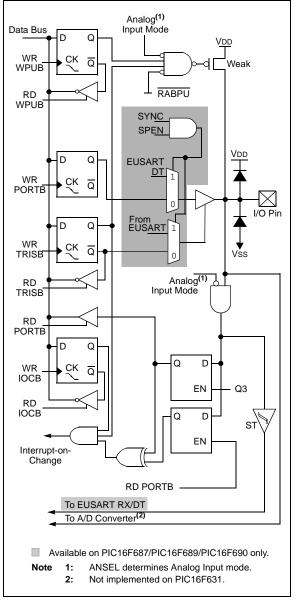

Each PORTB pin is multiplexed with other functions. The pins and their combined functions are briefly described here. For specific information about individual functions such as the SSP,  $l^2C^{TM}$  or interrupts, refer to the appropriate section in this data sheet.

# 4.4.3.1 RB4/AN10/SDI/SDA

Figure 4-7 shows the diagram for this pin. The RB4/ AN10/SDI/SDA<sup>(1)</sup> pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC (except PIC16F631)

- a SPI data I/O

- an I<sup>2</sup>C data I/O

FIGURE 4-7:

# 4.4.3.2 RB5/AN11/RX/DT<sup>(1, 2)</sup>

Figure 4-8 shows the diagram for this pin. The RB5/ AN11/RX/DT pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC (except PIC16F631)

- an asynchronous serial input

- a synchronous serial data I/O

Note 1: RX and DT are available on PIC16F687/ PIC16F689/PIC16F690 only.

2: AN11 is not implemented on PIC16F631.

#### FIGURE 4-8:

#### **BLOCK DIAGRAM OF RB5**

# 8.5 Operation During Sleep

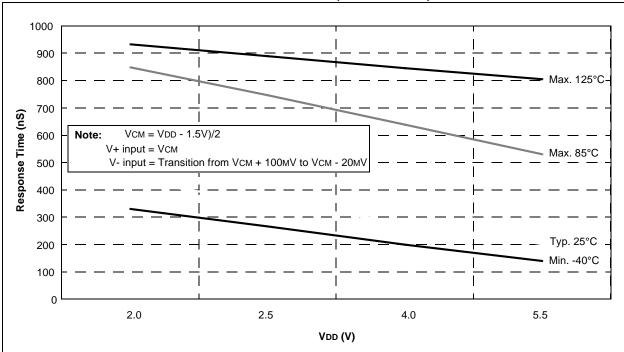

The comparator, if enabled before entering Sleep mode, remains active during Sleep. The additional current consumed by the comparator is shown separately in the **Section 17.0** "**Electrical Specifications**". If the comparator is not used to wake the device, power consumption can be minimized while in Sleep mode by turning off the comparator. Each comparator is turned off by clearing the CxON bit of the CMxCON0 register.

A change to the comparator output can wake-up the device from Sleep. To enable the comparator to wake the device from Sleep, the CxIE bit of the PIE1 register and the PEIE bit of the INTCON register must be set. The instruction following the Sleep instruction always executes following a wake from Sleep. If the GIE bit of the INTCON register is also set, the device will then execute the Interrupt Service Routine.

# 8.6 Effects of a Reset

A device Reset forces the CMxCON0 and CM2CON1 registers to their Reset states. This forces both comparators and the voltage references to their OFF states.

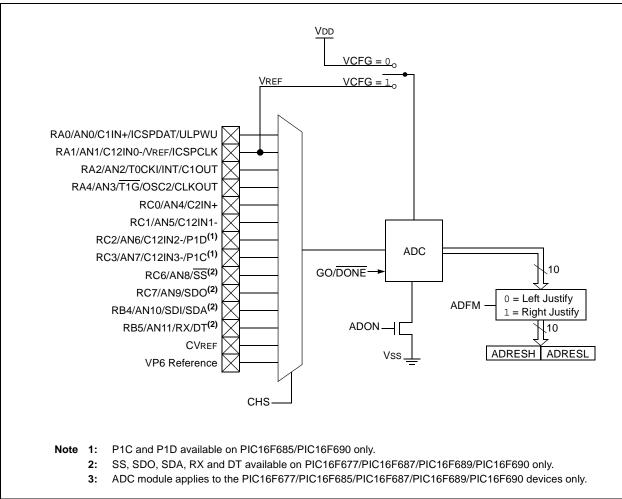

# 9.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 10-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 10-bit binary result via successive approximation and stores the conversion result into the ADC result registers (ADRESL and ADRESH).

Note: The ADC module applies to PIC16F677/ PIC16F685/PIC16F687/PIC16F689/ PIC16F690 devices only.

The ADC voltage reference is software selectable to be either internally generated or externally supplied.

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

# FIGURE 9-1: ADC BLOCK DIAGRAM

Figure 9-1 shows the block diagram of the ADC.

| Name    | Bit 7                               | Bit 6        | Bit 5       | Bit 4             | Bit 3       | Bit 2        | Bit 1      | Bit 0      | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-------------------------------------|--------------|-------------|-------------------|-------------|--------------|------------|------------|----------------------|---------------------------------|

| BAUDCTL | ABDOVF                              | RCIDL        | _           | SCKP              | BRG16       | _            | WUE        | ABDEN      | 01-0 0-00            | 01-0 0-00                       |

| INTCON  | GIE                                 | PEIE         | TOIE        | INTE              | RABIE       | T0IF         | INTF       | RABIF      | x000 000x            | 0000 000x                       |

| PIE1    | —                                   | ADIE         | RCIE        | TXIE              | SSPIE       | CCP1IE       | TMR2IE     | TMR1IE     | -000 0000            | -000 0000                       |

| PIR1    | _                                   | ADIF         | RCIF        | TXIF              | SSPIF       | CCP1IF       | TMR2IF     | TMR1IF     | -000 0000            | -000 0000                       |

| RCREG   | EUSART F                            | Receive Da   | ta Register |                   |             |              |            |            | 0000 0000            | 0000 0000                       |

| RCSTA   | SPEN                                | RX9          | SREN        | CREN              | ADDEN       | FERR         | OERR       | RX9D       | x000 000x            | 0000 000x                       |

| SPBRG   | BRG7                                | BRG6         | BRG5        | BRG4              | BRG3        | BRG2         | BRG1       | BRG0       | 0000 0000            | 0000 0000                       |

| SPBRGH  | BRG15                               | BRG14        | BRG13       | BRG12             | BRG11       | BRG10        | BRG9       | BRG8       | 0000 0000            | 0000 0000                       |

| TRISB   | TRISB7                              | TRISB6       | TRISB5      | TRISB4            |             |              |            |            | 1111                 | 1111                            |

| TXREG   | TXREG EUSART Transmit Data Register |              |             |                   |             |              |            |            |                      | 0000 0000                       |

| TXSTA   | CSRC                                | TX9          | TXEN        | SYNC              | SENDB       | BRGH         | TRMT       | TX9D       | 0000 0010            | 0000 0010                       |

| Legend: | x = unknov                          | vn, – = unir | nplemented  | <b>read as</b> '0 | '. Shaded c | ells are not | used for A | synchronou | is Reception.        |                                 |

# TABLE 12-2: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

# 12.5 EUSART Operation During Sleep

The EUSART WILL remain active during Sleep only in the Synchronous Slave mode. All other modes require the system clock and therefore cannot generate the necessary signals to run the Transmit or Receive Shift registers during Sleep.

Synchronous Slave mode uses an externally generated clock to run the Transmit and Receive Shift registers.

#### 12.5.1 SYNCHRONOUS RECEIVE DURING SLEEP

To receive during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for Synchronous Slave Reception (see Section 12.4.2.4 "Synchronous Slave Reception Set-up:").

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- The RCIF interrupt flag must be cleared by reading RCREG to unload any pending characters in the receive buffer.

Upon entering Sleep mode, the device will be ready to accept data and clocks on the RX/DT and TX/CK pins, respectively. When the data word has been completely clocked in by the external device, the RCIF interrupt flag bit of the PIR1 register will be set. Thereby, waking the processor from Sleep.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the GIE Global Interrupt Enable bit of the INTCON register is also set, then the Interrupt Service Routine at address 004h will be called.

### 12.5.2 SYNCHRONOUS TRANSMIT DURING SLEEP

To transmit during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for Synchronous Slave Transmission (see Section 12.4.2.2 "Synchronous Slave Transmission Set-up:").

- The TXIF interrupt flag must be cleared by writing the output data to the TXREG, thereby filling the TSR and transmit buffer.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the PEIE bit of the INTCON register.

- Interrupt enable bits TXIE of the PIE1 register and PEIE of the INTCON register must set.

Upon entering Sleep mode, the device will be ready to accept clocks on TX/CK pin and transmit data on the RX/DT pin. When the data word in the TSR has been completely clocked out by the external device, the pending byte in the TXREG will transfer to the TSR and the TXIF flag will be set. Thereby, waking the processor from Sleep. At this point, the TXREG is available to accept another character for transmission, which will clear the TXIF flag.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the GIE Global Interrupt Enable bit is also set then the Interrupt Service Routine at address 0004h will be called.

| R/W-0           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R/W-0                                                                                                                                                                                                                                                         | R/W-0                                                                                                                                                                                             | R/W-0                                                                                                               | R/W-0                                        | R/W-0                                  | R/W-0                              |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------|------------------------------------|

| WCOL            | SSPOV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SSPEN                                                                                                                                                                                                                                                         | CKP                                                                                                                                                                                               | SSPM3 <sup>(2)</sup>                                                                                                | SSPM2 <sup>(2)</sup>                         | SSPM1 <sup>(2)</sup>                   | SSPM0 <sup>(2)</sup>               |

| bit 7           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                               |                                                                                                                                                                                                   |                                                                                                                     | •                                            |                                        | bit                                |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                               |                                                                                                                                                                                                   |                                                                                                                     |                                              |                                        |                                    |

| Legend:         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                               |                                                                                                                                                                                                   |                                                                                                                     |                                              |                                        |                                    |

| R = Readable b  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | W = Writable b                                                                                                                                                                                                                                                | it                                                                                                                                                                                                | •                                                                                                                   | ented bit, read as                           | '0'                                    |                                    |

| -n = Value at P | OR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | '1' = Bit is set                                                                                                                                                                                                                                              |                                                                                                                                                                                                   | '0' = Bit is clea                                                                                                   | red                                          | x = Bit is unkno                       | wn                                 |

| bit 7           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -                                                                                                                                                                                                                                                             |                                                                                                                                                                                                   | still transmitting th                                                                                               | e previous word (                            | must be cleared ir                     | n software)                        |

| bit 6           | In SPI mode:<br>1 = A new byt<br>data in SS<br>transmittir<br>tion (and t<br>0 = No overflo<br>In I <sup>2</sup> C <sup>TM</sup> mode:<br>1 = A byte is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | PSR is lost. Oven<br>ng data, to avoid<br>rransmission) is i<br>ww<br>received while th<br>mode. SSPOV m                                                                                                                                                      | ile the SSPBU<br>rflow can only<br>setting overflow<br>nitiated by writi<br>ne SSPBUF re                                                                                                          | occur in Slave mo<br>v. In Master mode<br>ng to the SSPBU                                                           | ing the previous                             | st read the SSPB<br>is not set since e | BUF, even if onl<br>each new recep |

| bit 5           | <b>SSPEN</b> : Synch<br>In <u>SPI mode</u> :<br>1 = Enables se0 = Disables seIn I2C mode: $1 = Enables the0 = Disables se$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | rronous Serial Po<br>rrial port and con<br>erial port and cor<br>e serial port and<br>erial port and cor                                                                                                                                                      | figures SCK, S<br>figures these p<br>configures the<br>ifigures these p                                                                                                                           | oins as I/O port pi                                                                                                 | ns<br>ns as serial port p                    |                                        |                                    |

| bit 4           | <b>CKP</b> : Clock Po<br>In SPI mode:<br>1 = Idle state fo<br>0 = Idle state fo<br>In I <sup>2</sup> C mode:<br>SCK release co<br>1 = Enable cloo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | larity Select bit<br>or clock is a high<br>or clock is a low l<br>ontrol<br>ck                                                                                                                                                                                | level (Microwir<br>evel (Microwire                                                                                                                                                                | e default)<br>e alternate)                                                                                          |                                              | ·                                      |                                    |

| bit 3-0         | $\begin{array}{l} \textbf{SSPM<3:0>: S}\\ 0000 = SPI Ma\\ 0001 = SPI Ma\\ 0010 = SPI Ma\\ 0010 = SPI Ma\\ 0100 = SPI Sla\\ 0101 = SPI Sla\\ 0101 = SPI Sla\\ 0101 = SPI Sla\\ 0100 = Reserv\\ 1001 = Load S\\ 1010 = Reserv\\ 1001 = Load S\\ 1010 = Reserv\\ 1011 = I^2C Firr\\ 1100 = Reserv\\ 1101 $ | ynchronous Seri<br>aster mode, clock<br>aster mode, clock<br>aster mode, clock<br>ave mode, clock<br>ave mode, clock<br>ave mode, clock<br>ve mode, 7-bit a<br>ve mode, 10-bit<br>red<br>SPMSK register<br>red<br>mware Controlled<br>red<br>ve mode, 7-bit a | al Port Mode S<br>(= Fosc/4<br>(= Fosc/16<br>(= Fosc/64<br>(= TMR2 outpu<br>= SCK pin. <u>SS</u><br>= SCK pin. <u>SS</u><br>ddress<br>address<br>at SSPADD SI<br>d Master mode<br>ddress with Sta | ut/2<br>pin control enabl<br>pin control disabl<br>FR address <sup>(2)</sup><br>(slave IDLE)<br>art and Stop bit in | ed.<br>led. SS can be us<br>terrupts enabled |                                        |                                    |

# REGISTER 13-2: SSPCON: SYNC SERIAL PORT CONTROL REGISTER<sup>(1)</sup>

2: When this mode is selected, any reads or writes to the SSPADD SFR address actually accesses the SSPMSK register.

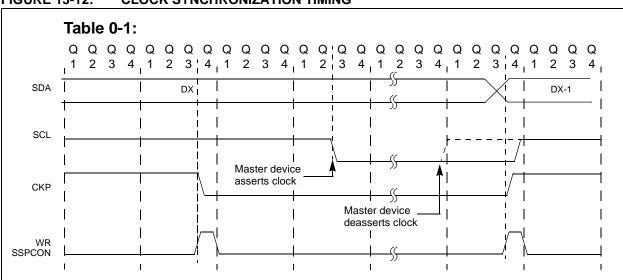

### FIGURE 13-12: CLOCK SYNCHRONIZATION TIMING

| Addr                  | Name                  | Bit 7              | Bit 6              | Bit 5       | Bit 4        | Bit 3        | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-----------------------|-----------------------|--------------------|--------------------|-------------|--------------|--------------|--------|--------|--------|----------------------|---------------------------------|

| 0Bh/8Bh/<br>10Bh/18Bh | INTCON                | GIE                | PEIE               | TOIE        | INTE         | RABIE        | TOIF   | INTF   | RABIF  | 0000 000x            | 0000 000x                       |

| 0Ch                   | PIR1                  | _                  | ADIF               | RCIF        | TXIF         | SSPIF        | CCP1IF | TMR2IF | TMR1IF | -000 0000            | -000 0000                       |

| 13h                   | SSPBUF                | Synchrono          | us Serial Po       | ort Receive | Buffer/Trans | smit Registe | r      |        |        | xxxx xxxx            | uuuu uuuu                       |

| 14h                   | SSPCON                | WCOL               | SSPOV              | SSPEN       | CKP          | SSPM3        | SSPM2  | SSPM1  | SSPM0  | 0000 0000            | 0000 0000                       |

| 86h                   | TRISB                 | TRISB7             | TRISB6             | TRISB5      | TRISB4       | _            | _      | _      | _      | 1111                 | 1111                            |

| 93h                   | SSPMSK <sup>(2)</sup> | MSK7               | MSK6               | MSK5        | MSK4         | MSK3         | MSK2   | MSK1   | MSK0   | 1111 1111            | 1111 1111                       |

| 94h                   | SSPSTAT               | SMP <sup>(3)</sup> | CKE <sup>(3)</sup> | D/A         | Р            | S            | R/W    | UA     | BF     | 0000 0000            | 0000 0000                       |

| 8Ch                   | PIE1                  | _                  | ADIE               | RCIE        | TXIE         | SSPIE        | CCP1IE | TMR2IF | TMR1IF | -000 0000            | -000 0000                       |

Legend: -= Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the SSP module.

Note 1: PIC16F677/PIC16F687/PIC16F689/PIC16F690 only.

2: SSPMSK register (Register 13-3) can be accessed by reading or writing to SSPADD register with bits SSPM<3:0> = 1001. See Registers 13-2 and 13-3 for more details.

3: Maintain these bits clear.

# 14.2.5 TIME-OUT SEQUENCE